Semiconductor memory system and method for data transmission between memory controller and semiconductor memory

A memory controller, memory system technology, applied in static memory, digital memory information, information storage, etc., can solve the problem that the start and end of data bursts cannot be identified, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

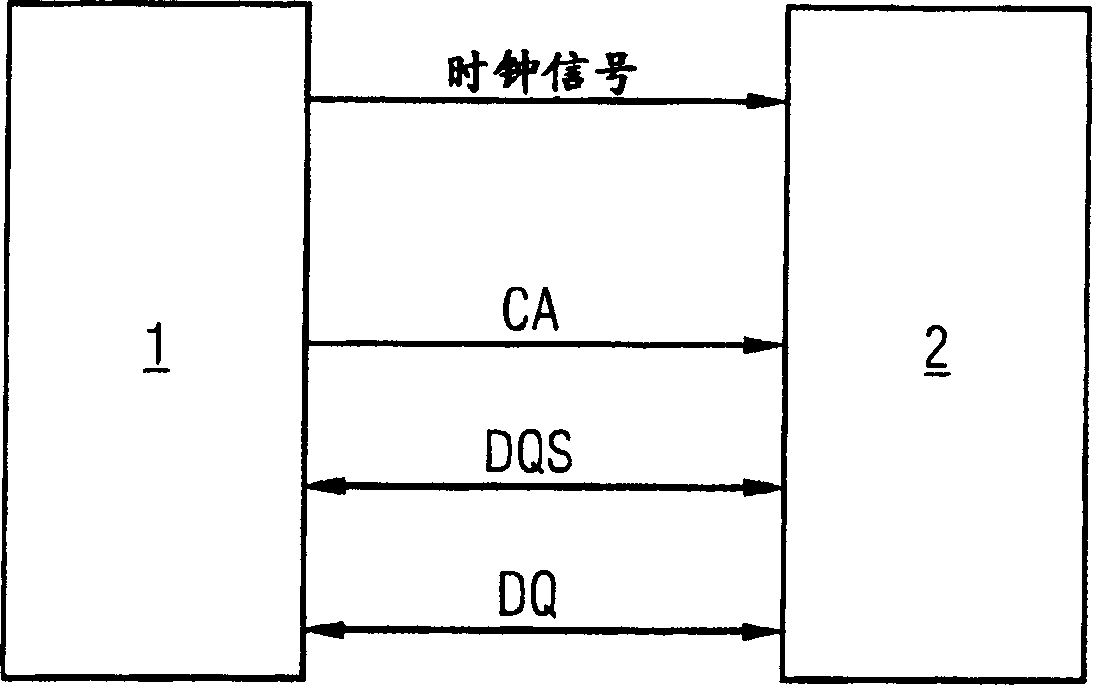

[0023] figure 1 The main components of the semiconductor memory system of the DDR2 generation memory are schematically shown. A clock signal and command / address data CA are transmitted from the memory controller 1 to the semiconductor memory. The bidirectional data strobe signal DQS is transmitted together with the memory data DQ in the semiconductor memory system of the DDR2 generation memory, and notifies the semiconductor memory 2 or the memory controller 1 of the transmission of the memory data DQ to be written or read.

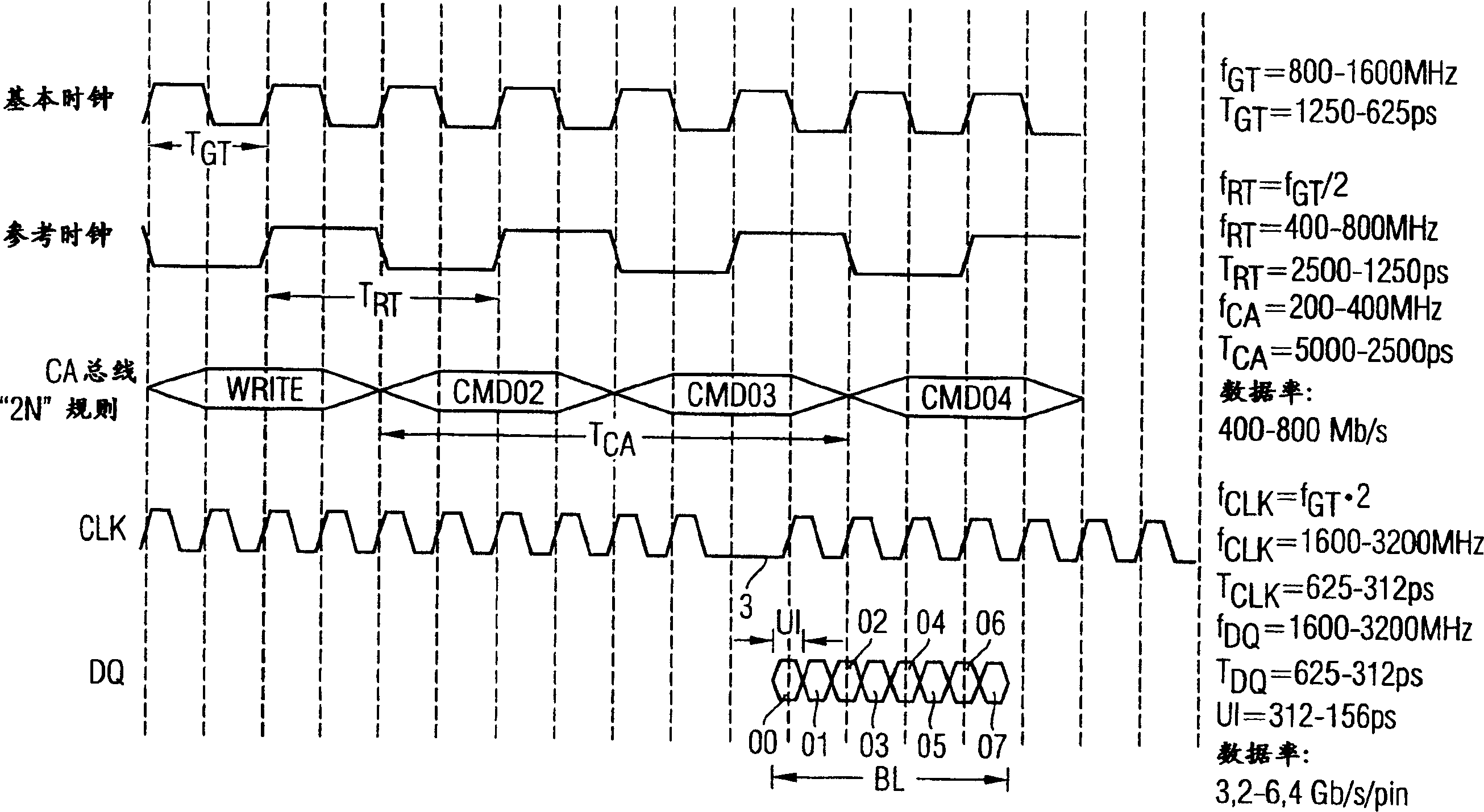

[0024] figure 2 The curve of the signal of the first embodiment is shown schematically with an exemplary signal value range of a future memory of the DDR4 generation, for example. In addition to cycle duration T GT In the range of 1250-625ps (frequency f GT =800-1600MHz) of the basic clock signal, also provided with a cycle duration T RT In the range of 2500-1250p s (frequency f RT = f GT / 2=400-800MHz) reference clock signal. In the clock signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More