Method for mfg. metal silicified layer

A technology of metal silicide and manufacturing method, which is applied in the field of metal silicide layer and metal silicide layer manufacturing, can solve problems such as spike phenomenon and piping effect, and achieve the effect of solving the spike phenomenon and piping effect and improving the gate area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

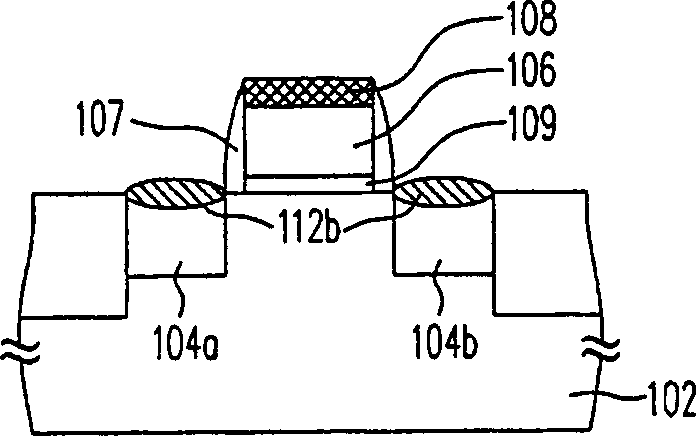

[0017] The concept of the present invention is to form silicide metal layers of different materials on the surface of the substrate, that is, the source region, the drain region and the surface of the gate, so that the problem of small line width and high resistance can be improved at the same time, and the problem of high resistance in the existing process can be solved. Nickel silicide is prone to spiking and piping in the source and drain regions. The following examples are used to illustrate the application of the present invention, but are not intended to limit the scope of the present invention. The present invention can be applied to any steps in the semiconductor process that require simultaneous formation of metal silicides on materials with different crystal structures.

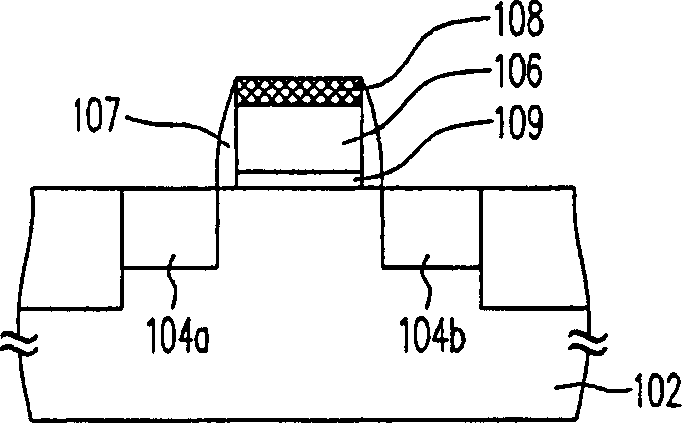

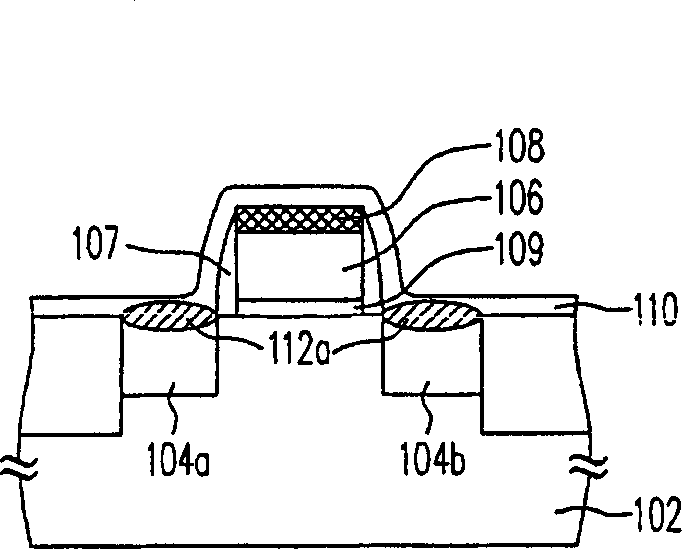

[0018] Figure 1A to Figure 1E It shows a sectional view of the manufacturing process of a metal silicide layer according to a preferred embodiment of the present invention.

[0019] First, please r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More