Patents

Literature

176 results about "Cobalt silicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process for forming cobalt and cobalt silicide materials in copper contact applications

InactiveUS20080268635A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingElectroless depositionCopper

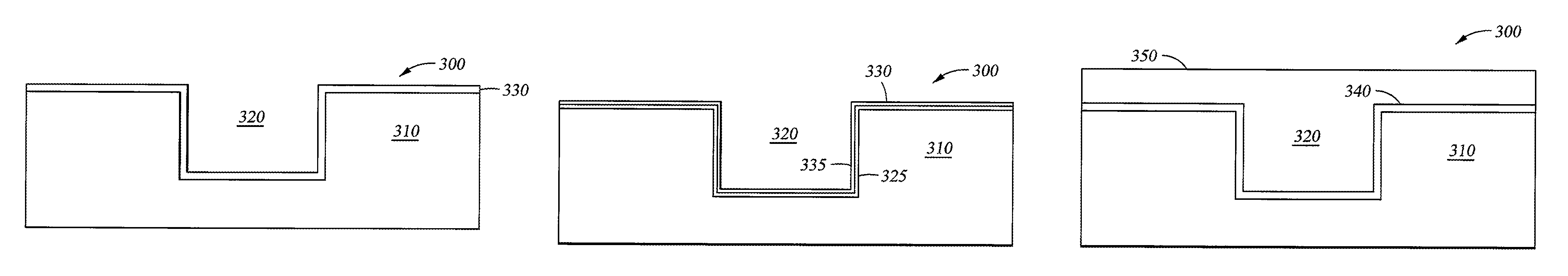

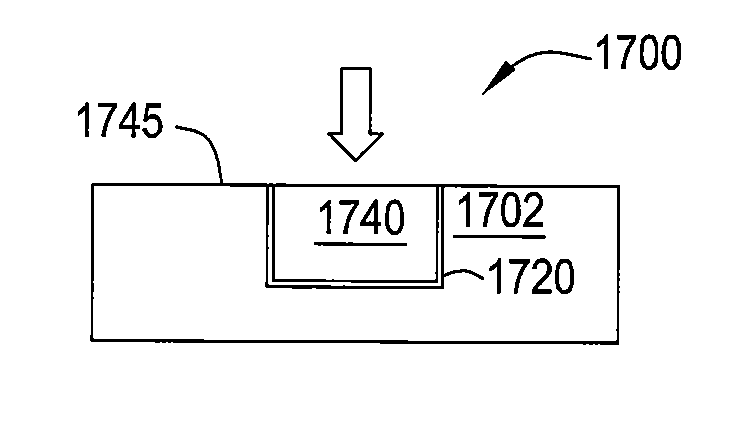

Embodiments of the invention described herein generally provide methods for forming cobalt silicide layers and metallic cobalt layers by using various deposition processes and annealing processes. In one embodiment, a method for forming a cobalt silicide material on a substrate is provided which includes treating the substrate with at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material over the silicon-containing surface, and depositing a copper material over the cobalt silicide material. In another embodiment, a metallic cobalt material may be deposited over the cobalt silicide material prior to depositing the copper material. In one example, the copper material may be formed by depositing a copper seed layer and a copper bulk layer on the substrate. The copper seed layer may be deposited by a PVD process and the copper bulk layer may be deposited by an ECP process or an electroless deposition process.

Owner:APPLIED MATERIALS INC

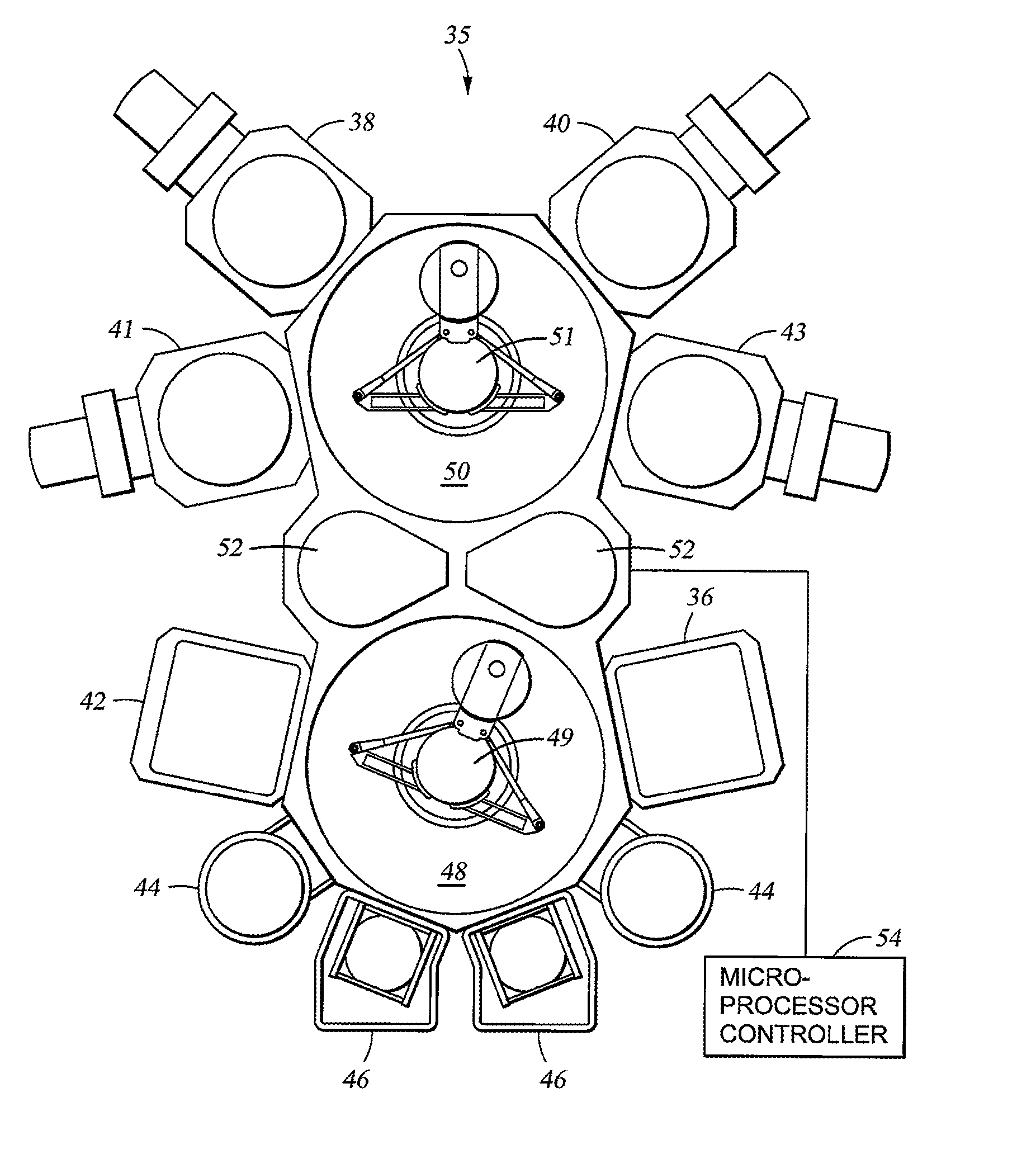

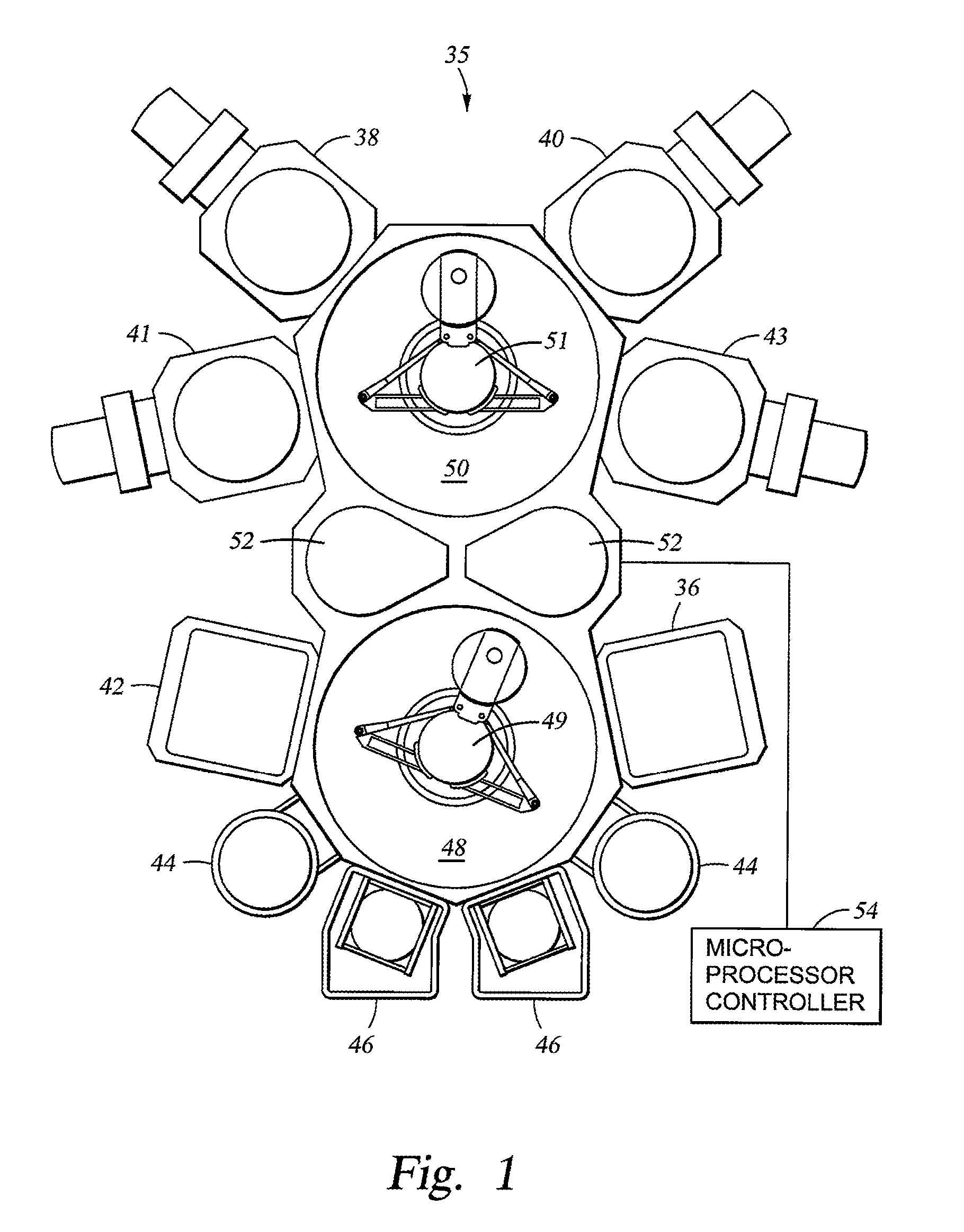

Process for forming cobalt-containing materials

InactiveUS20070202254A1Pretreated surfacesSemiconductor/solid-state device manufacturingCobaltCobalt silicide

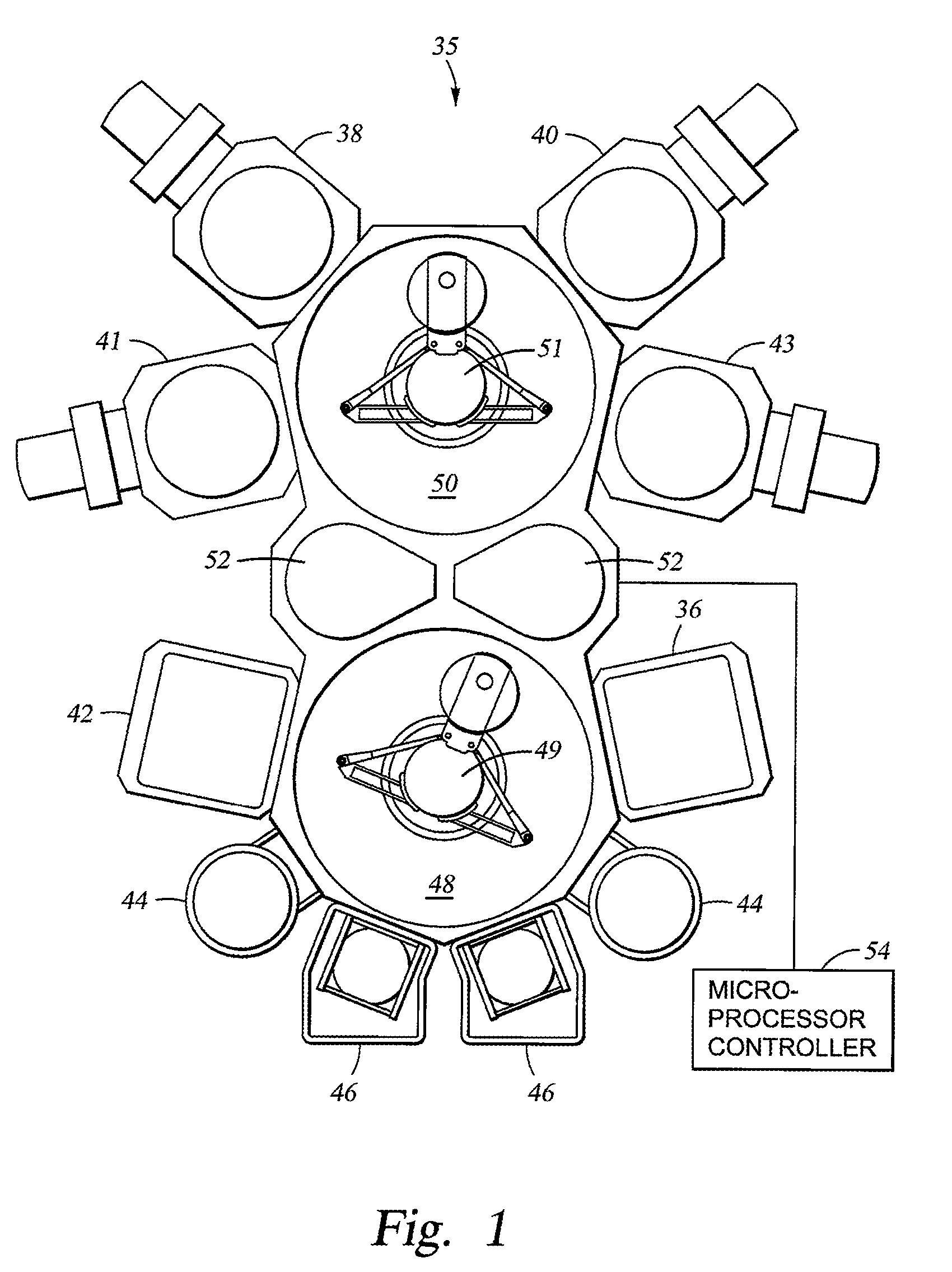

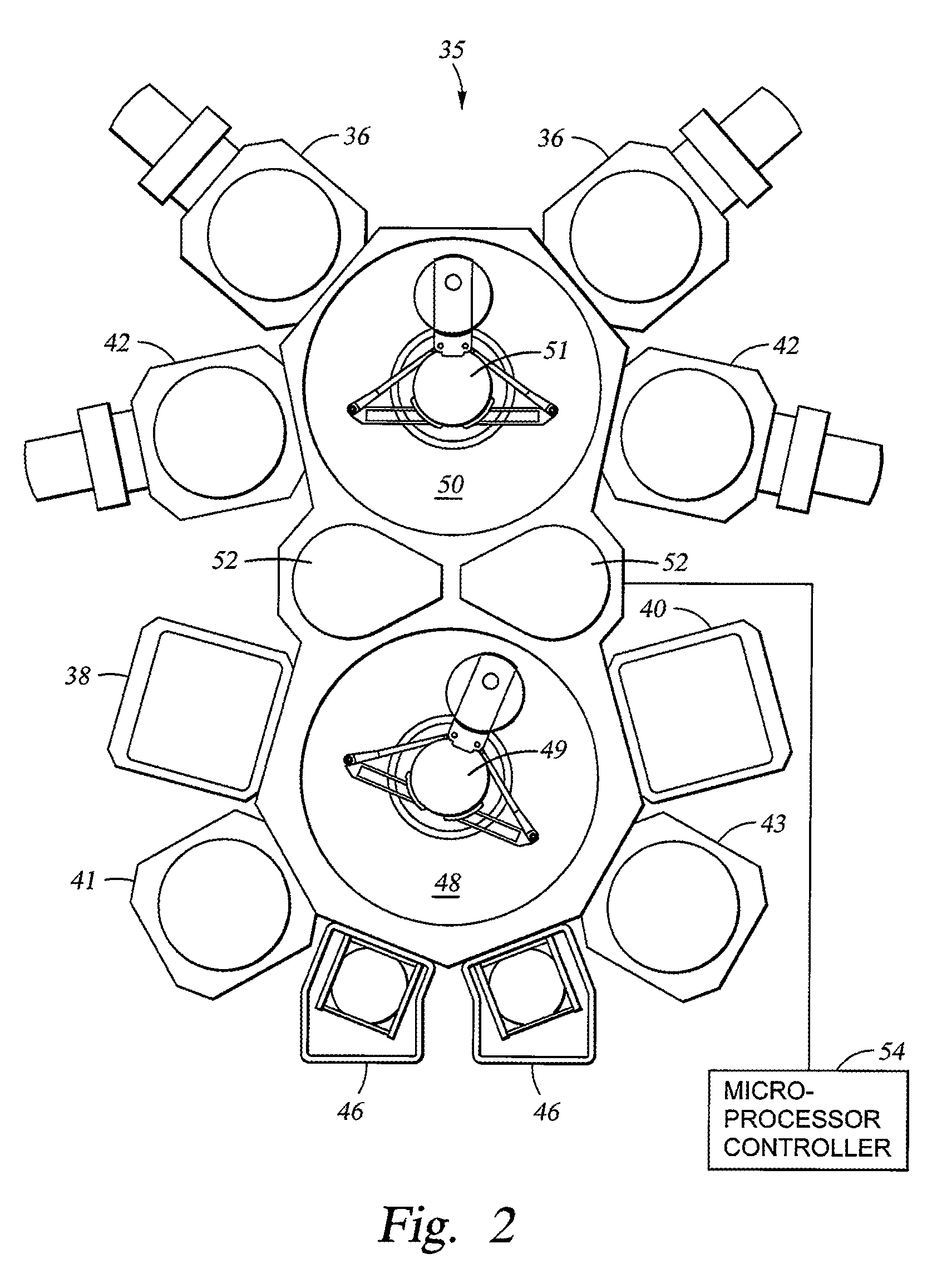

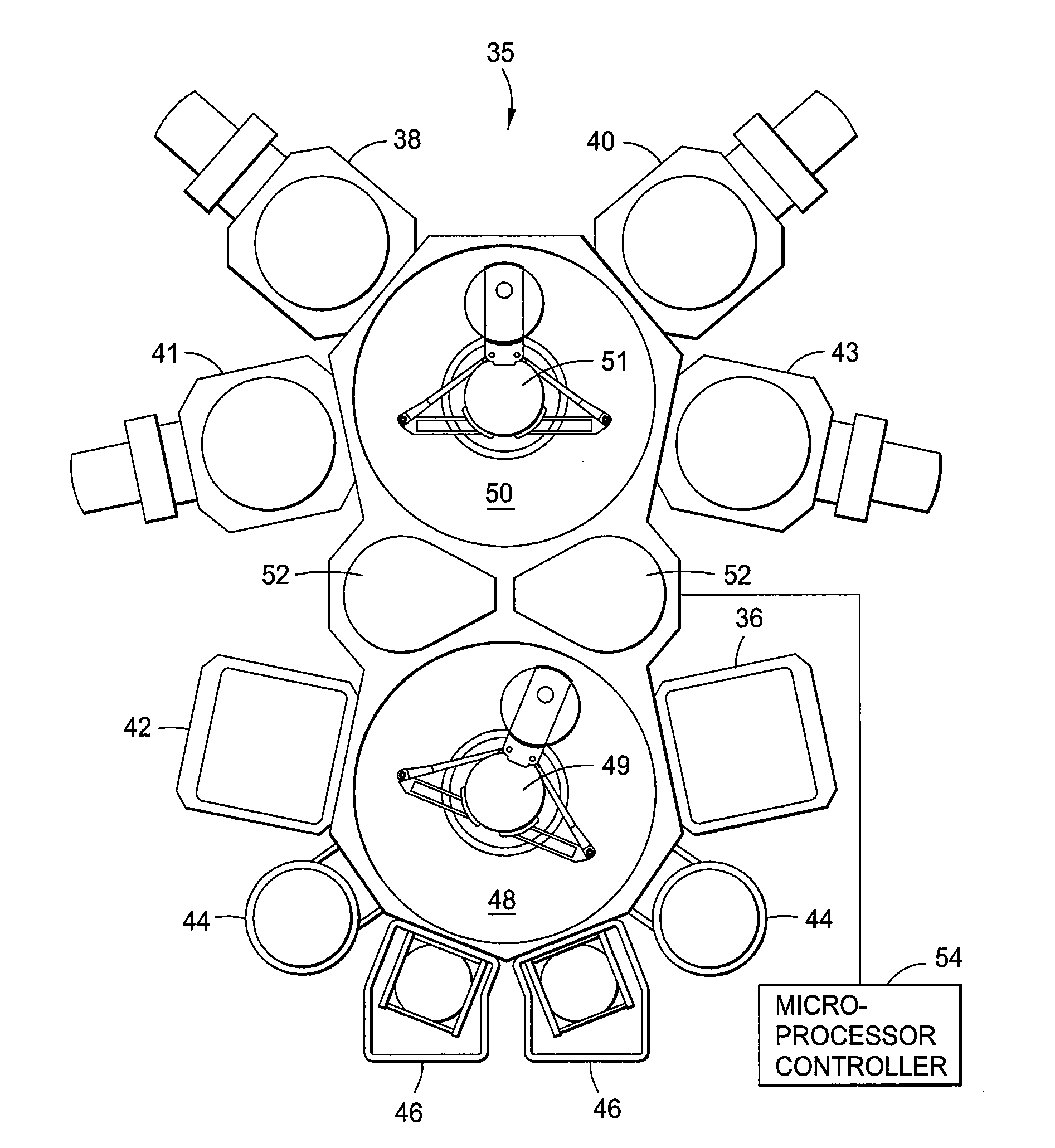

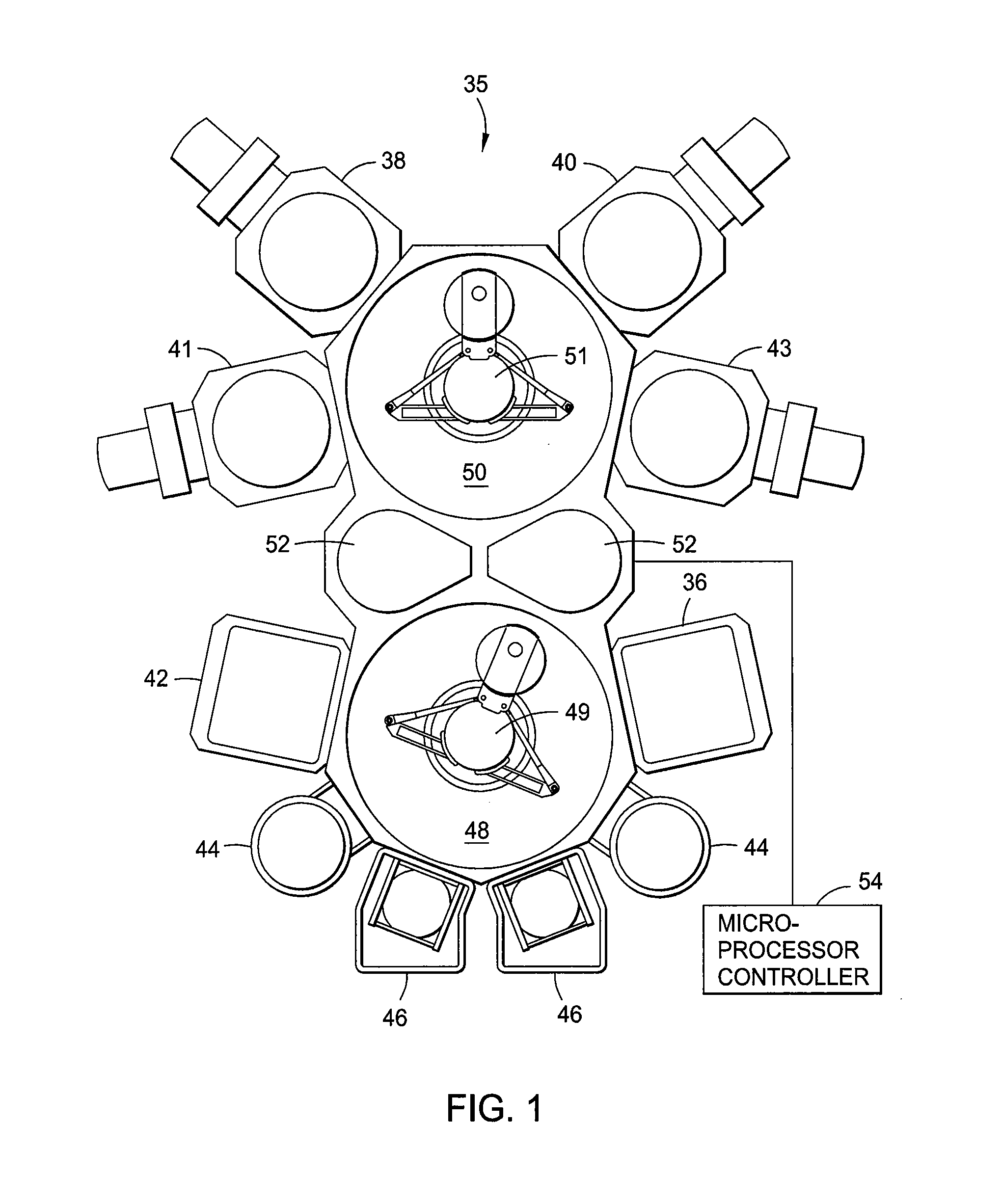

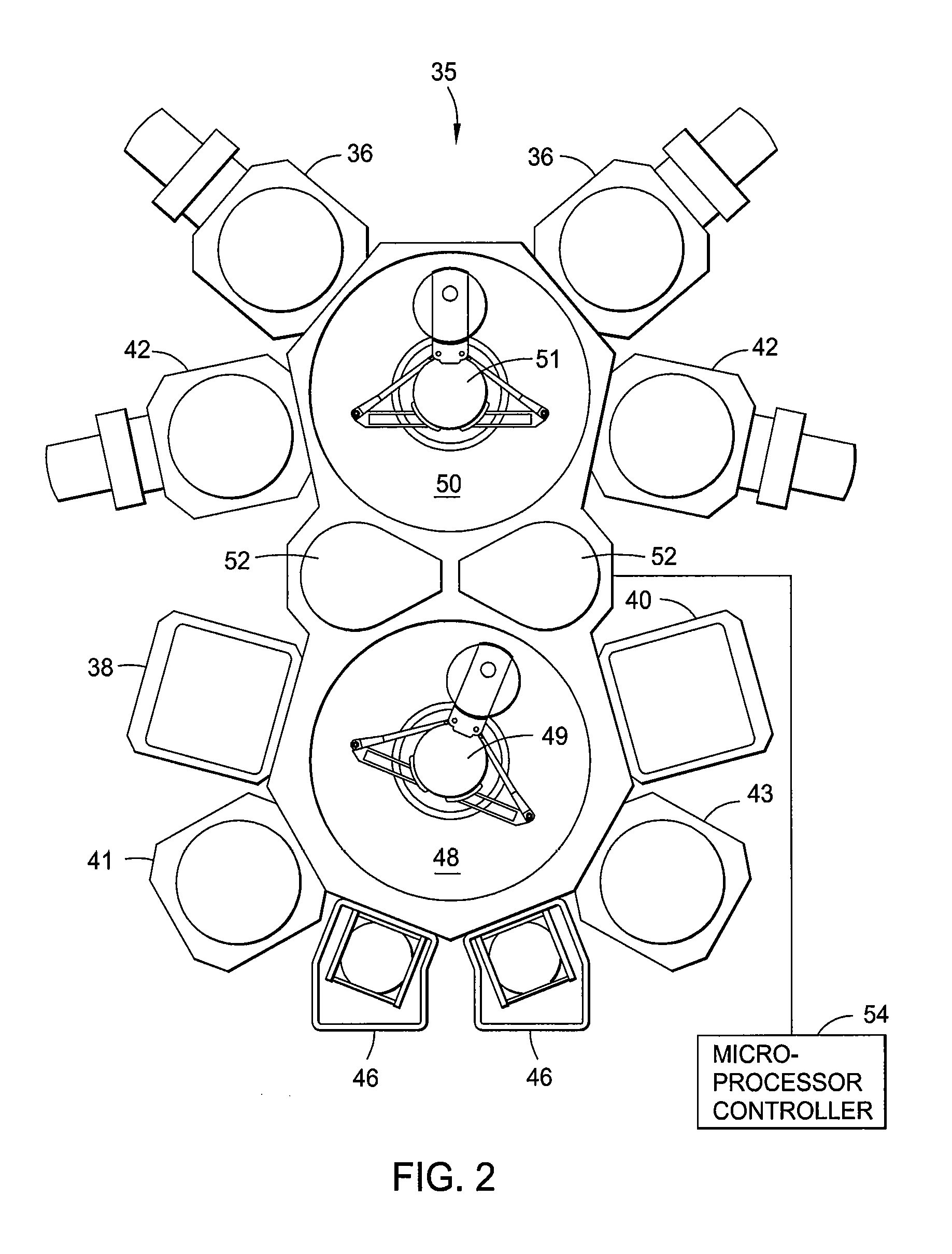

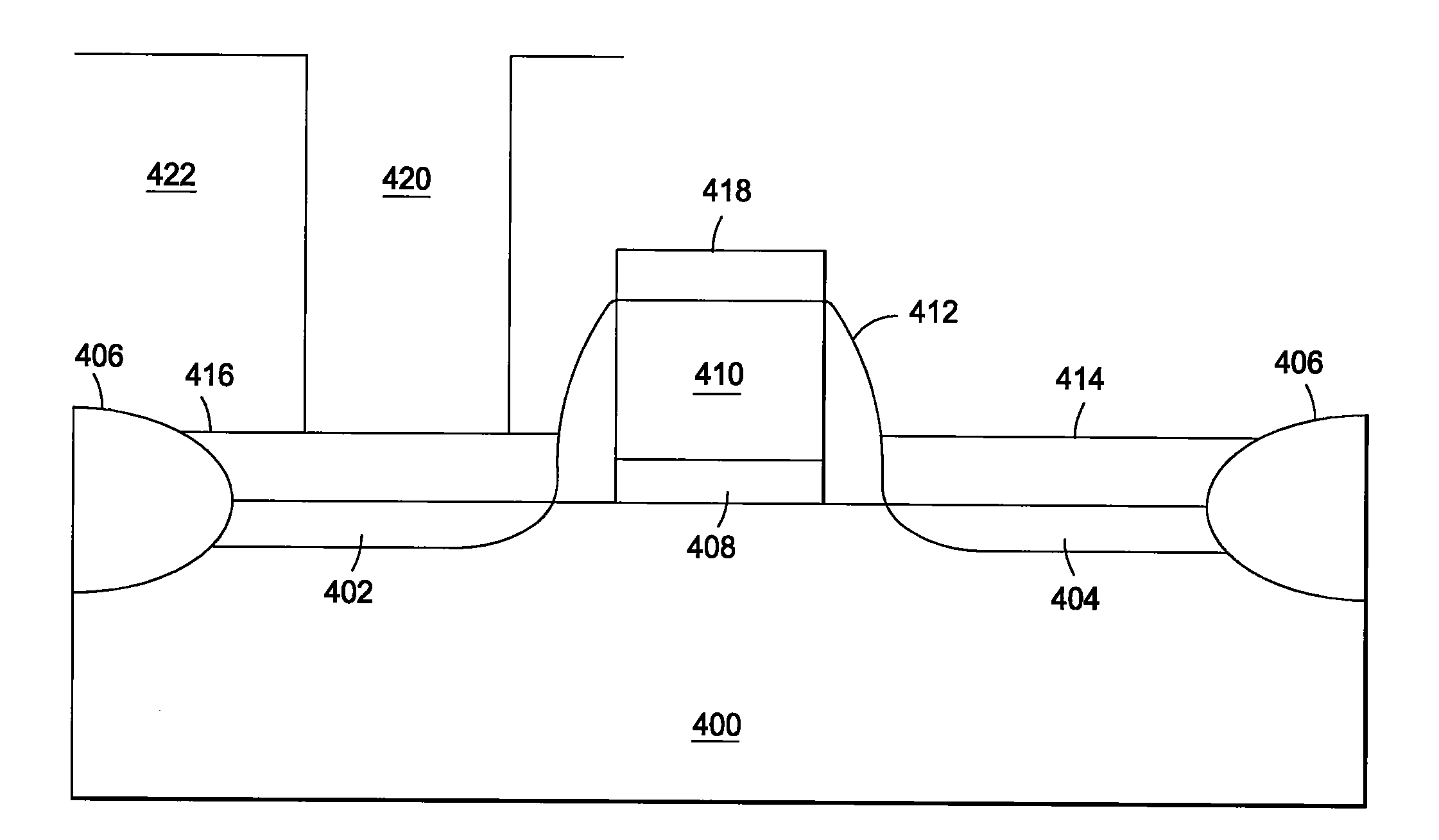

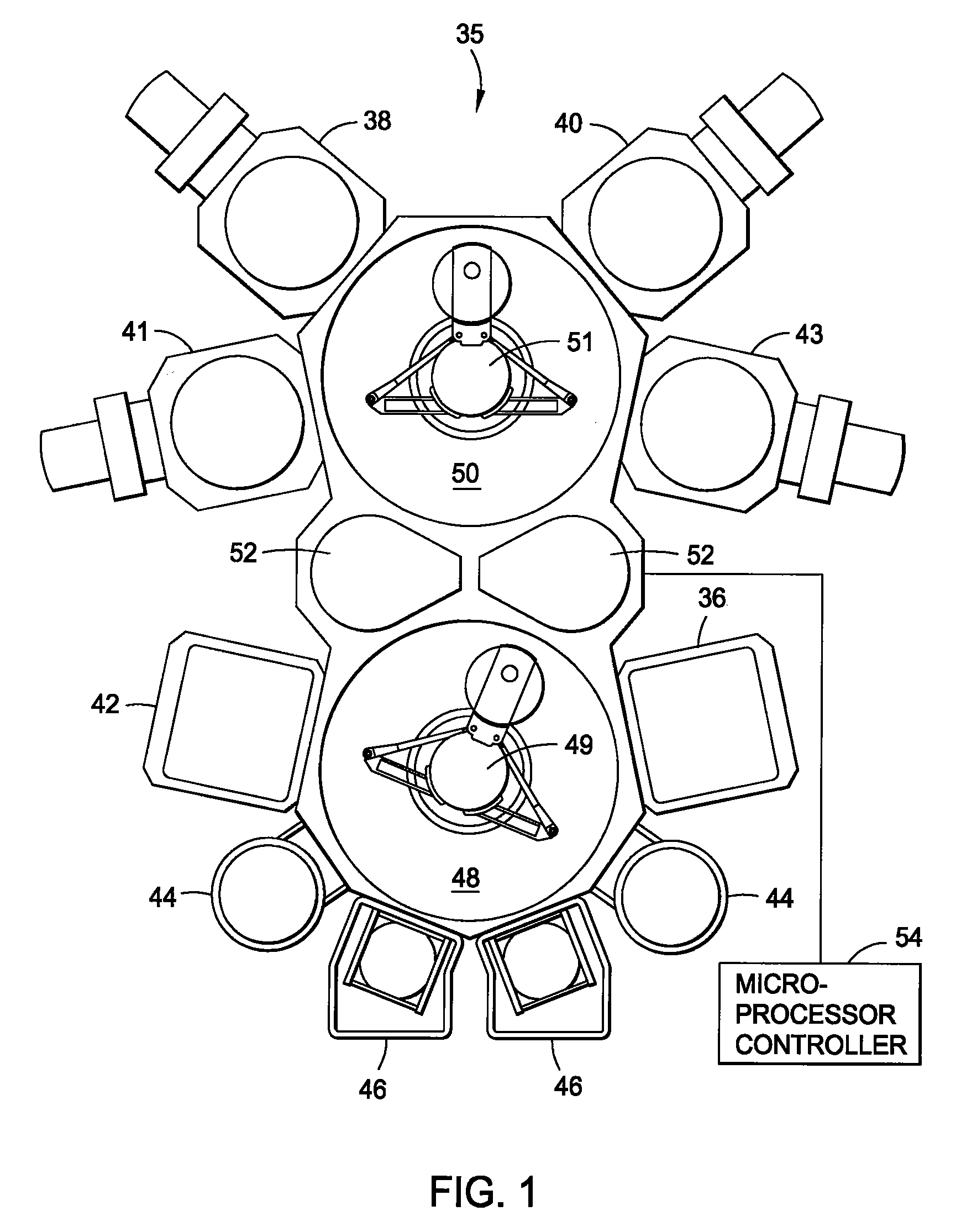

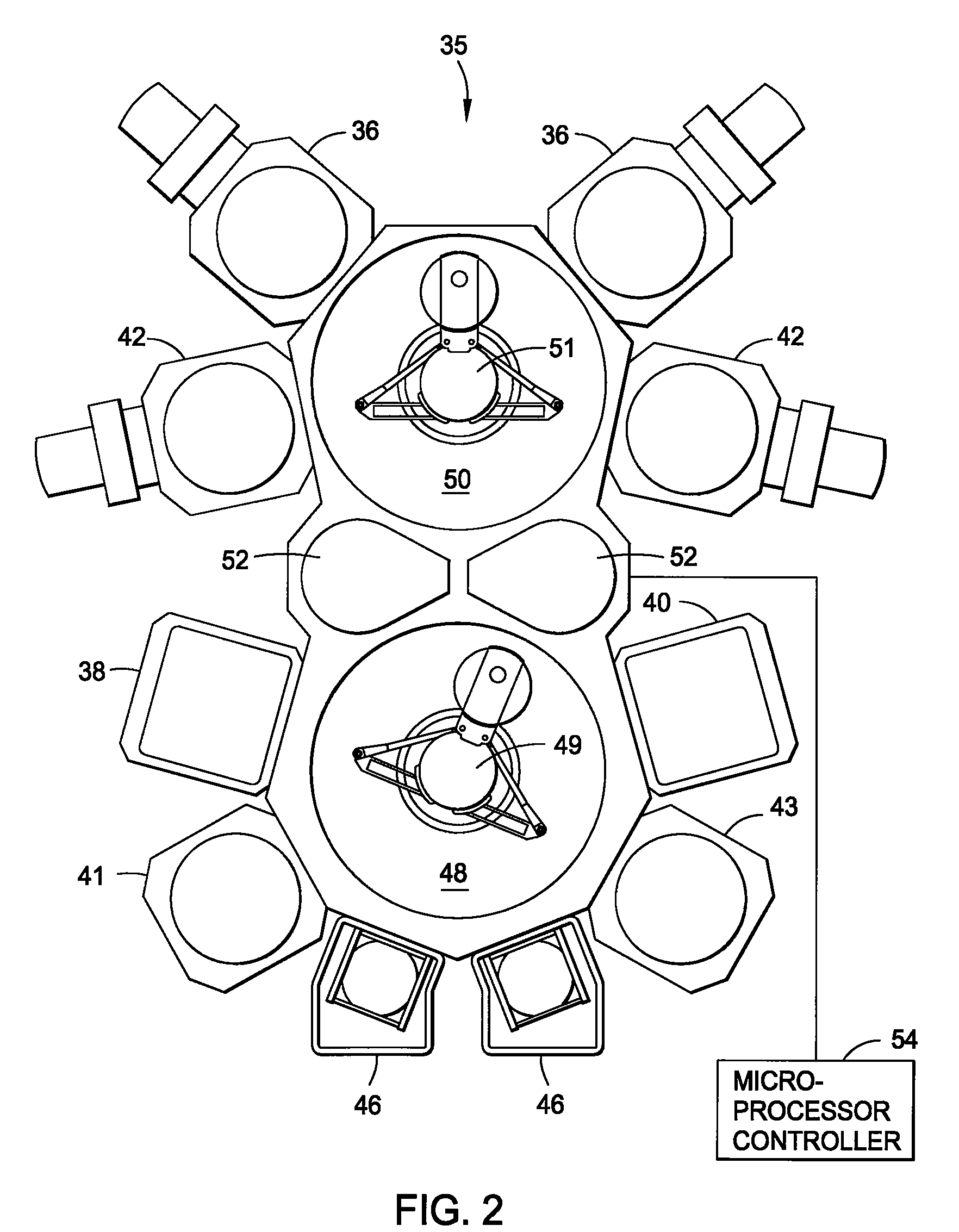

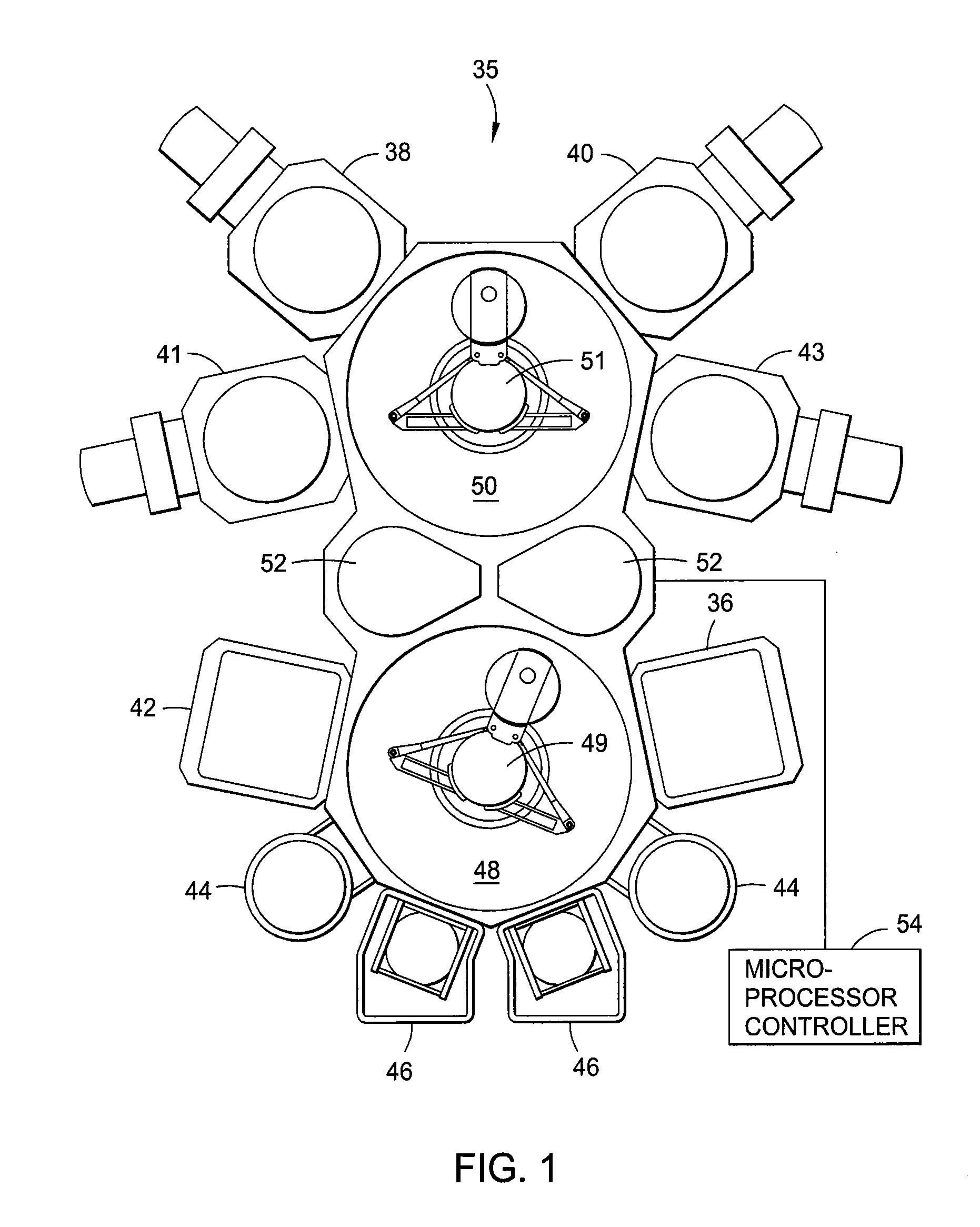

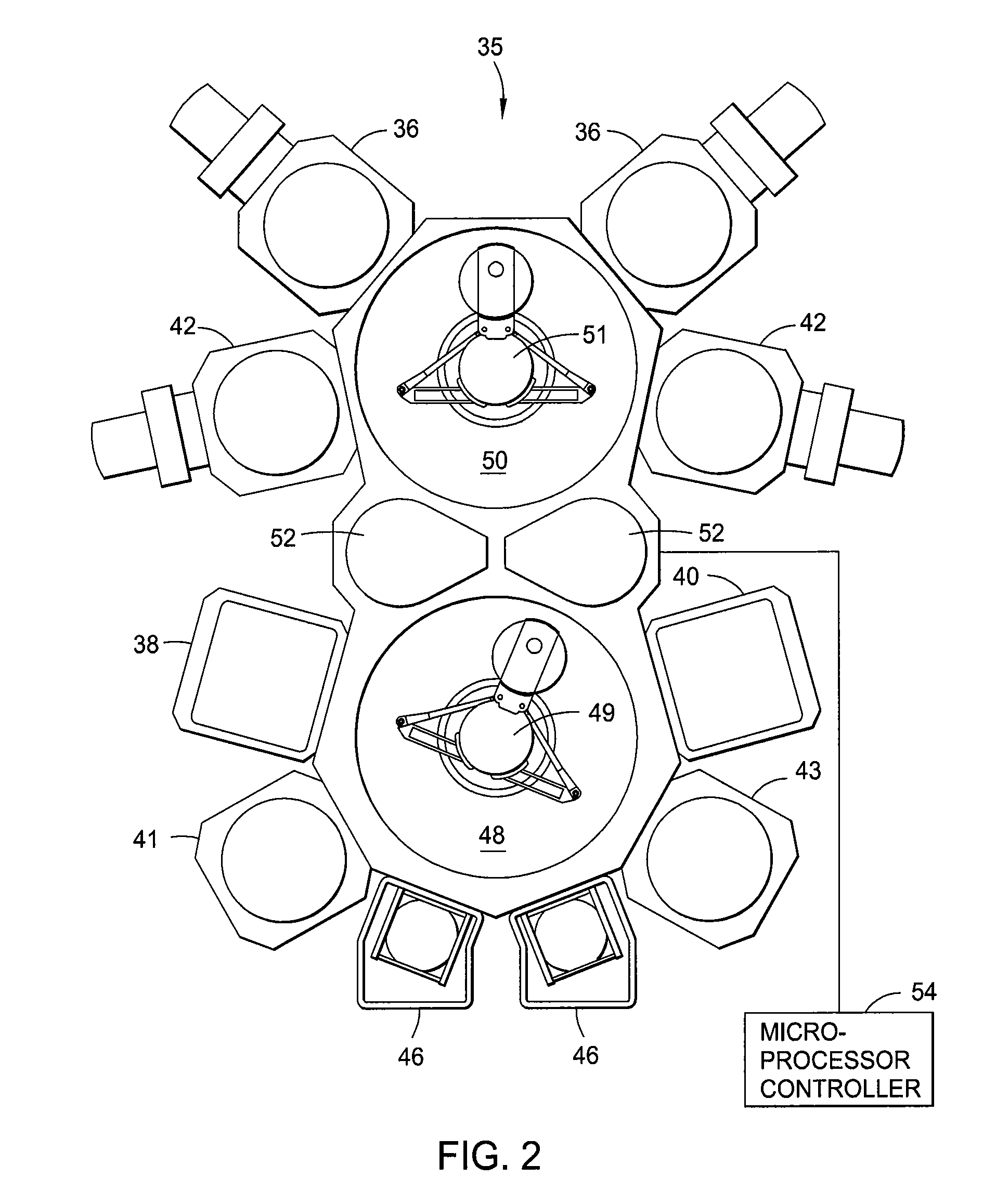

Embodiments of the invention described herein generally provide methods and apparatuses for forming cobalt silicide layers, metallic cobalt layers, and other cobalt-containing materials. In one embodiment, a method for forming a cobalt silicide containing material on a substrate is provided which includes exposing a substrate to at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material on the silicon-containing surface, depositing a metallic cobalt material on the cobalt silicide material, and depositing a metallic contact material on the substrate. In another embodiment, a method includes exposing a substrate to at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material on the silicon-containing surface, expose the substrate to an annealing process, depositing a barrier material on the cobalt silicide material, and depositing a metallic contact material on the barrier material.

Owner:APPLIED MATERIALS INC

Process for forming cobalt-containing materials

InactiveUS20110124192A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingCobaltCobalt silicide

Embodiments of the invention described herein generally provide methods and apparatuses for forming cobalt silicide layers, metallic cobalt layers, and other cobalt-containing materials. In one embodiment, a method for forming a cobalt silicide containing material on a substrate is provided which includes exposing a substrate to at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material on the silicon-containing surface, depositing a metallic cobalt material on the cobalt silicide material, and depositing a metallic contact material on the substrate. In another embodiment, a method includes exposing a substrate to at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material on the silicon-containing surface, expose the substrate to an annealing process, depositing a barrier material on the cobalt silicide material, and depositing a metallic contact material on the barrier material.

Owner:GANGULI SESHADRI +5

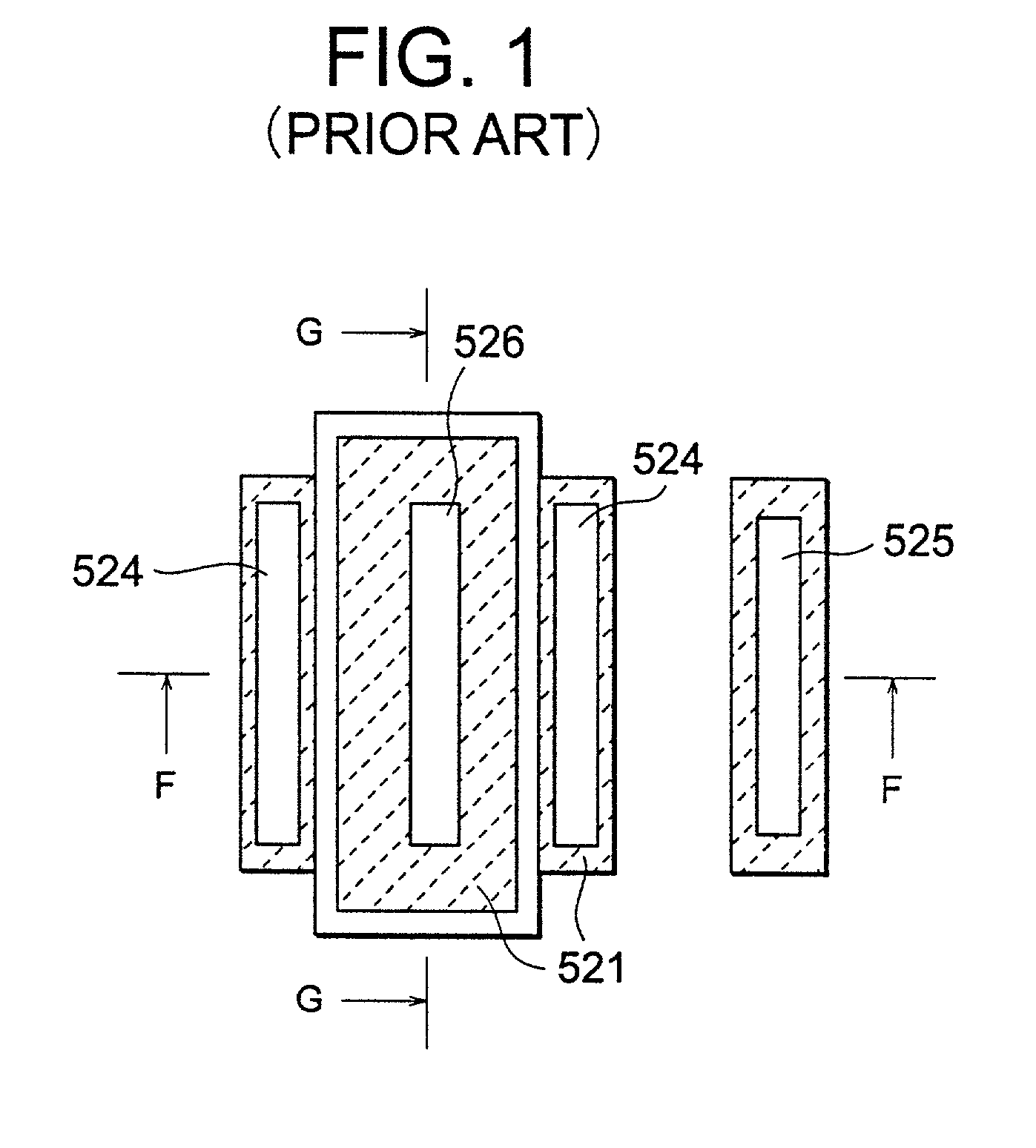

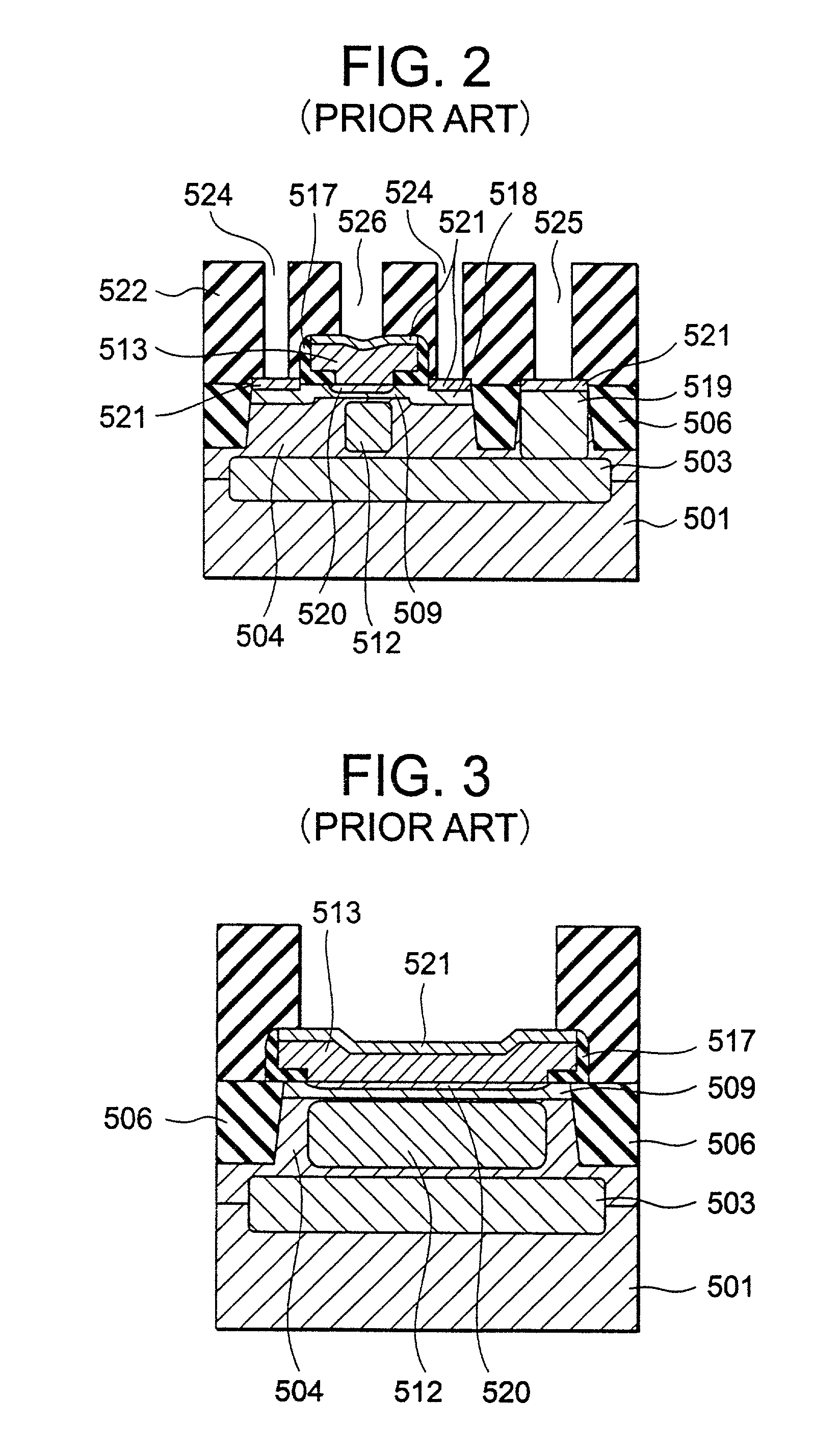

Manufacturing method of semiconductor device

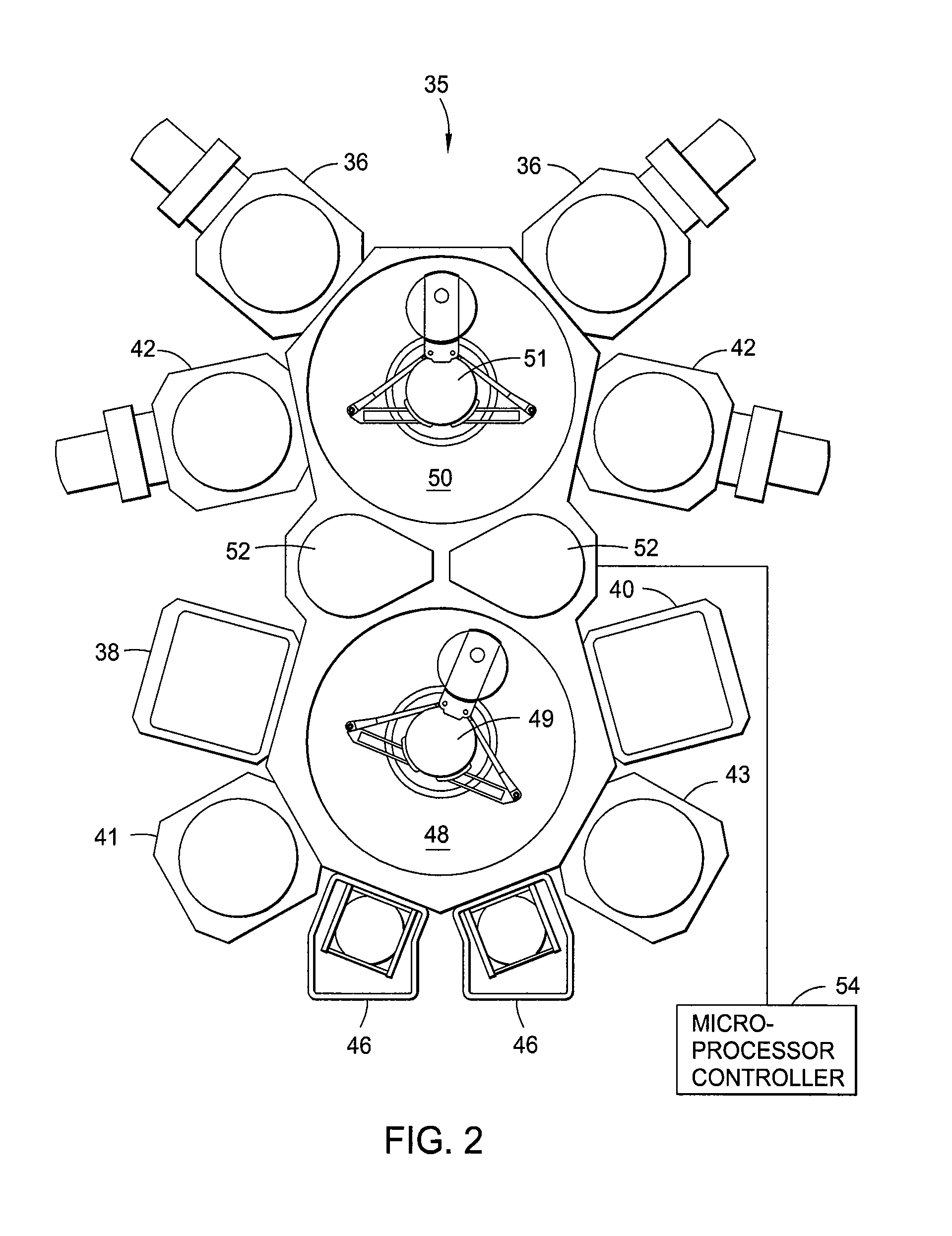

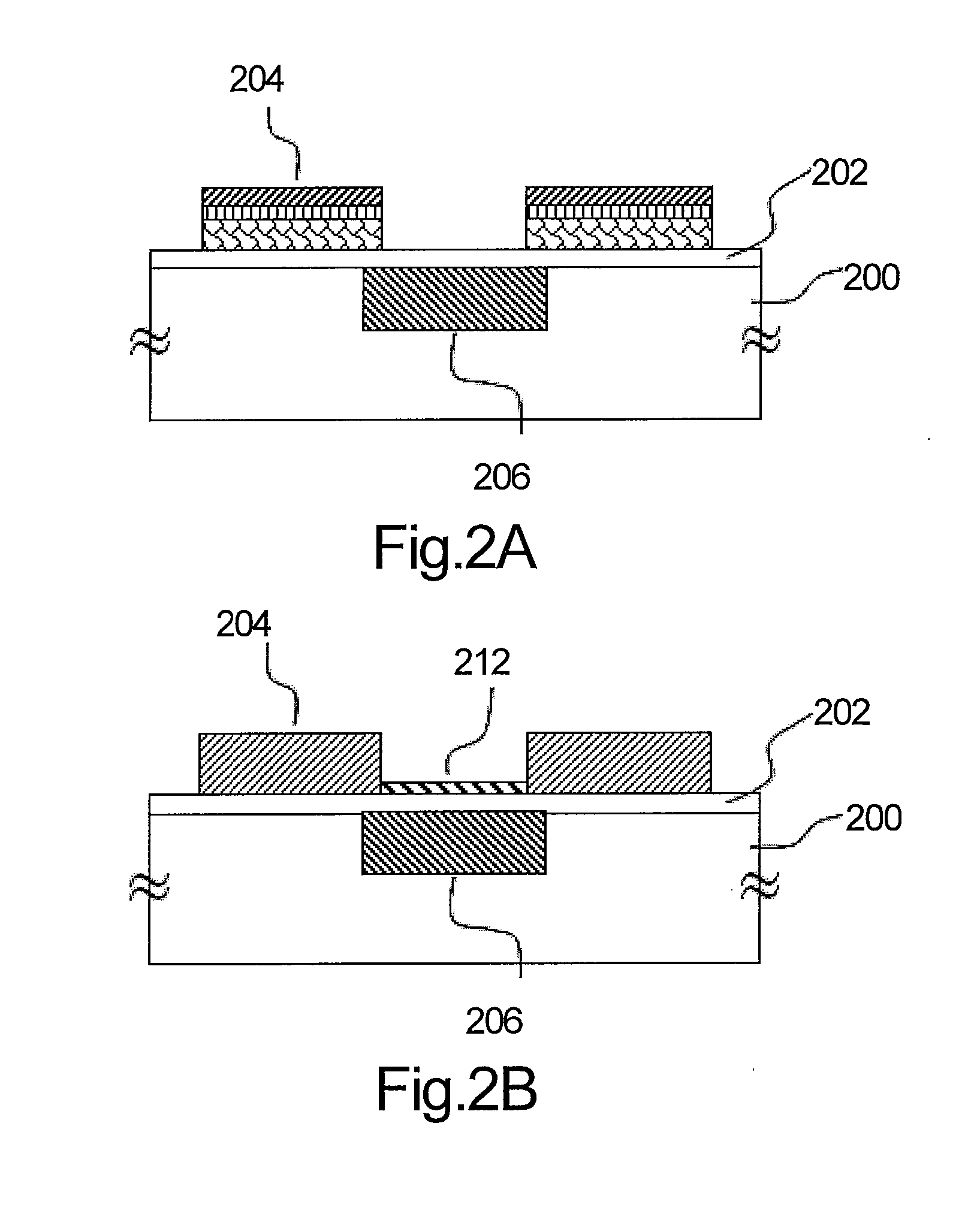

ActiveUS20080081472A1Reduce processing stepsIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesChemical solutionDevice material

A first structure is formed, having a contact plug formed on the bottom of a first opening in an interlayer insulating film, a second opening formed through the interlayer insulating film to reach a semiconductor substrate, and a third opening formed through the interlayer insulating film to reach a polymetal gate electrode. A cobalt layer is deposited on the surface of the structure, and thermally treated to form a cobalt silicide layer on the surface of the contact plug and on the bottom face of the second opening. The structure is then treated to remove the cobalt, in the state in which the cobalt silicide layer is formed, with the use of a chemical solution capable of dissolving cobalt but not the polymetal.

Owner:HEFEI RELIANCE MEMORY LTD

Deposition methods for barrier and tungsten materials

Embodiments are provided for a method to deposit barrier and tungsten materials on a substrate. In one embodiment, a method provides forming a barrier layer on a substrate and exposing the substrate to a silane gas to form a thin silicon-containing layer on the barrier layer during a soak process. The method further provides depositing a tungsten nucleation layer over the barrier layer and the thin silicon-containing layer during an atomic layer deposition process and depositing a tungsten bulk layer on the tungsten nucleation layer during a chemical vapor deposition process. In some examples, the barrier layer contains metallic cobalt and cobalt silicide, or metallic nickel and nickel silicide. In other examples, the barrier layer contains metallic titanium and titanium nitride, or metallic tantalum and tantalum nitride.

Owner:APPLIED MATERIALS INC

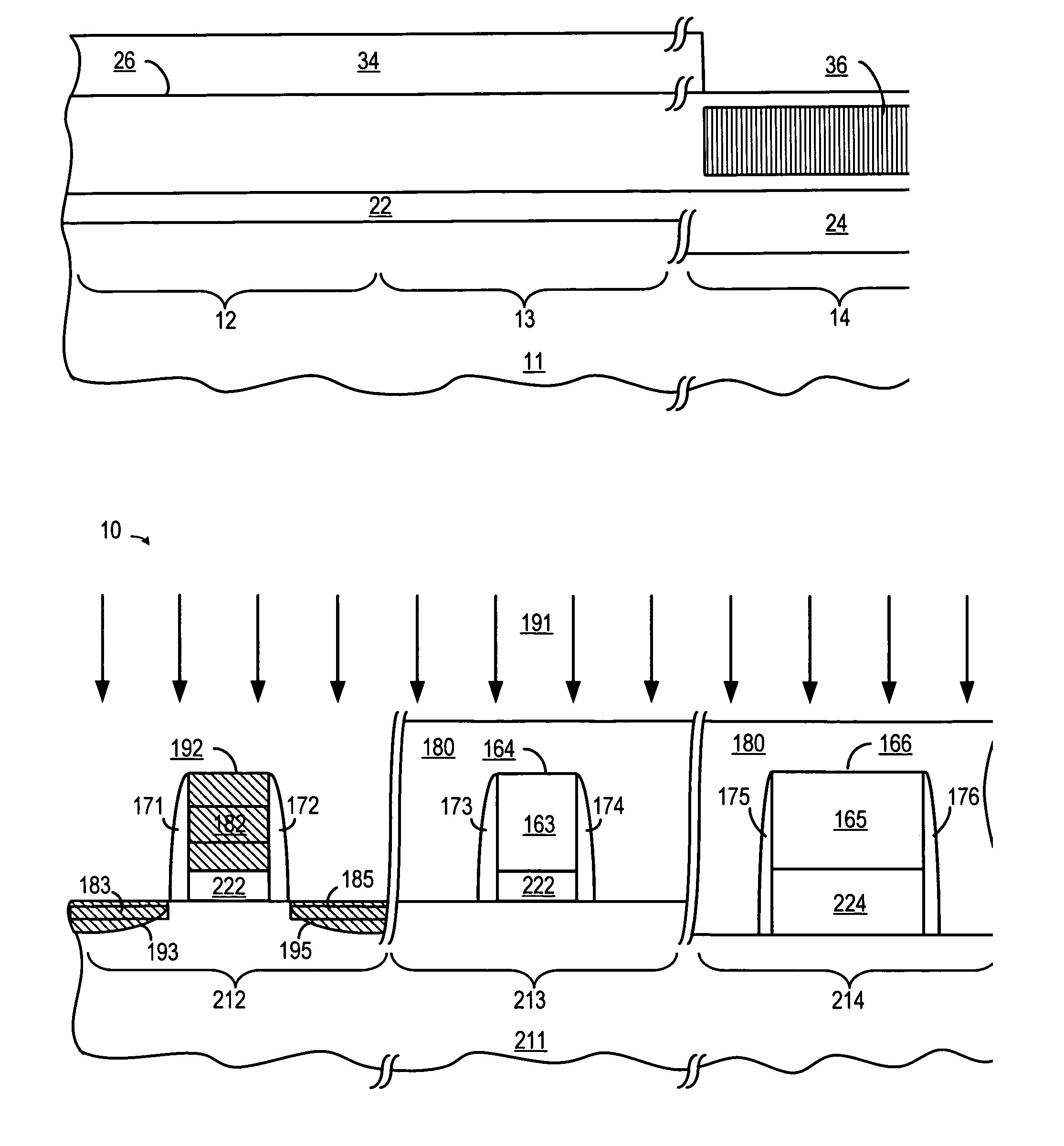

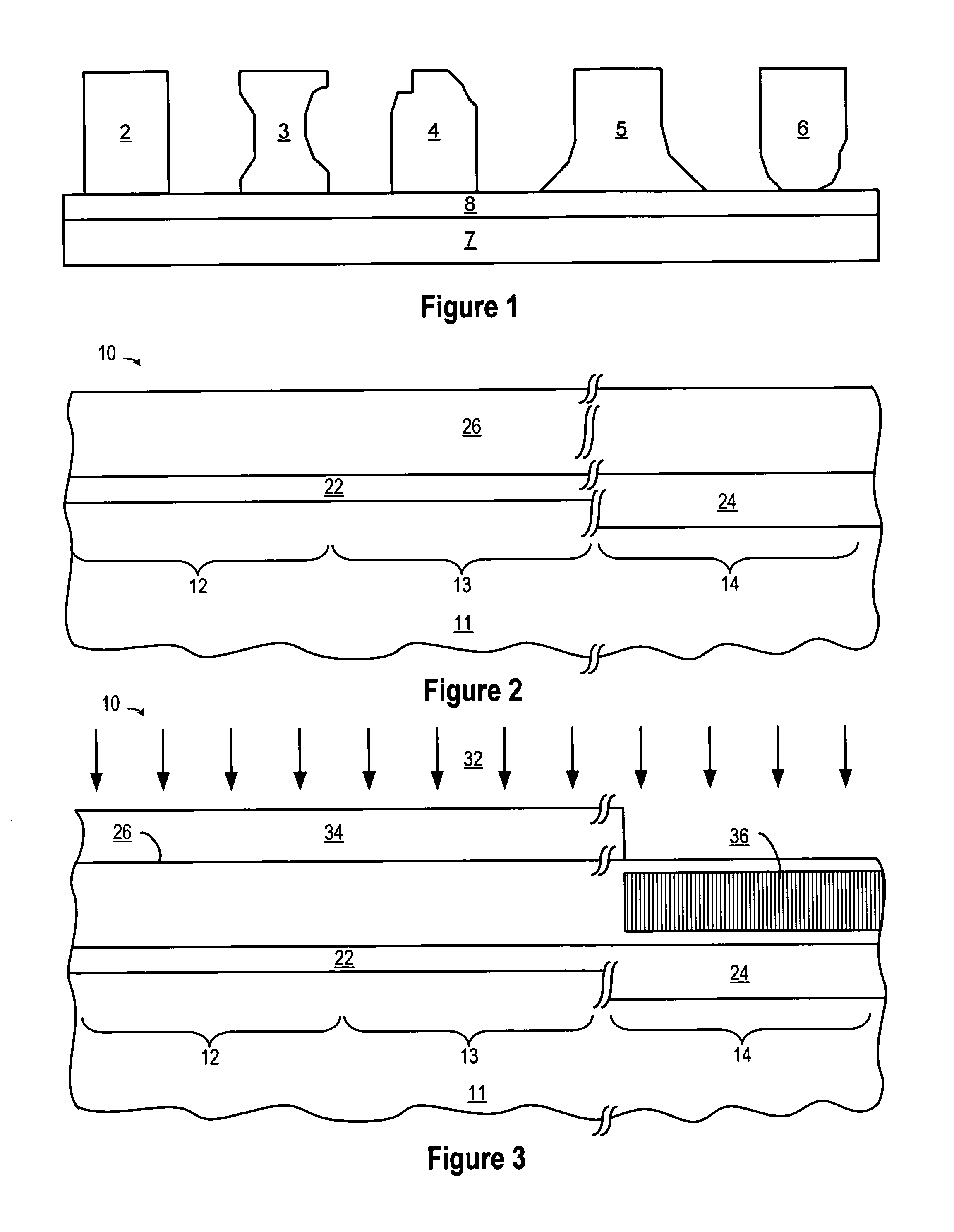

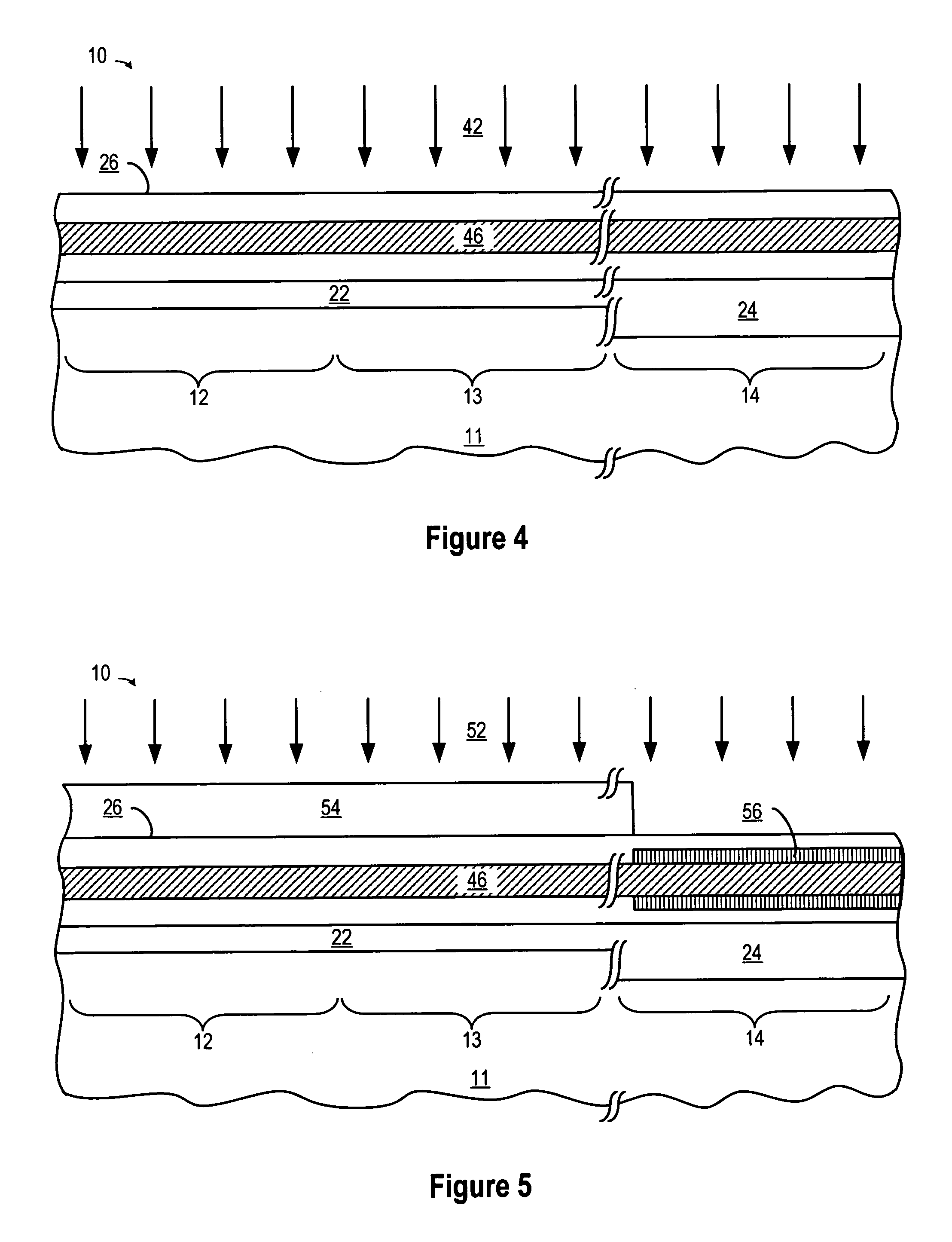

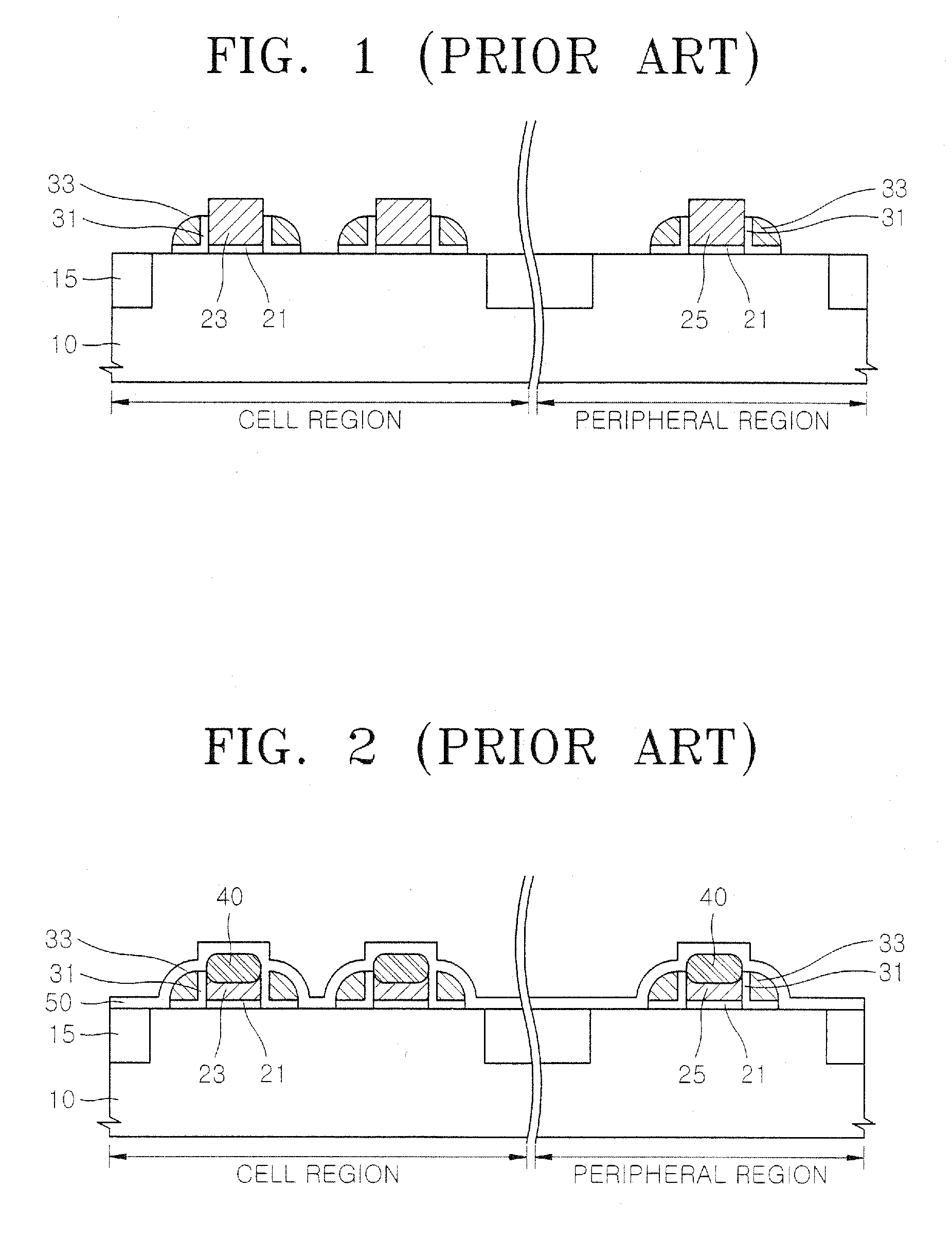

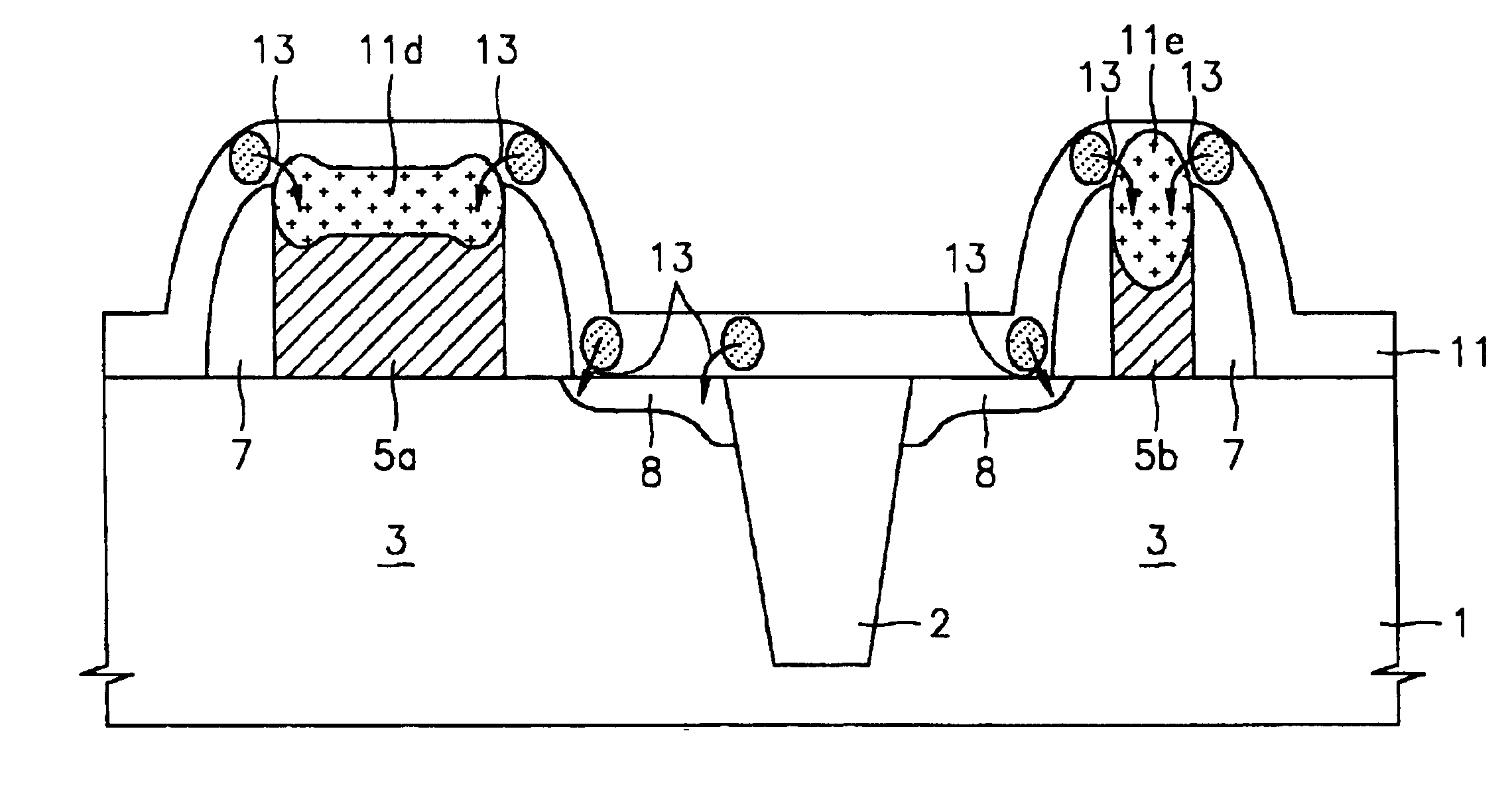

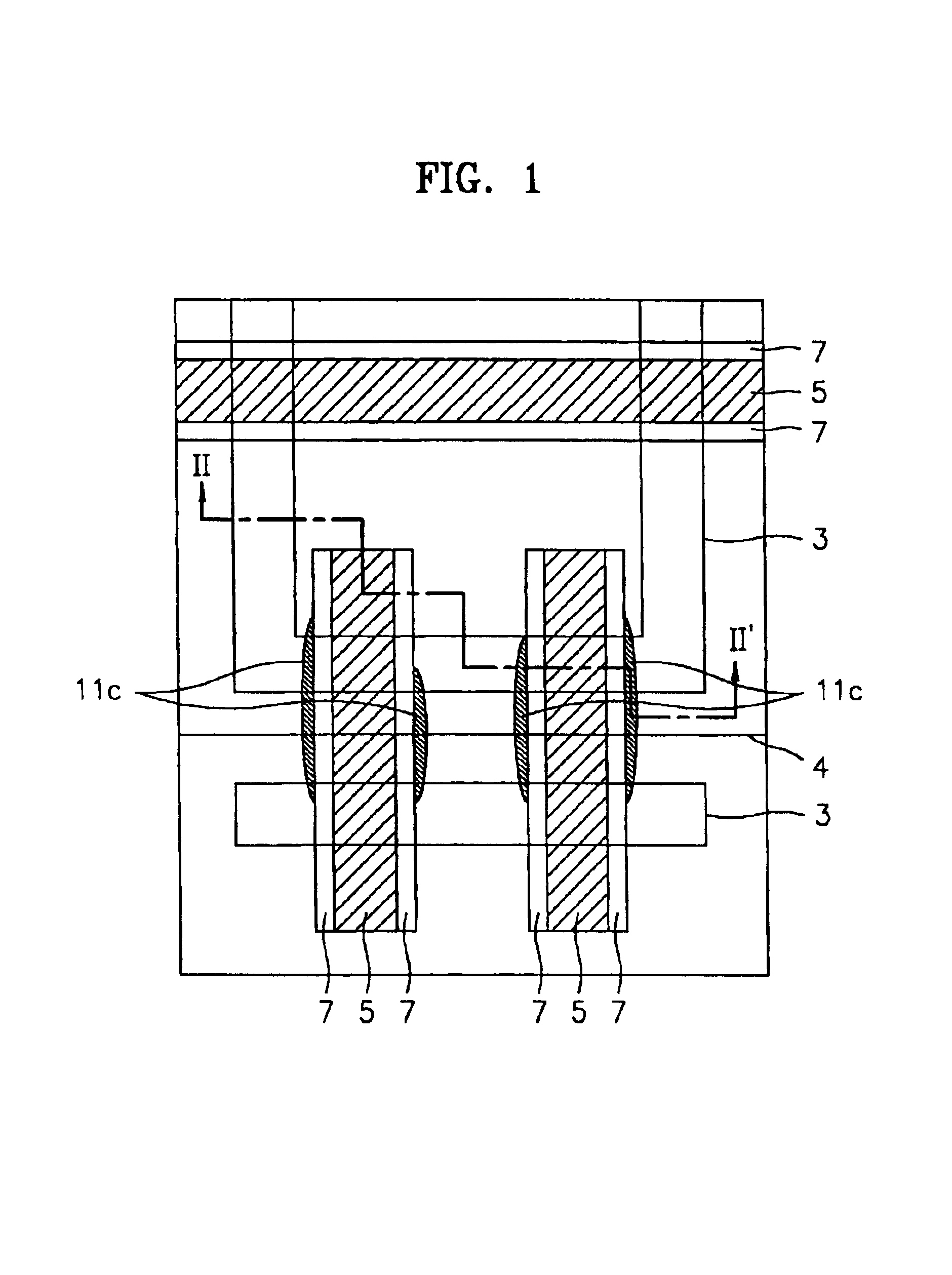

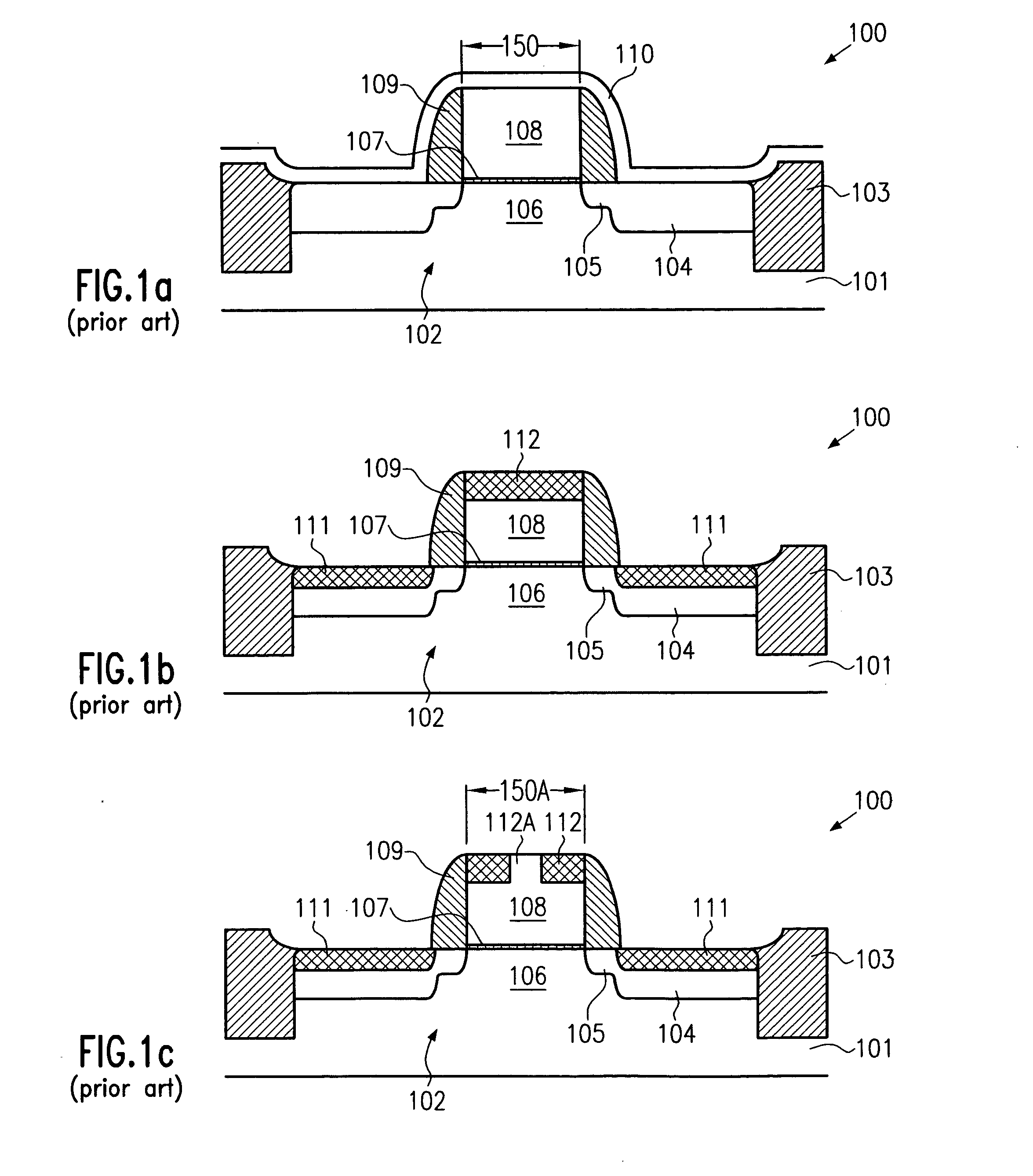

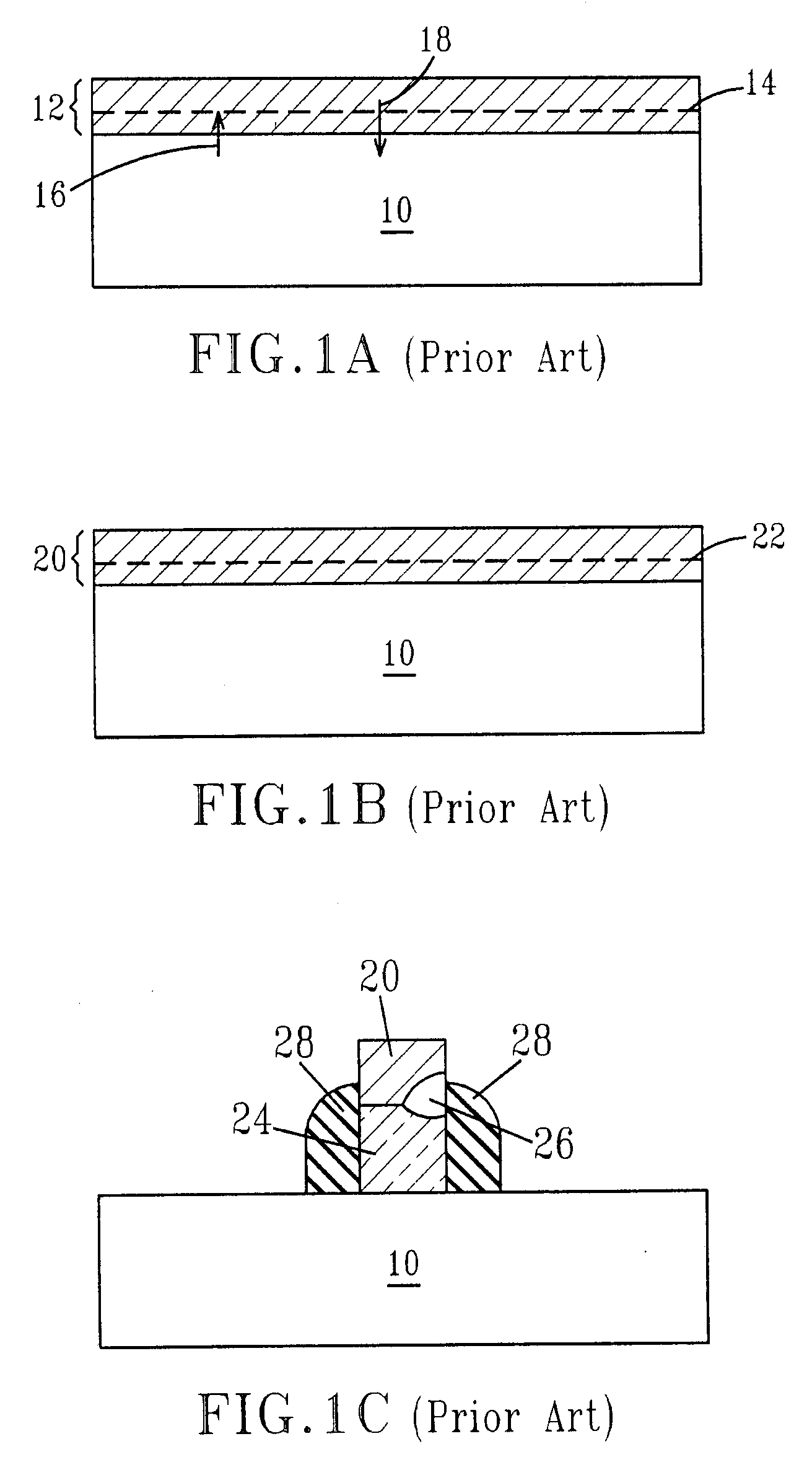

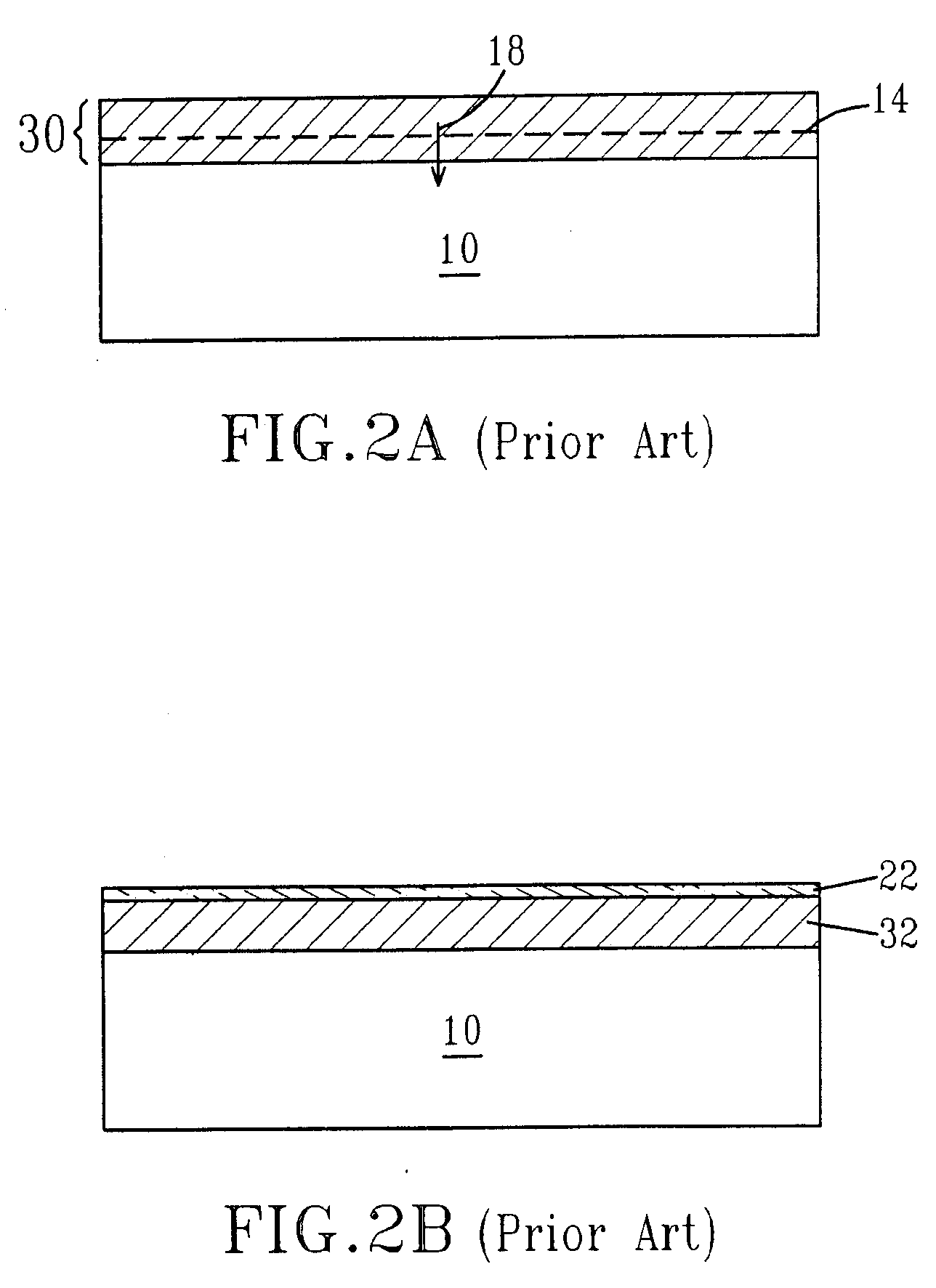

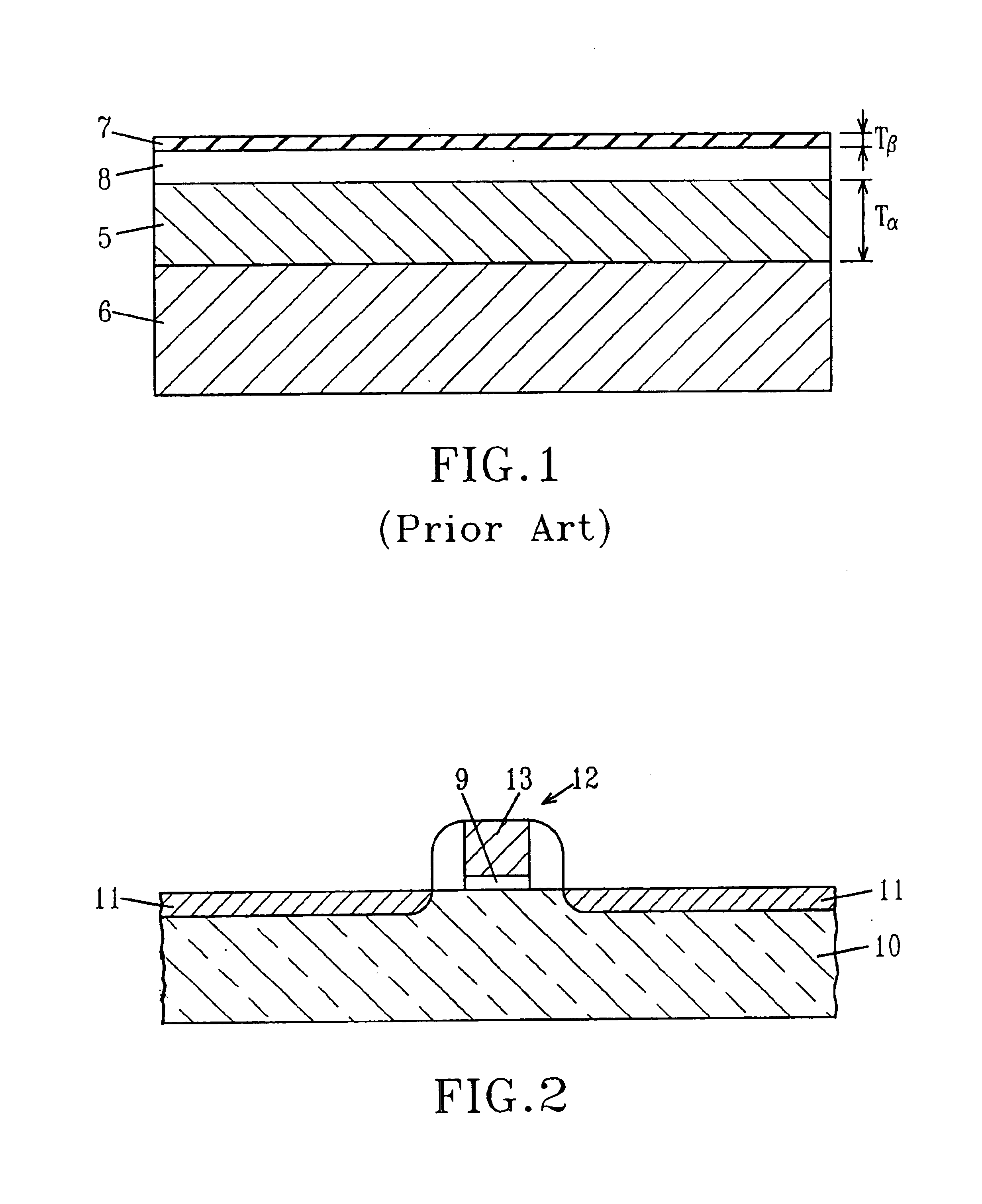

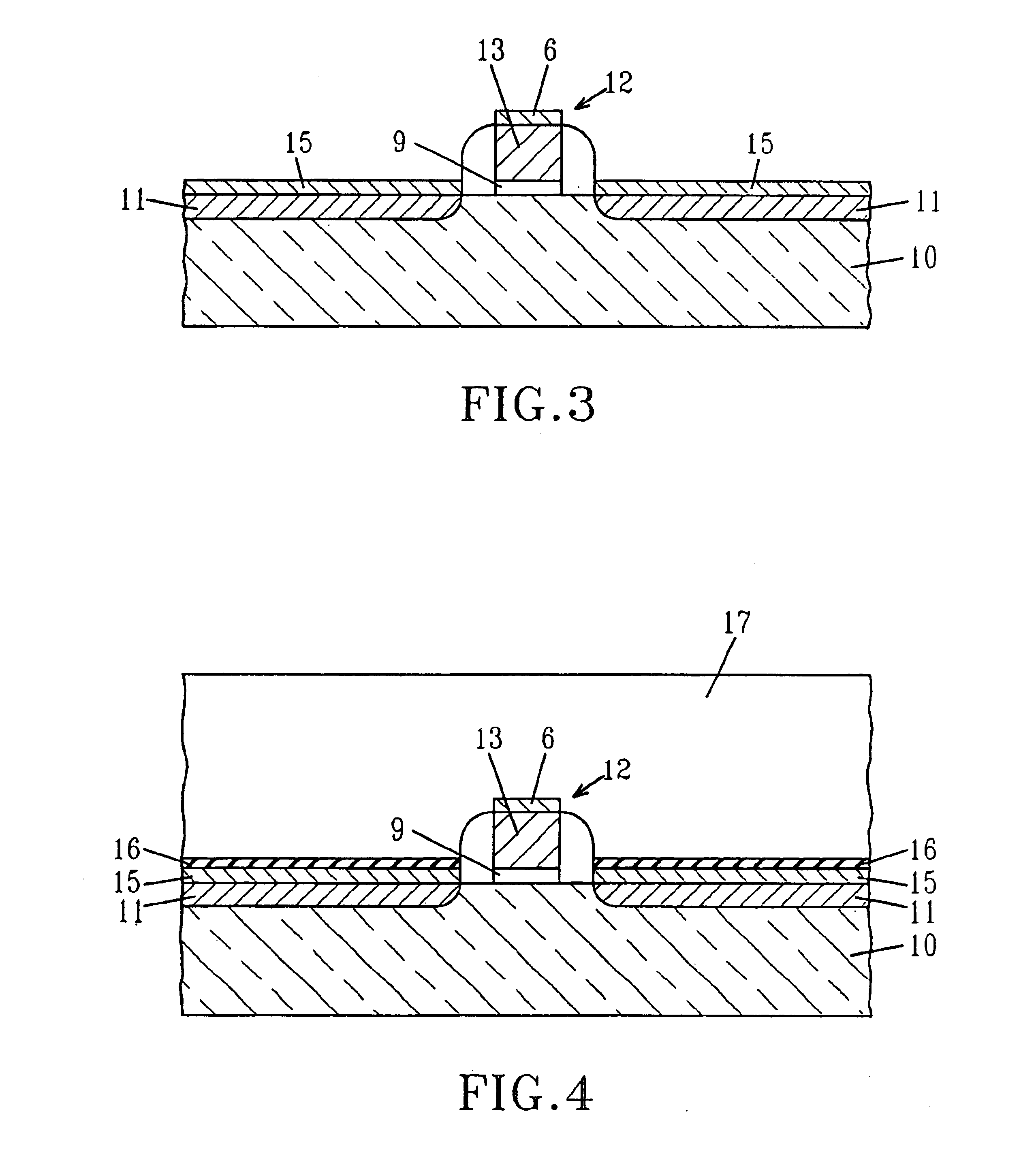

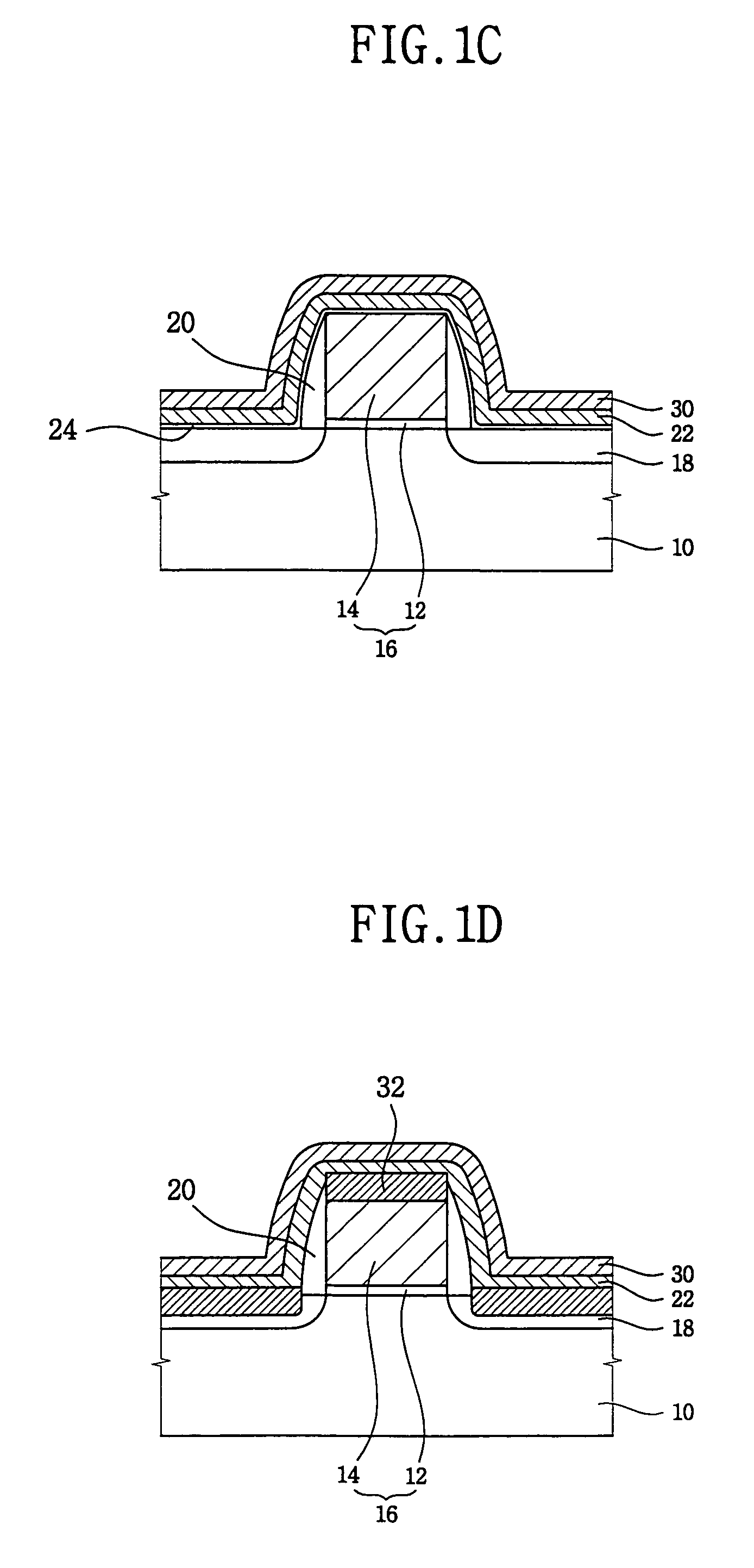

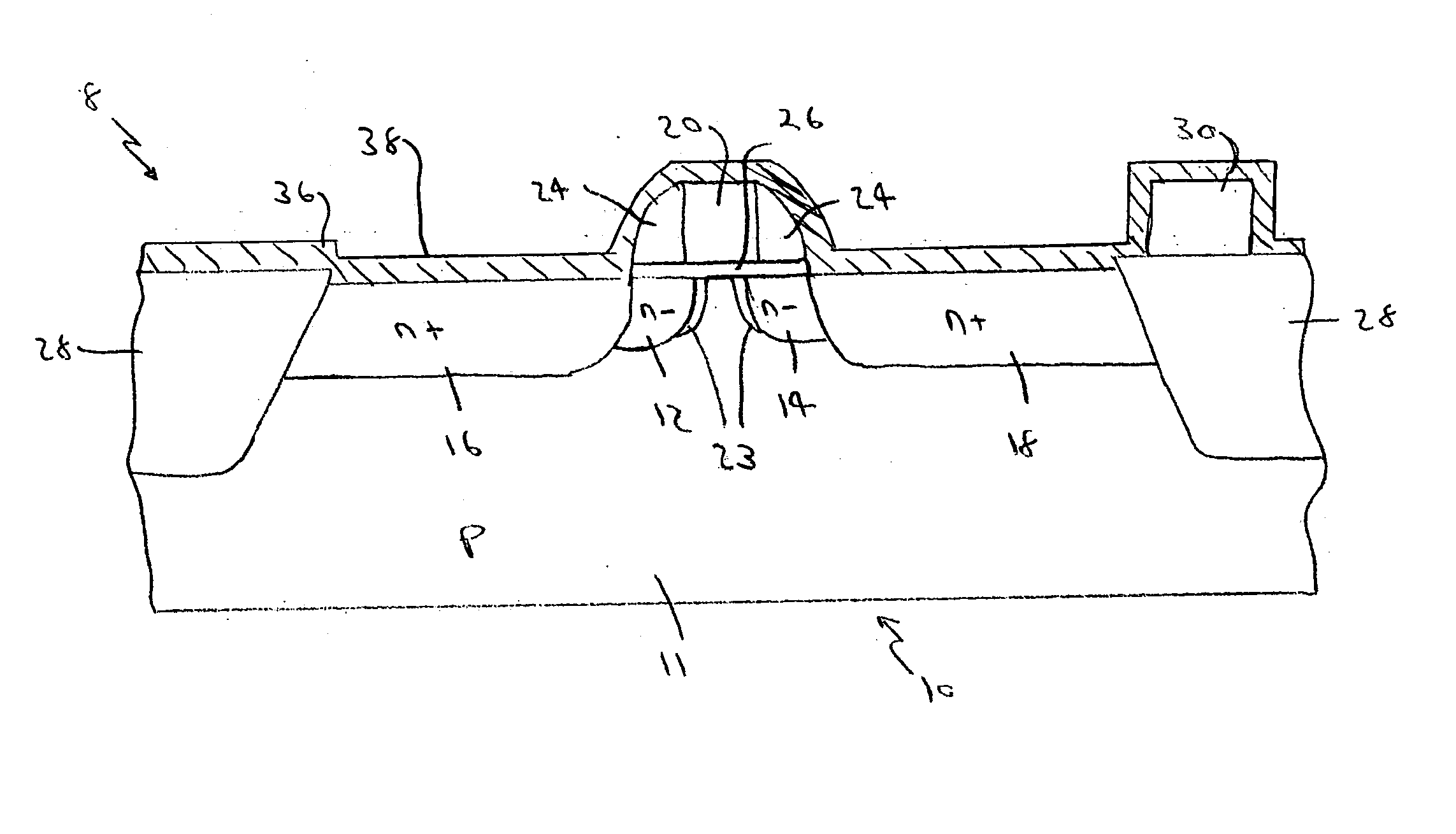

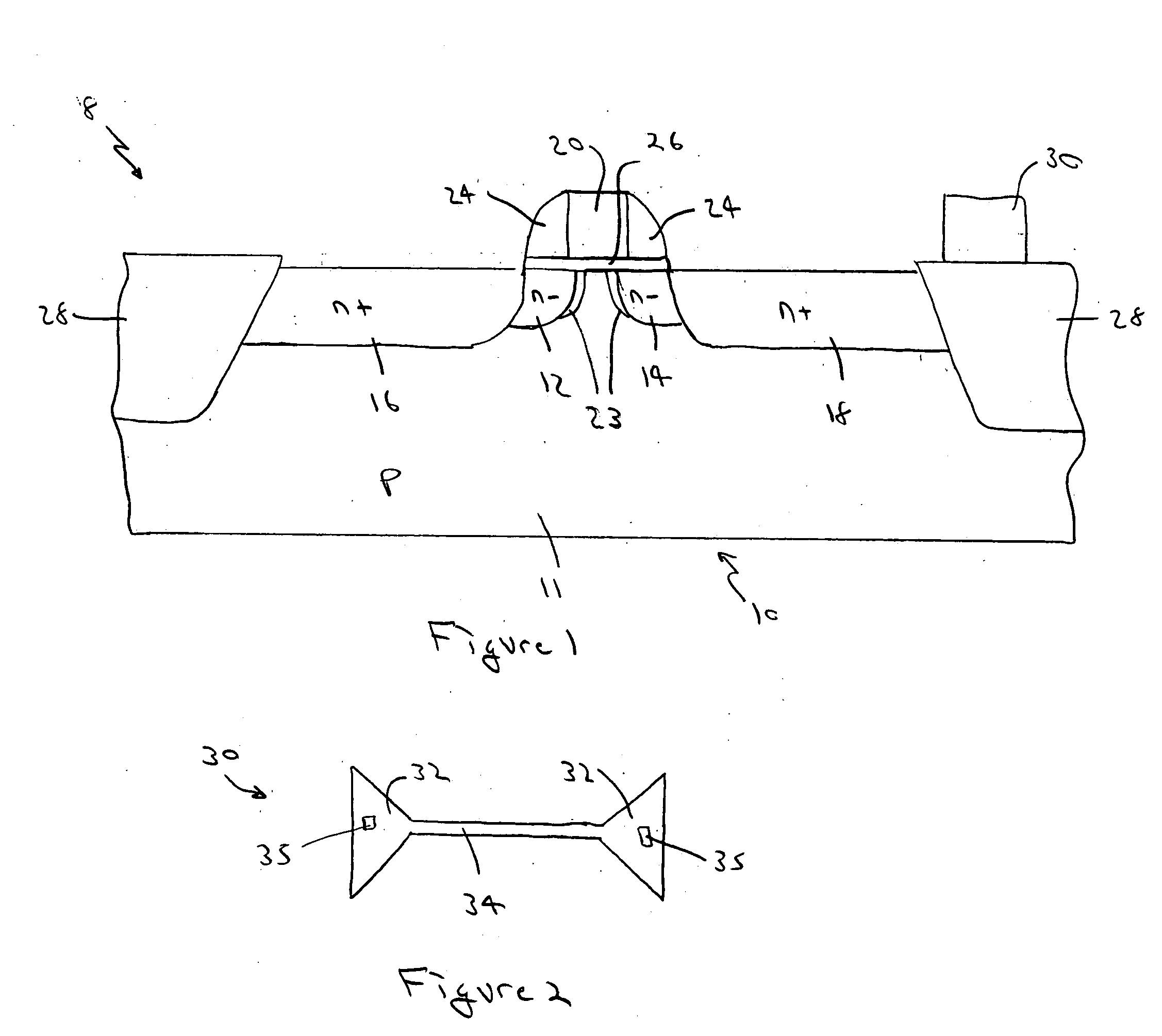

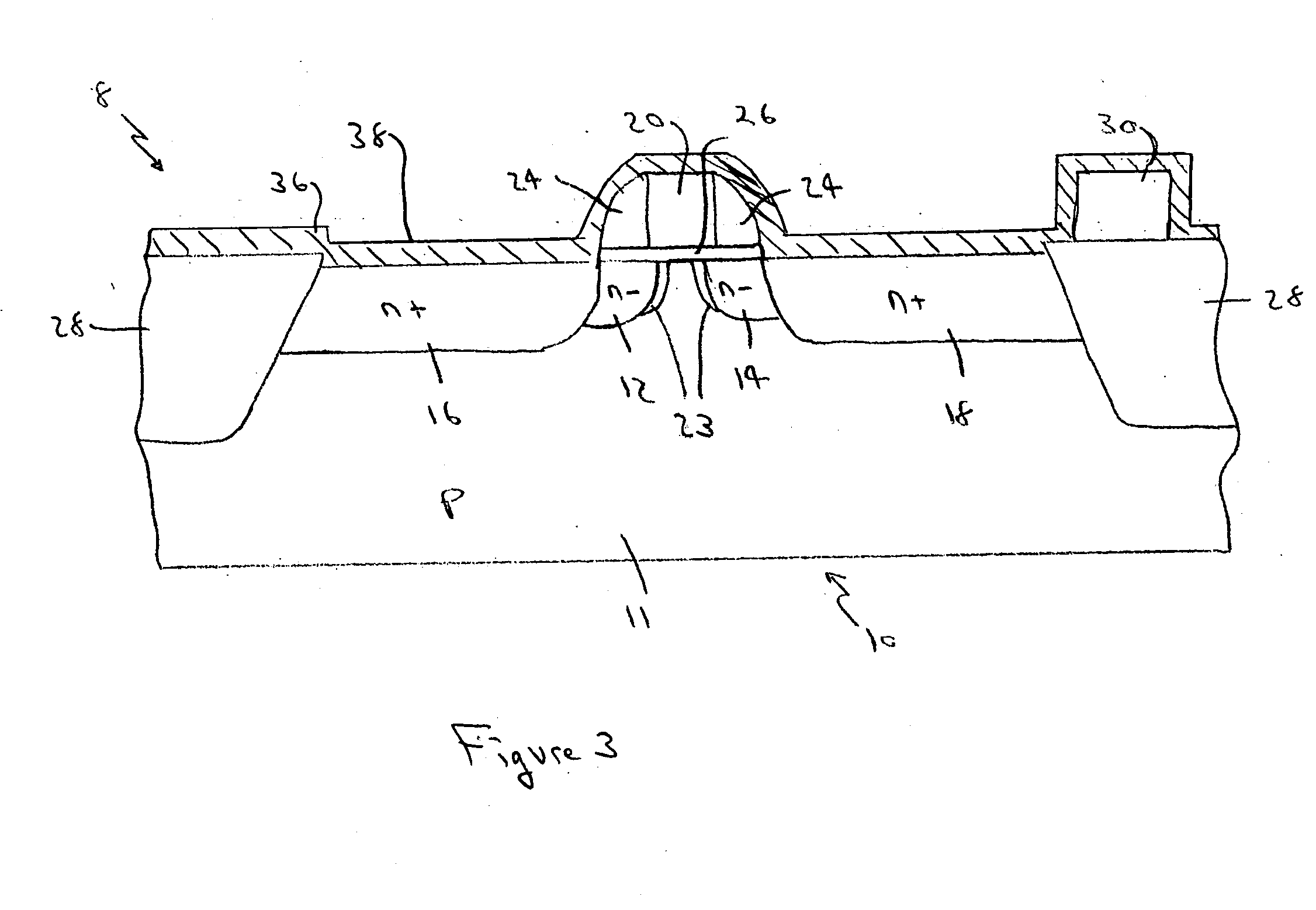

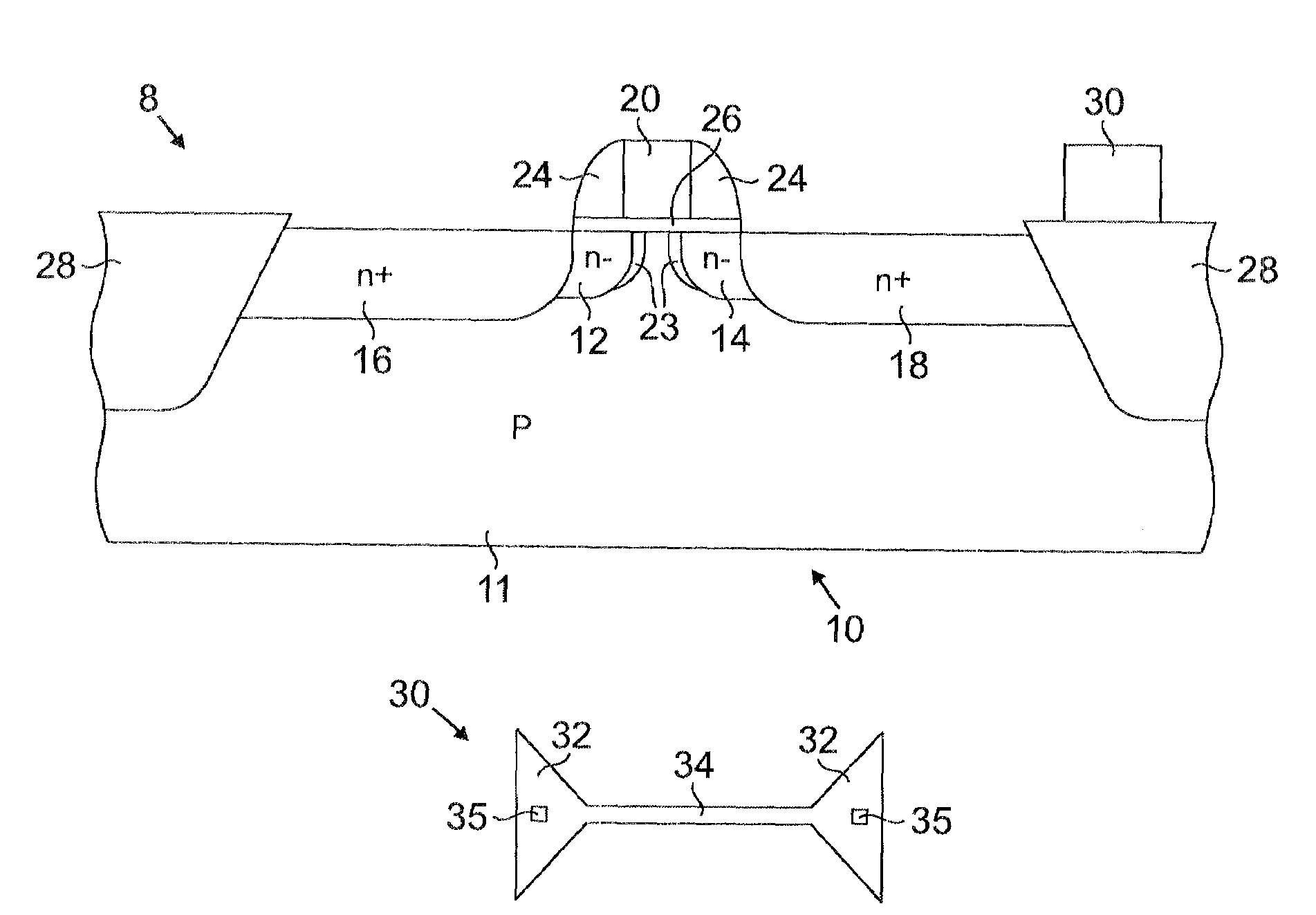

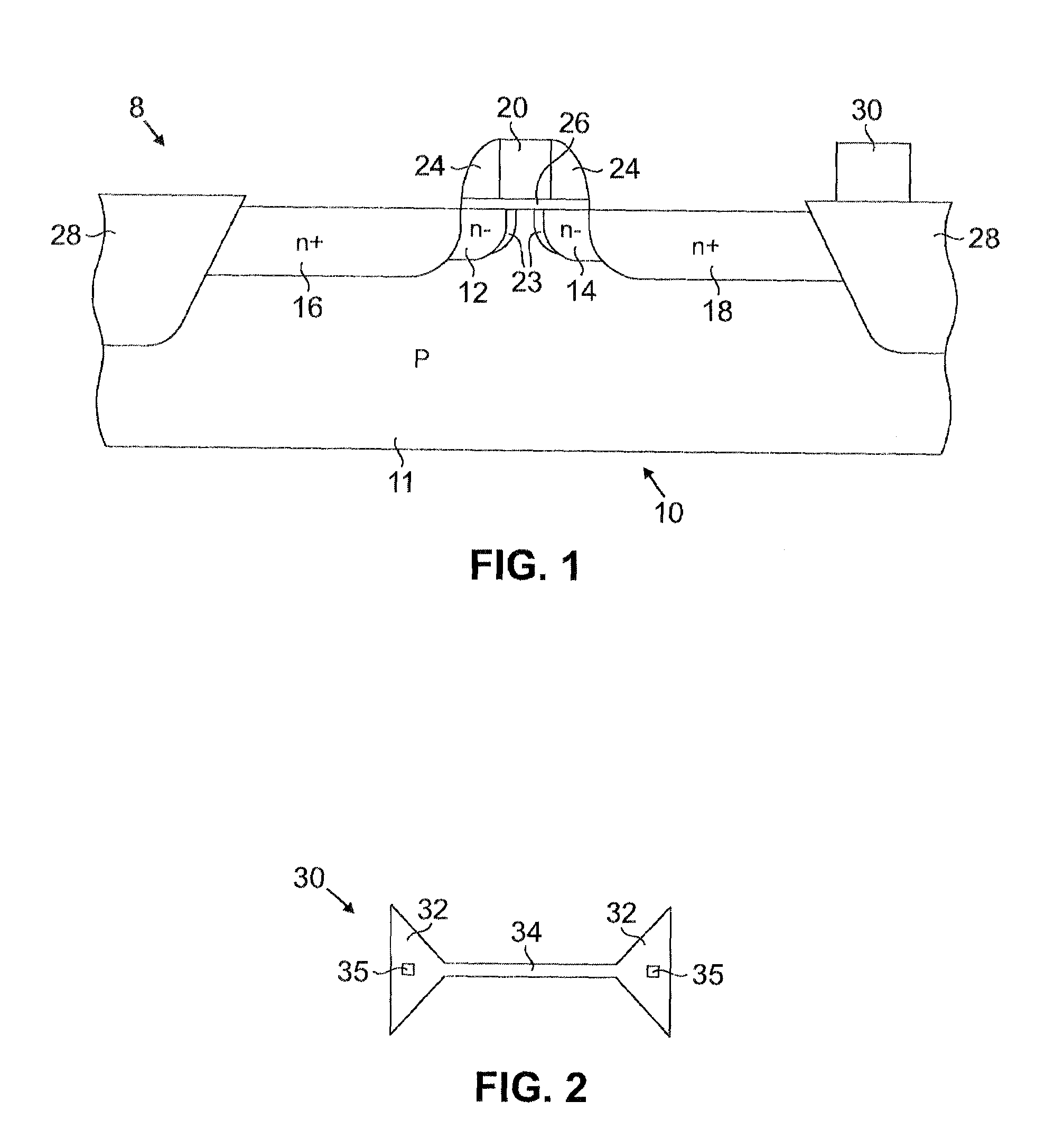

Undoped gate poly integration for improved gate patterning and cobalt silicide extendibility

A semiconductor process and apparatus uses a predetermined sequence of patterning and etching steps to etch an intrinsic polysilicon layer (26) formed over a substrate (11), thereby forming etched gates (62, 64) having vertical sidewall profiles (61, 63). While a blanket nitrogen implant (46) of the intrinsic polysilicon layer (26) may occur prior to gate etch, more idealized vertical gate sidewall profiles (61, 63) are obtained by fully doping the gates (80, 100) during the source / drain implantation steps (71, 77, 91, 97) and after the gate etch.

Owner:NORTH STAR INNOVATIONS

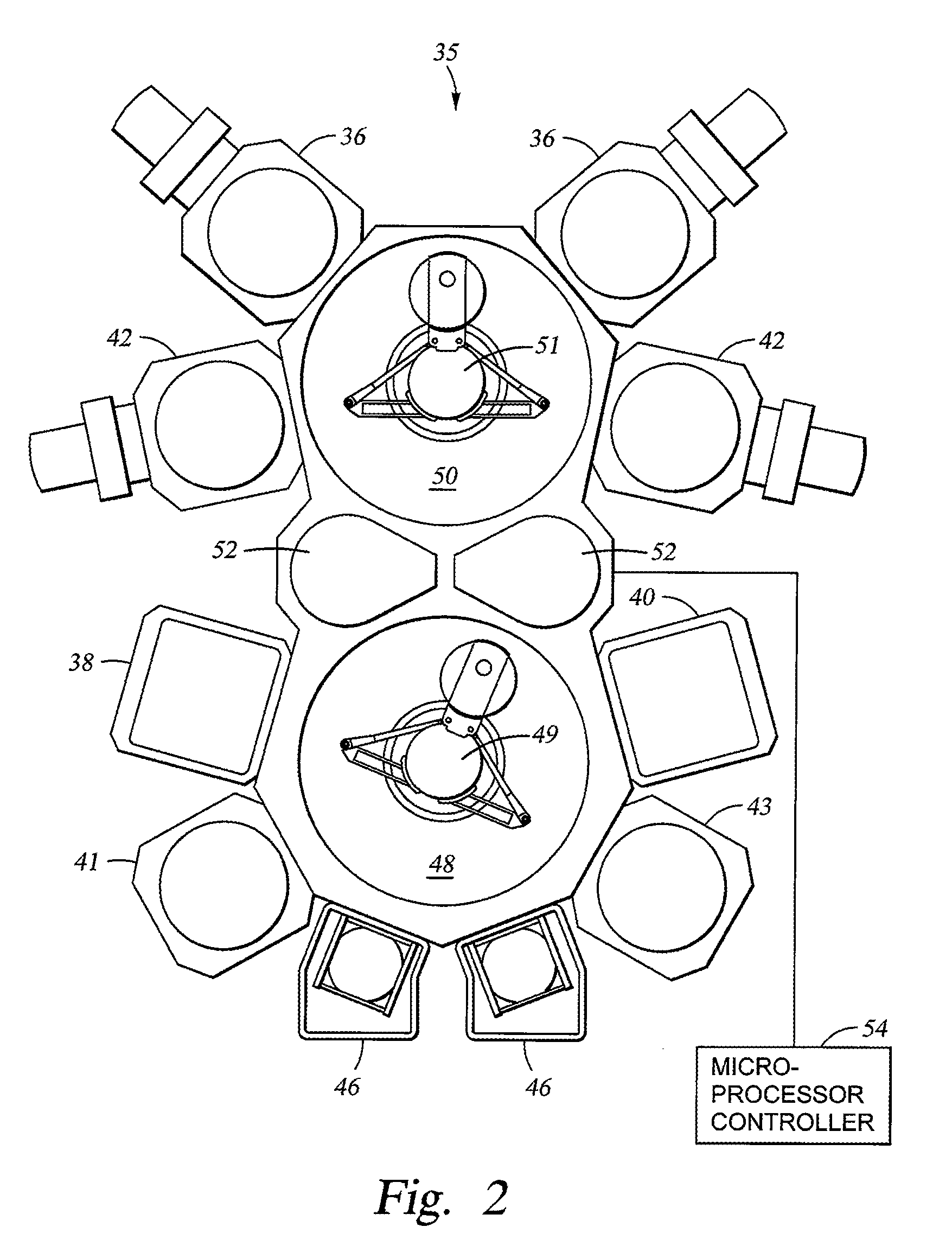

Process for forming cobalt-containing materials

ActiveUS20120264291A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingCobaltCobalt silicide

Owner:APPLIED MATERIALS INC

Process for forming cobalt and cobalt silicide materials in tungsten contact applications

InactiveUS20090004850A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSalicideSilylene

Embodiments of the invention described herein generally provide methods for forming cobalt silicide layers and metallic cobalt layers by using various deposition processes and annealing processes. In one embodiment, a method for forming a metallic silicide containing material on a substrate is provided which includes forming a metallic silicide material over a silicon-containing surface during a vapor deposition process by sequentially depositing a plurality of metallic silicide layers and silyl layers on the substrate, depositing a metallic capping layer over the metallic silicide material, heating the substrate during an annealing process, and depositing a metallic contact material over the barrier material. In one example, the metallic silicide layers and the metallic capping layer both contain cobalt. The cobalt silicide material may contain a silicon / cobalt atomic ratio of about 1.9 or greater, such as greater than about 2.0, or about 2.2 or greater.

Owner:APPLIED MATERIALS INC

Deposition methods for barrier and tungsten materials

Embodiments are provided for a method to deposit barrier and tungsten materials on a substrate. In one embodiment, a method provides forming a barrier layer on a substrate and exposing the substrate to a silane gas to form a thin silicon-containing layer on the barrier layer during a soak process. The method further provides depositing a tungsten nucleation layer over the barrier layer and the thin silicon-containing layer during an atomic layer deposition process and depositing a tungsten bulk layer on the tungsten nucleation layer during a chemical vapor deposition process. In some examples, the barrier layer contains metallic cobalt and cobalt silicide, or metallic nickel and nickel silicide. In other examples, the barrier layer contains metallic titanium and titanium nitride, or metallic tantalum and tantalum nitride.

Owner:APPLIED MATERIALS INC

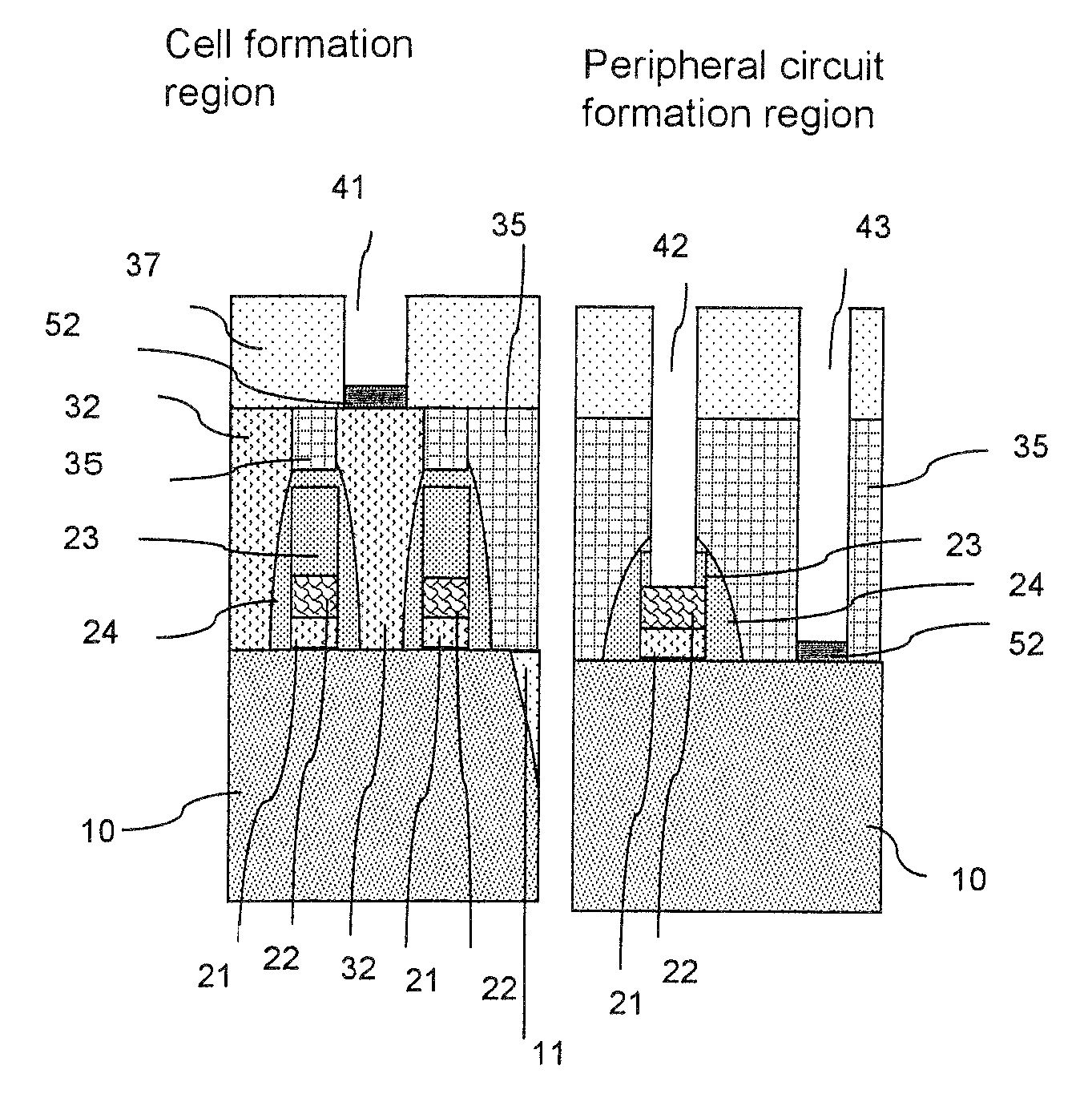

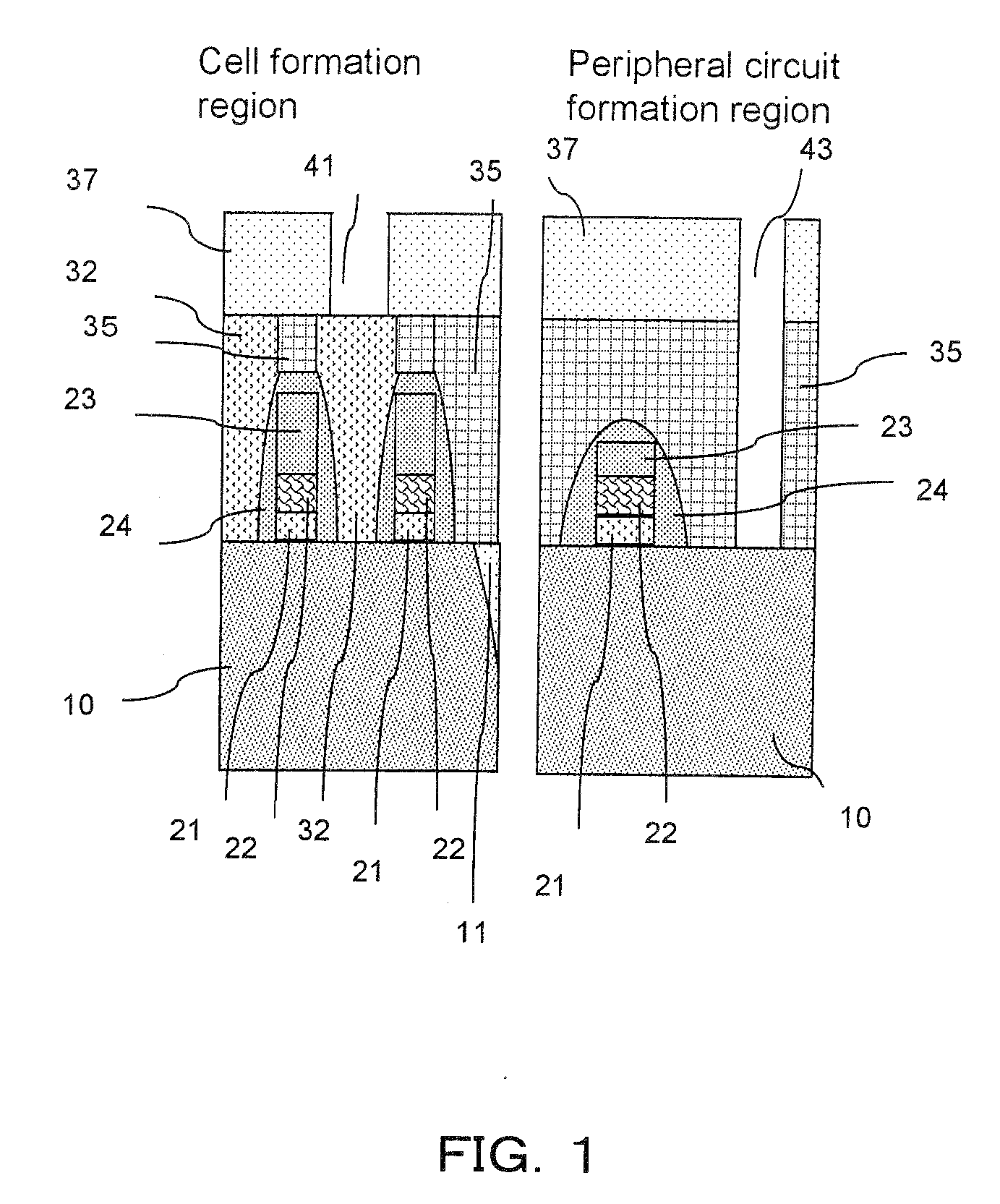

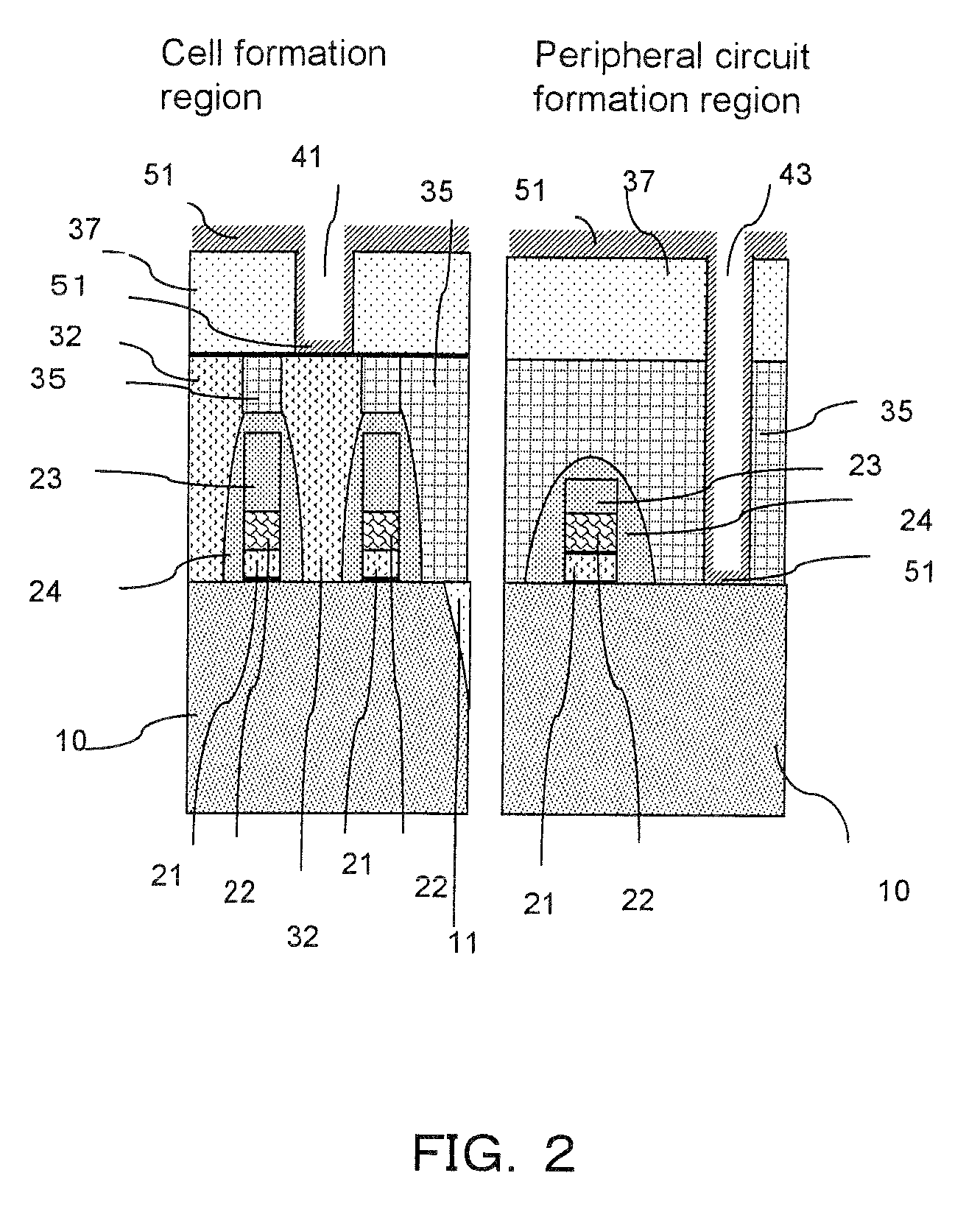

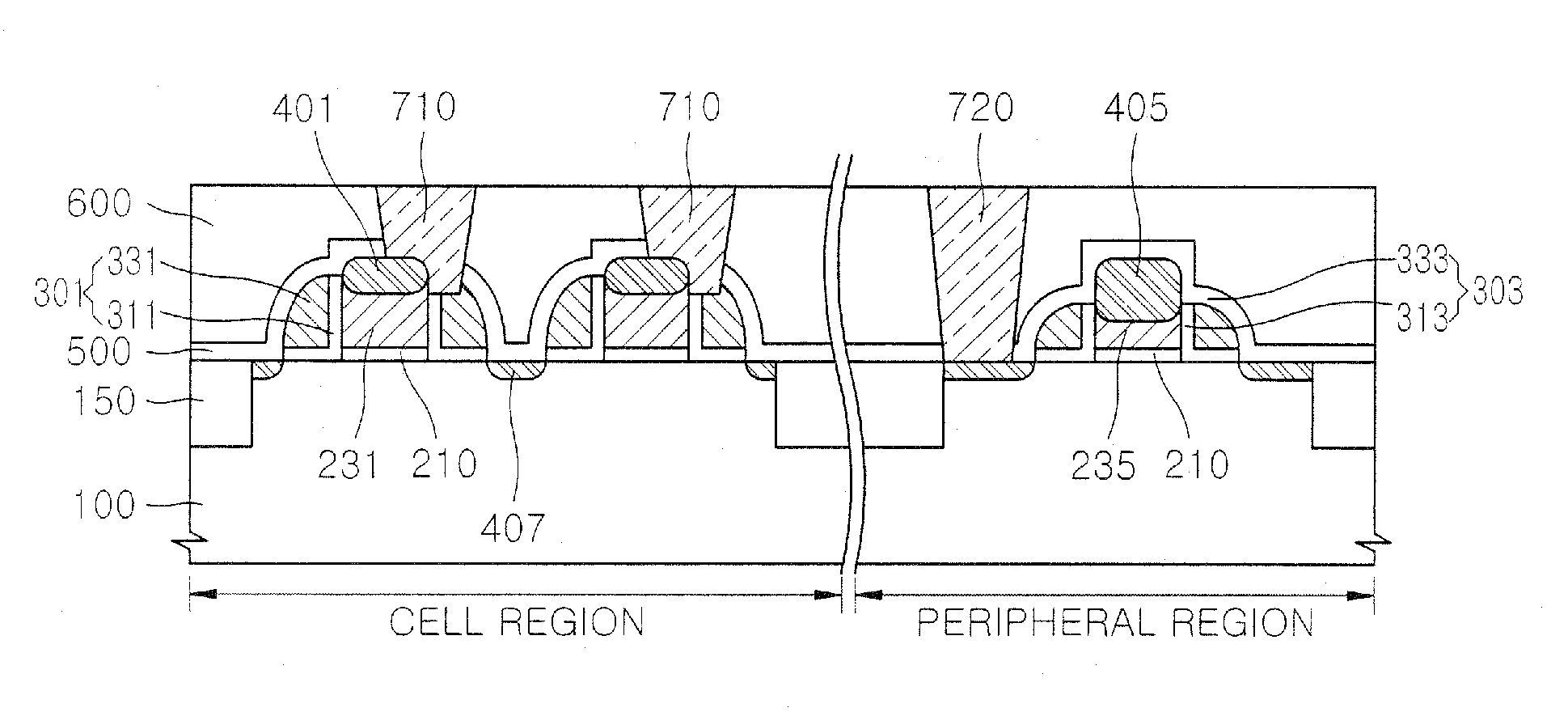

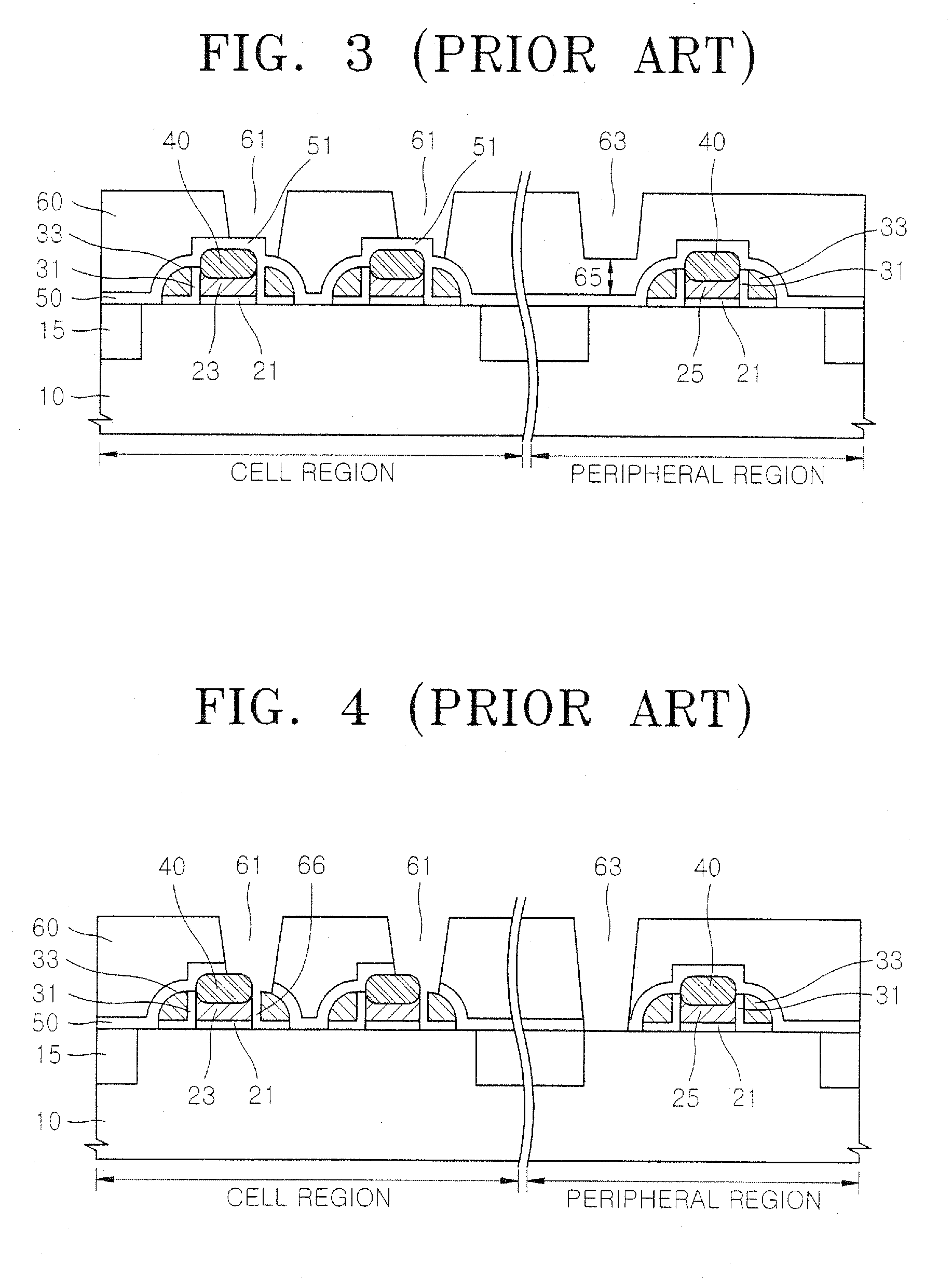

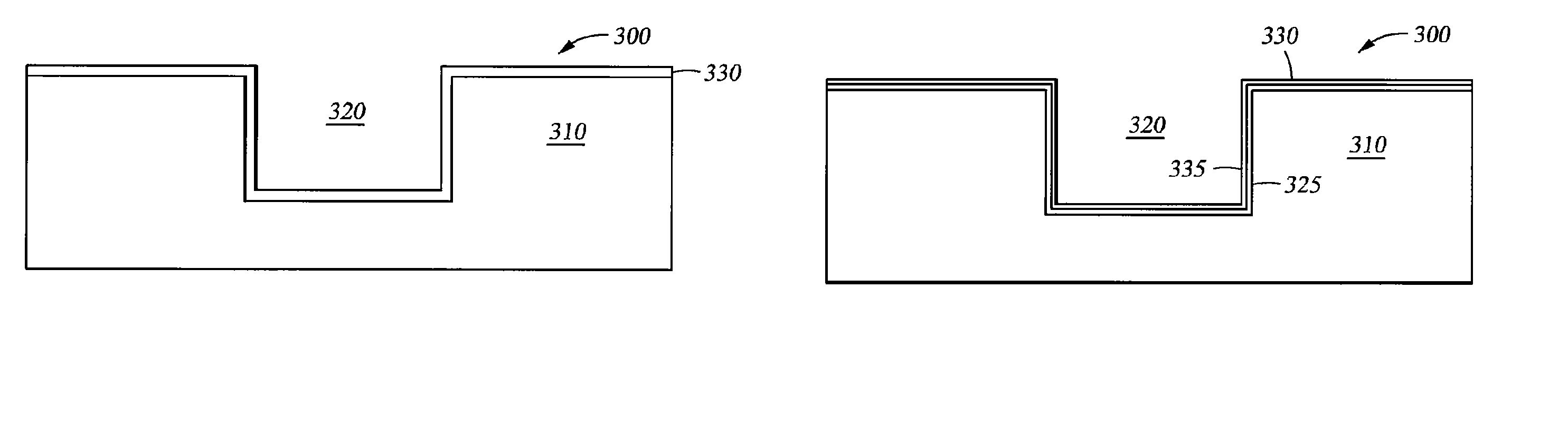

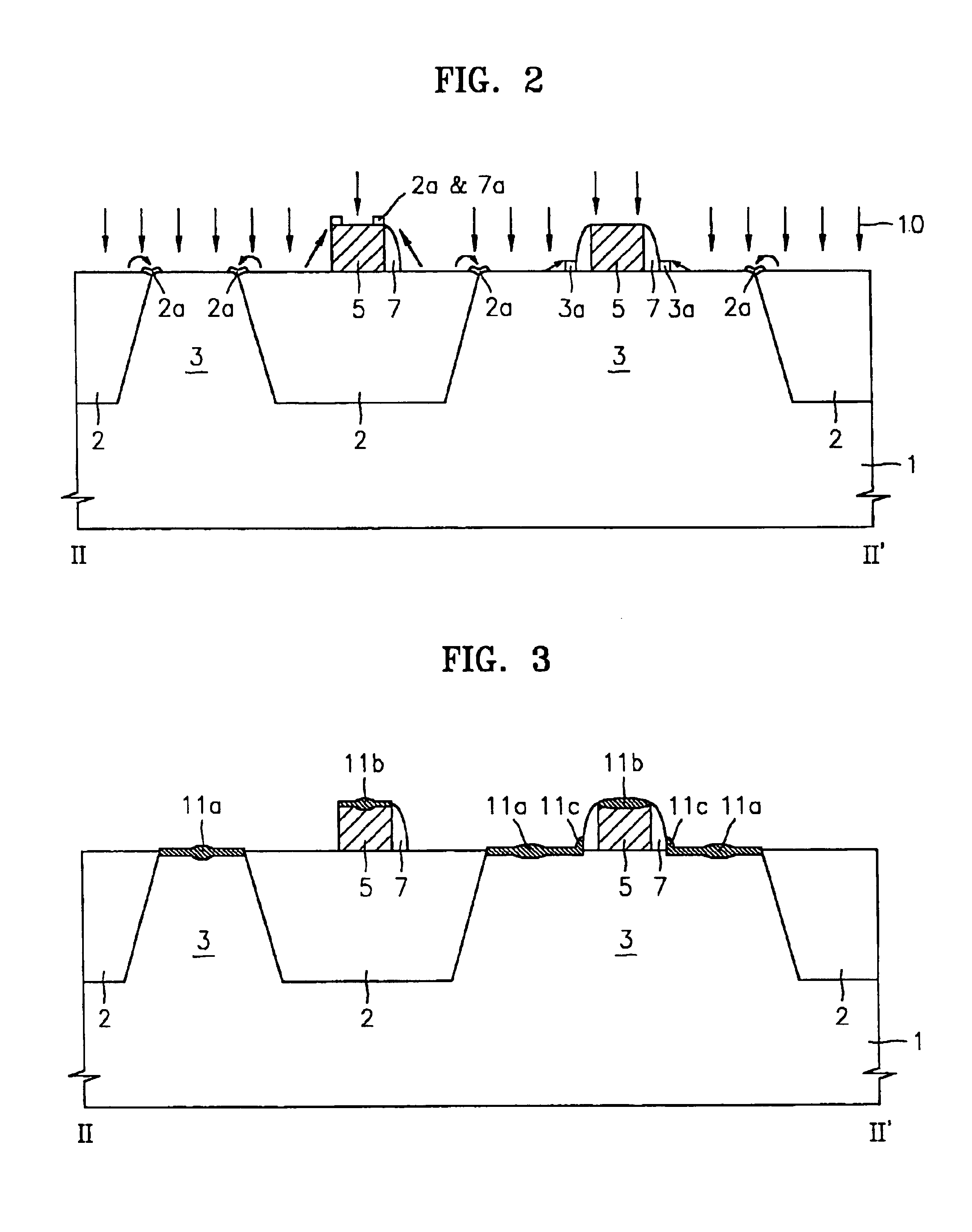

Semiconductor device with improved gate resistance and method of its manufacture

A semiconductor device is formed with a normal, non-recessed, spacer structure in a cell region and a recessed spacer structure in a peripheral region. The recessed spacer structure is formed as by etch masking those in the cell region and exposing those in the peripheral region, then performing an etch process. The increased height of the cell region spacers is adapted to further prevent over-etching during gate interconnect formation which would otherwise result in etching through the spacer to the substrate and subsequent short circuit. Therefore, it is also possible to prevent bridge defects due to over-etching, which occurs because the barrier metal layer for a subsequent interconnection contact is accidentally connected to the underlying substrate. Also, since the recessed spacer structure is provided in the peripheral region, it is possible to remarkably enhance a resistance distribution of a cobalt silicide layer occurring in a gate line width of 100 nm or less.

Owner:SAMSUNG ELECTRONICS CO LTD

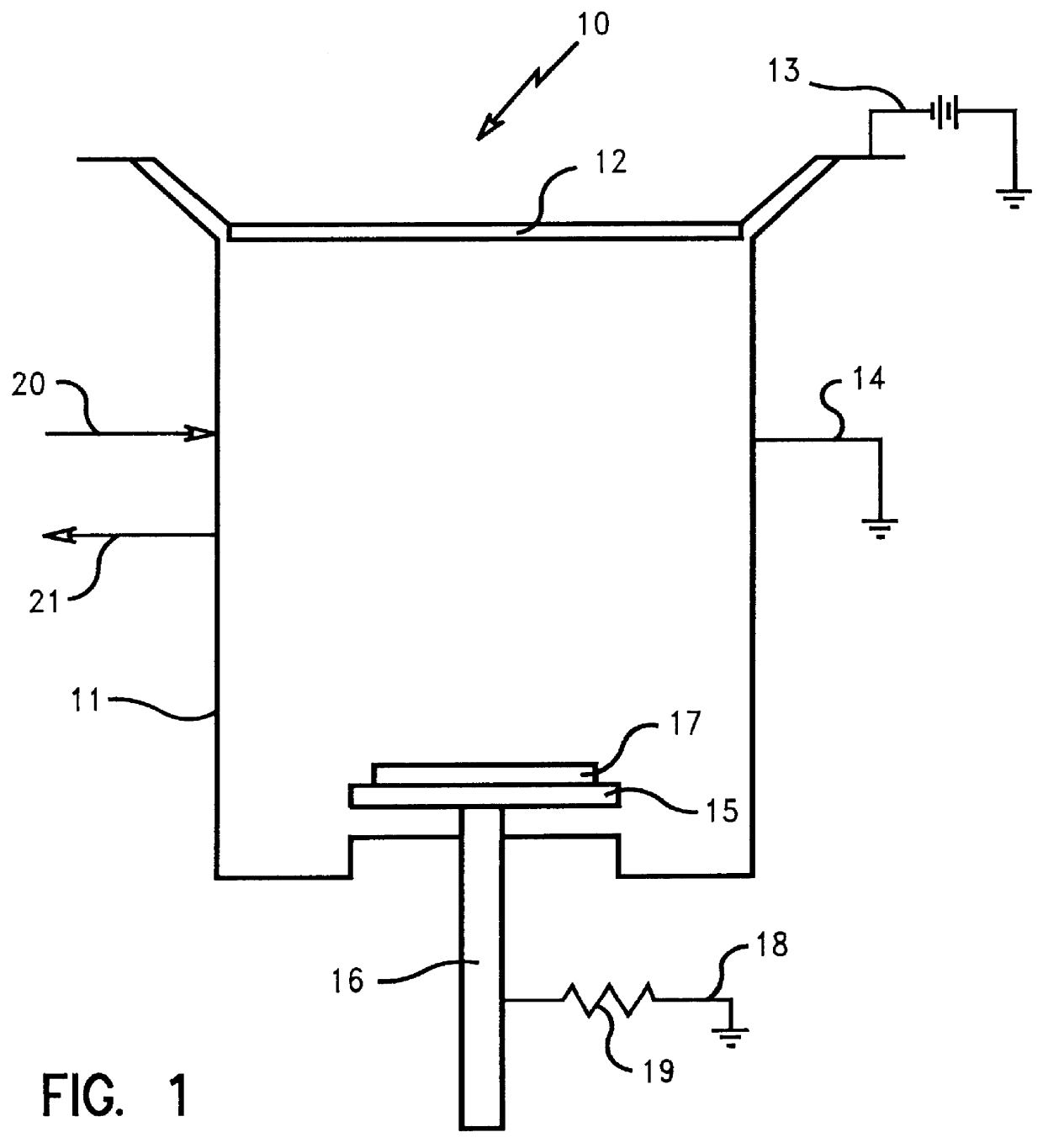

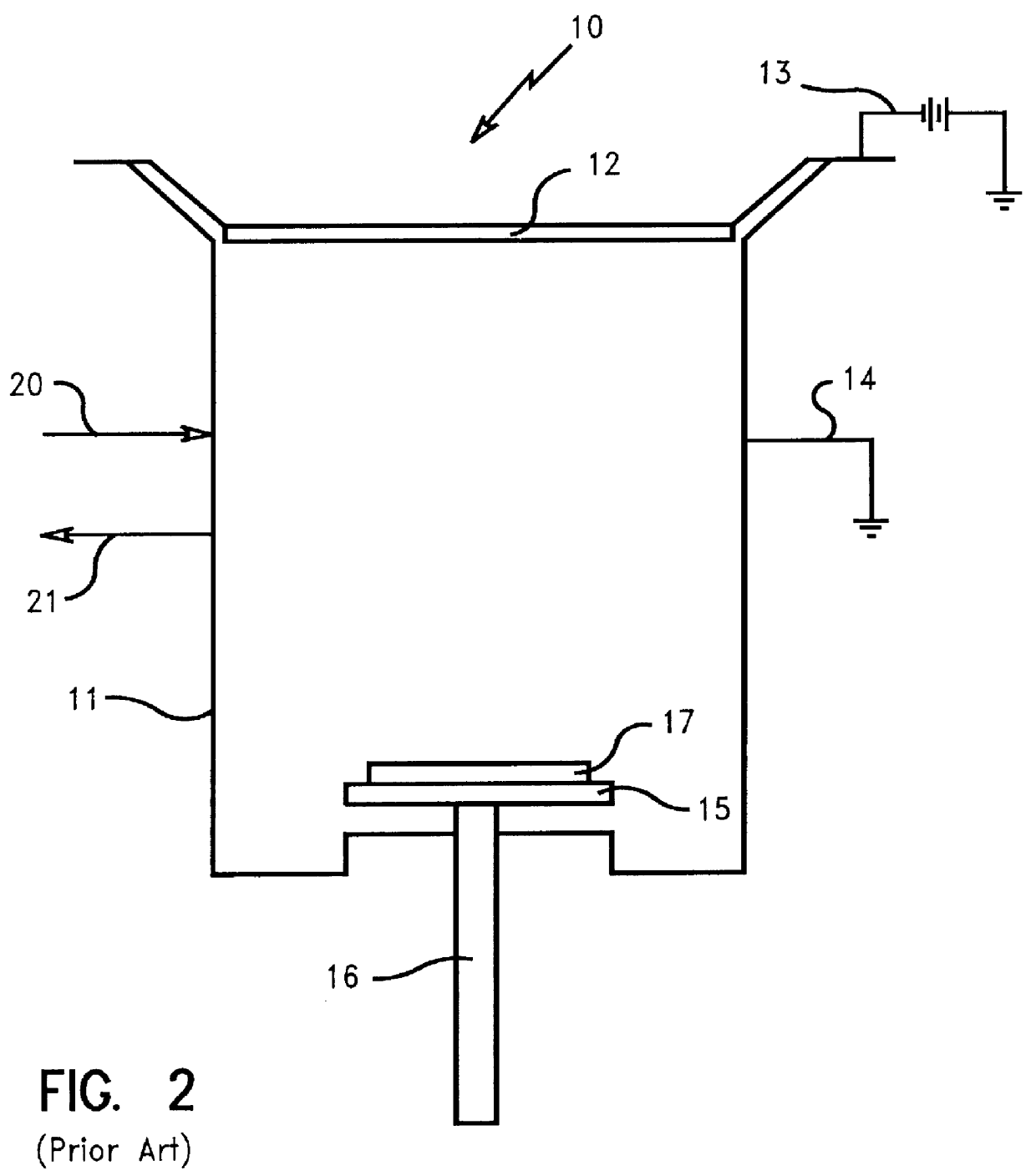

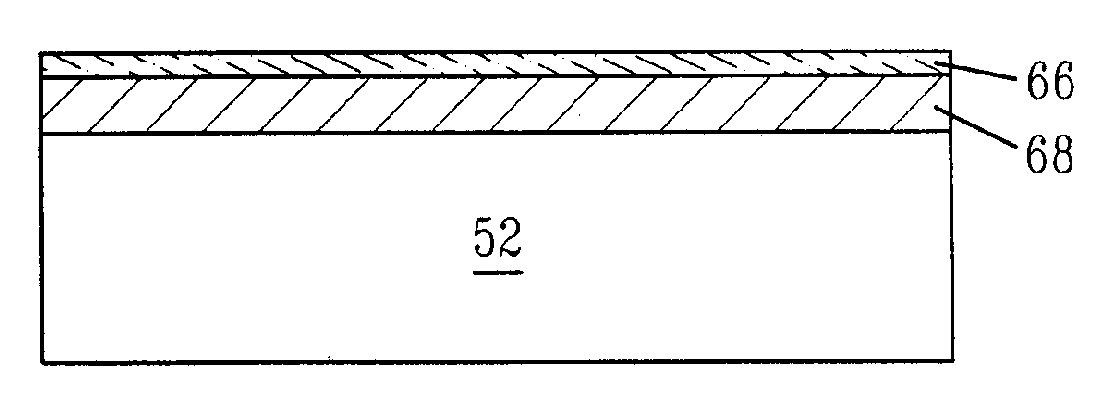

Method for depositing cobalt

A method and apparatus are provided for forming cobalt on a silicon substrate containing native silicon oxide on the surface thereof wherein a modified vapor sputtering device is used. The vapor sputtering device is modified by providing an electrical circuit to ground whereby the wafer disposed in the device is electrically connected to the ground circuit. The ground circuit preferably contains a resistor therein to control wafer voltage and current flow from the wafer to ground. It has been found that providing a current flow from the wafer to ground and particularly in a ground circuit containing a resistor, provides an in-situ simultaneous cleaning of native oxide on the silicon surface and deposition of cobalt on cleaned silicon. The deposited cobalt containing substrate may then be readily annealed to form cobalt silicide evenly and uniformly across the desired regions of the wafer surface. A cobalt coated silicon substrate and an annealed cobalt silicide coated silicon substrate made using the method and apparatus of the invention are also provided as well as electronic components made using the cobalt coated silicon substrate.

Owner:GLOBALFOUNDRIES INC

Deposition methods for barrier and tungsten materials

Embodiments as described herein provide a method for depositing barrier layers and tungsten materials on substrates. In one embodiment, a method for depositing materials is provided which includes forming a barrier layer on a substrate, wherein the barrier layer contains a cobalt silicide layer and a metallic cobalt layer, exposing the barrier layer to a soak gas containing a reducing gas during a soak process, and forming a tungsten material over the barrier layer. In one example, the barrier layer may be formed by depositing a cobalt-containing material on a dielectric surface of the substrate and annealing the substrate to form the cobalt silicide layer from a lower portion of the cobalt-containing material and the metallic cobalt layer from an upper portion of the cobalt-containing material.

Owner:APPLIED MATERIALS INC

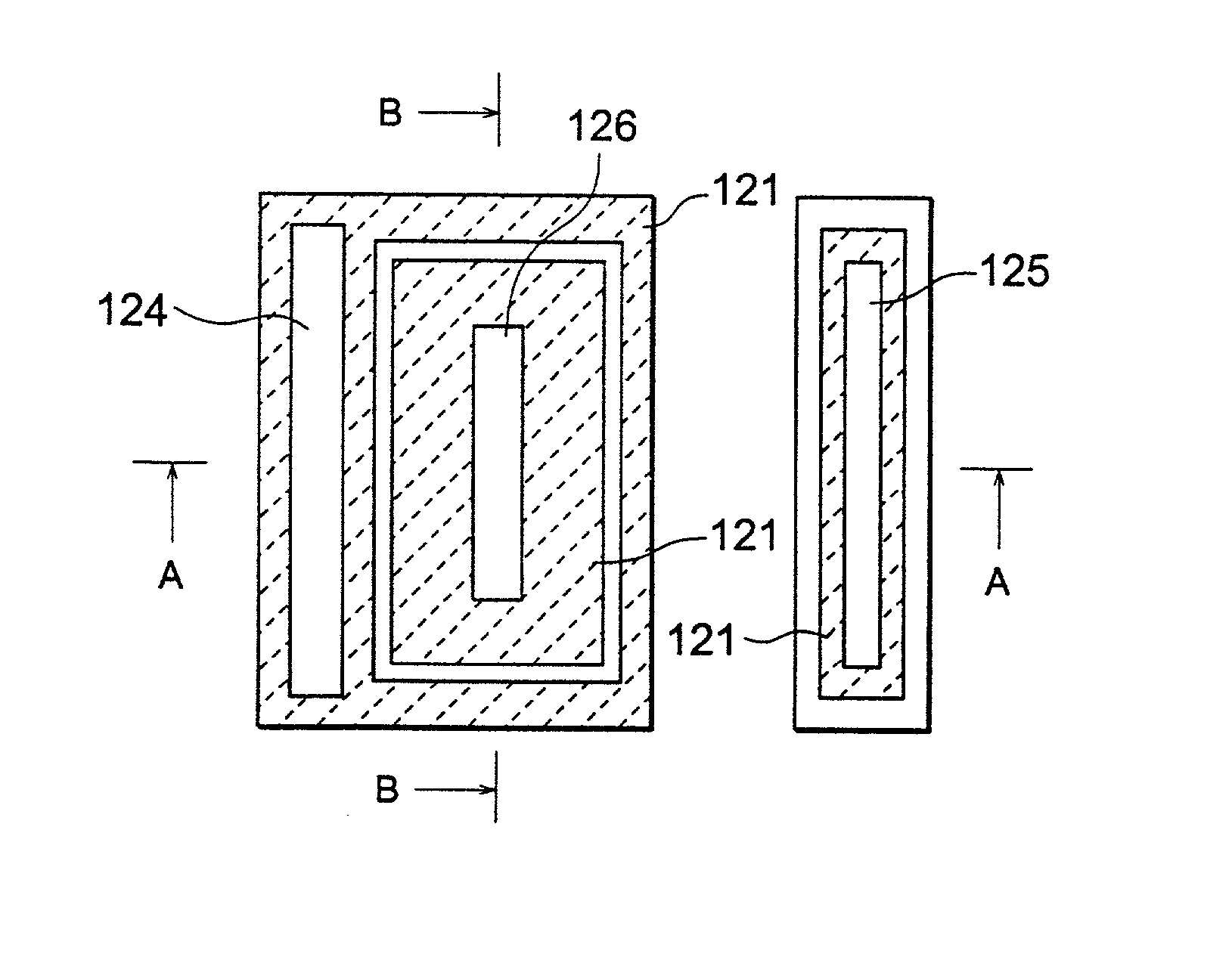

Method of forming cobalt silicide film and method of manufacturing semiconductor device having cobalt silicide film

A cobalt-containing film on a silicon-containing conductive region, and a titanium-rich capping layer is formed on cobalt-containing film. The atomic % ratio of titanium to other elements (if any) in the titanium-rich capping layer is more than one (1). The resultant structure is annealed so that cobalt of the cobalt-containing film and silicon of the silicon-containing conductive region react with each other to form a cobalt silicide film. When the formation of the cobalt-containing film is carried out at a high temperature, a diffusion restraint interface film is also formed.

Owner:SAMSUNG ELECTRONICS CO LTD

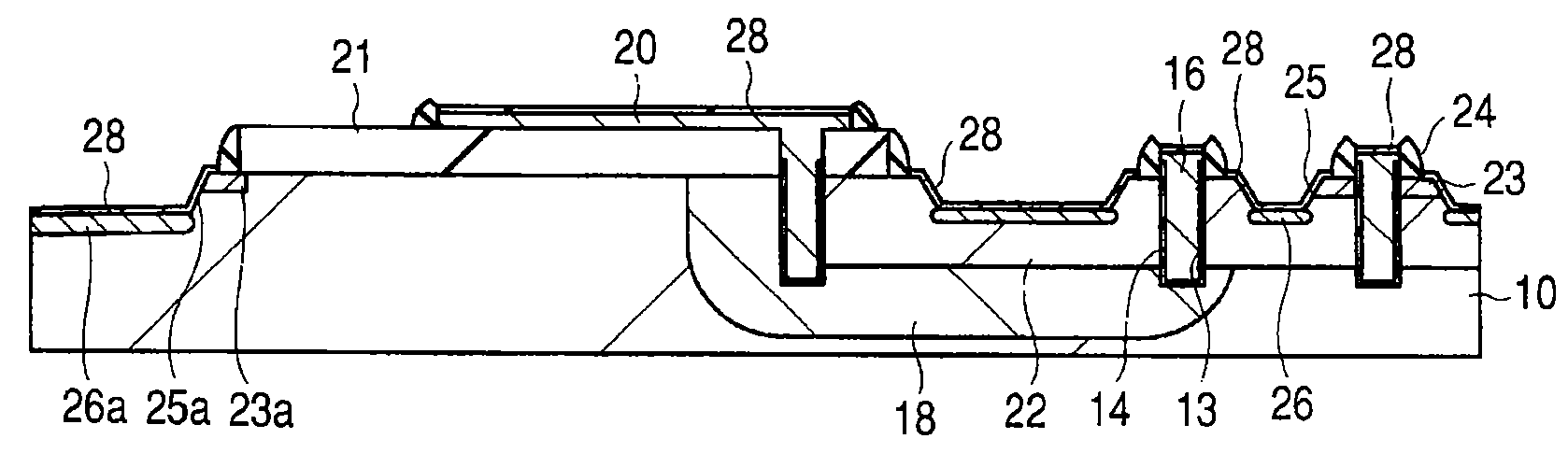

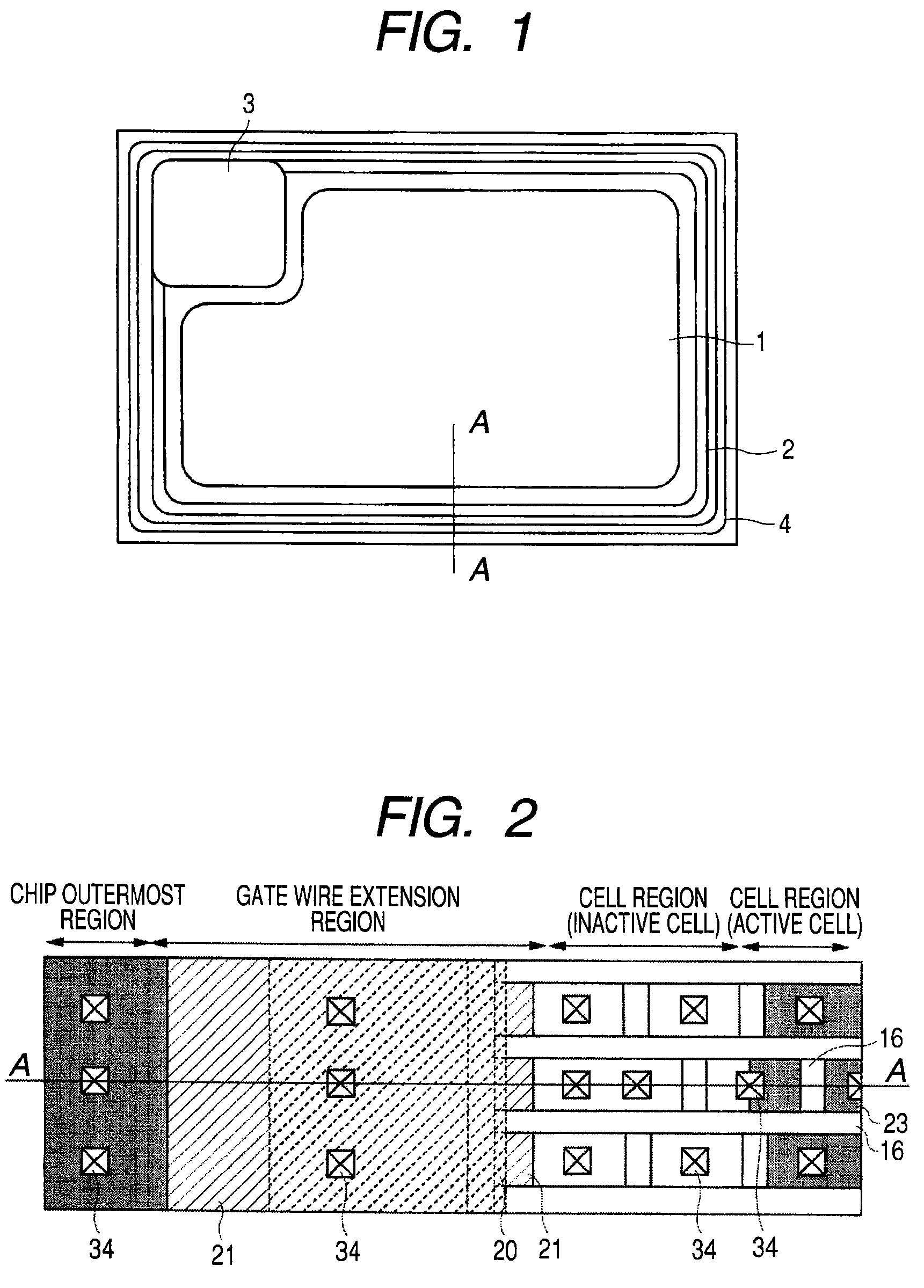

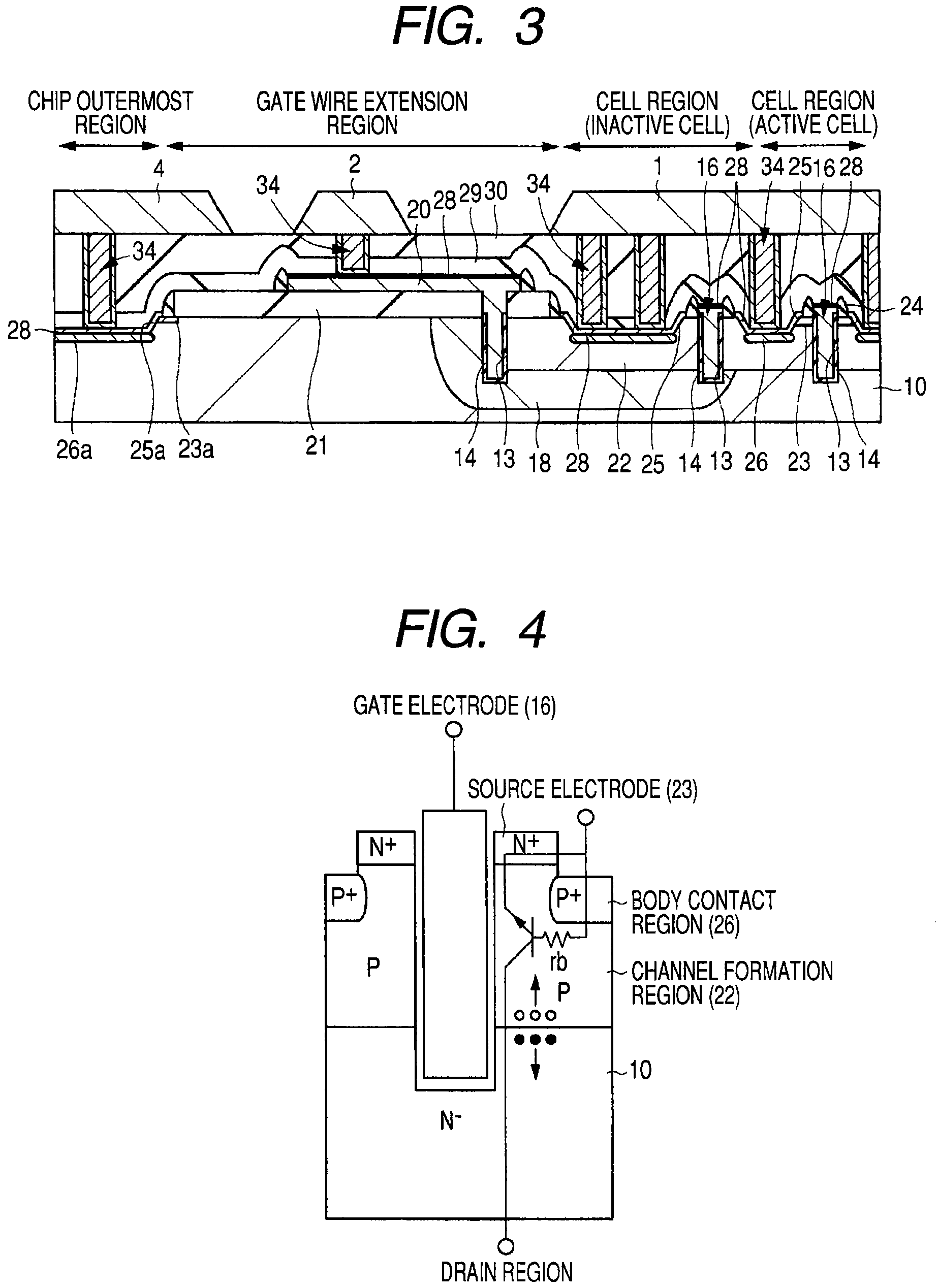

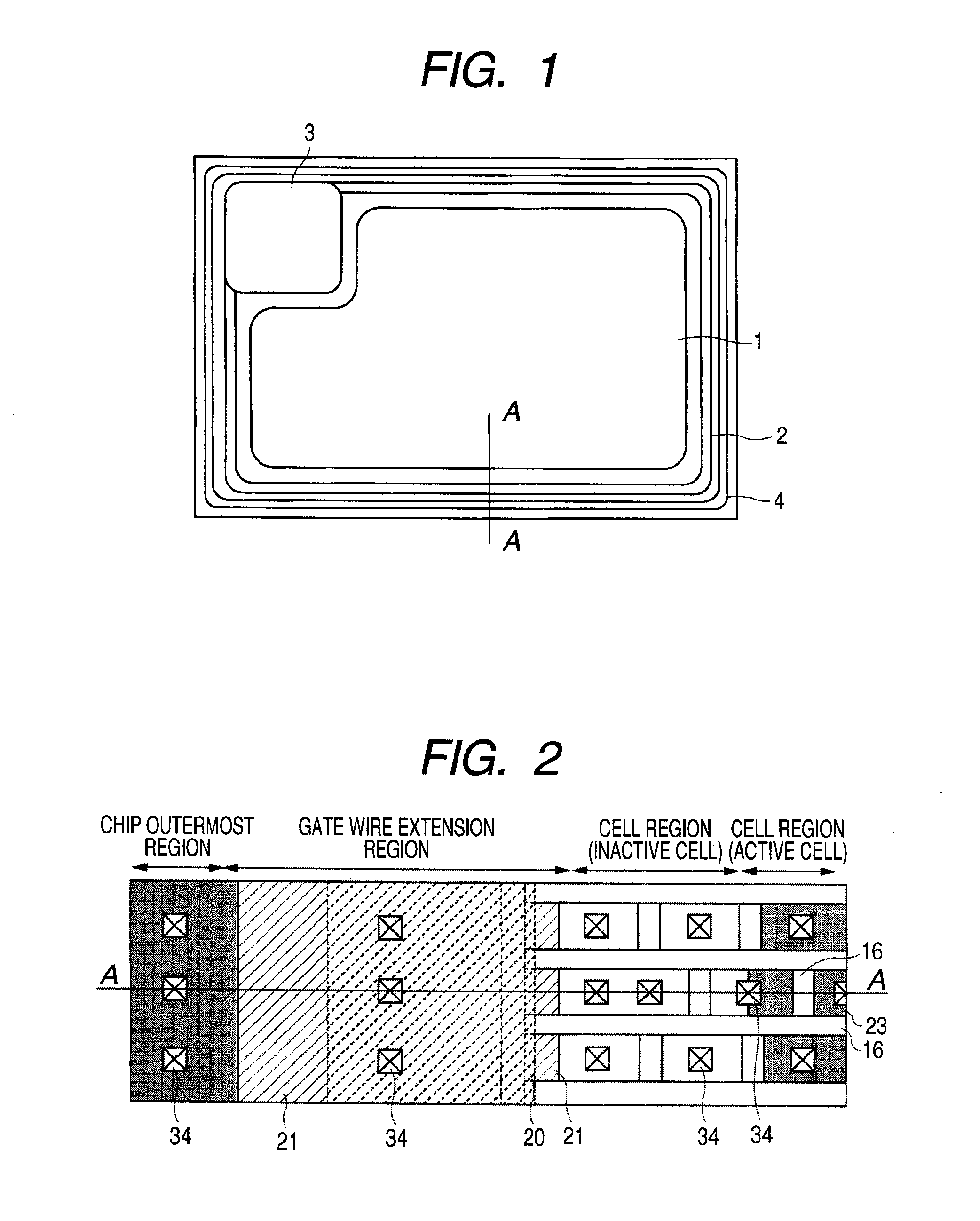

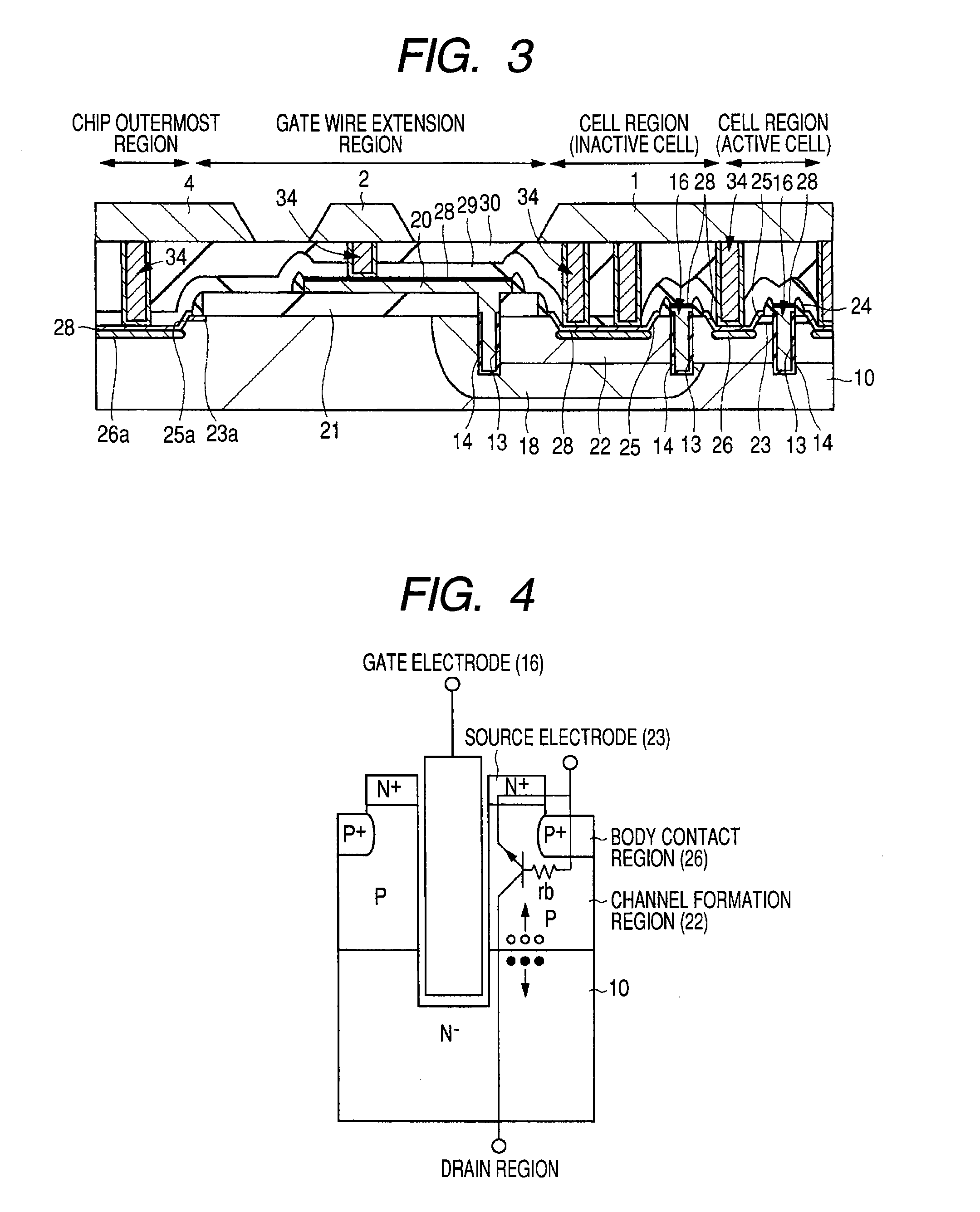

Semiconductor device and method of manufacturing the same

A gate trench 13 is formed in a semiconductor substrate 10. The gate trench 13 is provided with a gate electrode 16 formed over a gate insulating film 14. A portion of the gate electrode 16 protrudes from the semiconductor substrate 10, and a sidewall 24 is formed over a side wall portion of the protruding portion. A body trench 25 is formed in alignment with an adjacent gate electrode 16. A cobalt silicide film 28 is formed over a surface of the gate electrode 16 and over a surface of the body trench 25. A plug 34 is formed using an SAC technique.

Owner:RENESAS ELECTRONICS CORP

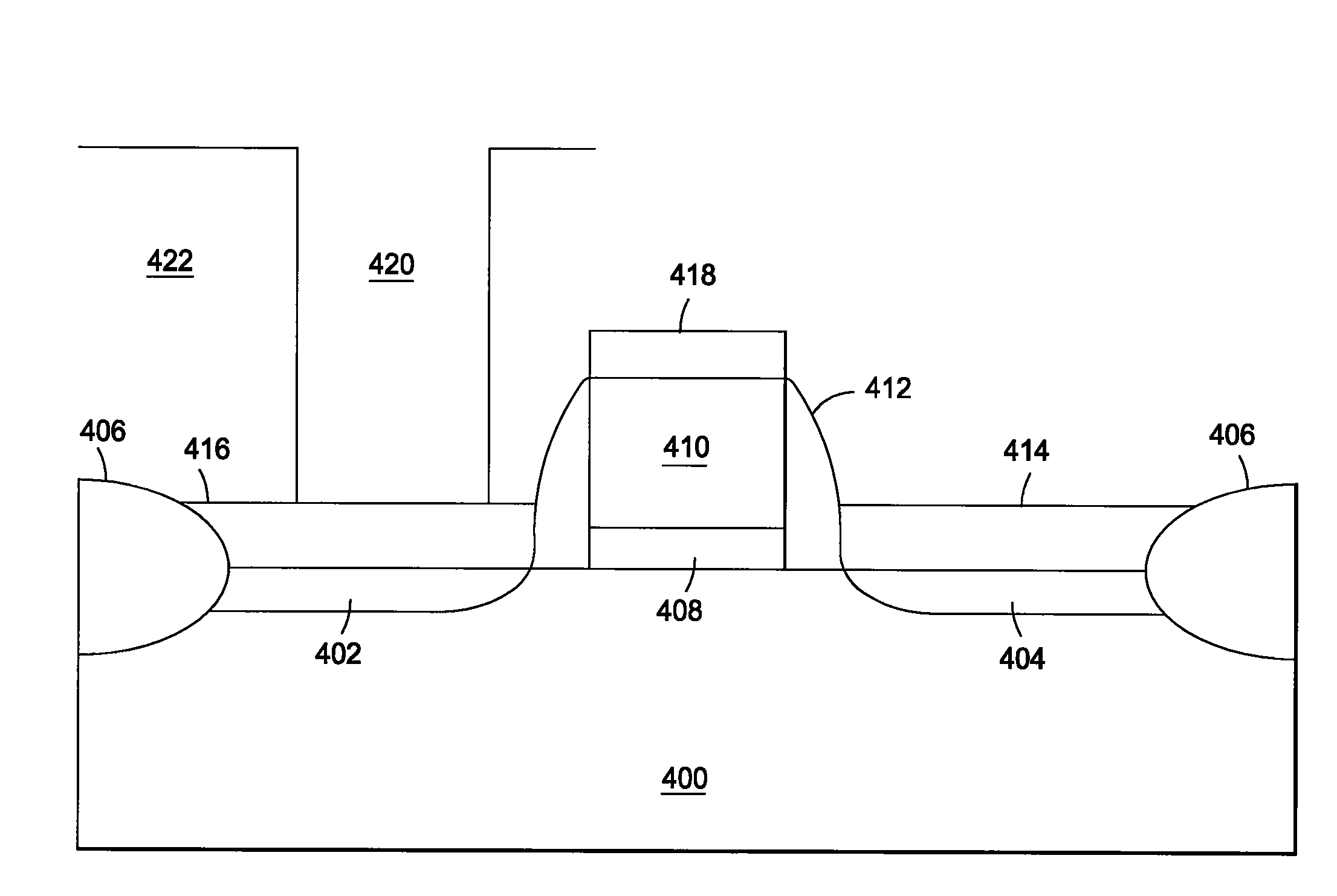

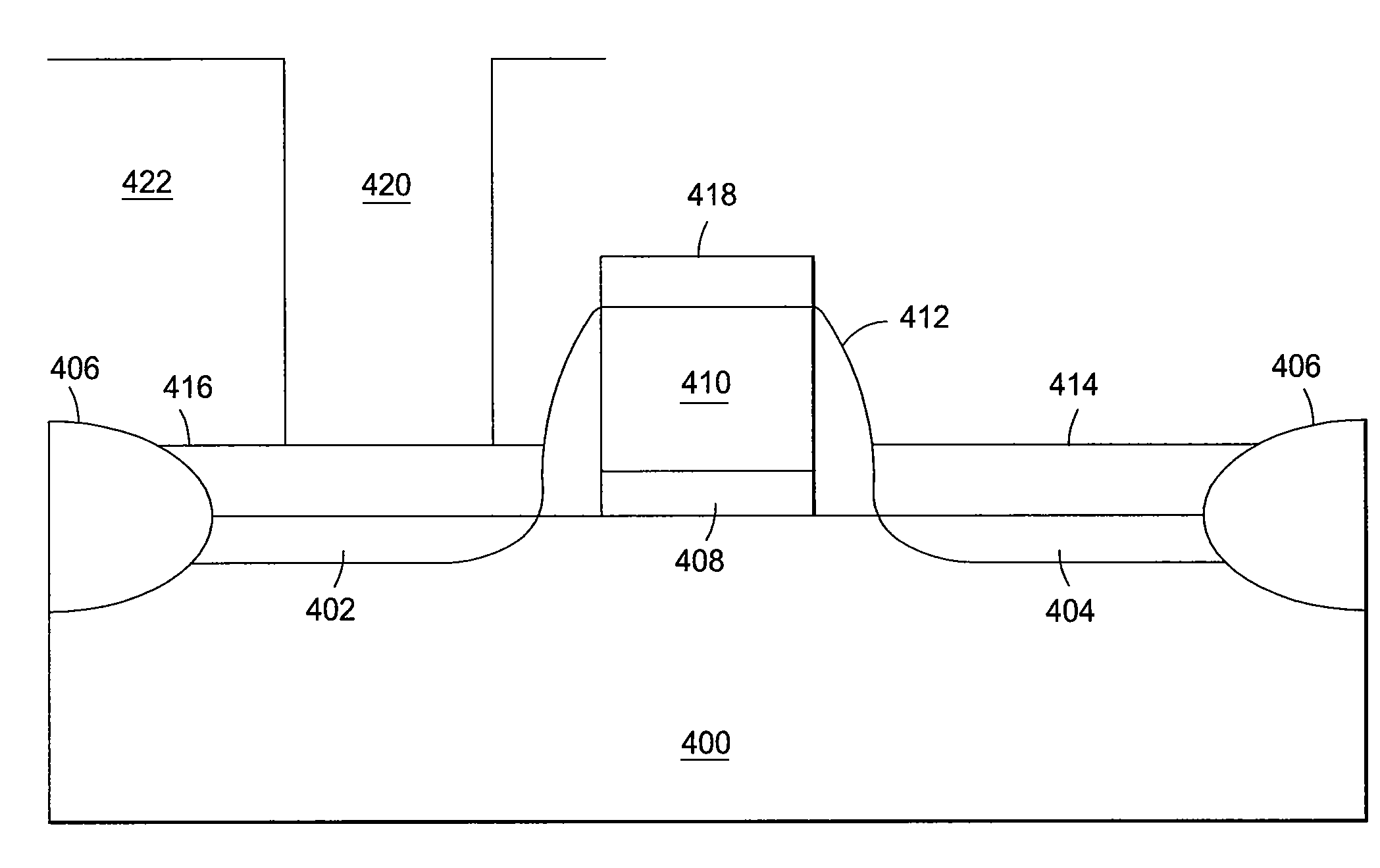

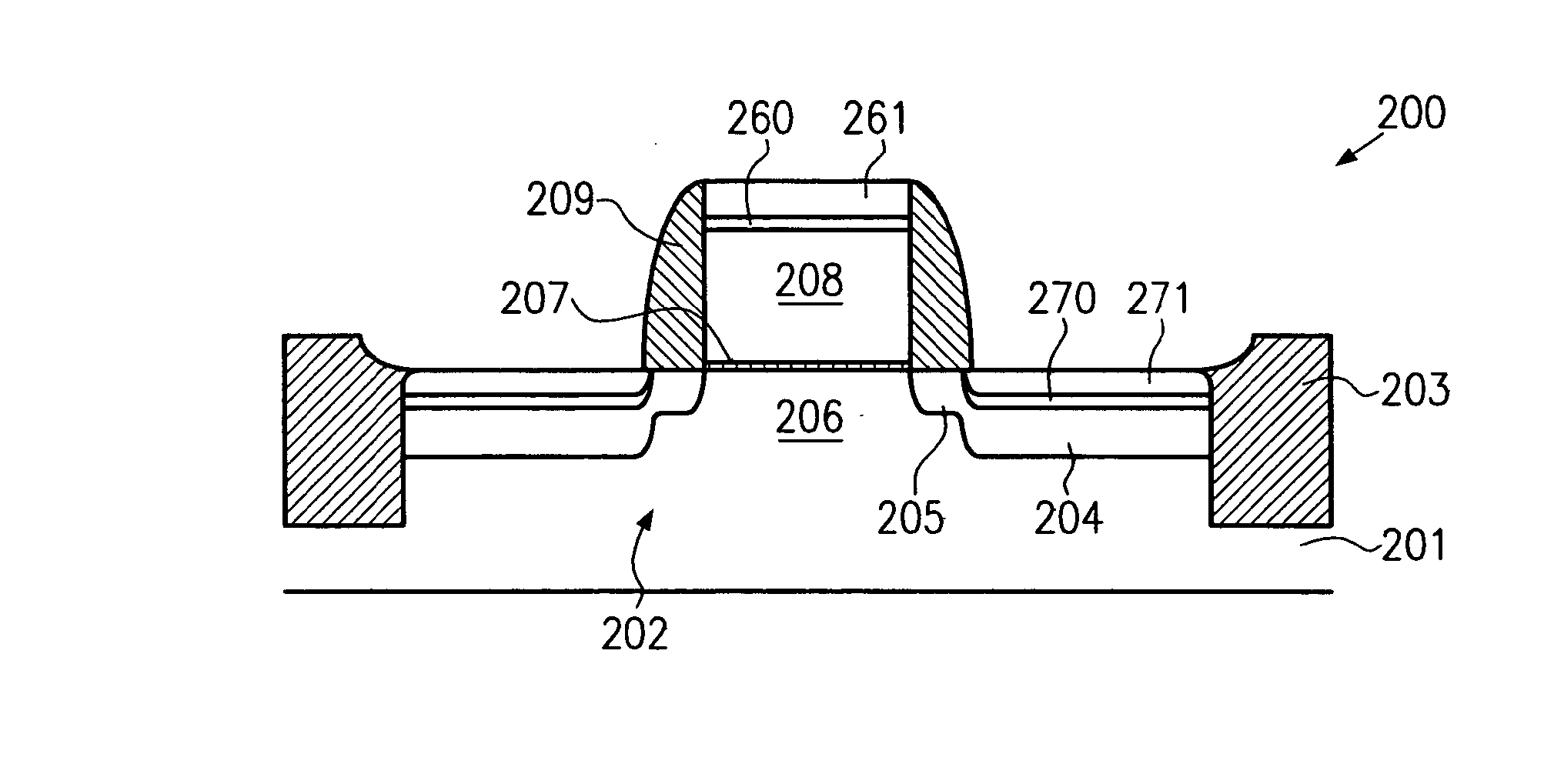

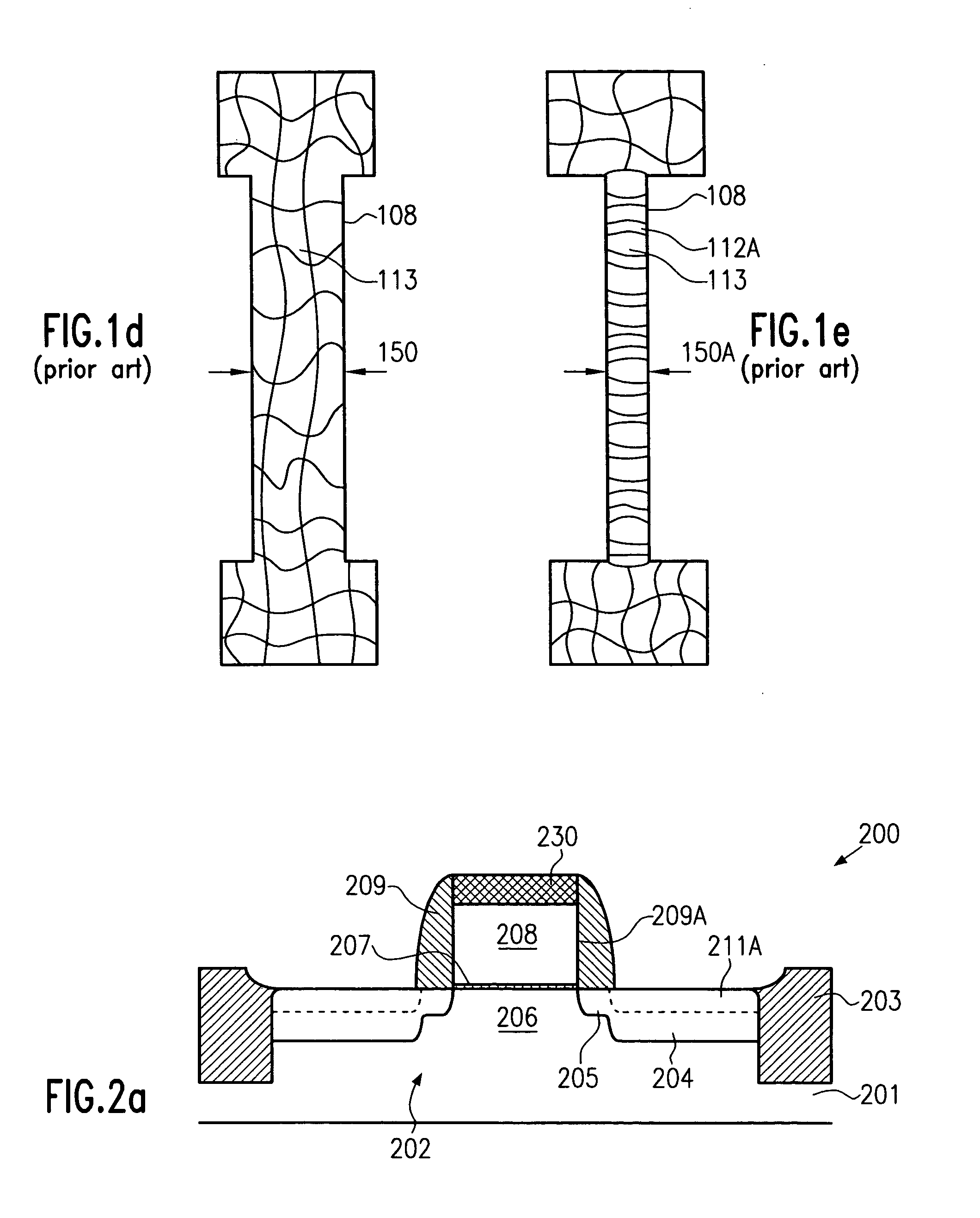

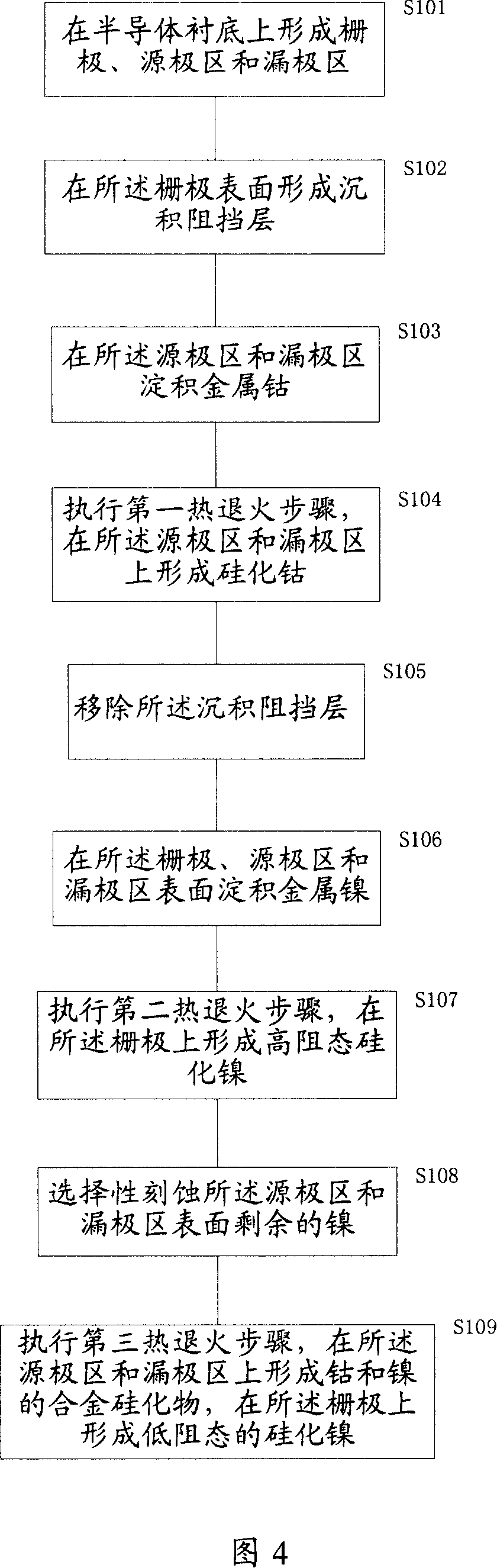

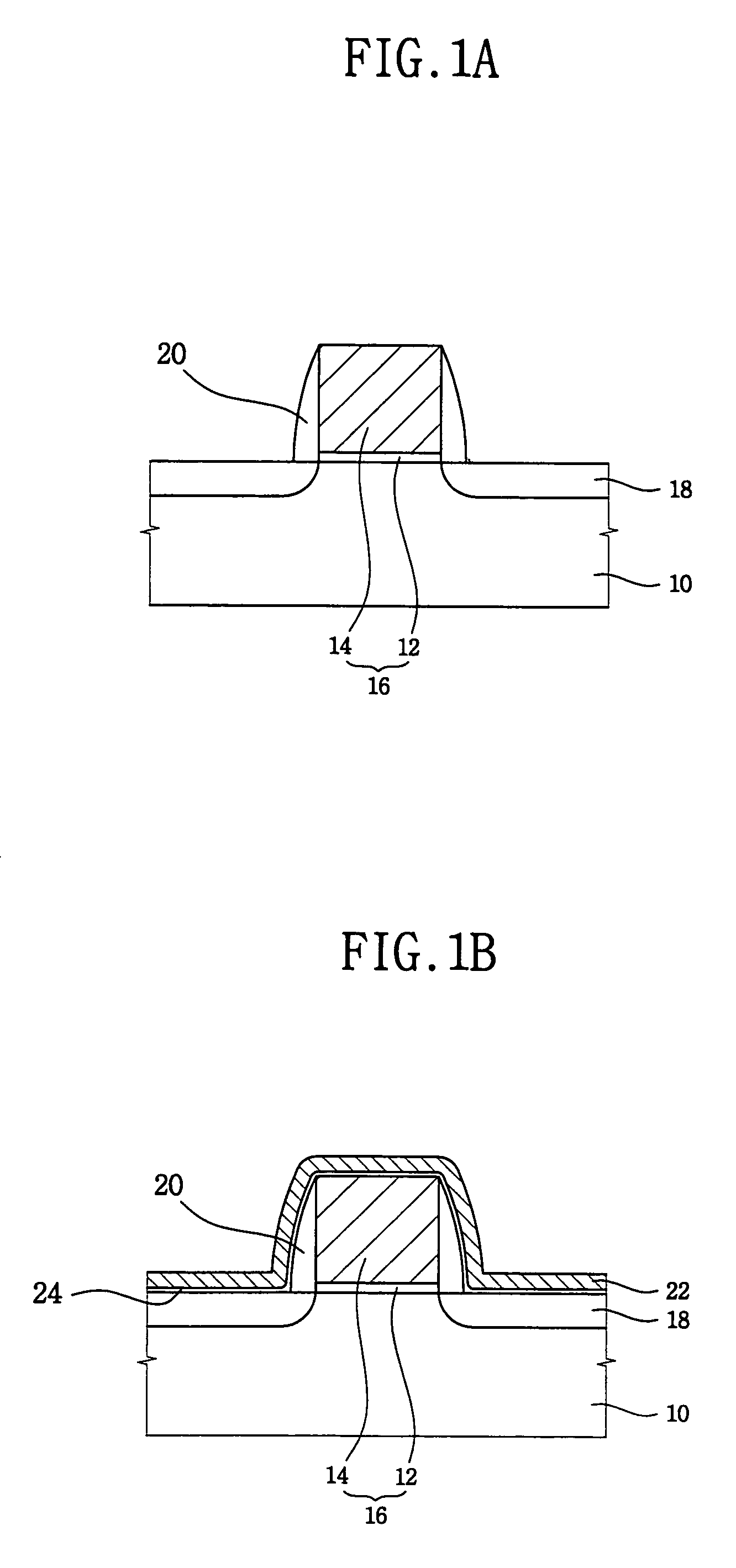

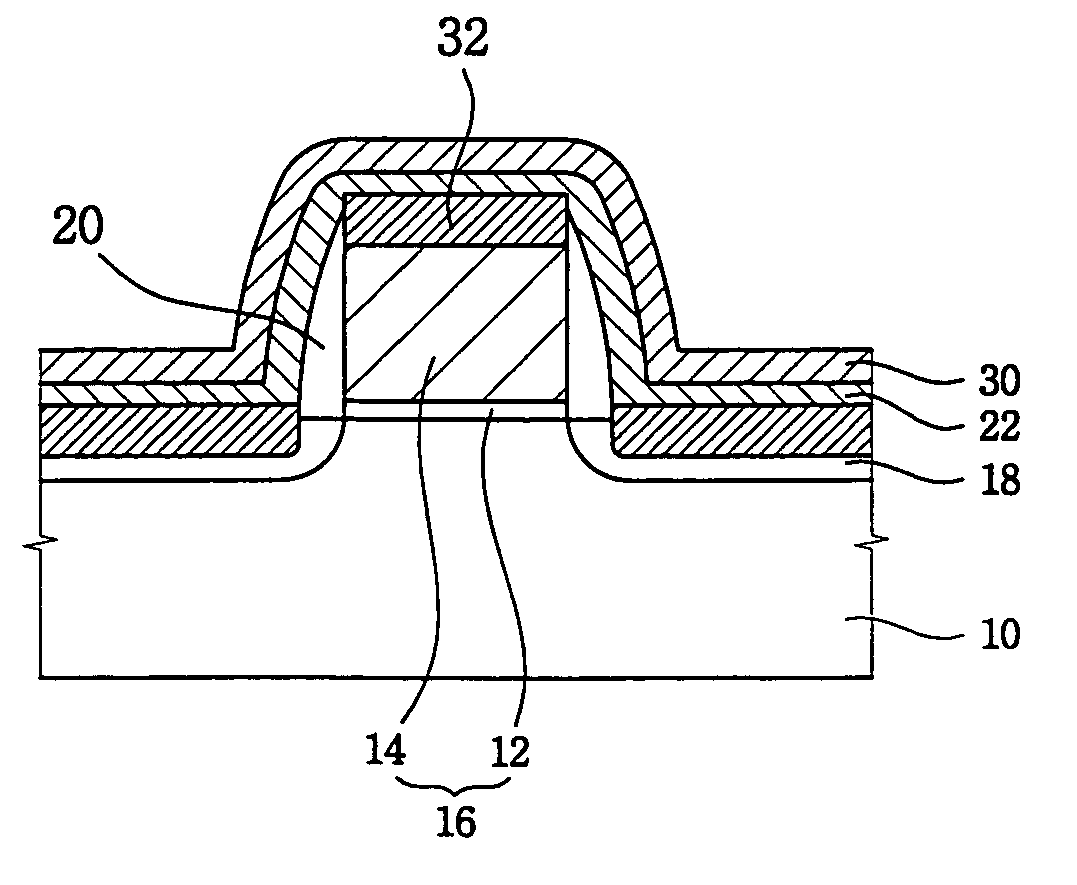

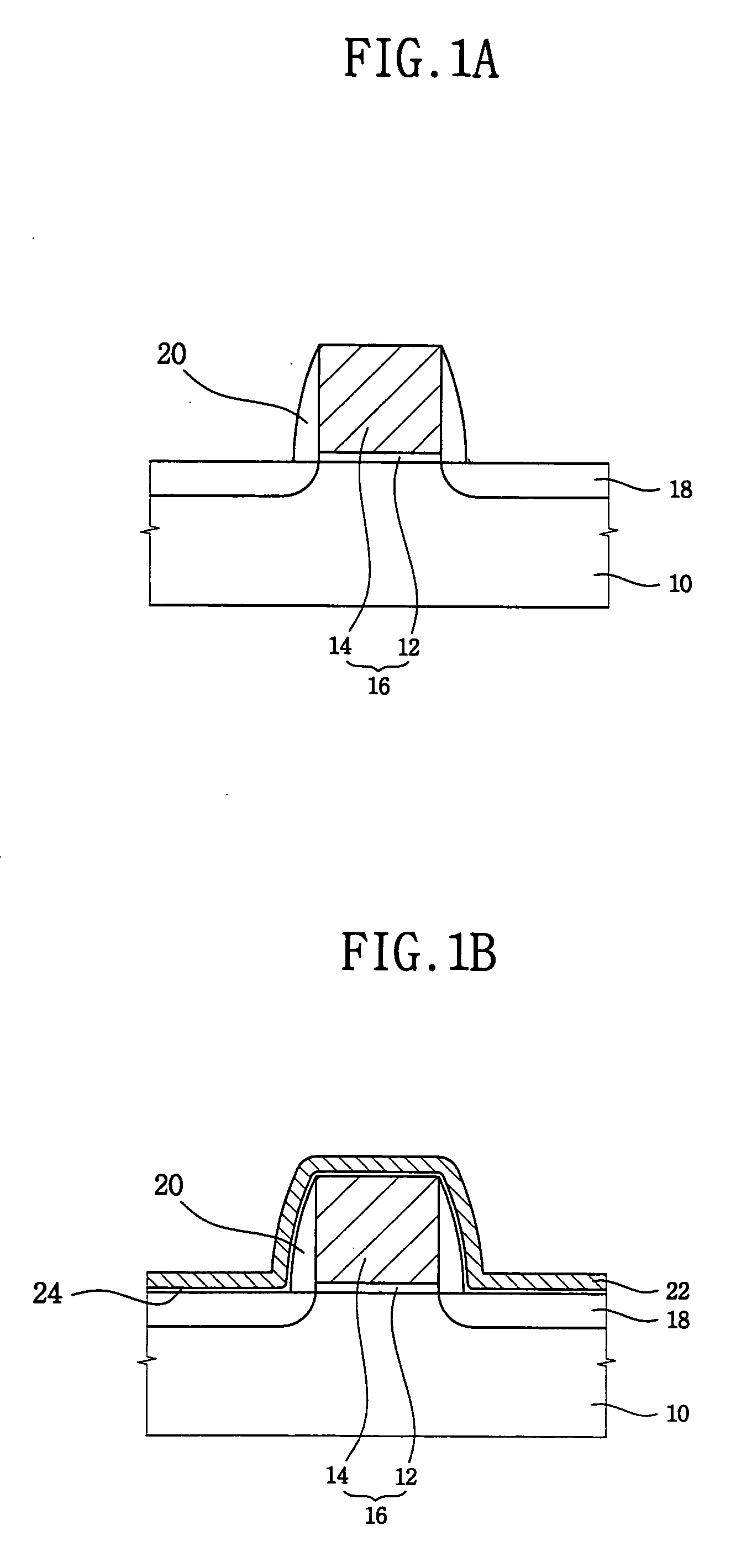

Semiconductor device having a nickel/cobalt silicide region formed in a silicon region

InactiveUS20050070082A1Improve bindingImproved contact characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceDevice material

By forming a buried nickel silicide layer followed by a cobalt silicide layer in silicon-containing regions, such as a gate electrode of a field effect transistor, the superior characteristics of both silicides may be combined so as to provide the potential for further device scaling without unduly compromising the sheet resistance and the contact resistance of scaled silicon circuit features.

Owner:ADVANCED MICRO DEVICES INC

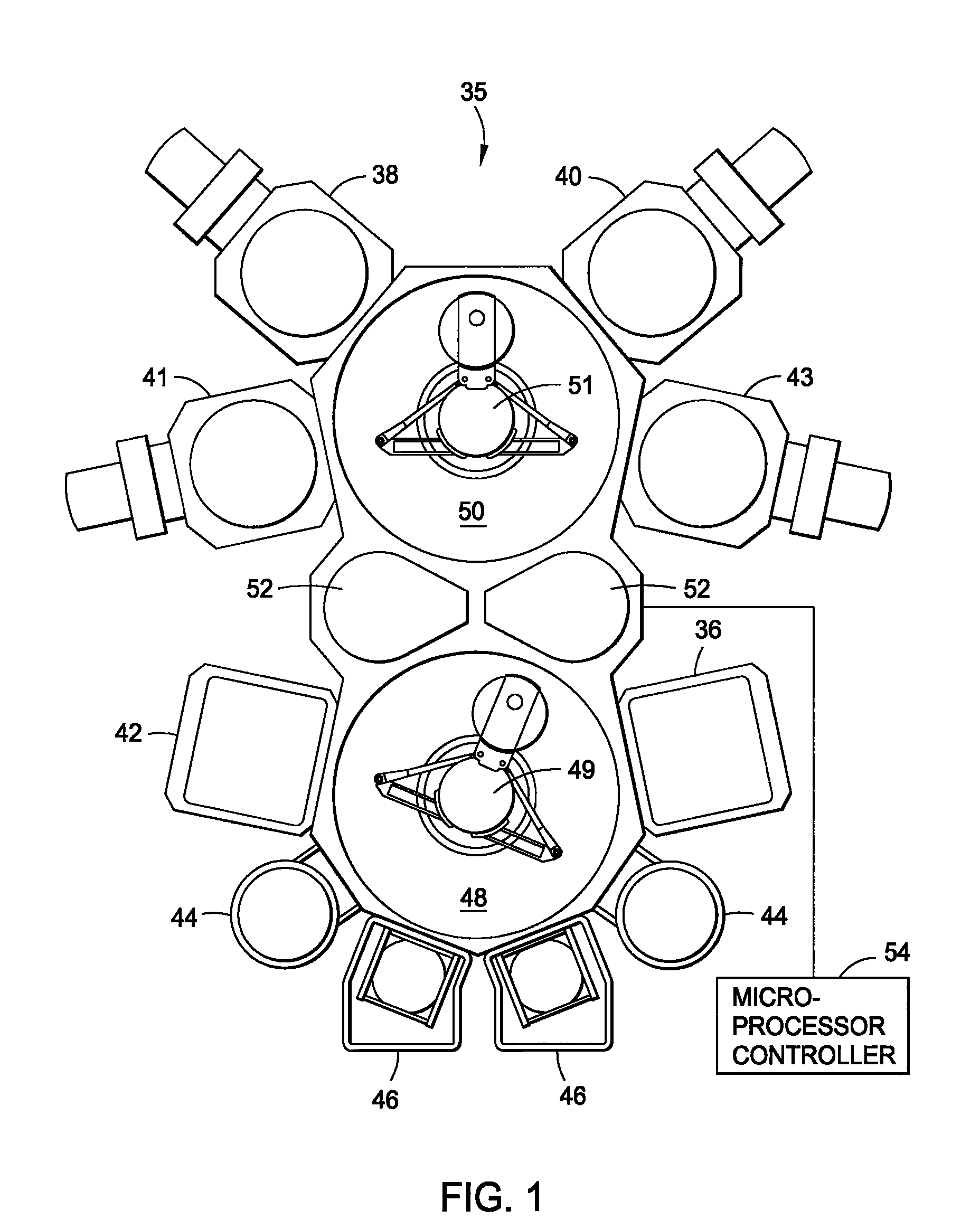

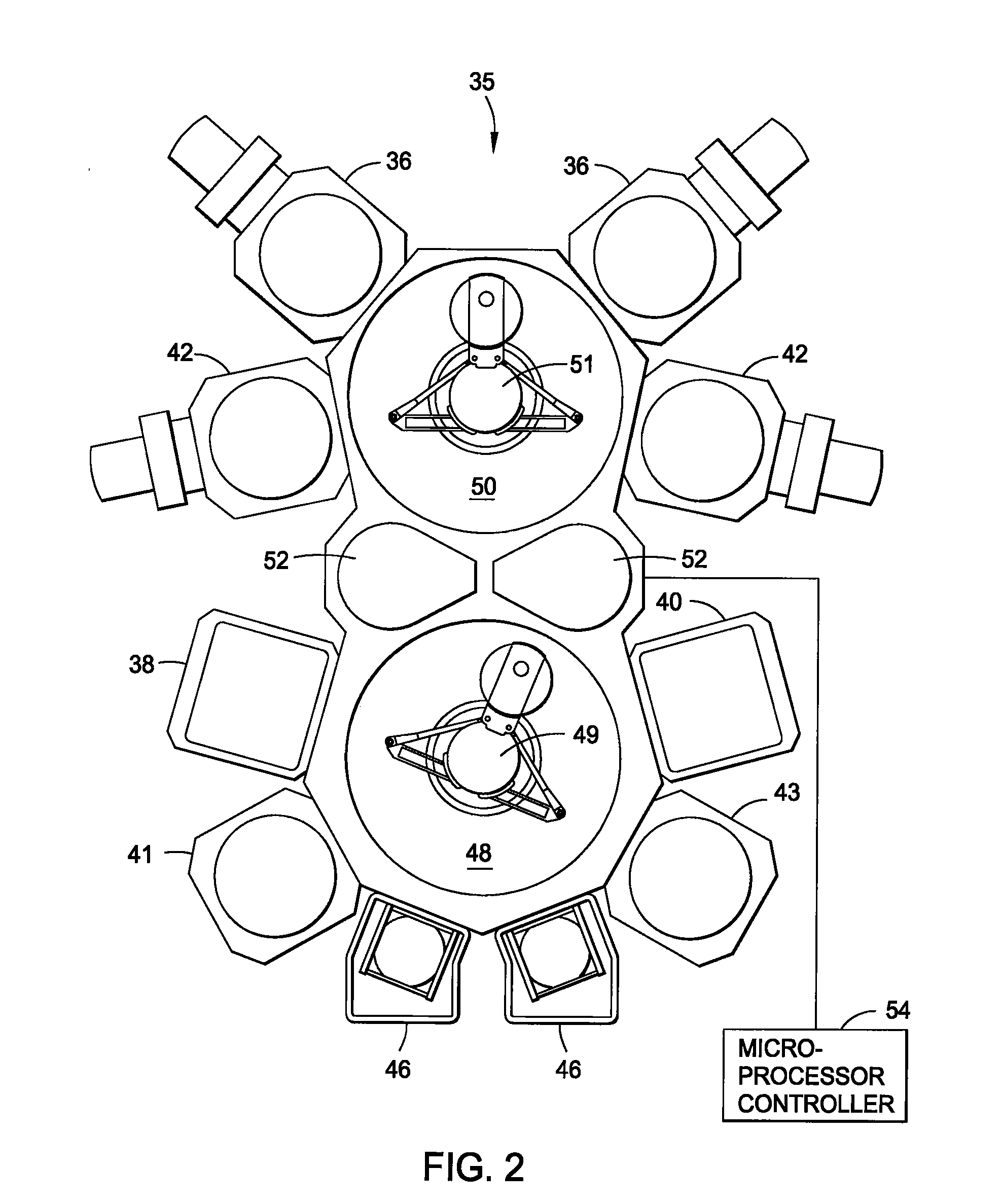

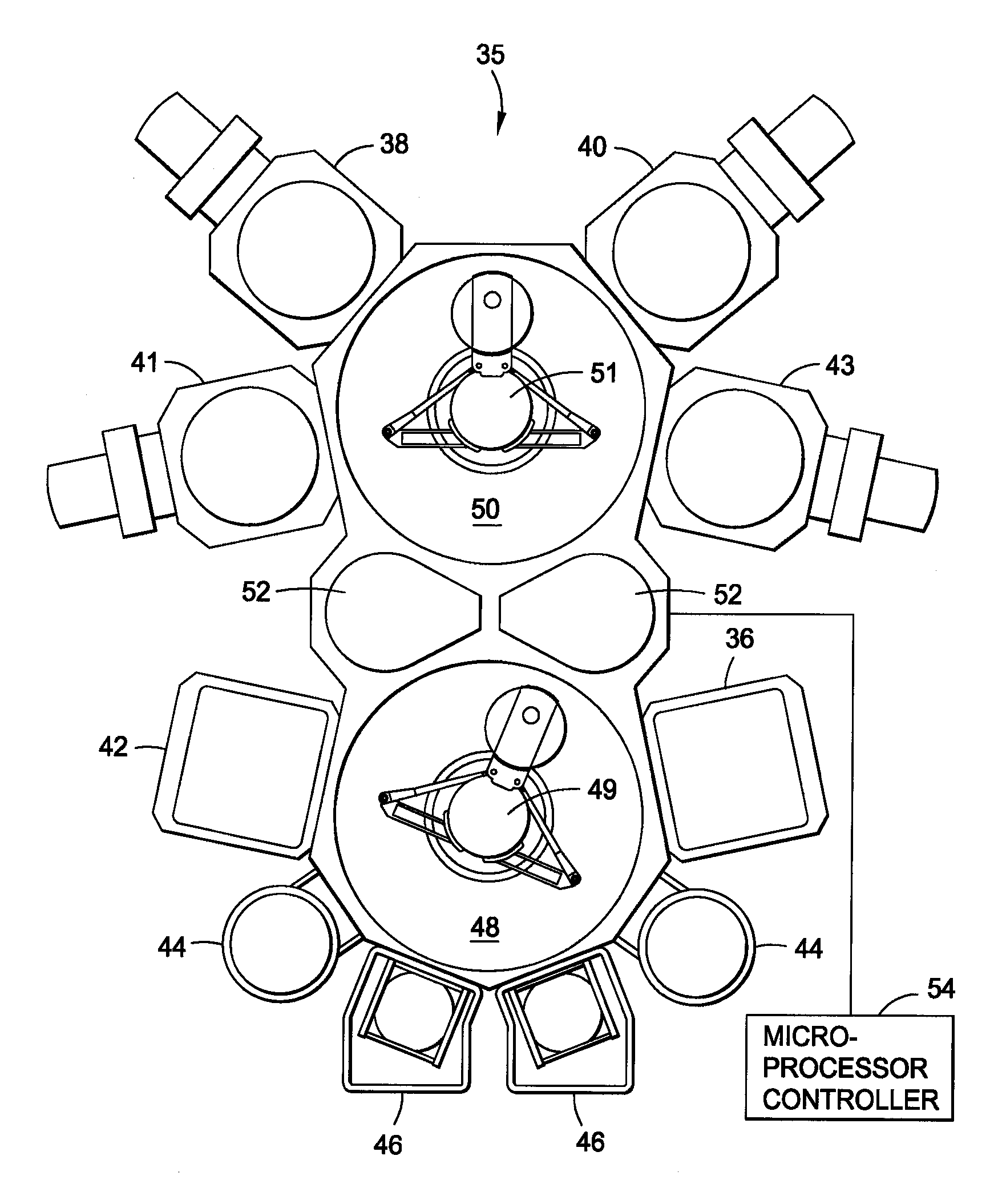

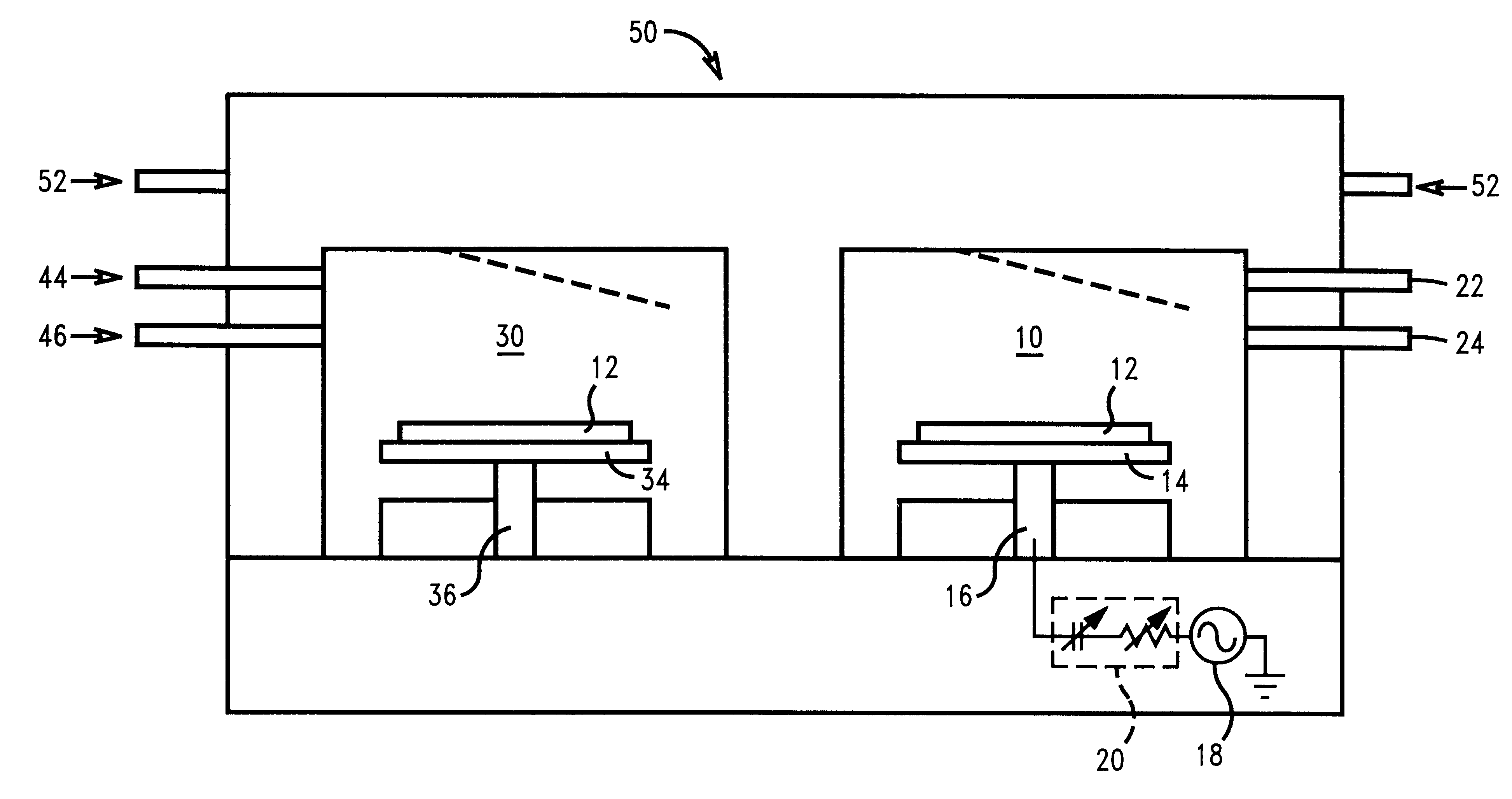

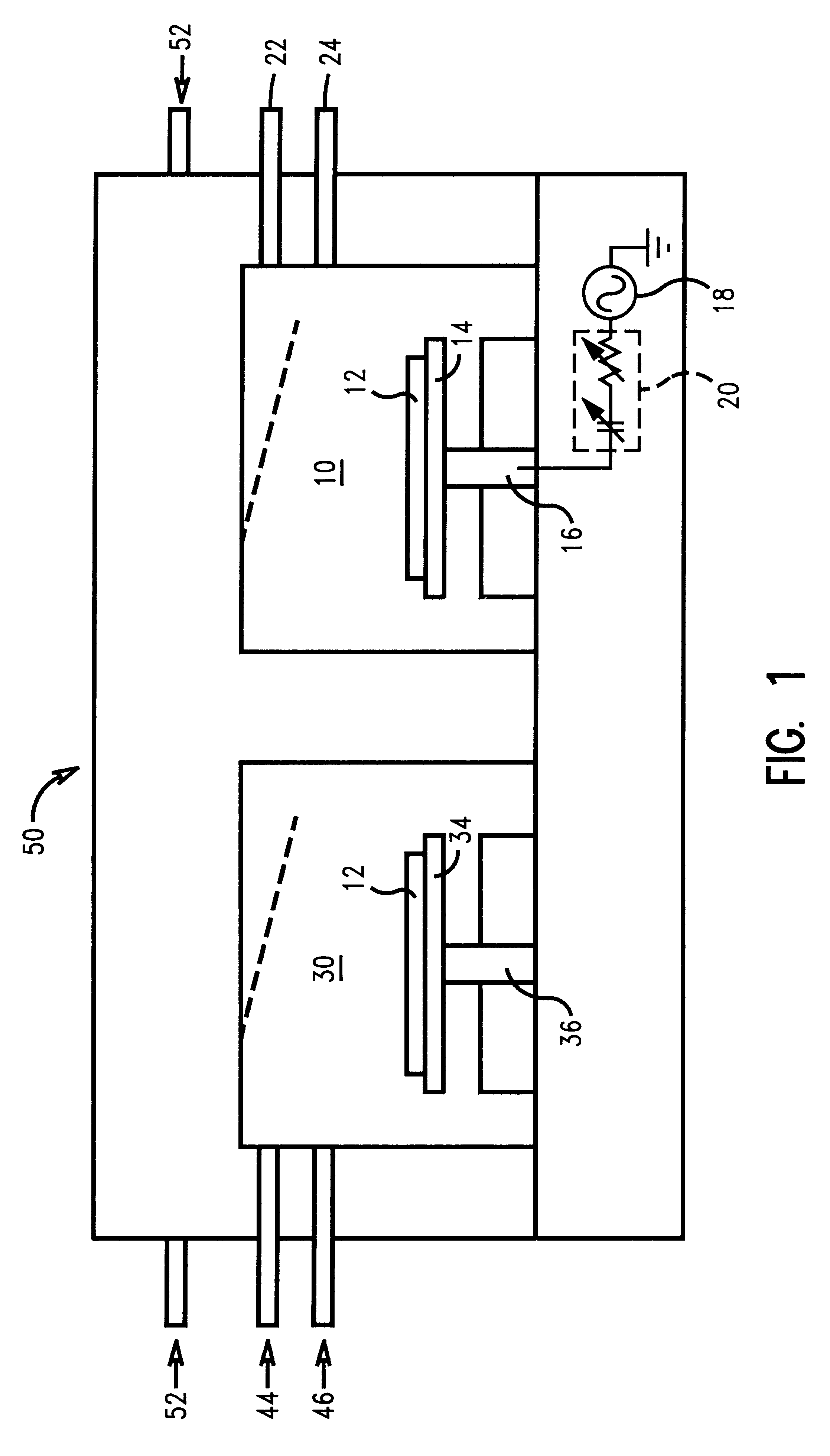

Integrated cobalt silicide process for semiconductor devices

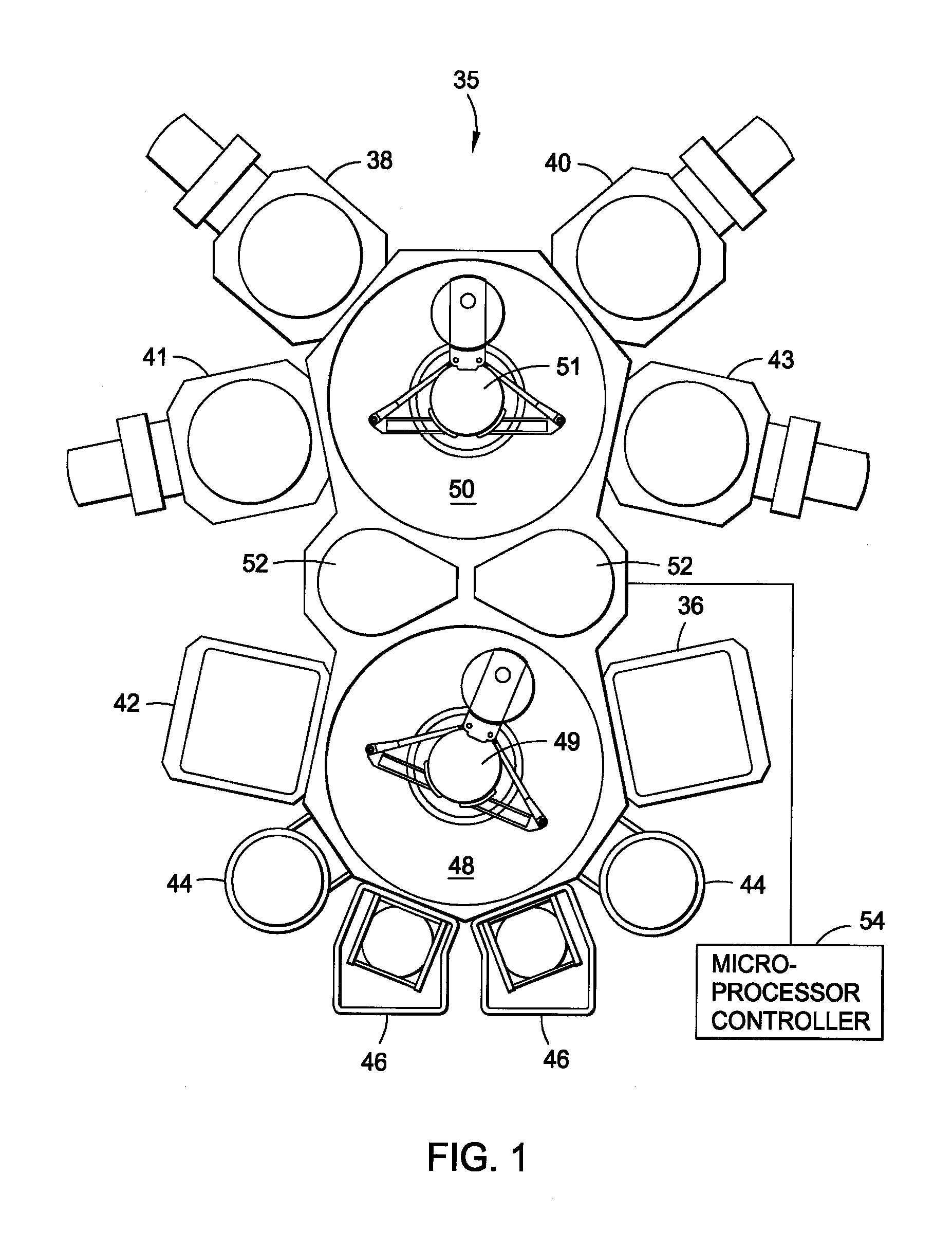

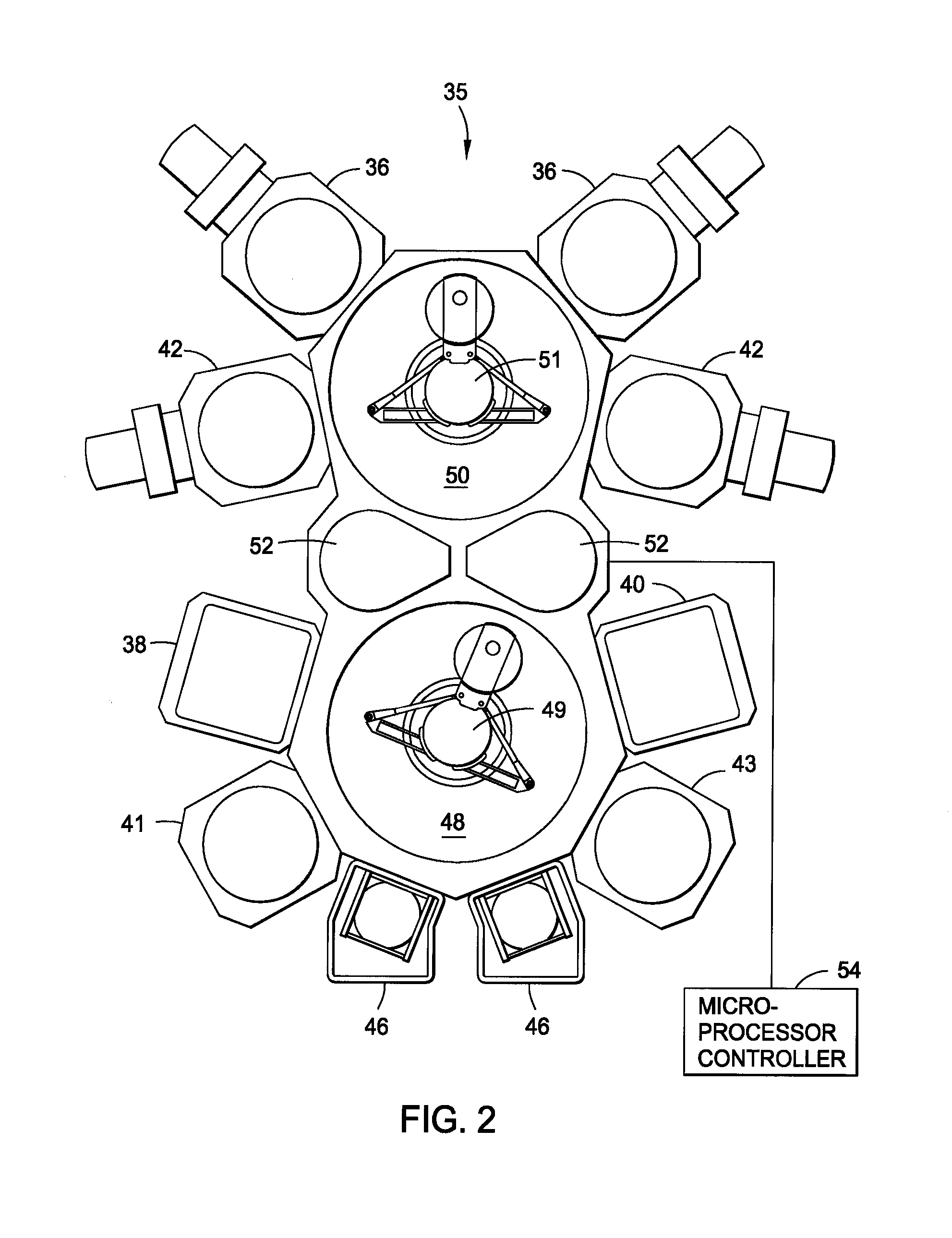

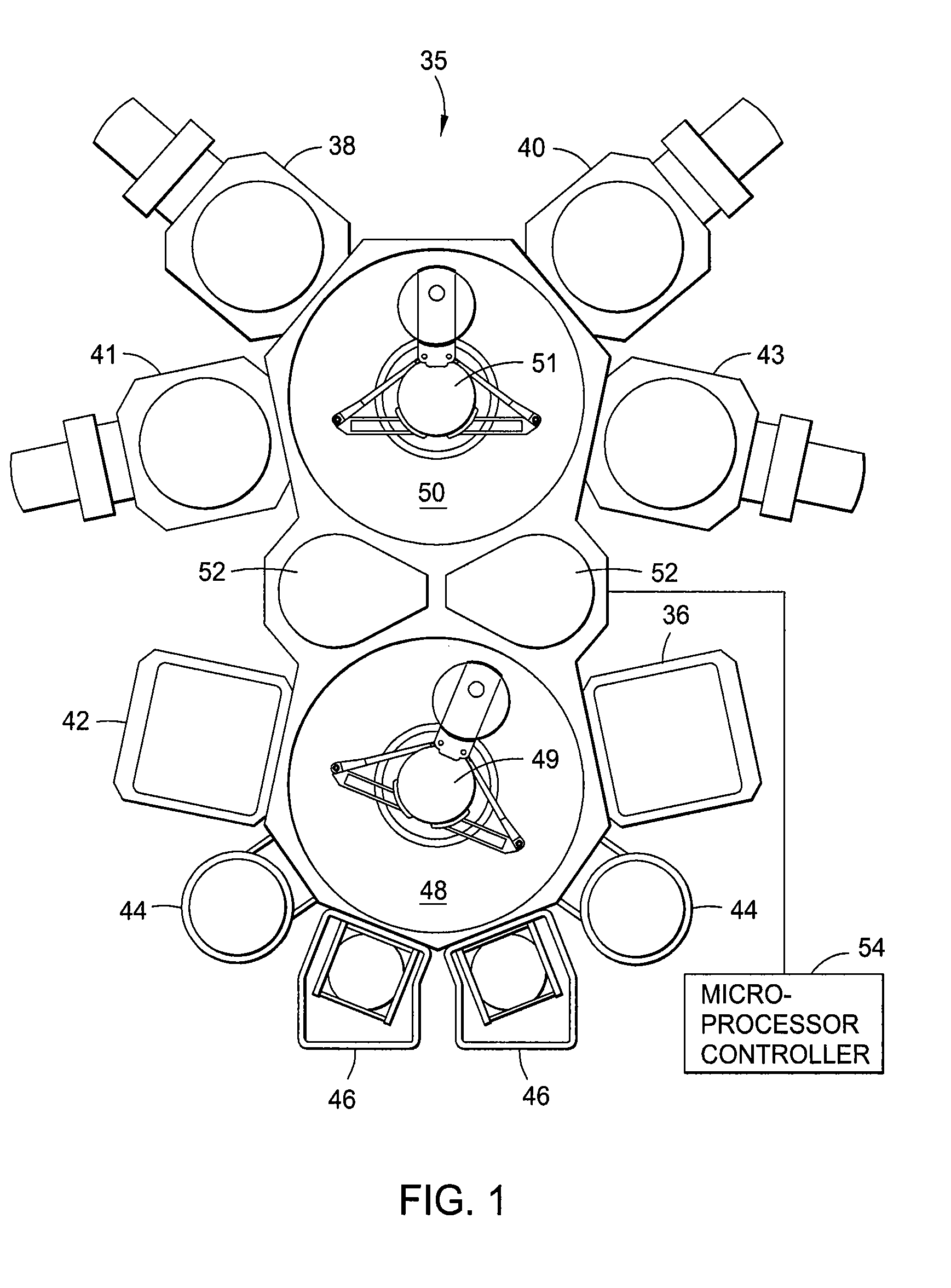

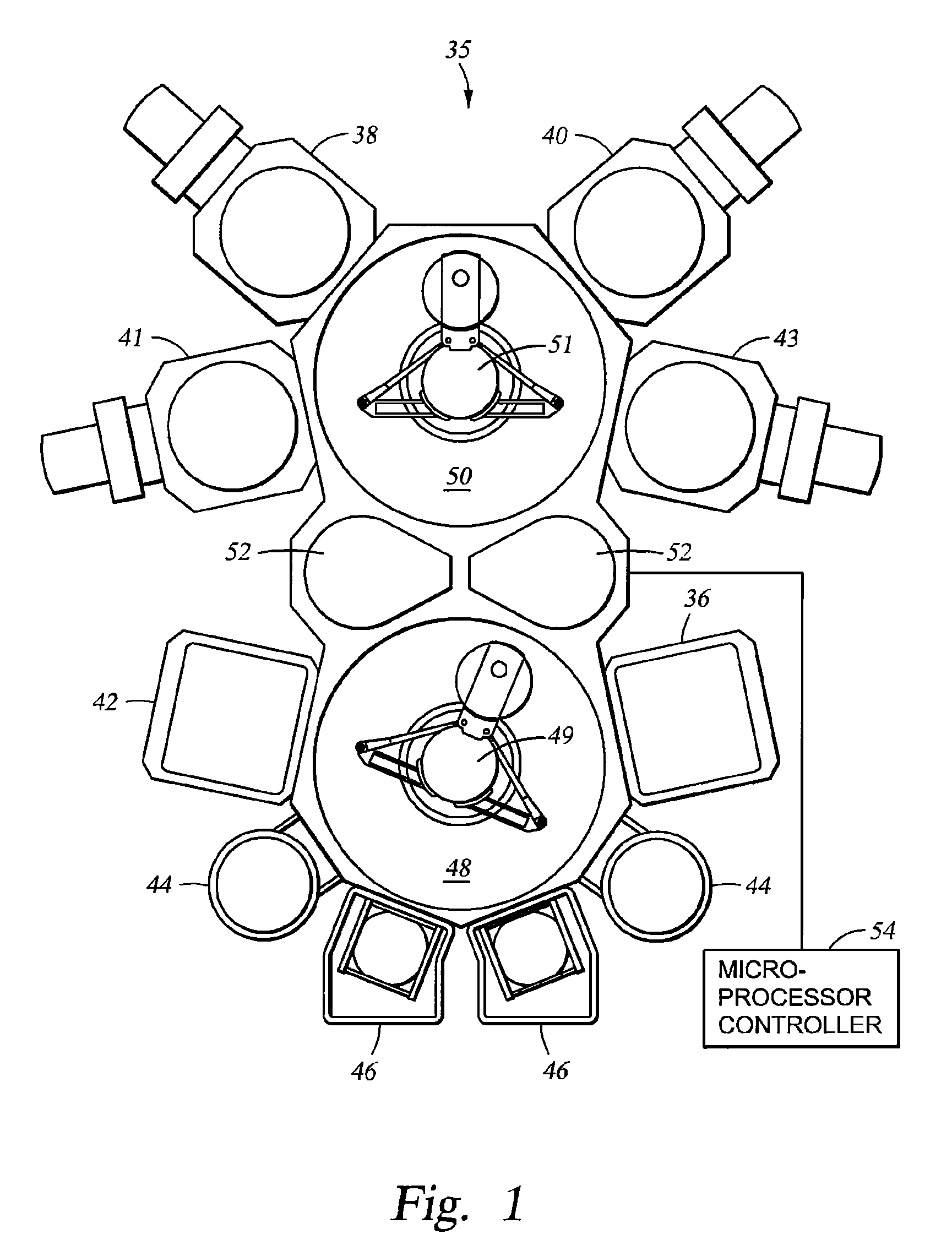

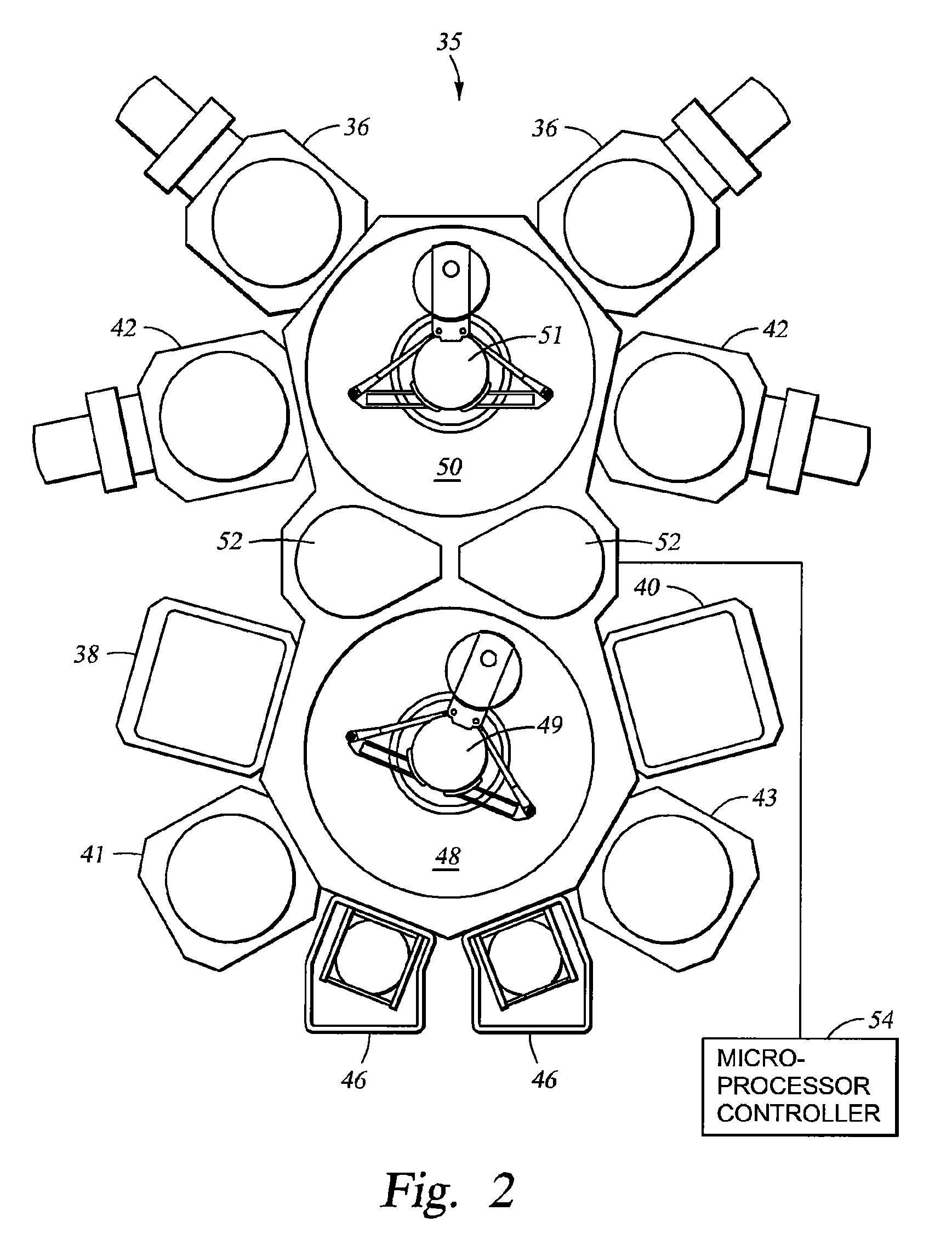

InactiveUS6184132B1Semiconductor/solid-state device manufacturingThin material handlingSalicideCobalt

A method and apparatus are provided for forming a silicide on a semiconductor substrate by integrating under a constant vacuum the processes of removing an oxide from a surface of a semiconductor substrate and depositing a metal on the cleaned surface without exposing the cleaned surface to air. The method and apparatus of the present invention eliminates the exposure of the cleaned substrate to air between the oxide removal and metal deposition steps. This in-situ cleaning of the silicon substrate prior to cobalt deposition provides a cleaner silicon substrate surface, resulting in enhanced formation of cobalt silicide when the cobalt layer is annealed.

Owner:GLOBALFOUNDRIES INC

Structure and method for enhanced uni-directional diffusion of cobalt silicide

InactiveUS20060057844A1Improves suicide processReducing Si consumptionSemiconductor/solid-state device detailsSolid-state devicesSelf limitingSilicon alloy

The present invention provides a method for enhancing uni-directional diffusion of a metal during silicidation by using a metal-containing silicon alloy in conjunction with a first anneal in which two distinct thermal cycles are performed. The first thermal cycle of the first anneal is performed at a temperature that is capable of enhancing the uni-directional diffusion of metal, e.g., Co and / or Ni, into a Si-containing layer. The first thermal cycle causes an amorphous metal-containing silicide to form. The second thermal cycle is performed at a temperature that converts the amorphous metal-containing silicide into a crystallized metal rich silicide that is substantially non-etchable as compared to the metal-containing silicon alloy layer or a pure metal-containing layer. Following the first anneal, a selective etch is performed to remove any unreacted metal-containing alloy layer from the structure. A second anneal is performed to convert the metal rich silicide phase formed by the two thermal cycles of the first anneal into a metal silicide phase that is in its lowest resistance phase. A metal silicide is provided whose thickness is self-limiting.

Owner:GLOBALFOUNDRIES INC

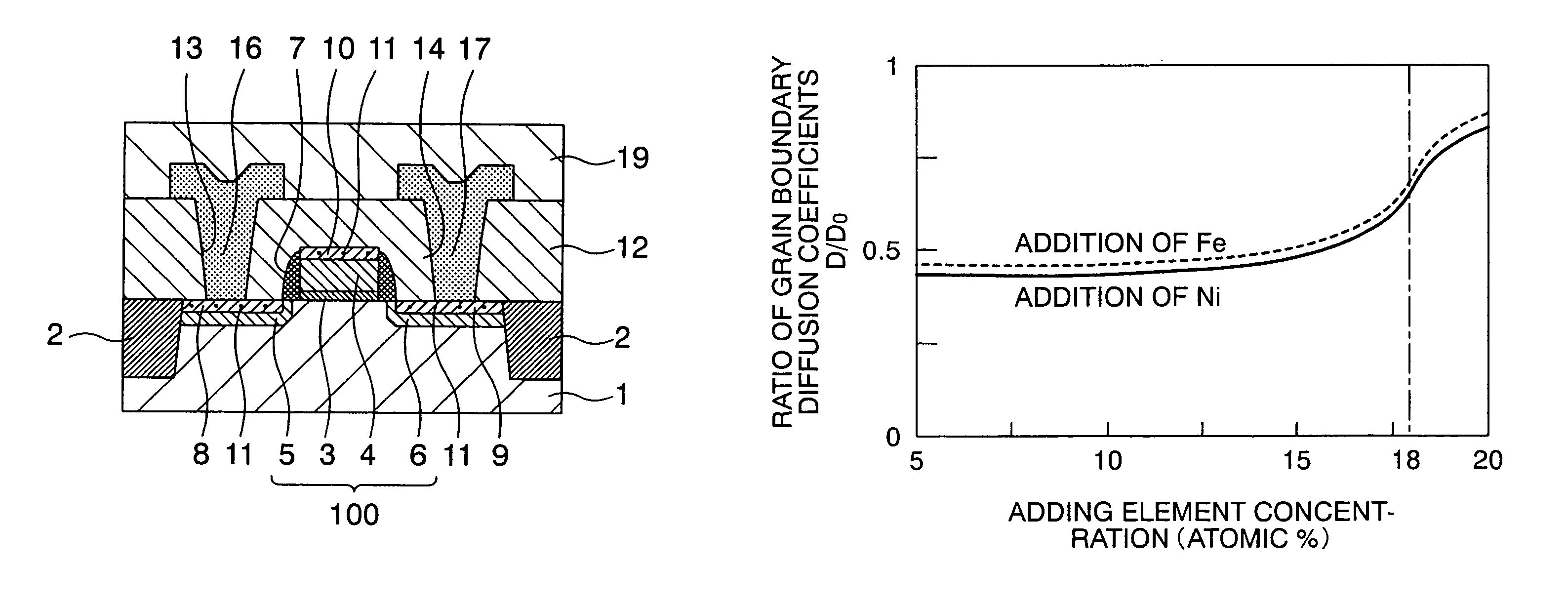

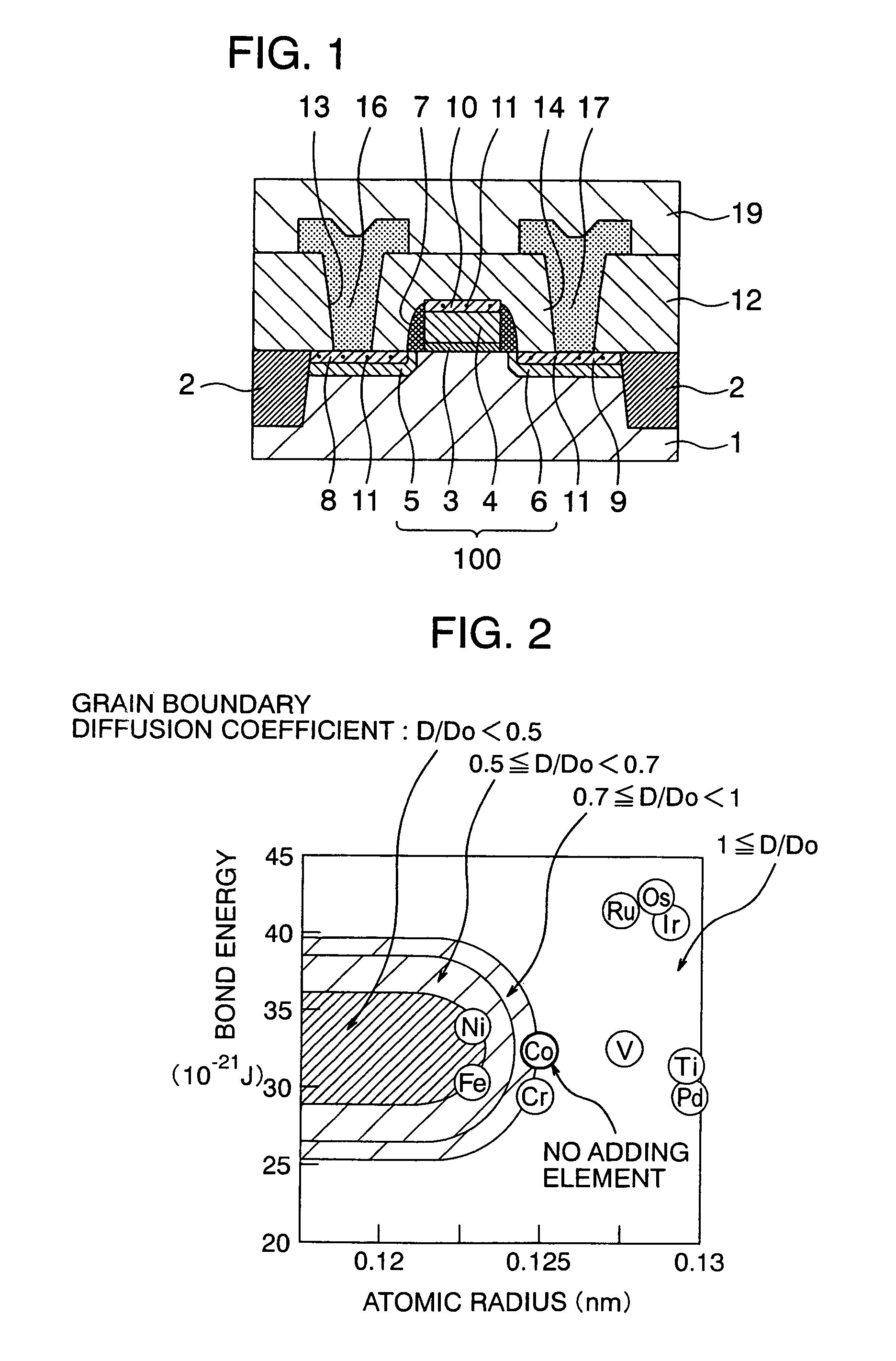

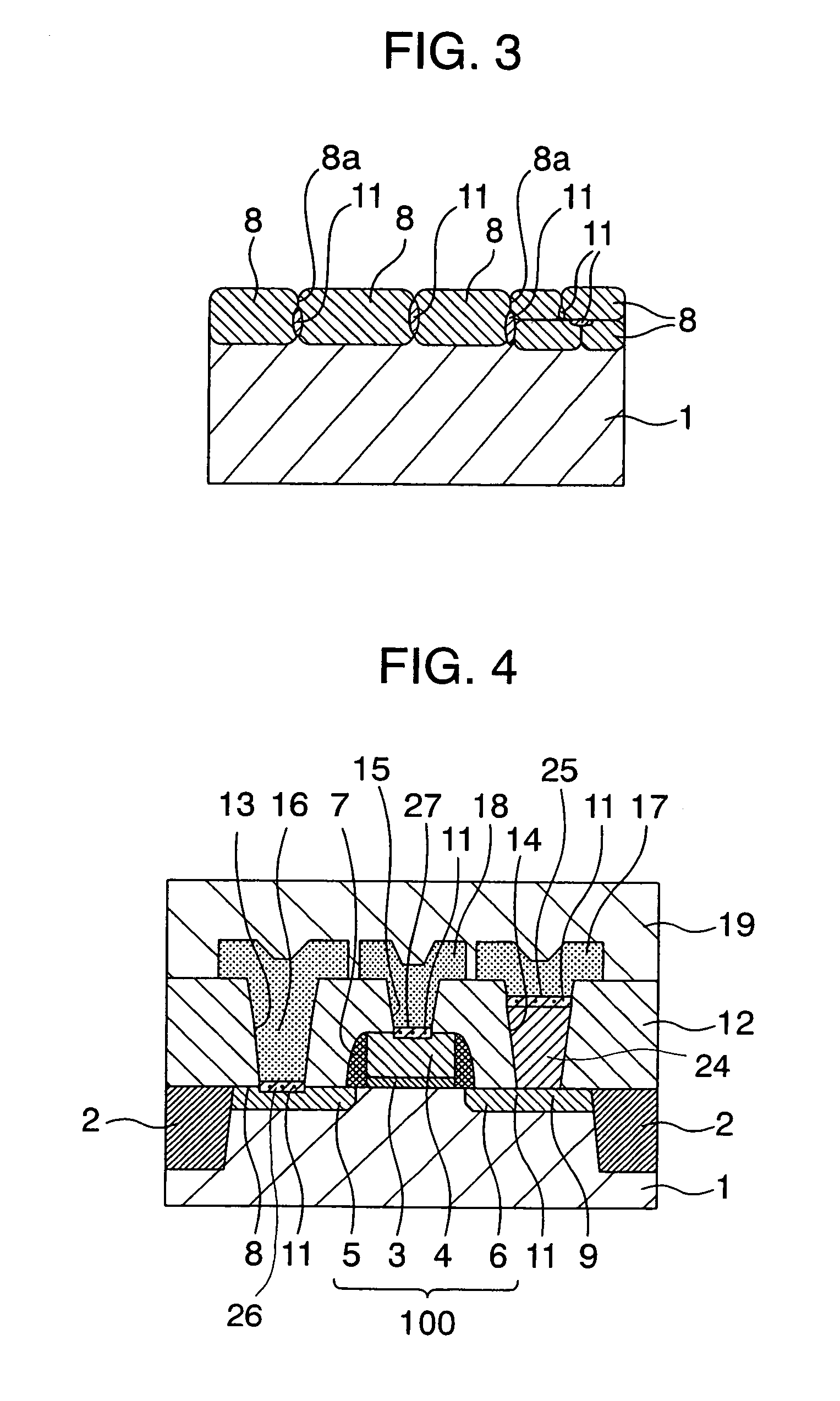

Semiconductor device and its production process

InactiveUS6960832B2Suppresses resistance riseInhibit grain boundary diffusionSemiconductor/solid-state device detailsSolid-state devicesCobalt silicideSemiconductor

Owner:RENESAS ELECTRONICS CORP

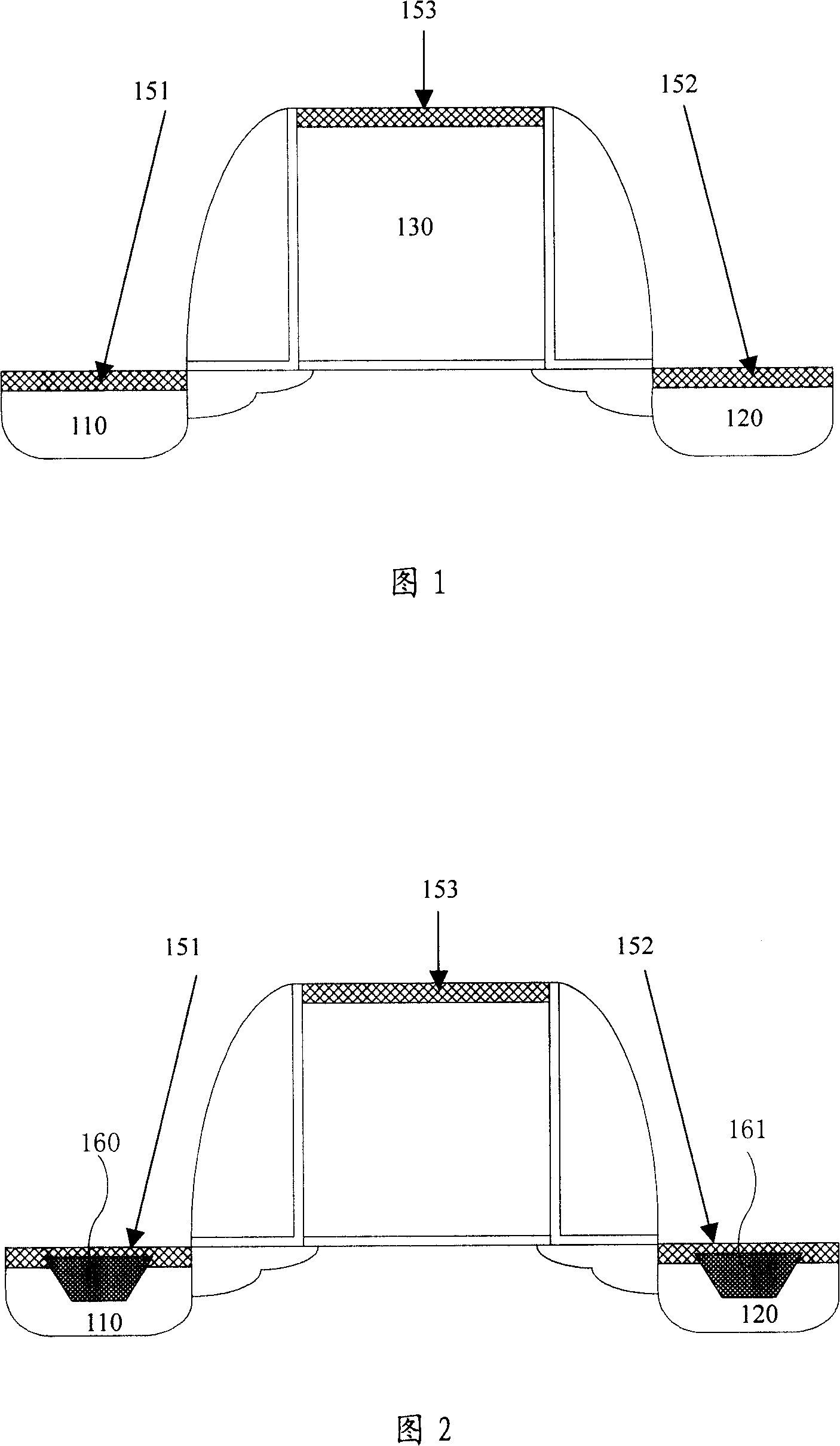

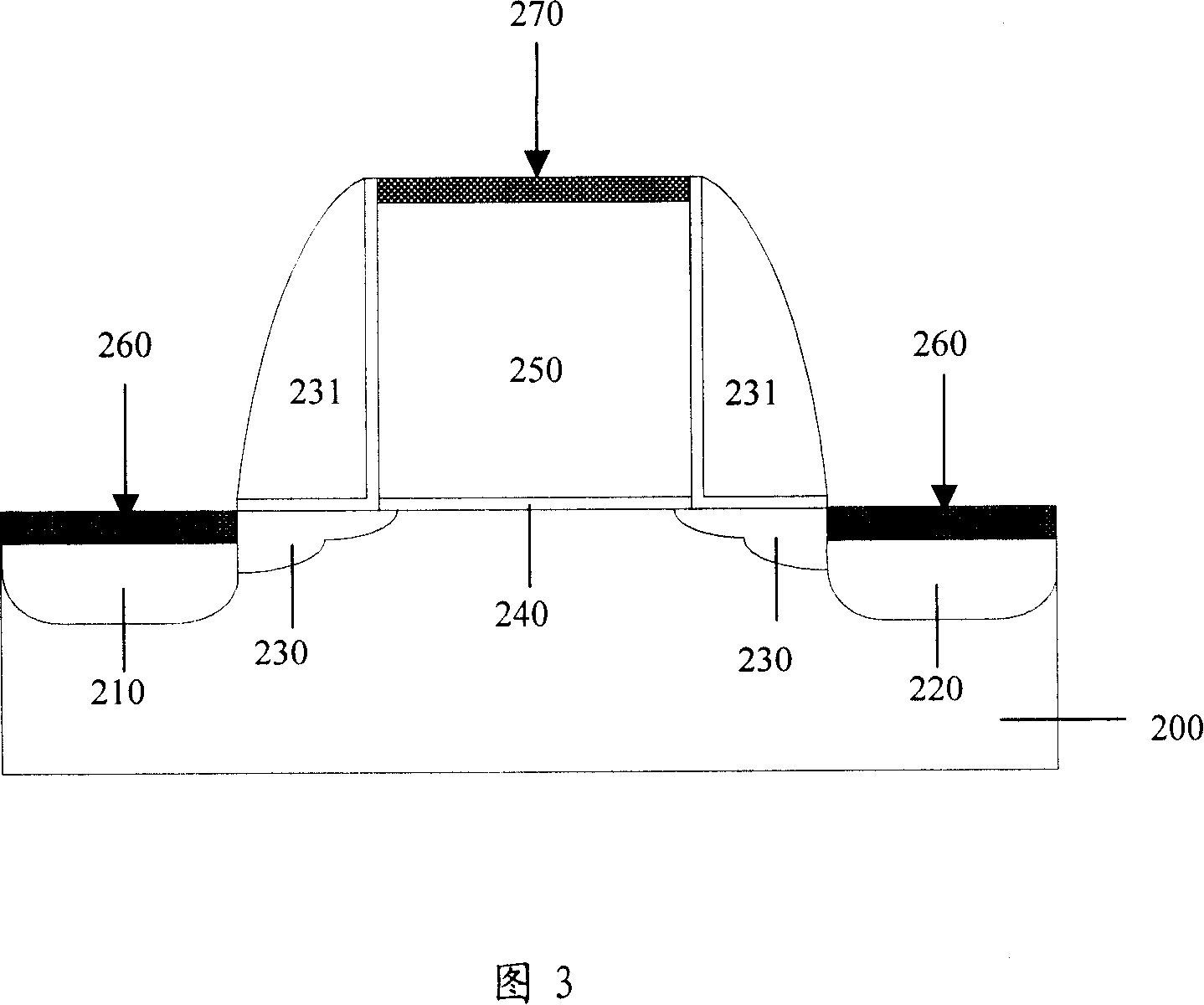

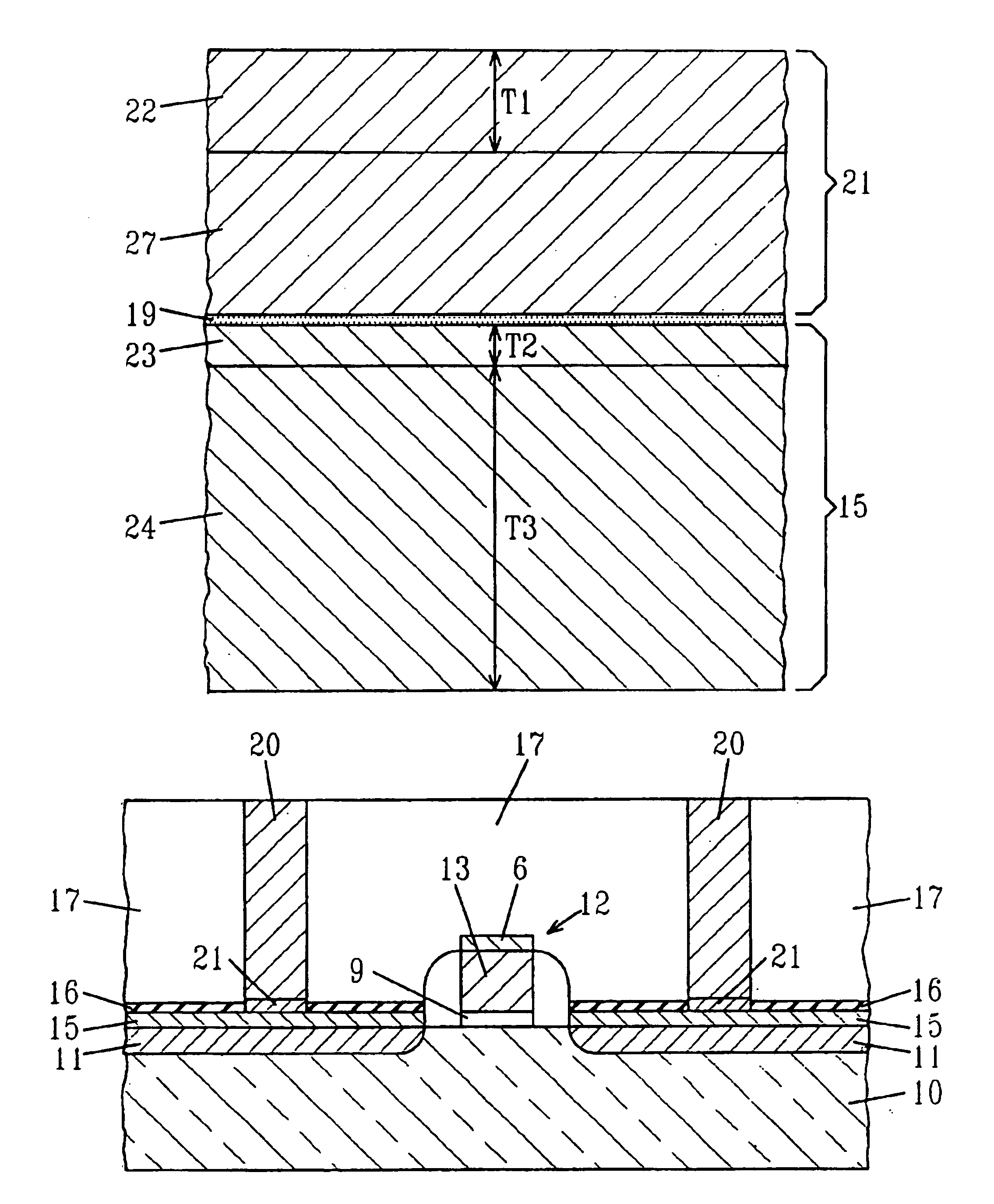

Semiconductor device and its making method

ActiveCN101123271AOvercome the lack of craftsmanshipReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideMetal silicide

The invention discloses a metal oxide semi-conductor device, which comprises a semi-conductor underlayer, a grid structure formed on the surface of the underlayer, and the two sides of which have side wall isolators, a source electrode area and a drain electrode area positioned on the two sides of the side wall isolators on the underlayer, a first metal silicide positioned on the source electrode area and the drain electrode area, and a second silicide positioned on the grid structure. The manufacturing method of semi-conductor devices of the invention forms respectively the first metal silicide containing the first and the second metal, and forms the second silicide containing the second metal. The invention combines the advantages of both the cobalt silicide techniques and the nickel silicide techniques, and applies well the nickel silicide techniques to the following technique nodes below 65nm. The invention reduces the risk of forming spriking in the source / drain area, when assuring the formation of metal contact layer of high reliability on the surface of the grid by using nickel silicide.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Pre-anneal of CoSi, to prevent formation of amorphous layer between Ti-O-N and CoSi

InactiveUS6878624B1Controlled diffusionSemiconductor/solid-state device detailsSolid-state devicesSalicideNitrogen

The present invention provides a method for forming an interconnect to a cobalt or nickel silicide having a TiN diffusion barrier. The inventive method comprises providing an initial structure having vias to exposed silicide regions positioned on a substrate; annealing the initial structure in a nitrogen-containing ambient, wherein a nitrogen passivation layer is formed atop the exposed silicide region; depositing Ti atop the nitrogen passivation layer; annealing the Ti in a nitrogen-containing ambient to form a TiN diffusion barrier and an amorphous Ti cobalt silicide between the TiN diffusion layer and the cobalt or nickel silicide and depositing an interconnect metal within the vias and atop the TiN diffusion barrier. The nitrogen passivation layer substantially restricts diffusion between the Ti and silicide layers minimizing the amorphous Ti cobalt silicide layer that forms. Therefore, the amorphous Ti cobalt or Ti nickel silicide is restricted to a thickness of less than about 3.0 nm.

Owner:GLOBALFOUNDRIES INC

Methods for forming cobalt layers including introducing vaporized cobalt precursors and methods for manufacturing semiconductor devices using the same

InactiveUS7172967B2Good step coverageSemiconductor/solid-state device manufacturingSemiconductor devicesCobaltCobalt silicide

The present invention provides methods for forming cobalt silicide layers, including introducing a vaporized cobalt precursor onto a silicon substrate to form a cobalt layer. The vaporized cobalt precursor has the formula Co2(CO)6(R1—C≡C—R2), wherein R1 is H or CH3, and R2 is H, t-butyl, methyl or ethyl. The silicon substrate is thermally treated so that silicon is reacted with cobalt to form a cobalt silicide layer. Methods for manufacturing semiconductor devices including the cobalt silicide layers described herein and such devices are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

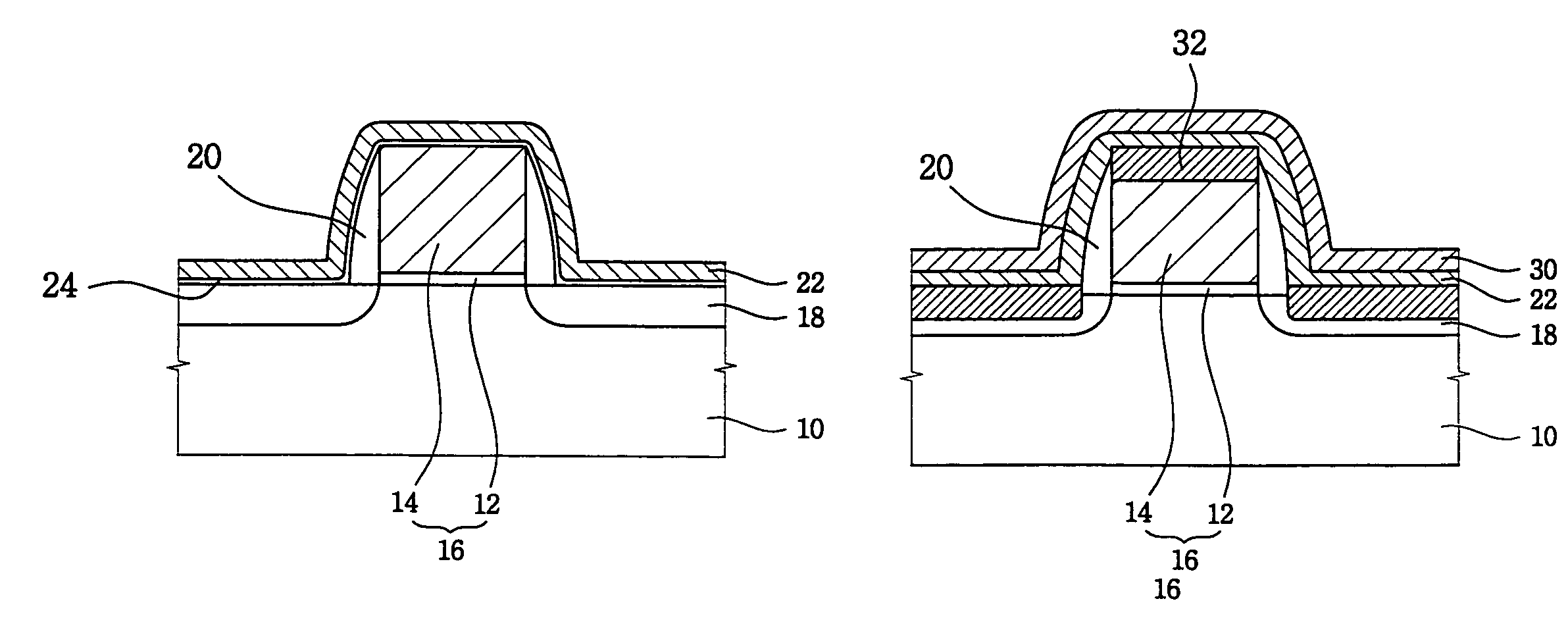

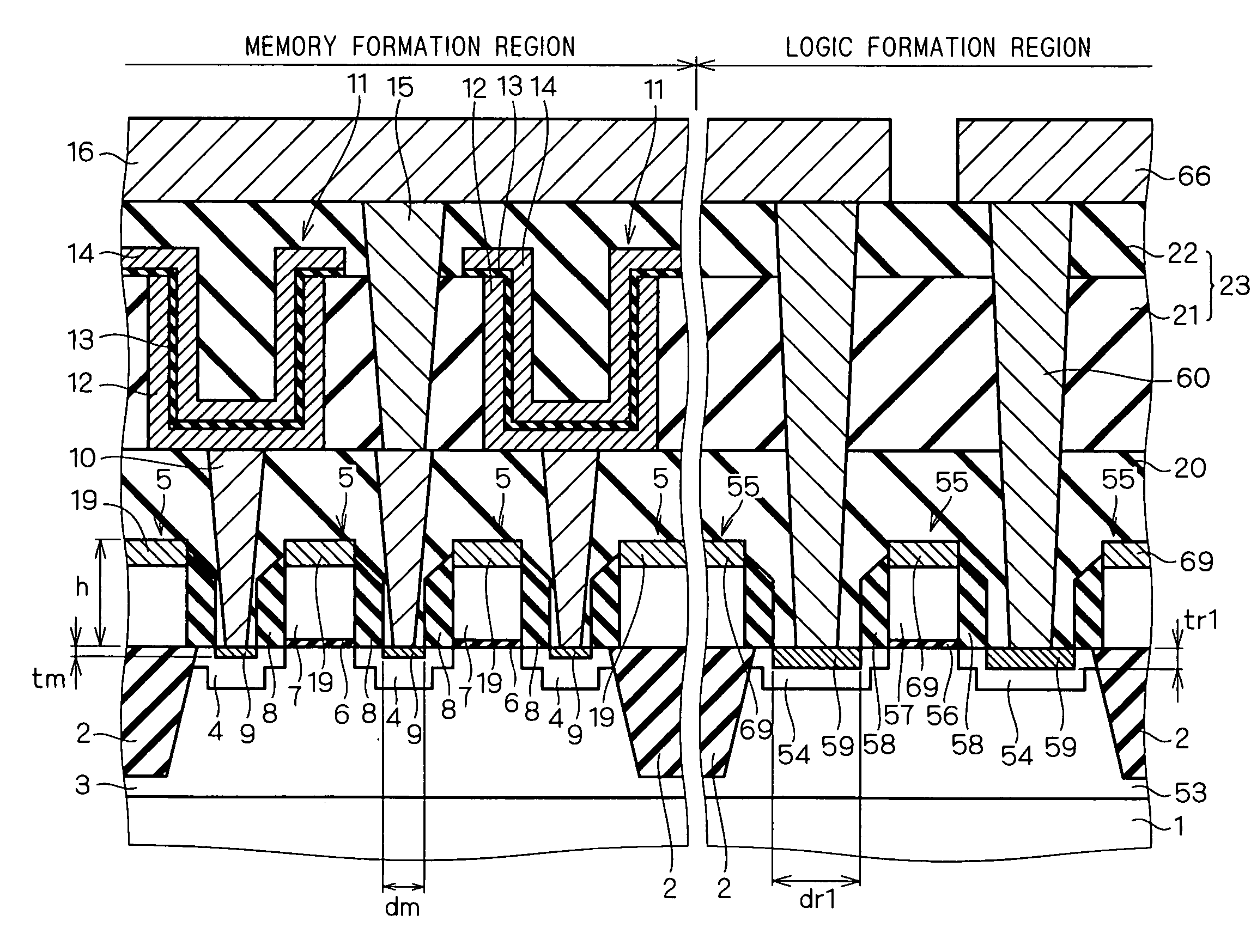

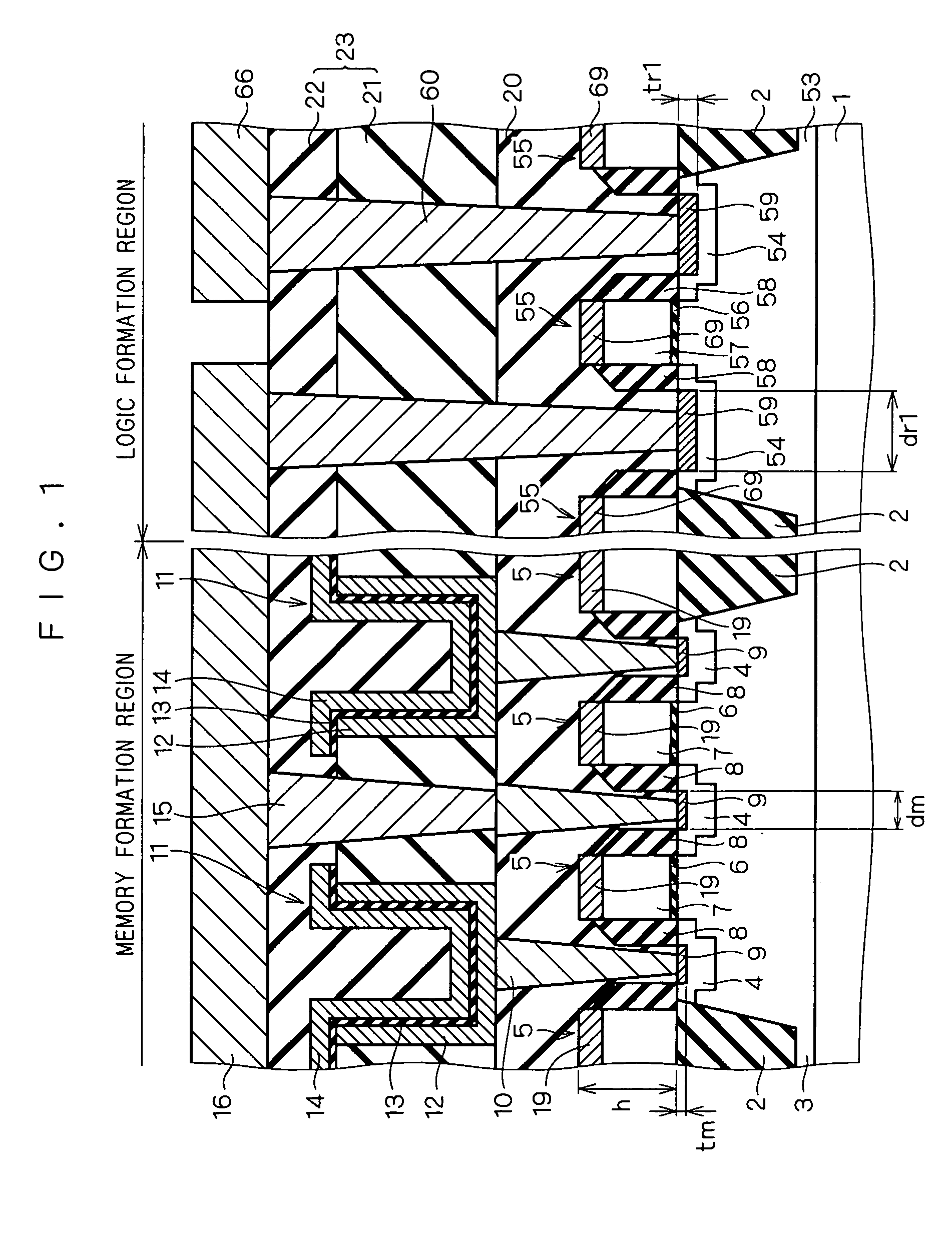

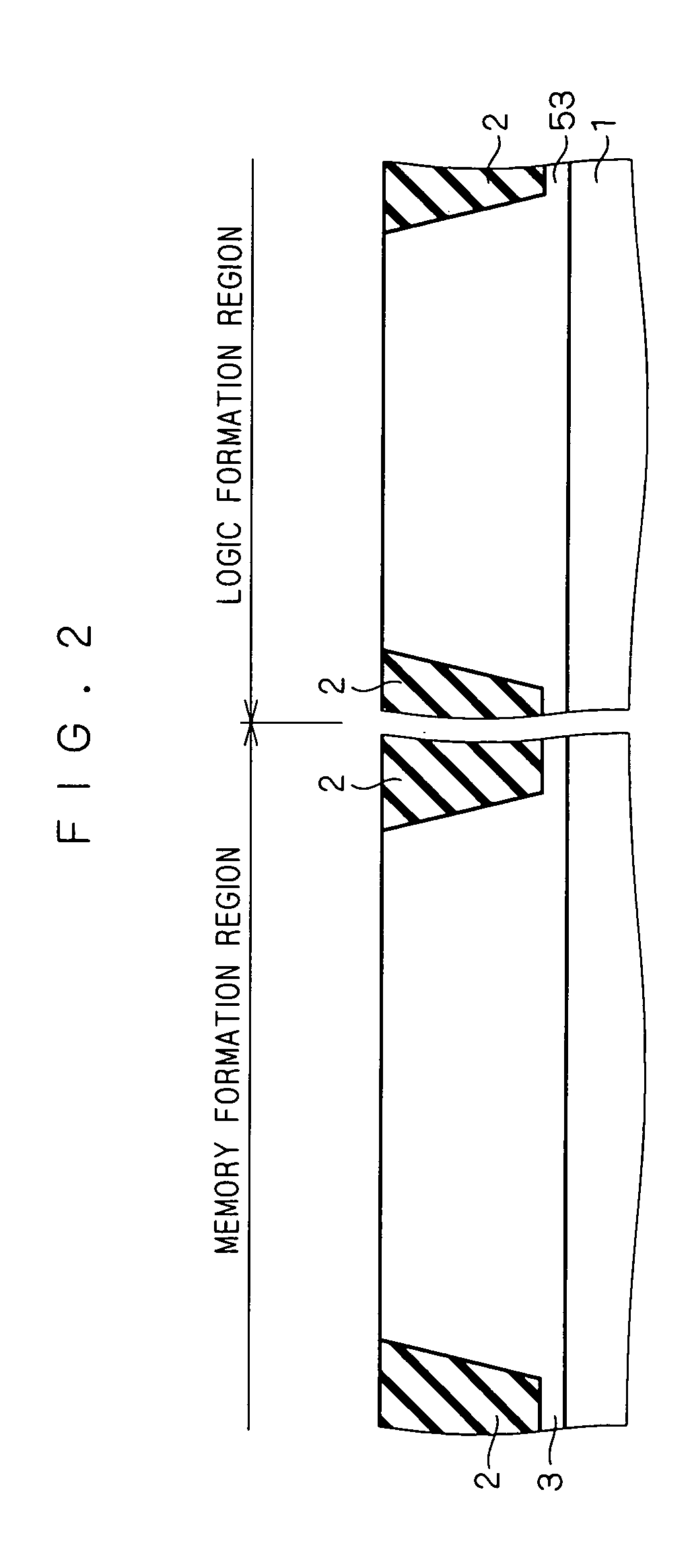

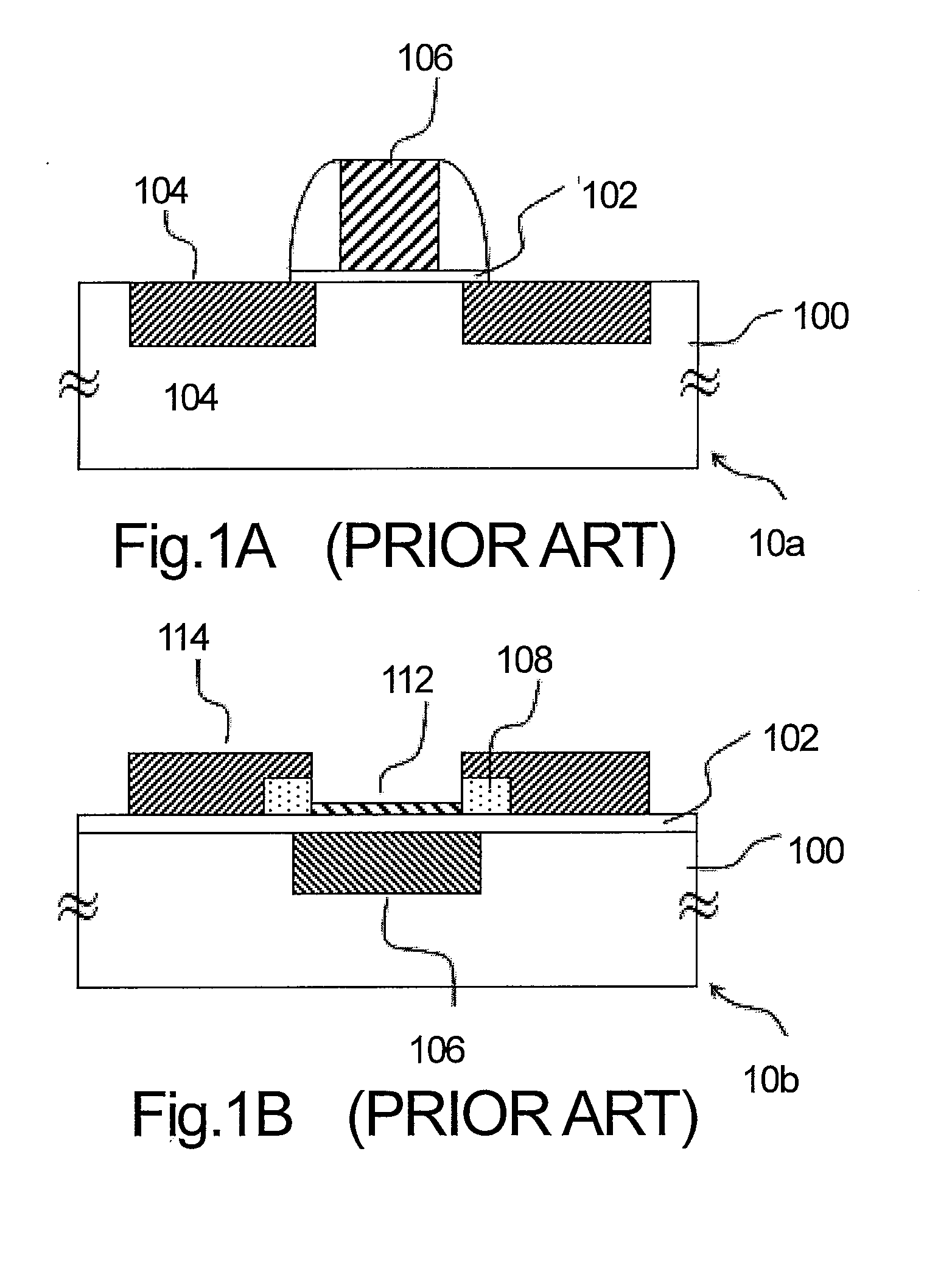

Semiconductor device having memory and logic devices with reduced resistance and leakage current

ActiveUS7078758B2Reduce resistanceReduce leakage currentTransistorSolid-state devicesMemory formationEngineering

A semiconductor technique is provided which can achieve both of lowered resistance in a logic formation region and reduced leakage current of the capacitor of a memory device. Source / drain regions (4) are formed in the upper surface of a semiconductor substrate (1) in a memory formation region and cobalt silicide films (9) are formed in the upper surfaces of the source / drain regions (4). Source / drain regions (54) are formed in the upper surface of the semiconductor substrate (1) in a logic formation region and cobalt silicide films (59) are formed in the upper surfaces of the source / drain regions (54). The cobalt silicide films (59) in the logic formation region are thicker than the cobalt silicide films (9) in the memory formation region.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing the same

ActiveUS20080035990A1Eliminate side effectsStructure of deviceTransistorSolid-state devicesDevice materialElectrode pair

A gate trench 13 is formed in a semiconductor substrate 10. The gate trench 13 is provided with a gate electrode 16 formed over a gate insulating film 14. A portion of the gate electrode 16 protrudes from the semiconductor substrate 10, and a sidewall 24 is formed over a side wall portion of the protruding portion. A body trench 25 is formed in alignment with an adjacent gate electrode 16. A cobalt silicide film 28 is formed over a surface of the gate electrode 16 and over a surface of the body trench 25. A plug 34 is formed using an SAC technique.

Owner:RENESAS ELECTRONICS CORP

Method and apparatus for using cobalt silicided polycrystalline silicon for a one time programmable non-volatile semiconductor memory

A fusible link formed on a semiconductor substrate. The fusible link comprises a silicide layer overlying a polysilicon layer. The fusible link is programmed to an open state by passing a current therethrough that opens the polysilicon and the silicide layers.

Owner:AVAGO TECH INT SALES PTE LTD

Methods for forming cobalt layers including introducing vaporized cobalt precursors and methods for manufacturing semiconductor devices using the same

InactiveUS20050064706A1Good step coverageSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCobalt

The present invention provides methods for forming cobalt silicide layers, including introducing a vaporized cobalt precursor onto a silicon substrate to form a cobalt layer. The vaporized cobalt precursor has the formula Co2(CO)6(R1—C≡C—R2), wherein R1 is H or CH3, and R2 is H, t-butyl, methyl or ethyl. The silicon substrate is thermally treated so that silicon is reacted with cobalt to form a cobalt silicide layer. Methods for manufacturing semiconductor devices including the cobalt silicide layers described herein and such devices are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

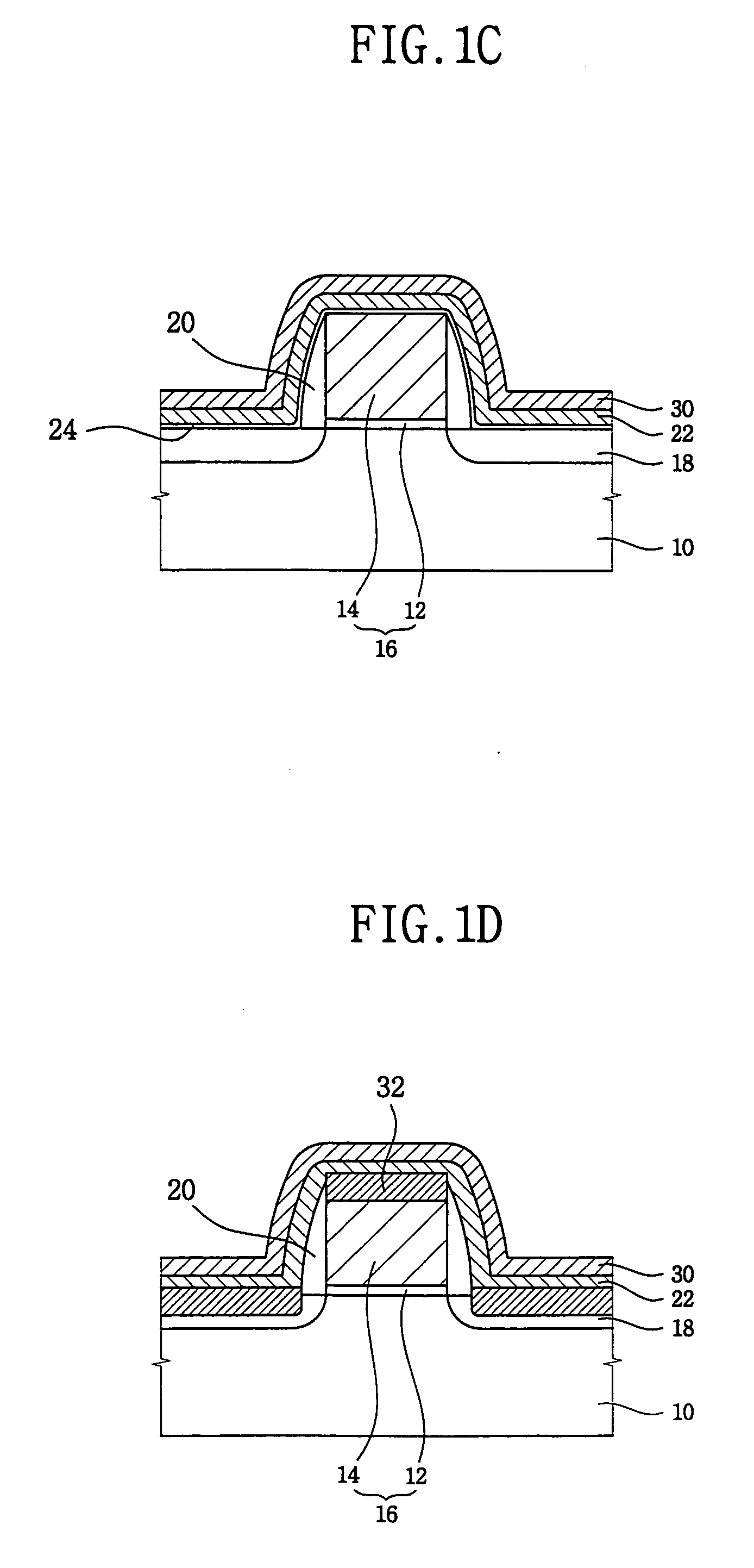

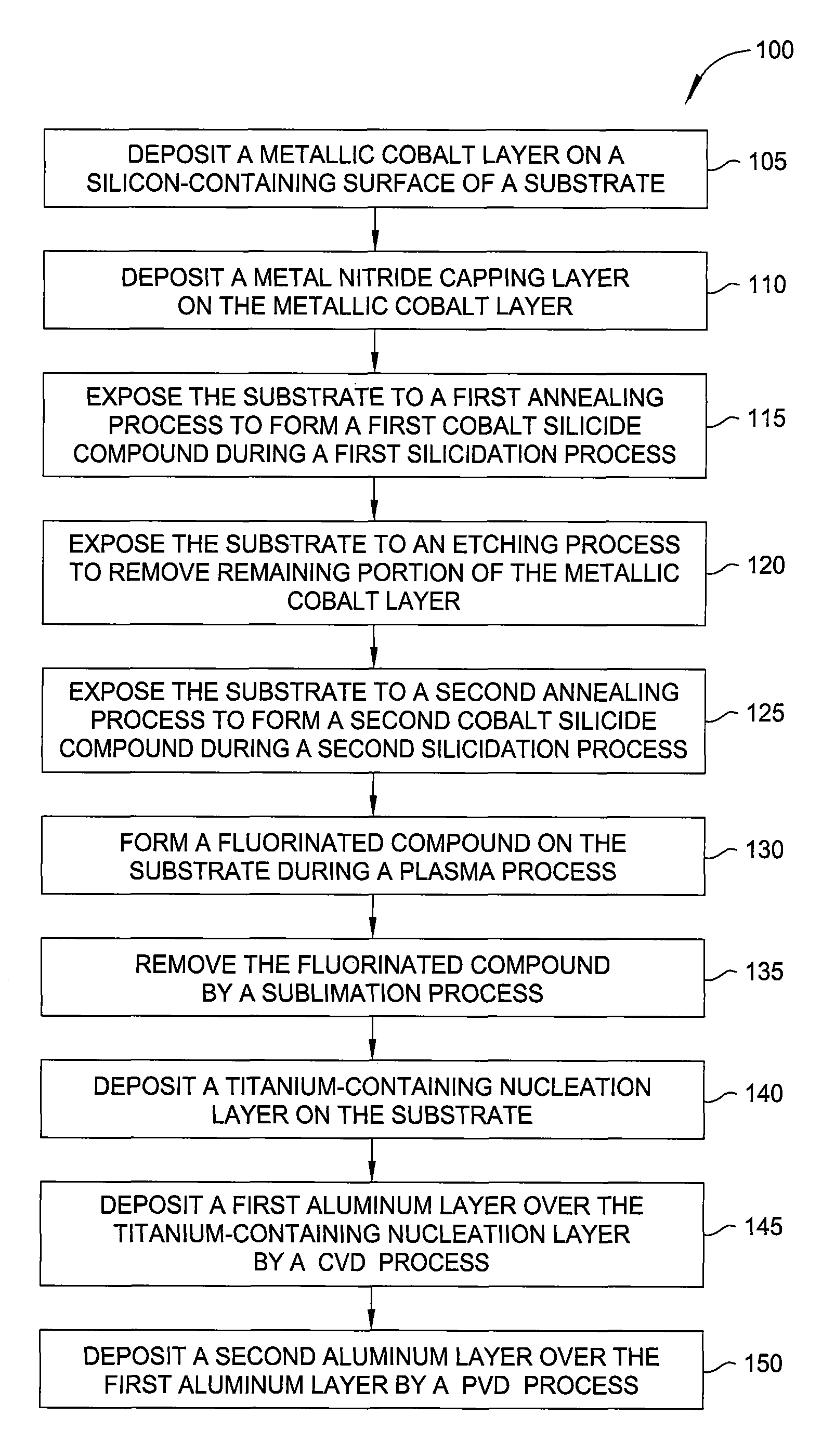

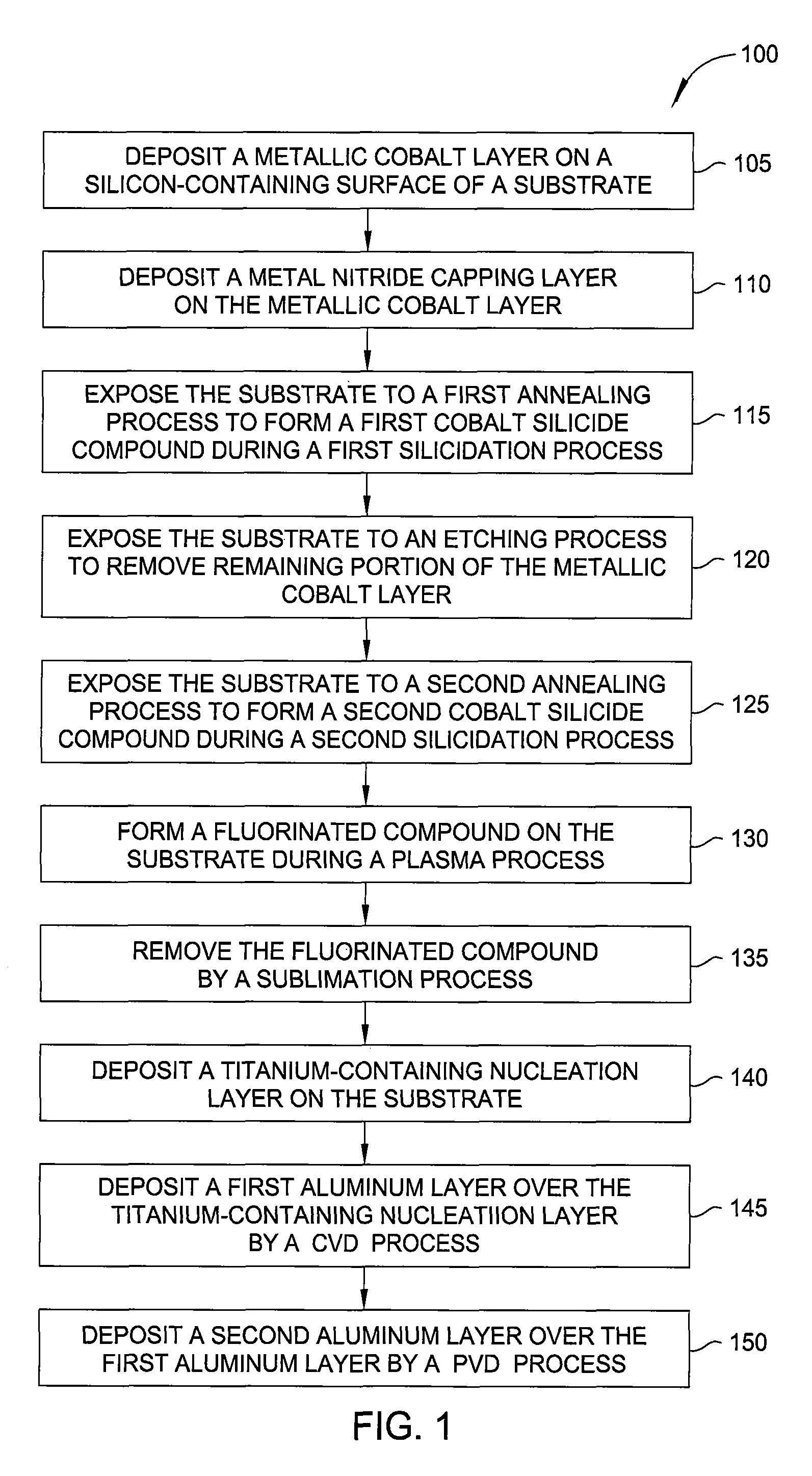

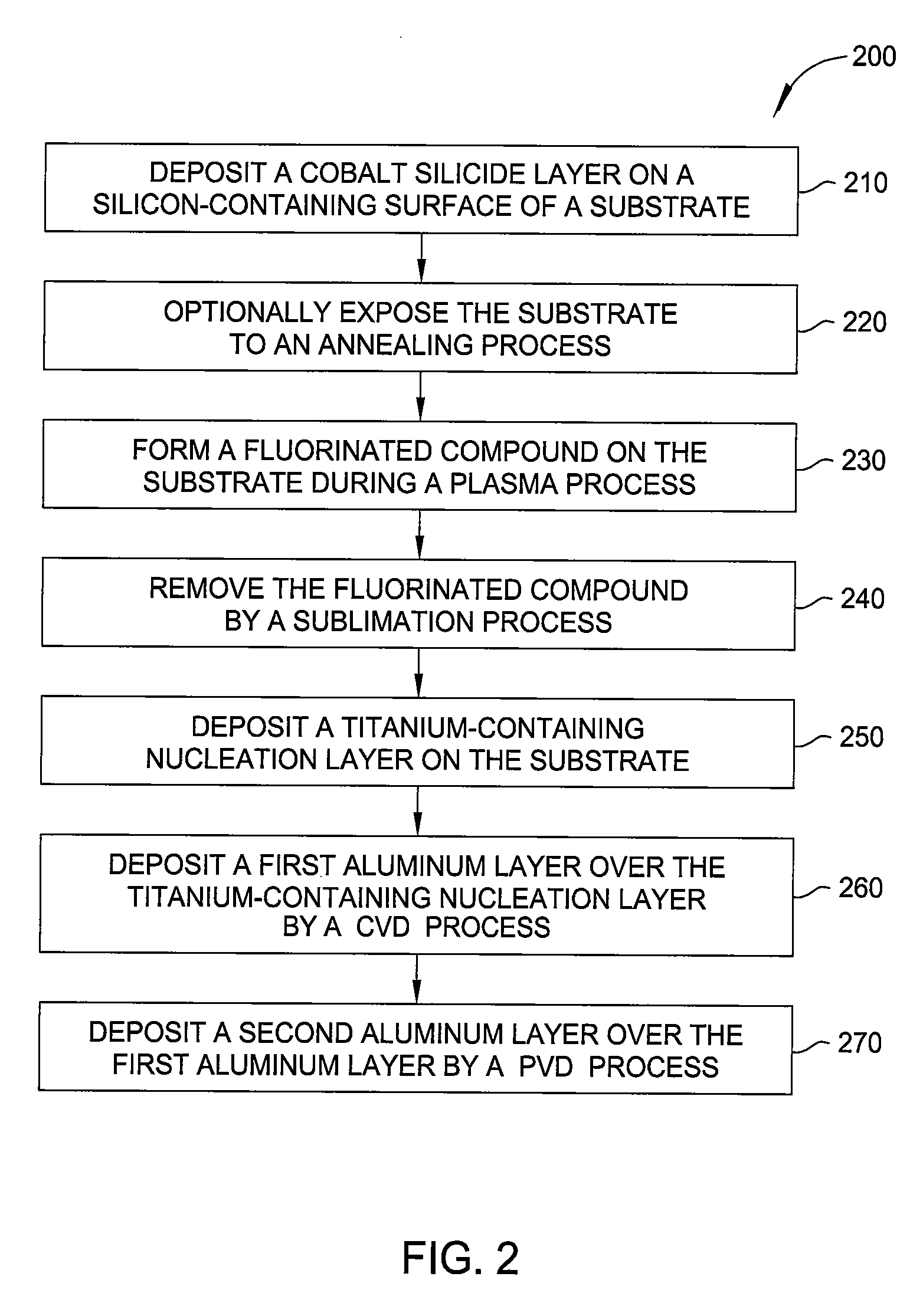

Aluminum contact integration on cobalt silicide junction

Embodiments herein provide methods for forming an aluminum contact on a cobalt silicide junction. In one embodiment, a method for forming materials on a substrate is provided which includes forming a cobalt silicide layer on a silicon-containing surface of the substrate during a silicidation process, forming a fluorinated sublimation film on the cobalt silicide layer during a plasma process, heating the substrate to a sublimation temperature to remove the fluorinated sublimation film, depositing a titanium-containing nucleation layer over the cobalt silicide layer, and depositing an aluminum-containing material over the titanium-containing nucleation layer. In one example, the method further provides forming the cobalt silicide layer by depositing a cobalt-containing layer on the silicon-containing surface, heating the substrate during a rapid thermal annealing (RTA) process, etching away any remaining portions of the cobalt-containing layer from the substrate, and subsequently heating the substrate during another RTA process.

Owner:APPLIED MATERIALS INC

Process for forming cobalt and cobalt silicide materials in tungsten contact applications

InactiveUS20110086509A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingCobalt metalHydrogen

Embodiments of the invention generally provide methods for forming cobalt silicide. In one embodiment, a method for forming a cobalt silicide material includes exposing a substrate having a silicon-containing material to either a wet etch solution or a pre-clean plasma during a first step and then to a hydrogen plasma during a second step of a pre-clean process. The method further includes depositing a cobalt metal layer on the silicon-containing material by a CVD process, heating the substrate to form a first cobalt silicide layer comprising CoSi at the interface of the cobalt metal layer and the silicon-containing material during a first annealing process, removing any unreacted cobalt metal from the substrate during an etch process, and heating the substrate to form a second cobalt silicide layer comprising CoSi2 during a second annealing process.

Owner:APPLIED MATERIALS INC

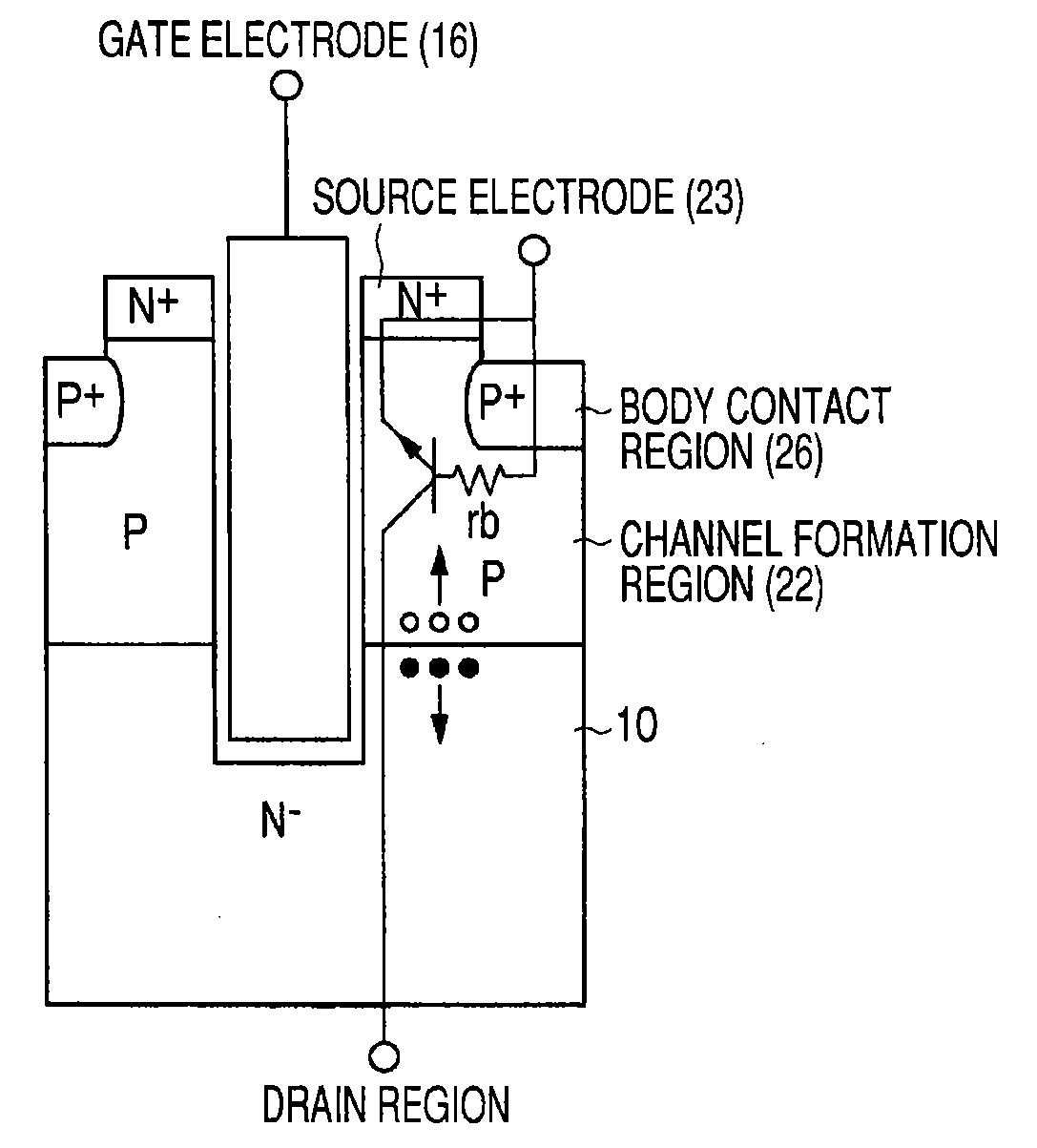

Bipolar/bicmos semiconductor device

An N type buried layer is buried in a P type silicon substrate. An N type epitaxial layer is formed on this buried layer. A P type intrinsic base region and an extrinsic base region are formed on the surface of the epitaxial layer. An N type emitter region is formed in the intrinsic base region. An emitter electrode is formed to contact the emitter region. A collector plug region is formed in an area separated from the extrinsic base region through a filed insulating film. A cobalt silicide film is formed on the extrinsic base region to surround the emitter electrode. An extrinsic base contact hole is formed at only one side of the emitter electrode. In the semiconductor device, the base resistance Rb and the collector-base capacity Ccb are reduced to make the maximum oscillation frequency fmax sufficiently large.

Owner:RENESAS ELECTRONICS CORP

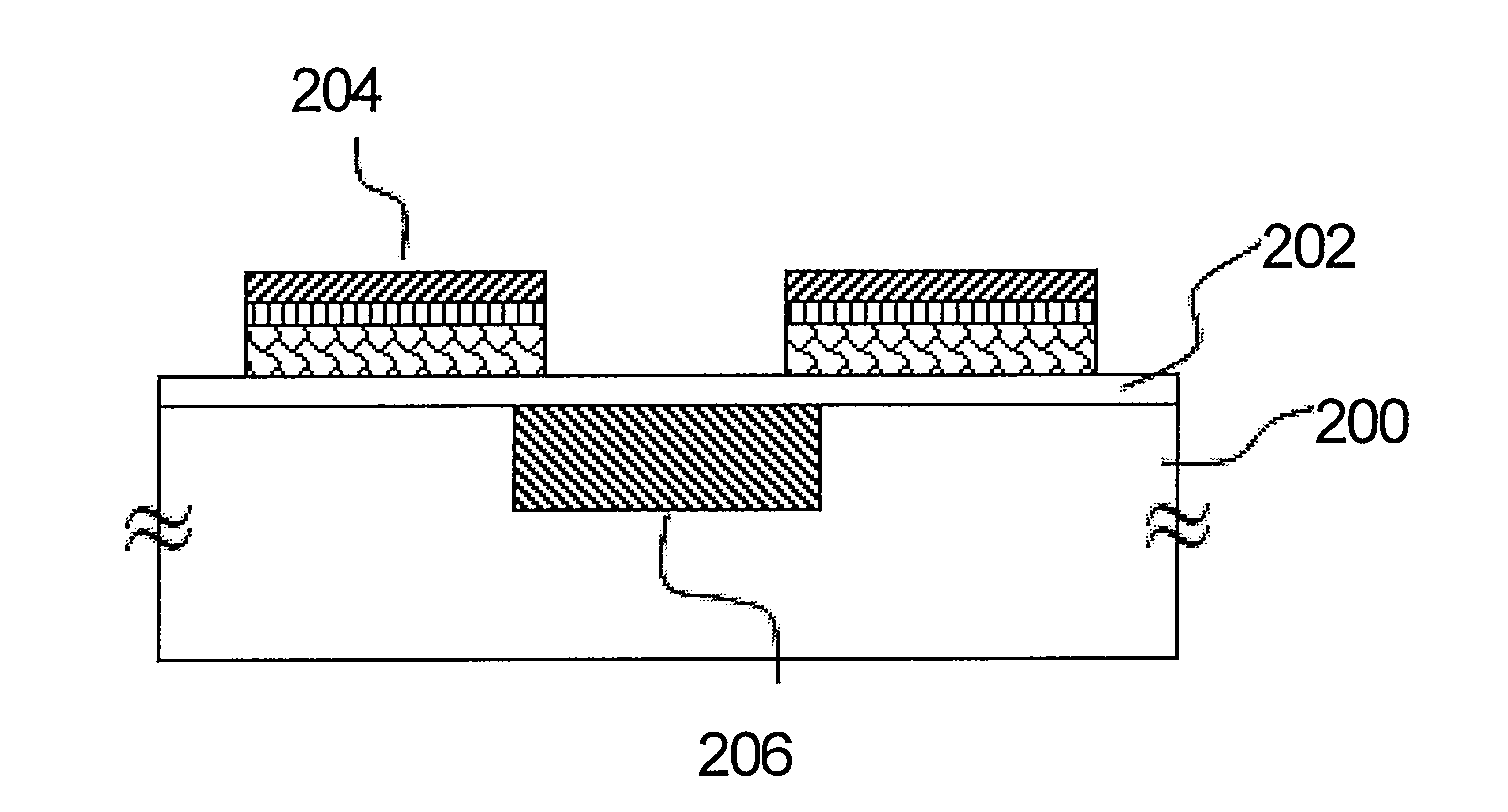

Self-aligned field-effect transistor structure and manufacturing method thereof

InactiveUS20090236675A1Simplify the manufacturing processNanoinformaticsSolid-state devicesCarbon nanotubeMetal silicide

A self-aligned field-effect transistor (FET) is provided. The self-aligned FET includes a substrate, a dielectric layer, conductive electrodes, and a carbon nanotube. A patterned back-gated conductive electrode is disposed in the substrate. The dielectric layer is disposed on the substrate. The conductive electrodes are disposed on the dielectric layer and function as a source / drain. The patterned source / drain conductive electrodes contain a metal silicide such as cobalt silicide serve as a catalyst for carbon nanotube synthesis. The carbon nanotube is disposed on the dielectric layer to be electrically connected with the source / drain conductive electrodes.

Owner:NATIONAL TSING HUA UNIVERSITY

Method and apparatus for using cobalt silicided polycrystalline silicon for a one time programmable non-volatile semiconductor memory

A fusible link formed on a semiconductor substrate. The fusible link comprises a silicide layer overlying a polysilicon layer. The fusible link is programmed to an open state by passing a current therethrough that opens the polysilicon and the silicide layers.

Owner:AVAGO TECH INT SALES PTE LTD