Memory outputting circuit and data outputting method

An output-level circuit and memory technology, applied in static memory, digital memory information, information storage, etc., can solve problems affecting SRAM read time, output delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

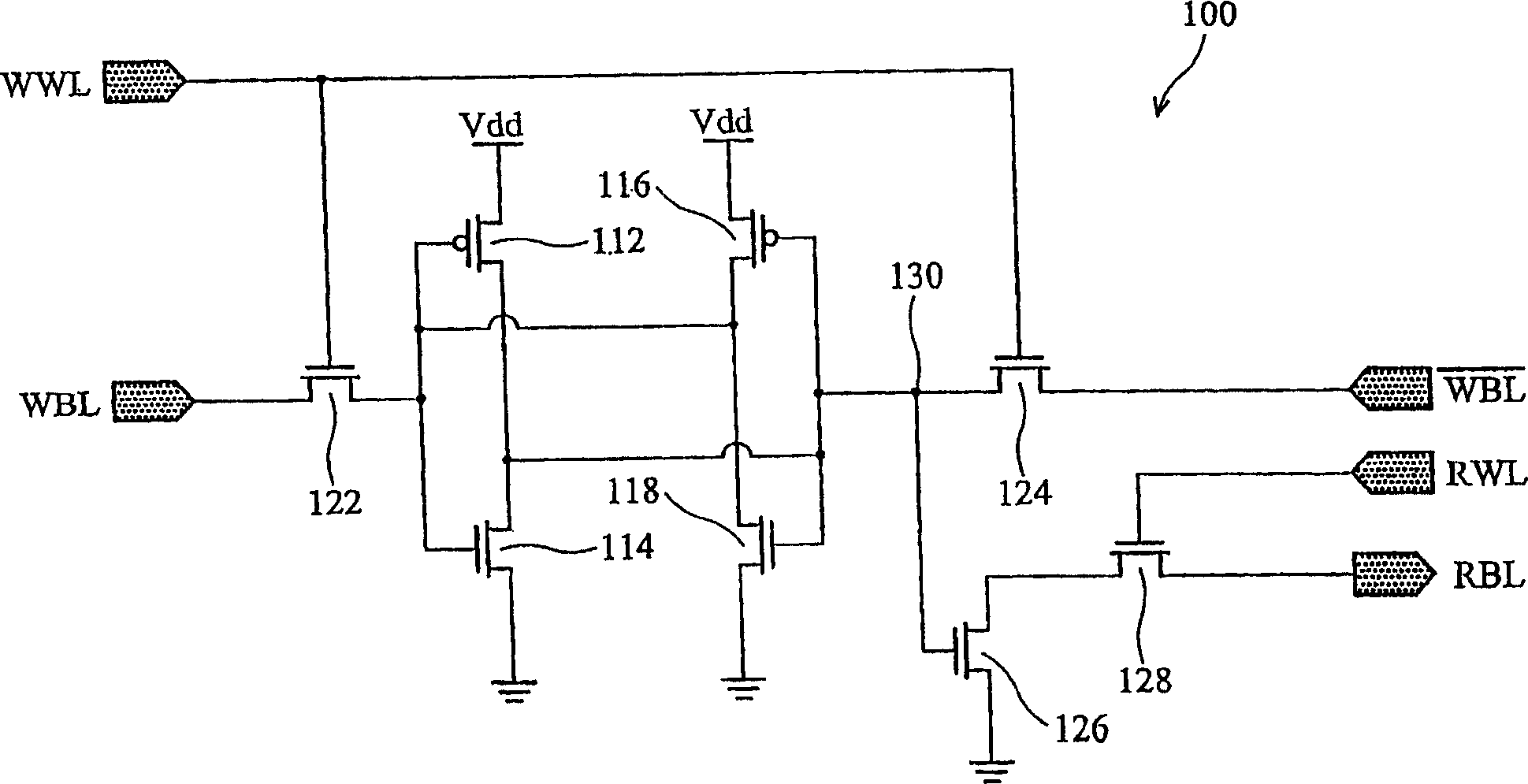

[0047] figure 1 is a circuit diagram of a SRAM cell 100 . The SRAM unit 100 is a dual port 8-transistor (8T) memory unit with a single output terminal. The eight transistors include pull-up transistors 112 and 116 , pull-down transistors 114 and 118 , pass gate transistors 122 and 124 , and sense port transistors 126 and 128 . The pull-up transistors 112 and 116 are PMOS transistors, and the pull-down transistors 114 and 118 , pass gate transistors 122 and 124 , and sense port transistors 126 and 128 are NMOS transistors. However, the present invention still allows other configurations of NMOS and PMOS transistors.

[0048] The sources of the pull-up transistors 112 and 116 are coupled to the voltage source Vdd. The drain of the pull-up transistor 112 is coupled to the source of the pass-gate transistor 124 , the drain of the pull-down transistor 114 , and the gate of the pull-up transistor 116 . Likewise, the drain of pull-up transistor 116 is coupled to the source of pas...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap