Verifying system, establishing method of verifying system and verifying method

A verification system and bus technology, applied in the field of verification systems, can solve problems such as difficulty in system integration, poor verification quality, and impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

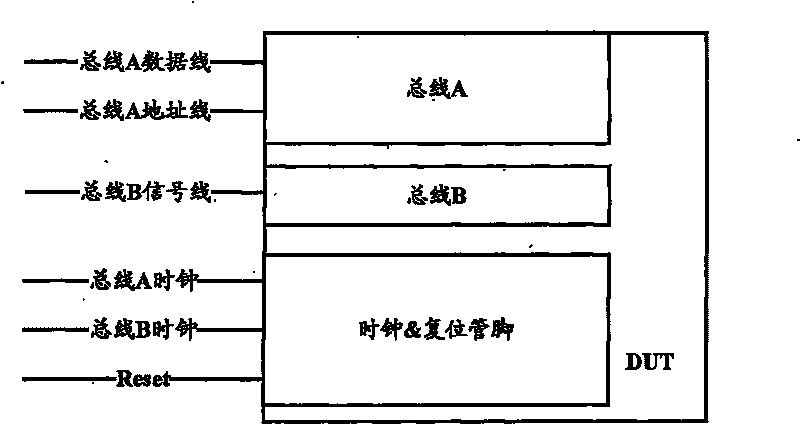

[0061] For DUT (Device Under Test, device under test), in the present invention, as figure 1 As shown, the external interface of the DUT is divided into two parts:

[0062] A bus set, wherein the bus set includes one or more. In the specific embodiment of the present invention, two bus sets are taken as an example for illustration, namely, bus A and bus B. At the same time, bus A is declared as a data bus, and the division of the bus set The bus with the same function can be divided into a bus set, or the standard bus can be divided into a bus set, of course, it can also be divided into other ways; because the bus A is a data bus, it is necessary to mark the data line and address line;

[0063] The corresponding clock and reset pins of each bus set correspond to bus A and bus B respectively outputting the clock of bus A and the clock of bus B, and simultaneously outputting and / or receiving a reset signal.

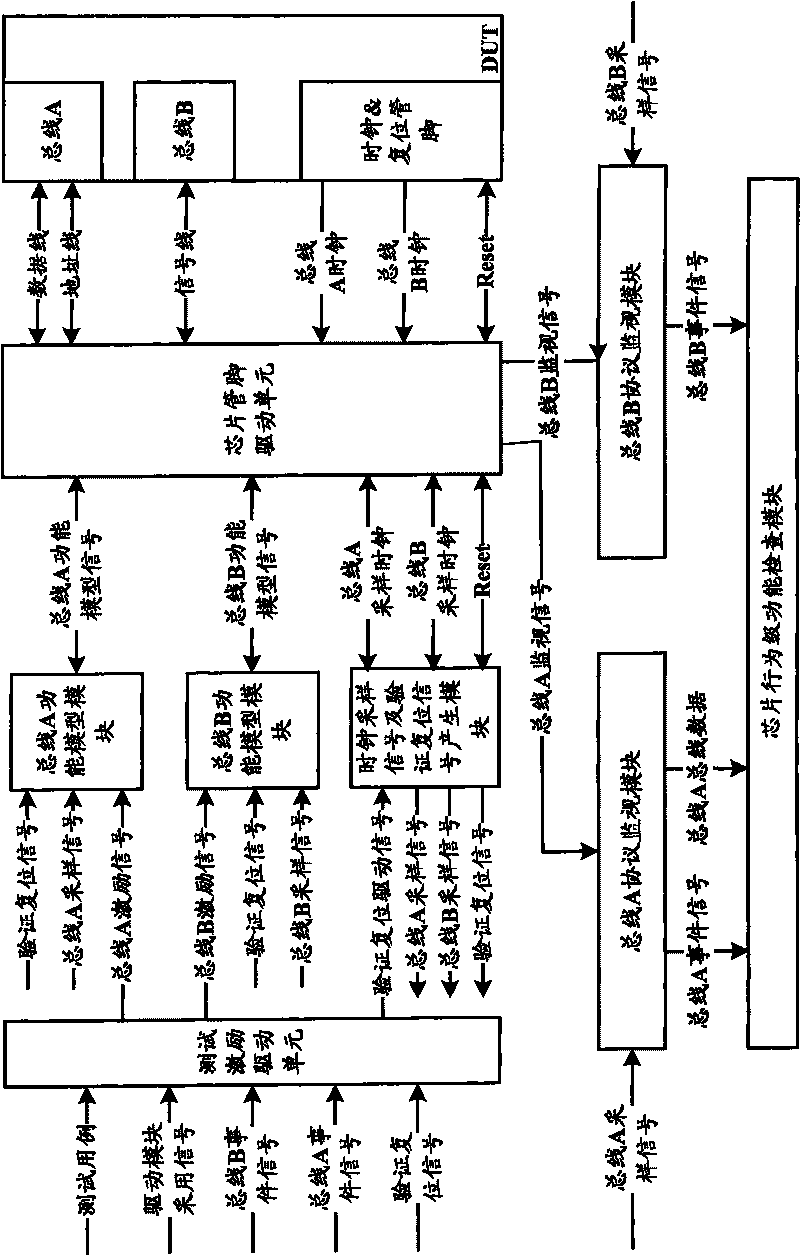

[0064] The verification system of the present invention is as figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More