Partitionable embedded circuit test system for integrated circuit

a test system and integrated circuit technology, applied in the direction of instruments, static storage, etc., can solve the problems of ic testers external to the ic not being able to directly test such embedded rams, requiring a substantial amount of scarce space within, and unable to access read and write access via the ic's input/output terminals (i/o)

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

)

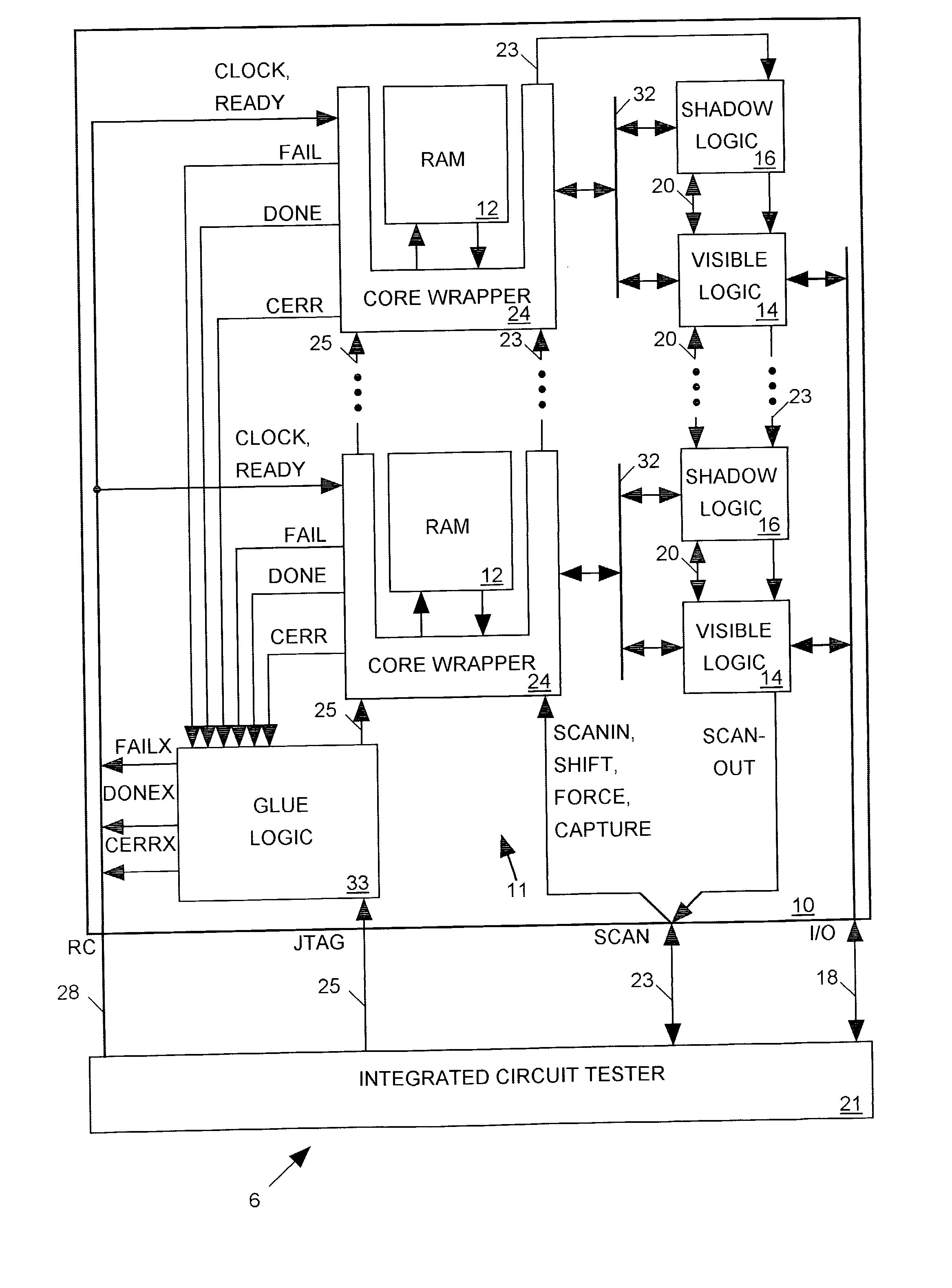

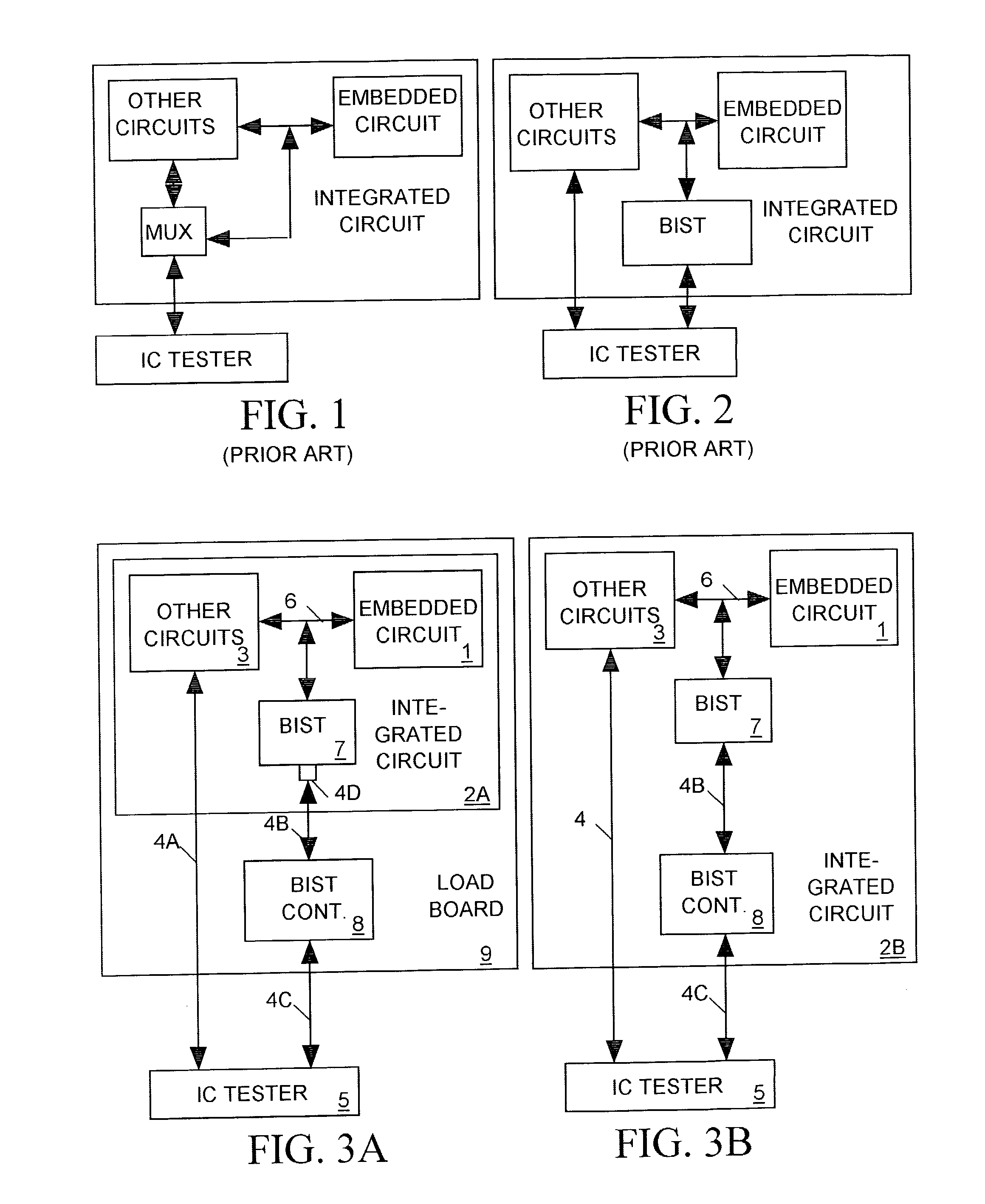

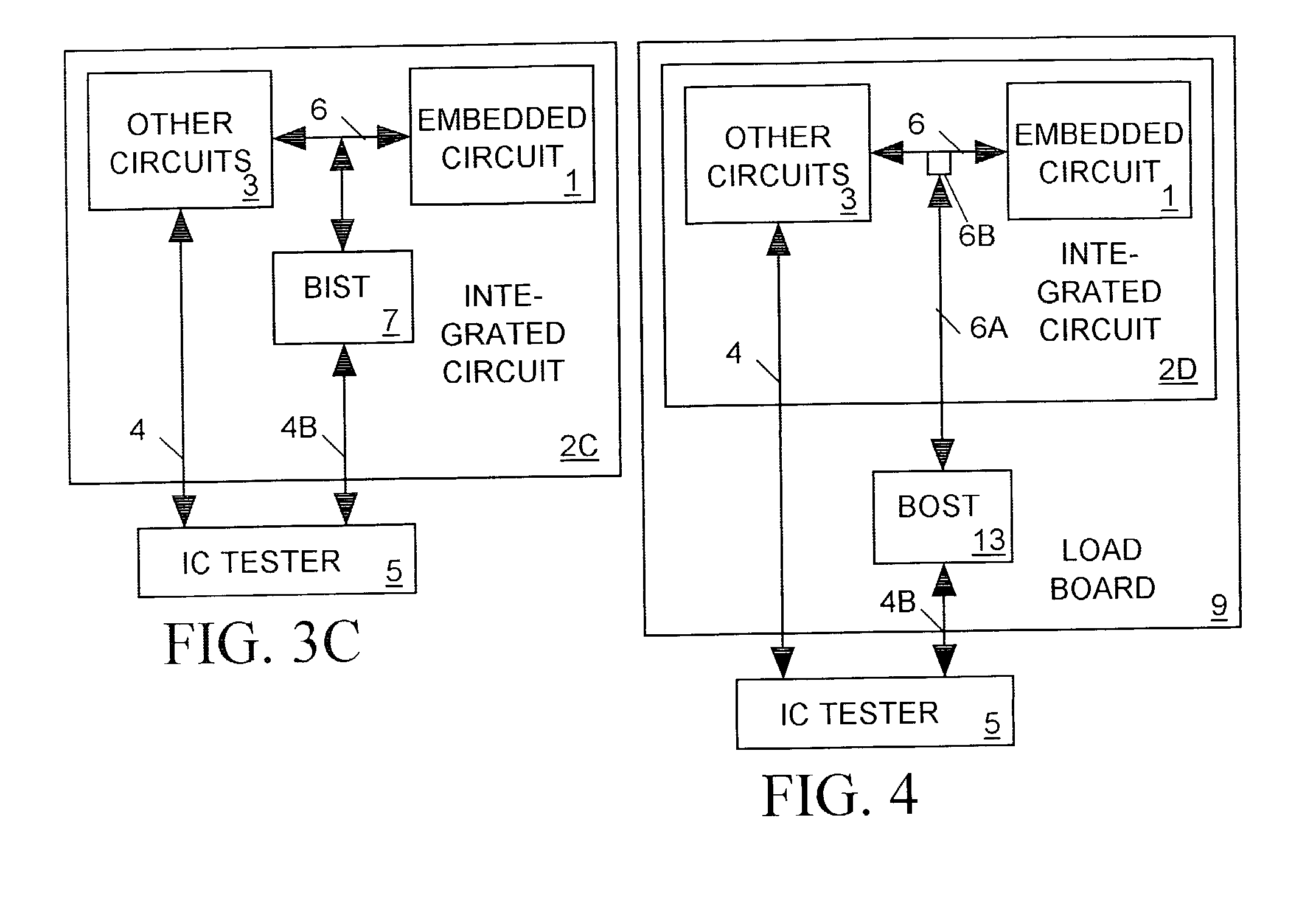

[0041] FIGS. 3A-3C and 4 illustrate alternative versions of a system in accordance with the present invention for testing an circuit 1 such as one or more random access memories embedded in an integrated circuit (IC) 2A-2D along with other circuits 3. Embedded circuit 1 communicates with other circuits 3 linked to via input / output (I / O) terminals 4 that may be accessed by an external IC tester 5. However since the bus 6 linking embedded circuit 1 to other circuit 3 is not linked to IC I / O terminals, IC tester 5 cannot directly test embedded circuit 1. However as illustrated in FIGS. 3A and 3B, a built-in, self-test (BIST) circuit 7 is provided within integrated circuit 2A or 2B to access bus 6 and test embedded circuit 1. BIST circuit 7 communicates with a BIST controller circuit 8 which, as illustrated in FIG. 3A, may be implemented by a separate IC mounted on the same circuit board (load board 9) on which IC 2A is mounted when being tested by IC tester 5. BIST controller circuit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More