Method of making microelectronic packages including electrically and/or thermally conductive element

a technology of electrical and/or thermal conductivity elements and microelectronic components, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of time-consuming and expensive semiconductor chips with each other

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

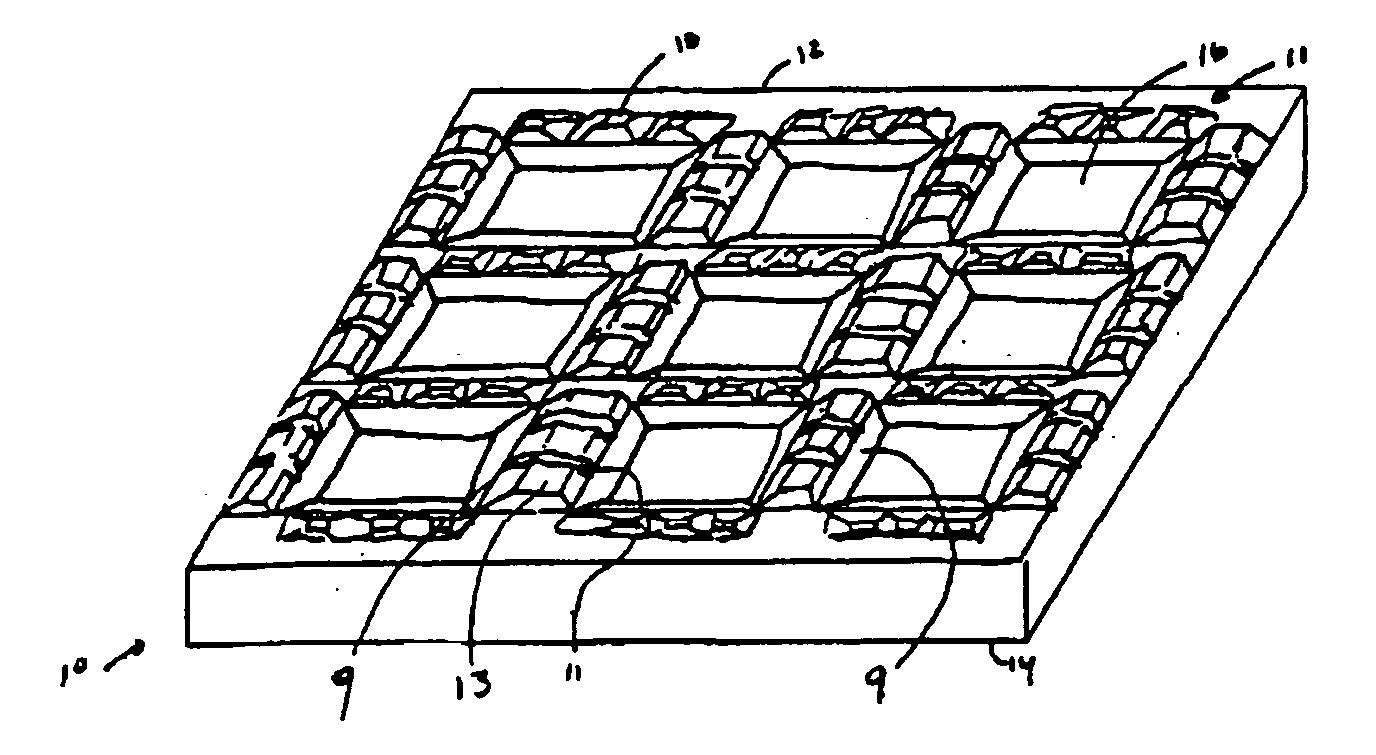

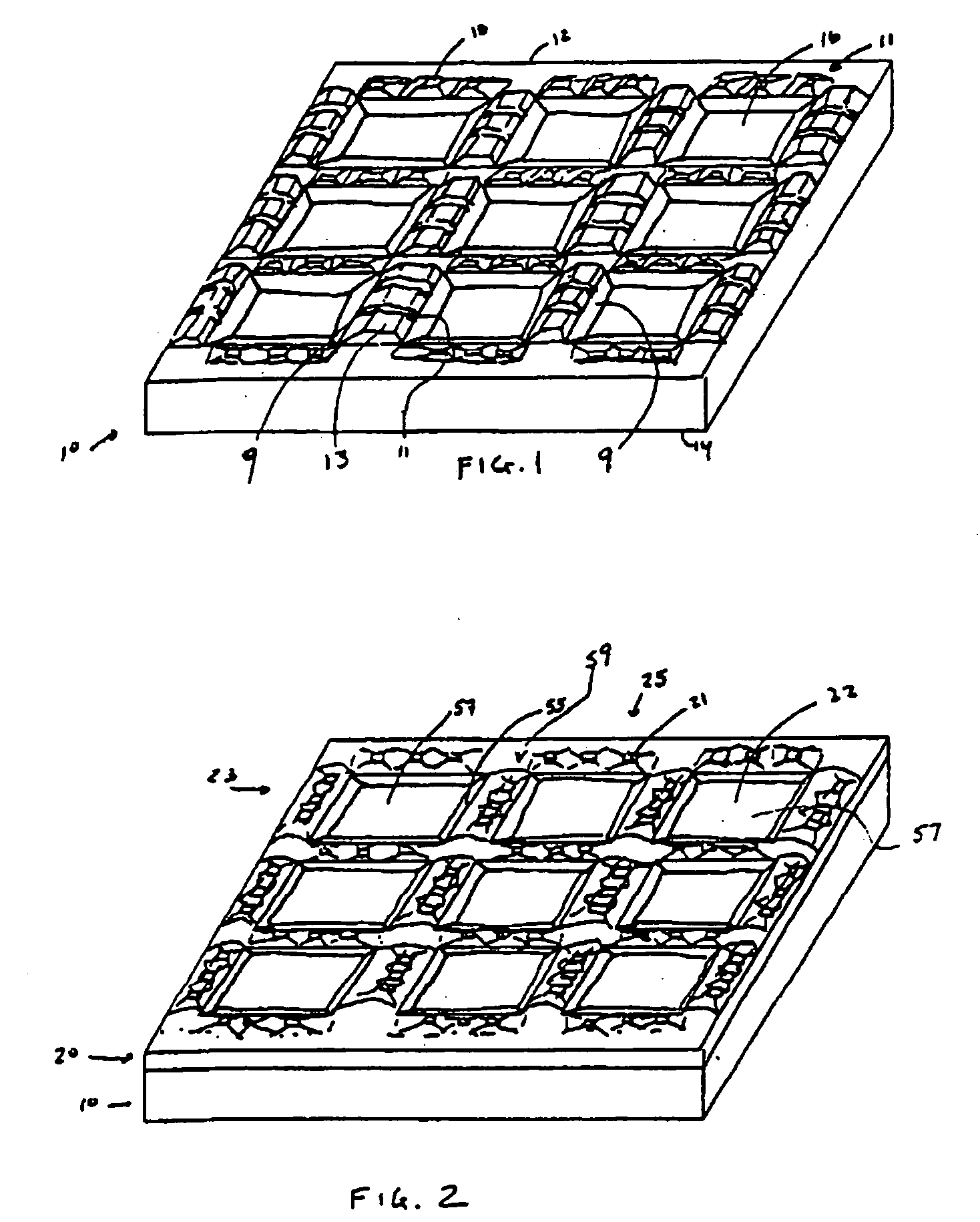

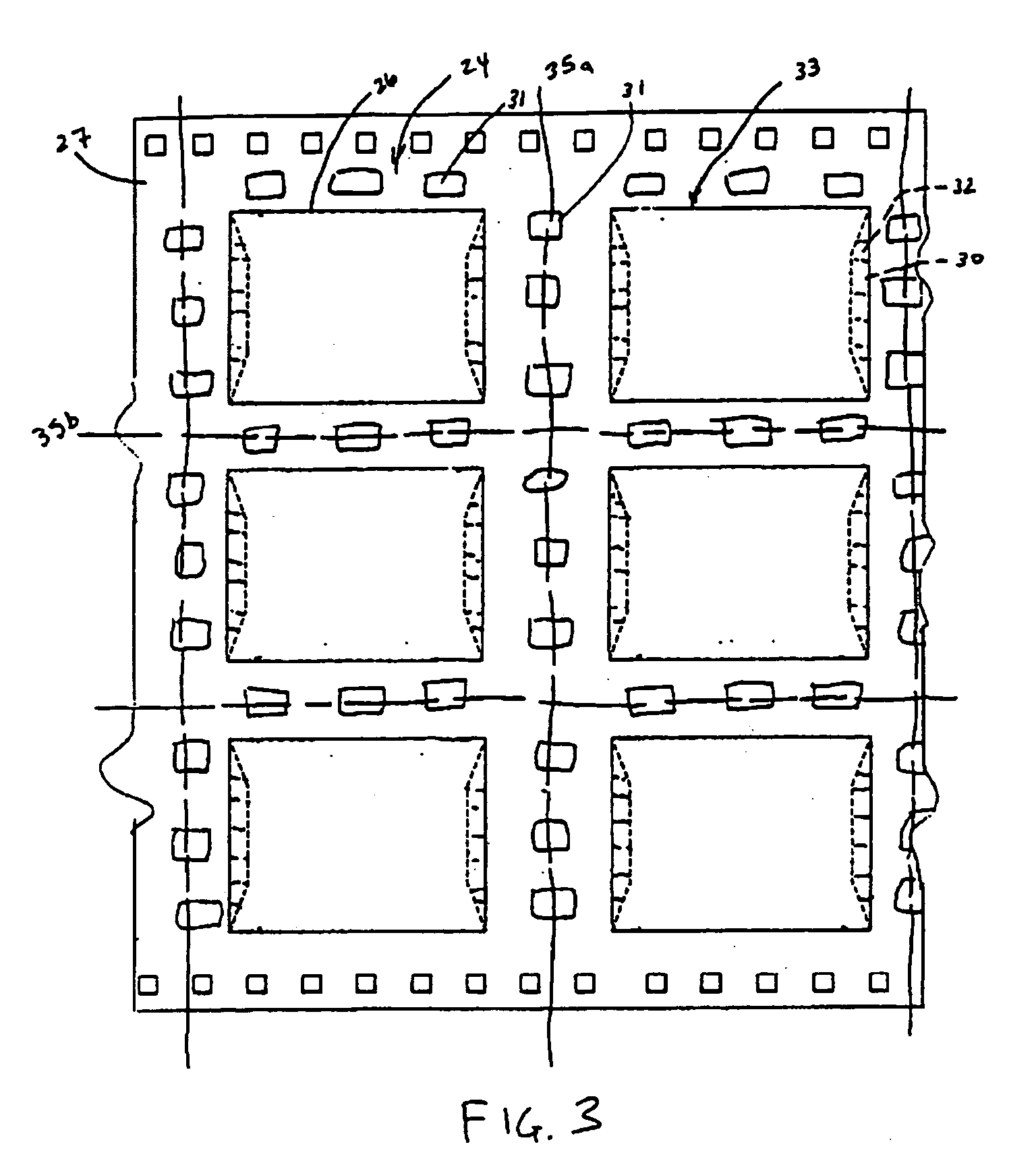

[0031] A method in accordance with one embodiment of the invention includes using a support 10. Support 10 comprises an element having a first major surface 12 and a second major surface 14 facing oppositely from the first major surface 12. Recesses 16 are formed in the first major surface 12 of the support 10. The support has surface portions 11 surrounding each recess 16 and projecting upwardly from the bottom surface of the recess. In this embodiment, each surface portion 11 is in the form of a substantially continuous wall extending along one side of a recess or forming a division between two adjacent recesses. Each surface portion or wall 11 has outwardly-sloping surfaces extending from the top of the wall to the bottom surface of each adjacent recess, so that each wall widens toward the bottom of the recess whereas each recess widens toward the top or open side of the recess. Each surface portion or wall 11 has a set of spaced apart support protrusions or bumps 13 disposed alo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More