Microelectronic assemblies having low profile connections

a microelectronic and low-profile technology, applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of increasing the stress of the leads, affecting the flexibility of the dielectric layer, and increasing the height of the connection between the leads and contacts, so as to achieve low stress on the conductive elements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

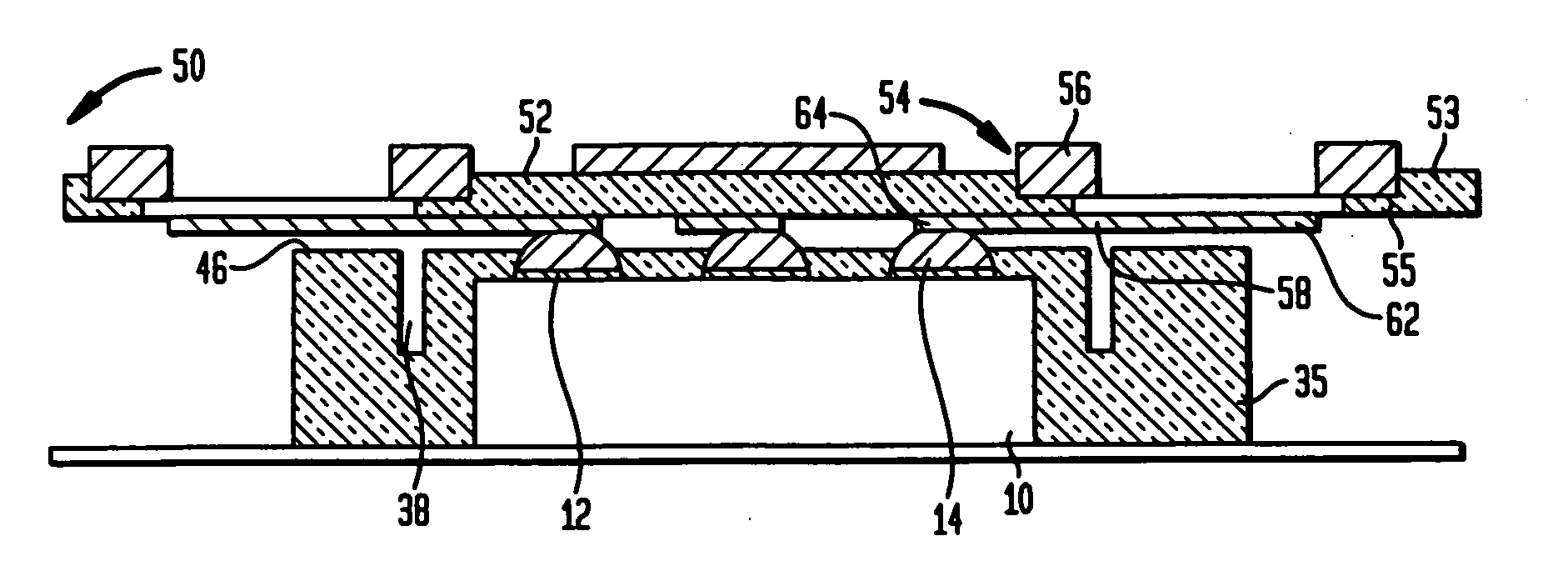

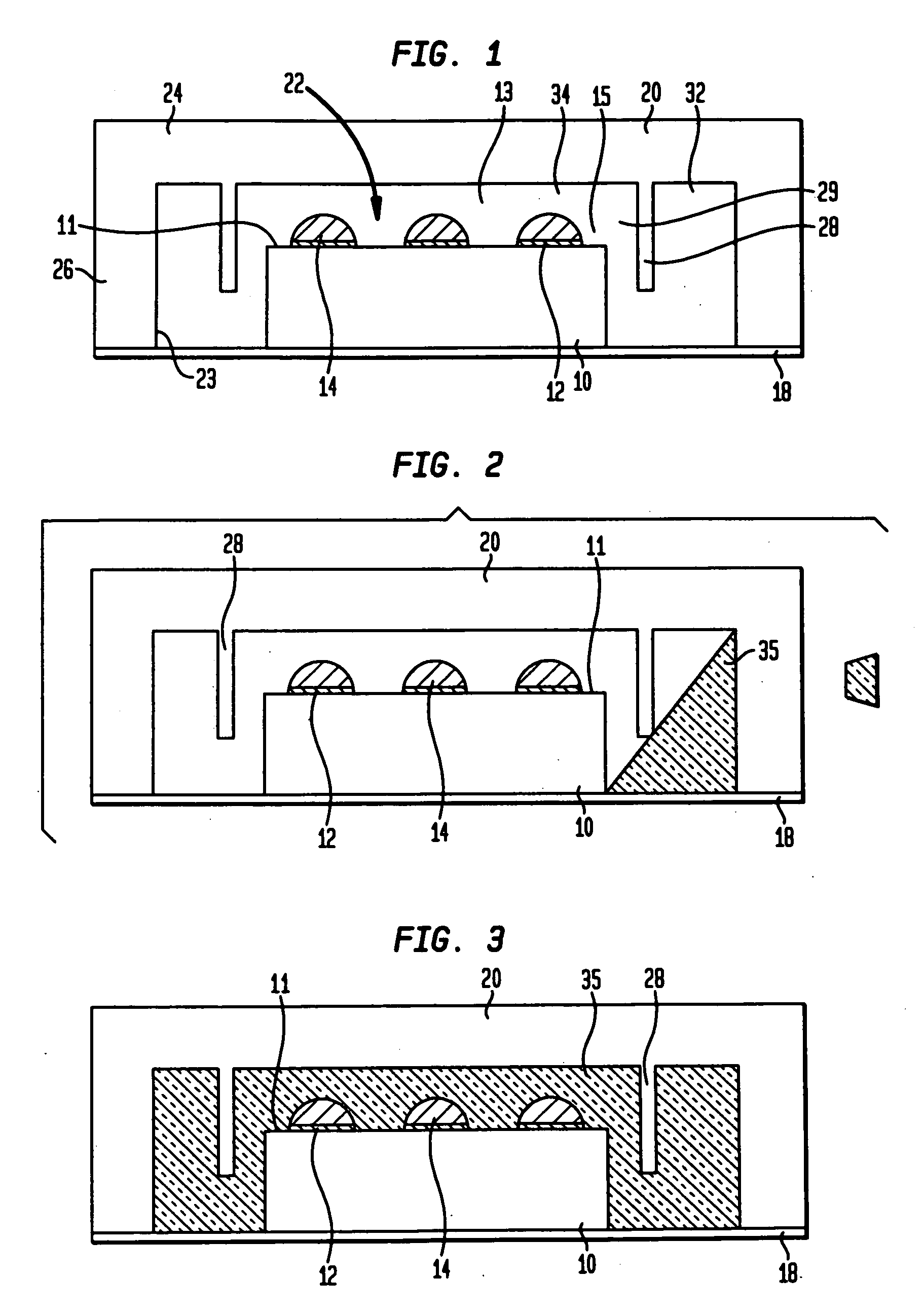

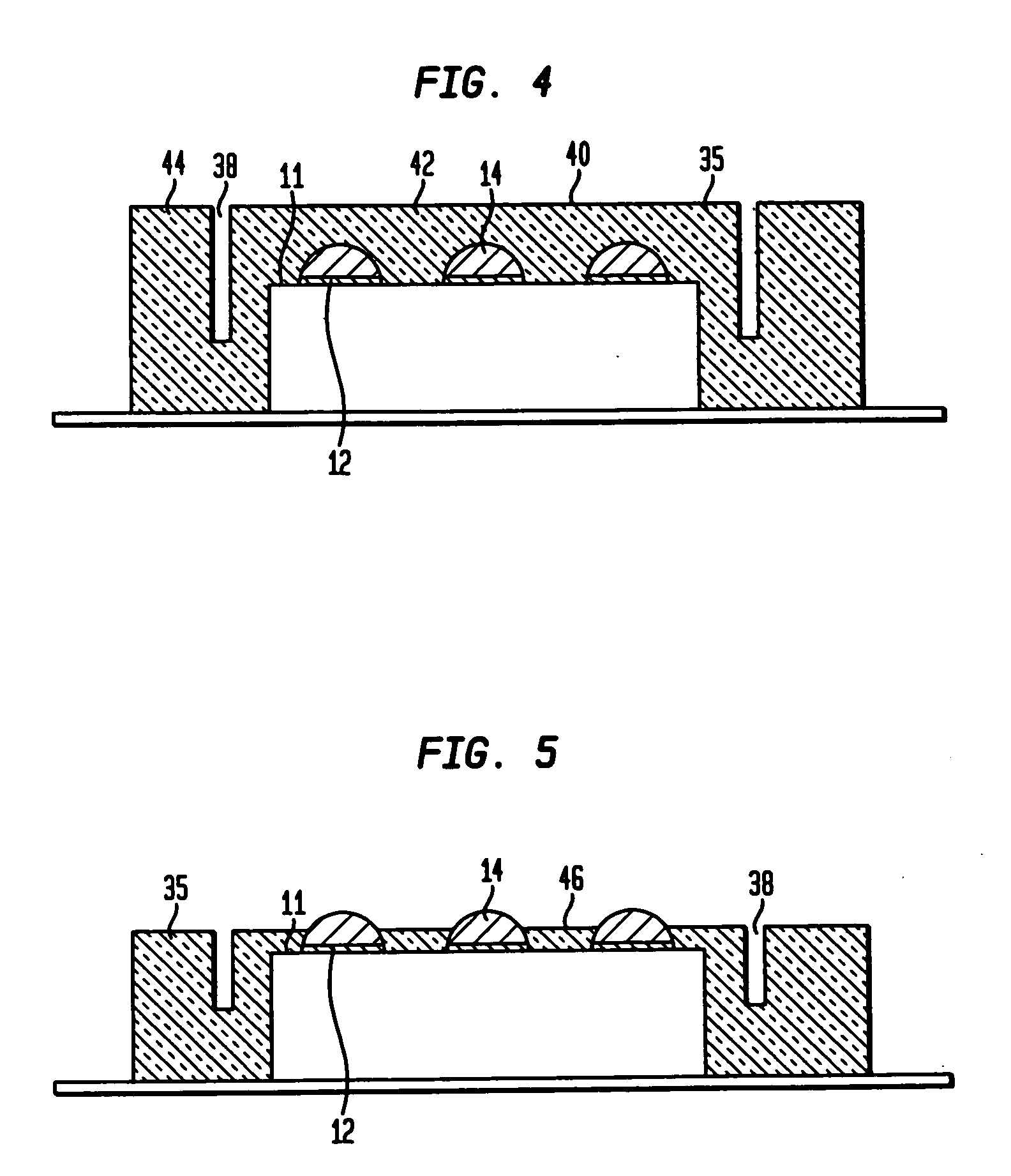

[0058] The method of forming a microelectronic assembly in accordance with one embodiment of the invention is shown in FIGS. 1-9. As shown in FIG. 1, the microelectronic element 10 has a first surface 11 with a plurality of conductive features including contacts 12 exposed at the first surface. The microelectronic element 10 has a central region 13 lying inwardly of a peripheral region 15. In the cross-sectional view of FIG. 1, only three contacts 12 are shown. However, typically a microelectronic element 10 has many contacts that are arranged on the first surface 11 in the central region 13, or in the peripheral region 15 of the microelectronic element 10, or both. The arrangement of the contacts on the microelement element 10 is not critical to the invention.

[0059] The conductive features also include, in certain embodiments, protrusions, such as masses of bonding material, such as solder. The protrusions may comprise bumps or posts or other members attached to the contacts 12. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More