Methods, Apparatus and Computer Program Products for Generating Selective Netlists that Include Interconnection Influences at Pre-Layout and Post-Layout Design Stages

a technology of interconnection influences and netlists, applied in the field of circuit design units, can solve the problems of affecting the performance increasing design costs and design time, and difficult to change the parasitic resistance and parasitic capacitance of interconnections, so as to reduce the time required for simulation of semiconductor integrated circuits, accurately analyze the modeling of parasitic resistance and parasitic capacitance, and reduce the effect of designer errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The structure and operation of each embodiment of a selective netlist generation device according to the present invention and a method according to the present invention for each embodiment of the selective netlist generation device will be described more fully with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The same reference numerals in different drawings represent the same element. The operations described hereinbelow may be performed by an entirely hardware embodiment, an entirely software embodiment or an embodiment combining software and hardware aspects. Moreover, embodiments of the invention may take the form of a computer program product on a computer-readable storage medium having computer-readable program code means embodied in the medium. Any suitable computer-readable medium may be utilized including hard disks, CD-ROMs or other optical or magnetic storage devices.

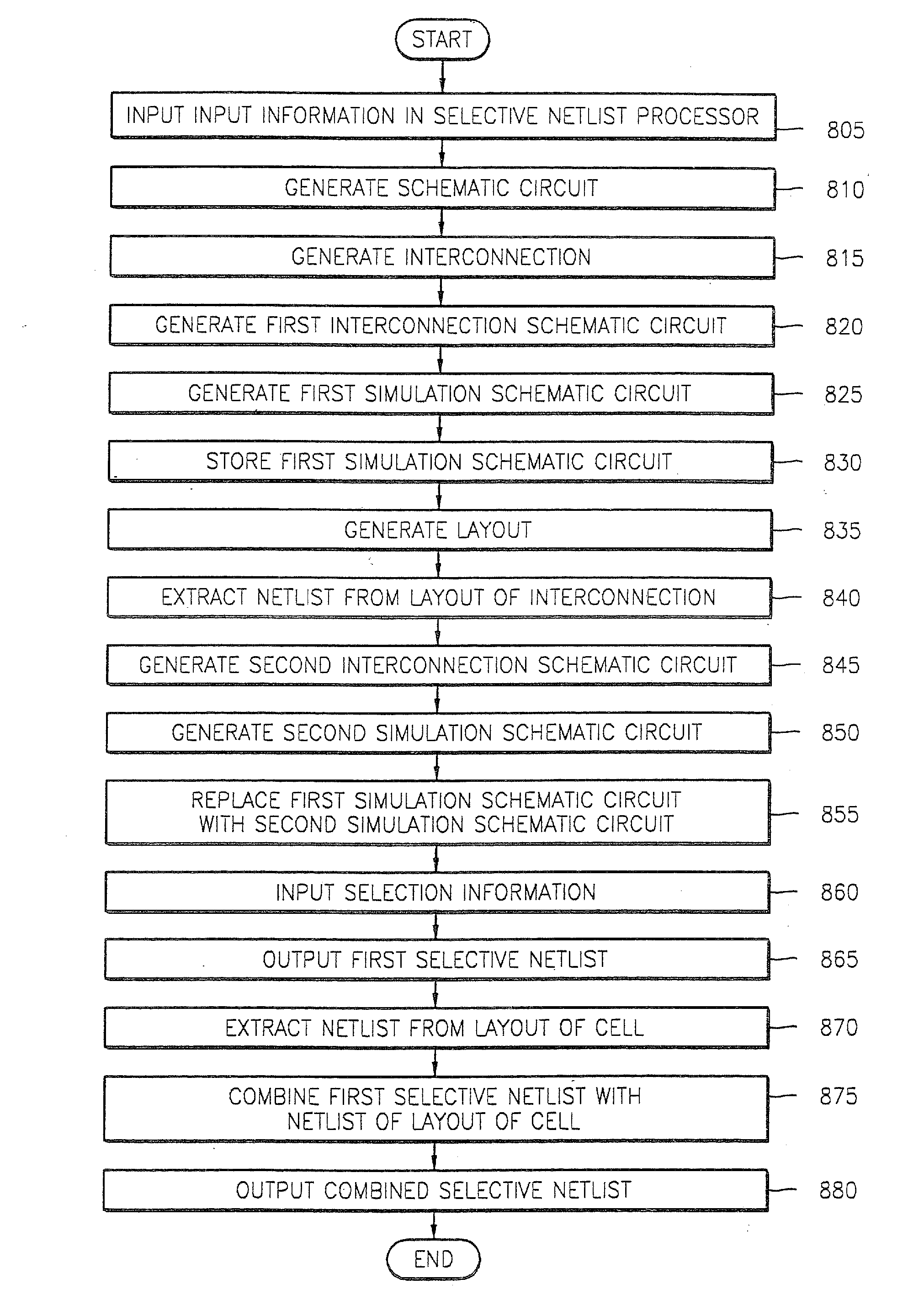

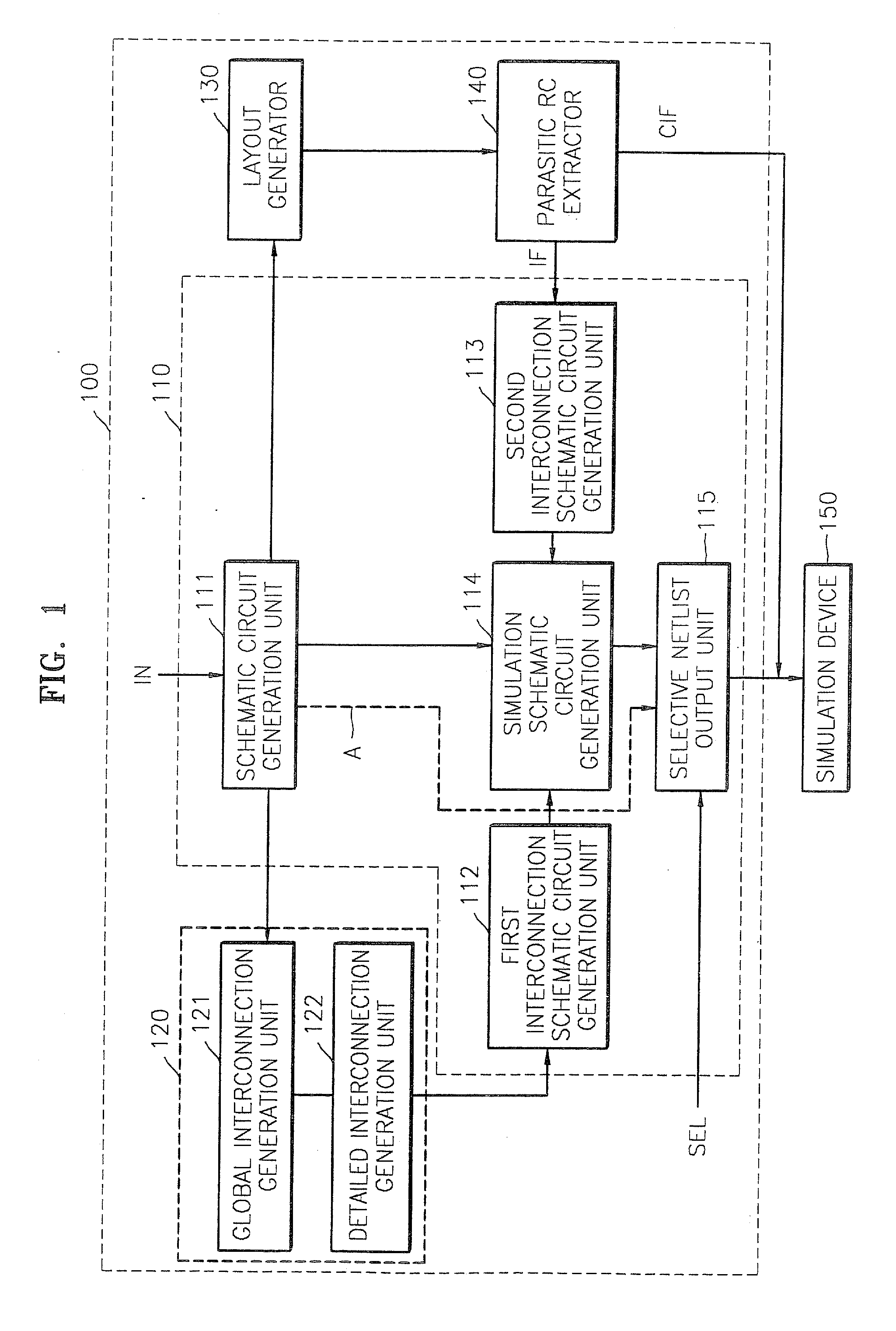

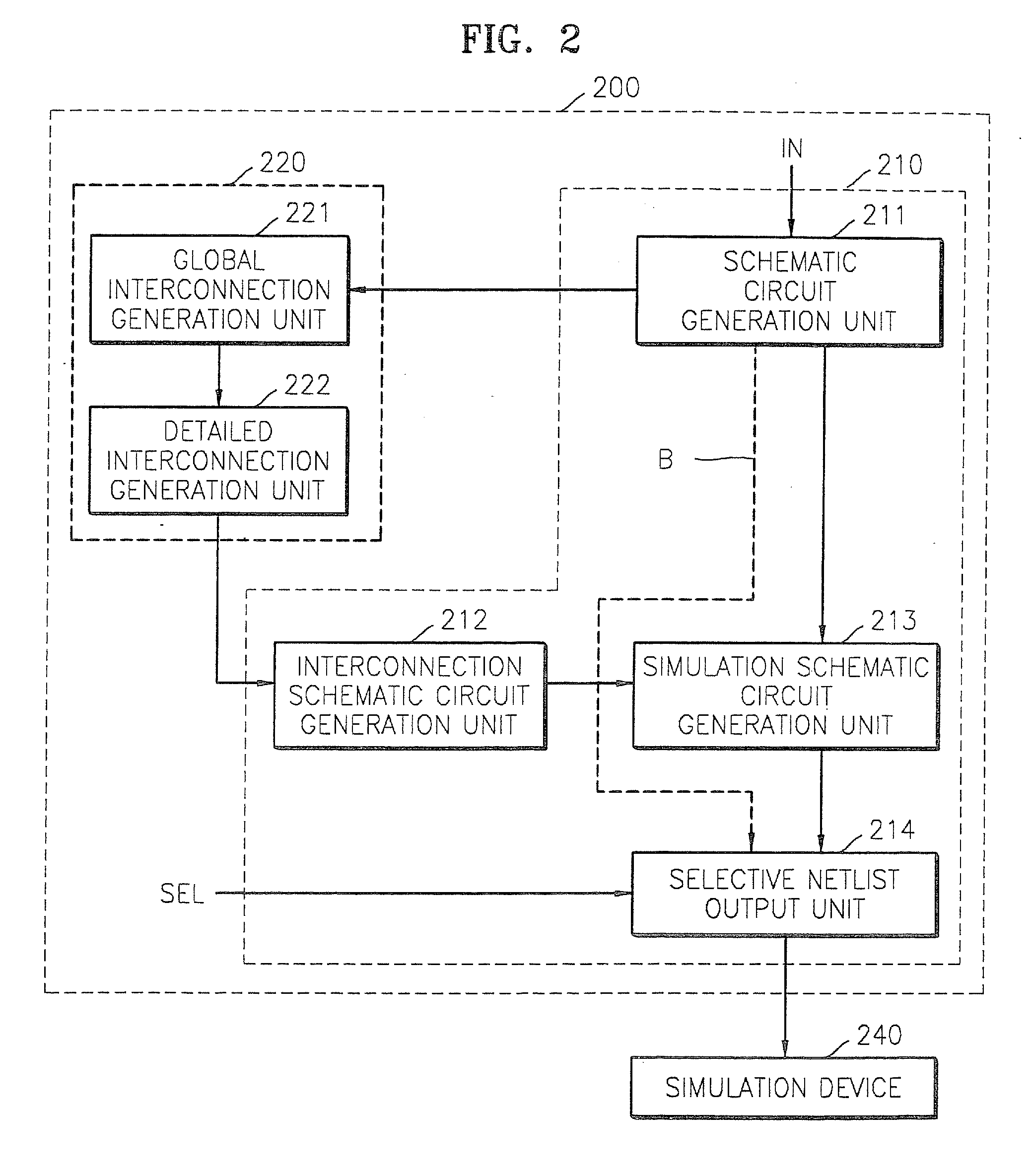

[0038]FIG. 1 is a block diagram illustrati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More