Element placement method and apparatus

a placement method and element technology, applied in the field of electronic circuit design, can solve the problems of chyan-breuer algorithm trapped in local minima, software algorithm and workstation capabilities not improving fast enough to keep up with the exponentially increasing number of resources available, and achieving the effects of improving quality, rapid prototyping, and substantial reduction in placement tim

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

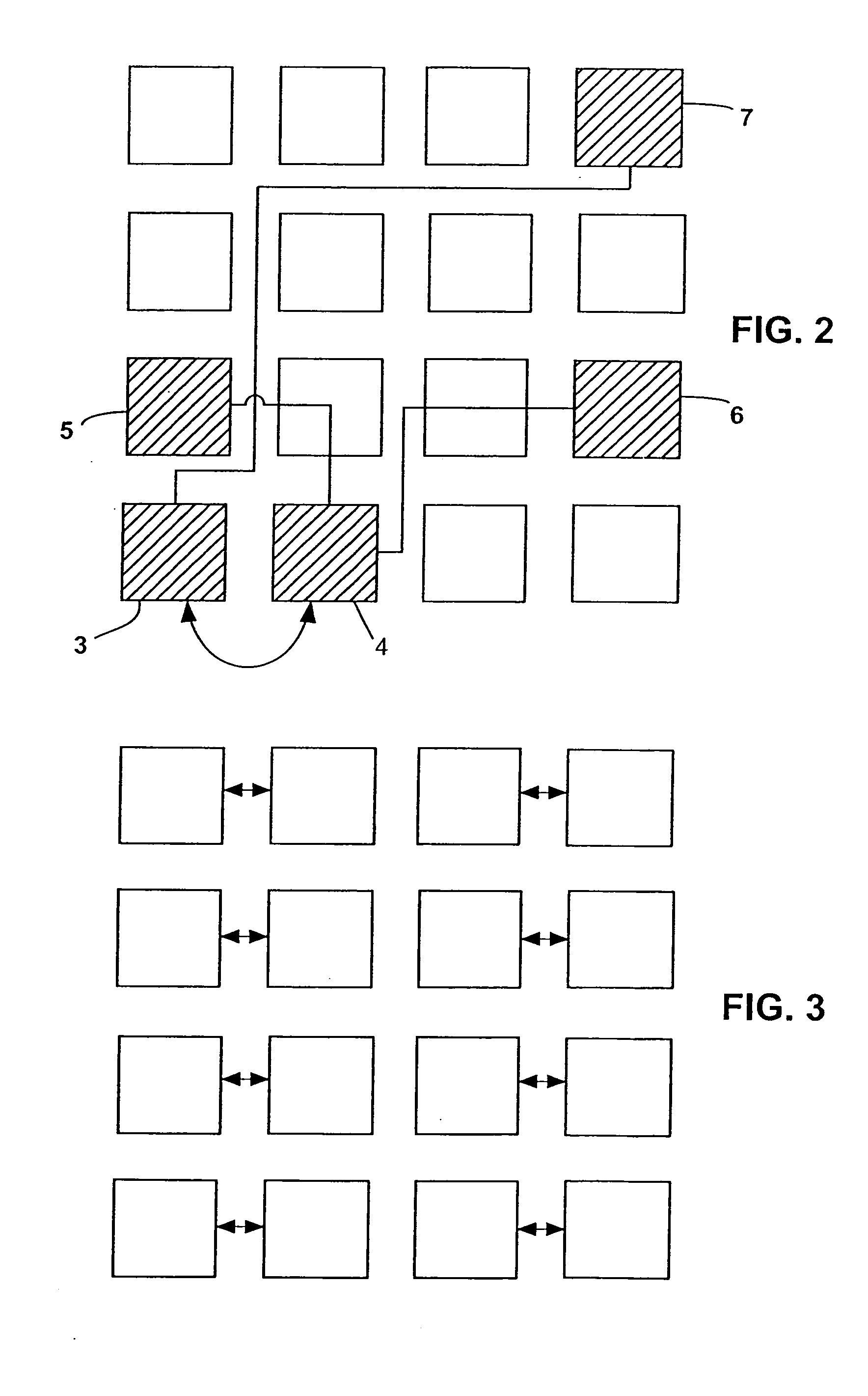

[0117] A first embodiment uses a “windowing” approach, as shown in FIG. 15, where placement has to be performed on a design of 20×20 elements, when only an array of 4×4 processing units is available. The windowing approach provides for movement of a window 300 across the design. In particular, a move could be either a horizontal move (arrows 301 or 302) or a vertical move (arrows 303 or 304). In particular, each time the nodes move, they stop considering the elements along one of their edges and add the elements along the opposing edge. The edge processing elements are responsible for communicating the updated information to a memory when the elements are removed from the window. The edge processing elements also bring in new information on elements which enter the region being processed.

second embodiment

[0118] A second embodiment uses a “folding” approach, where each processing unit is associated to more than one element. Once placement ends, the elements assigned to a particular processing unit can be arbitrarily assigned. Assuming, for example, that four elements are associated to each processing unit, the elements associated with the processing unit at (1, 1) can be assigned to (1, 1), (1, 2), (2, 1) and (2, 2), while the elements associated with the processing unit at (2, 2) can be assigned to (3, 3), (3, 4), (4, 3), and (4, 4) and so on.

[0119] Alternately, the processing unit can keep track of the multiple physical locations that it represents so that it does swap things into their final position. In addition to the external / neighbor swapping phases, an internal swapping phase can be added, in which the processing unit considers swaps among the cells that are associated with it. Also other optimization steps for the cells associated with it are possible.

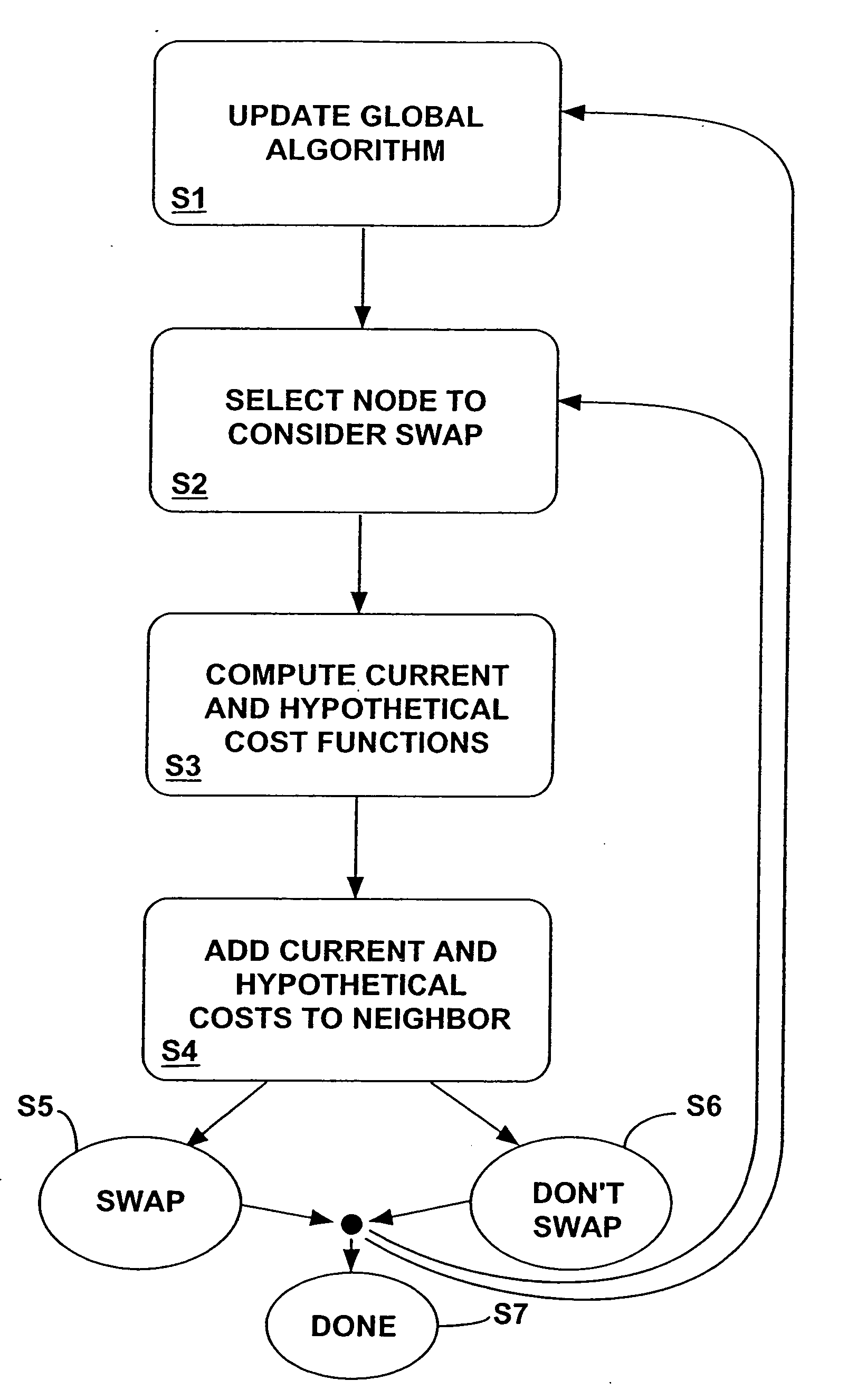

[0120] The method desc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More