Wide output swing CMOS imager

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

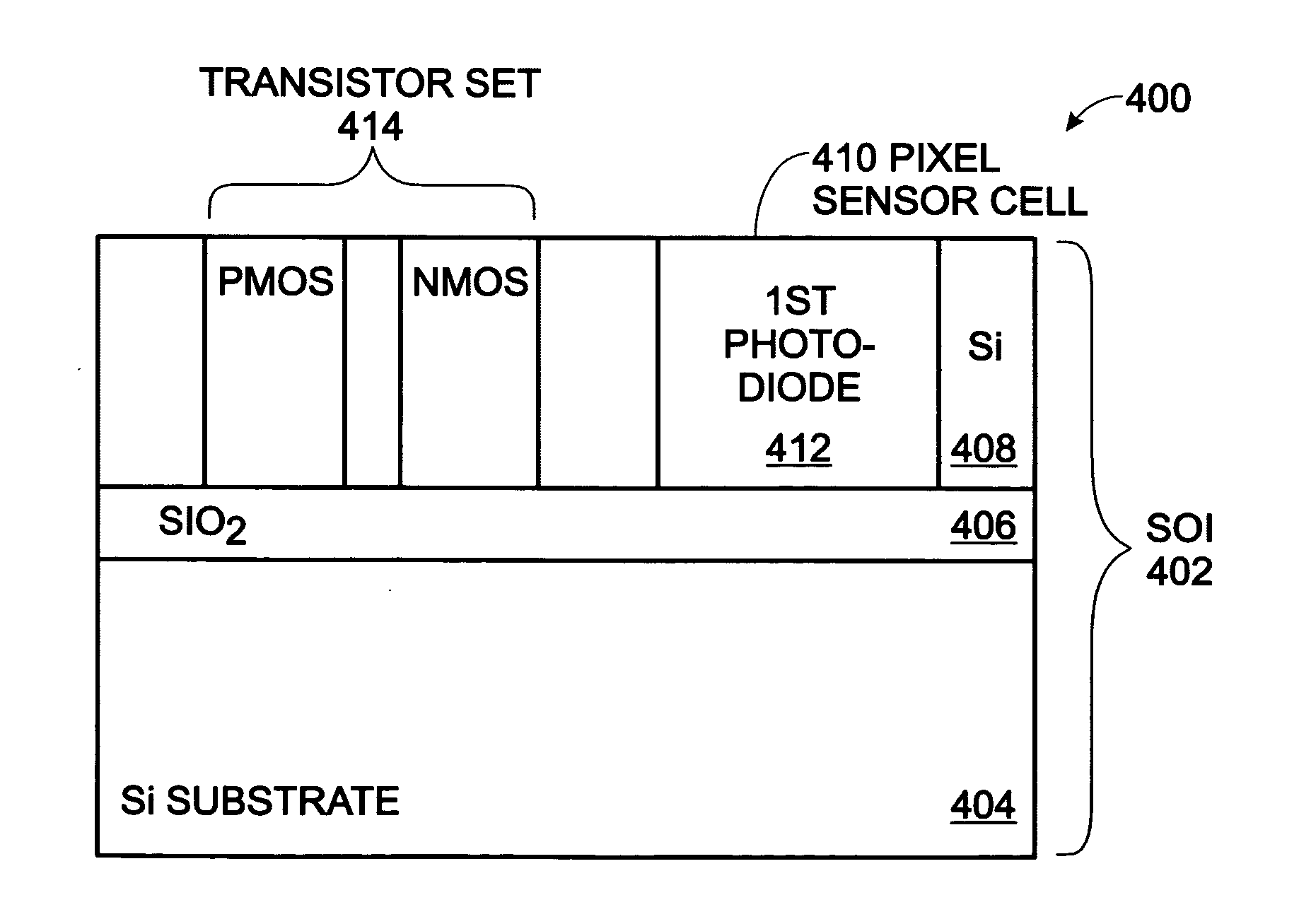

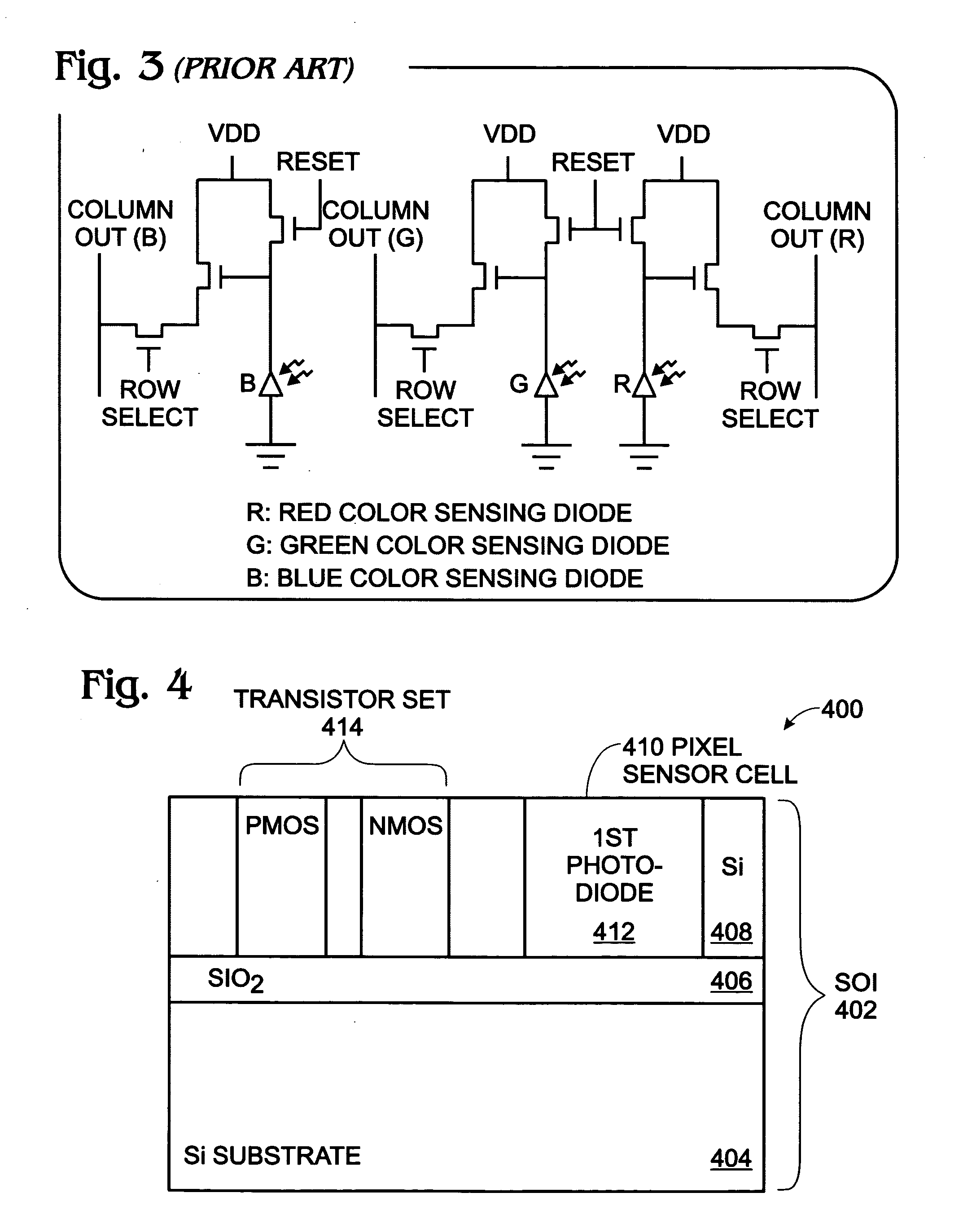

[0030]FIG. 4 is a schematic block diagram depicting a CMOS APS imager cell on a silicon-on-insulator (SOI) substrate. The APS imager cell is comprised of a pixel sensor cell and a pixel transistor set. The APS imager cell 400 comprises a SOI substrate 402 including a silicon (Si) substrate 404, a silicon dioxide insulator 406 overlying the substrate 404, and a Si top layer 408 overlying the insulator 406. A pixel sensor cell 410, including a photodiode 412, is formed in the Si top layer 408 of the SOI substrate 402. A pixel transistor set 414 is also formed in the SOI top Si layer 408 and connected to the pixel sensor cell 410. As described in more detail below, the pixel transistor set 414 includes at least one p-channel MOS (PMOS) transistor and at least one n-channel MOS (NMOS) transistor. Typically, the pixel transistor set 414 is a three-transistor (3T) set for use with a single photodiode, or a nine-transistor (9T) or a six-transistor (6T) cell, for use with stacked (multiple)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More