Laterally Interconnected IC Packages and Methods

a technology of lateral interconnection and ic package, which is applied in the direction of printed circuit, sustainable manufacturing/processing, final product manufacturing, etc., can solve the problems of reducing the area required on the substrate, the inability to increase density while reducing the area, and the inability to meet the practical limit, so as to achieve faster data throughput, reduce costs, and increase the pin count of the package

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

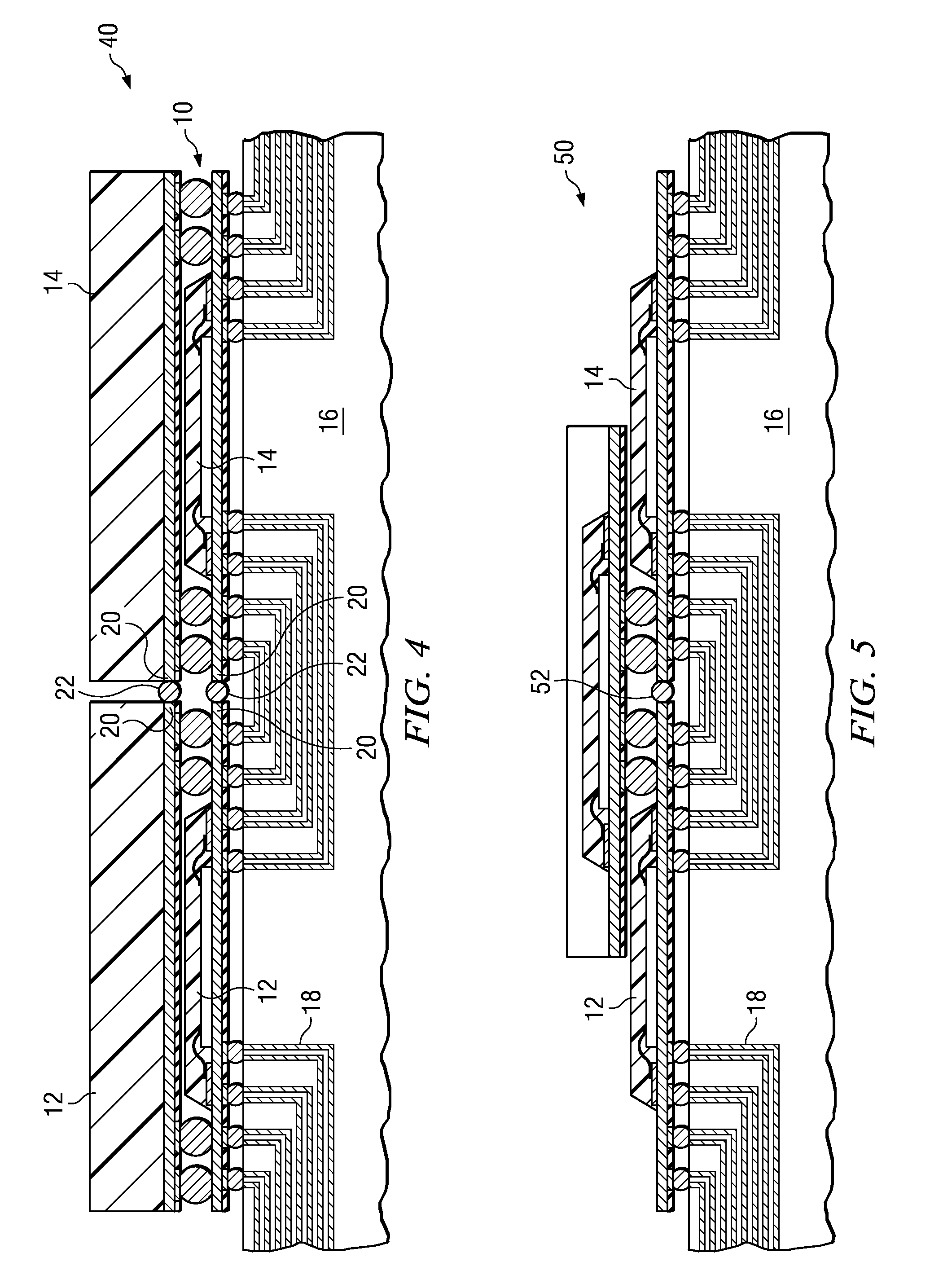

[0018]In general, the invention provides improvements in multi-package semiconductor device assemblies. Laterally interconnected multi-IC configurations facilitate direct communication of electronic signals among adjacent semiconductor devices with decreased reliance on a board interface.

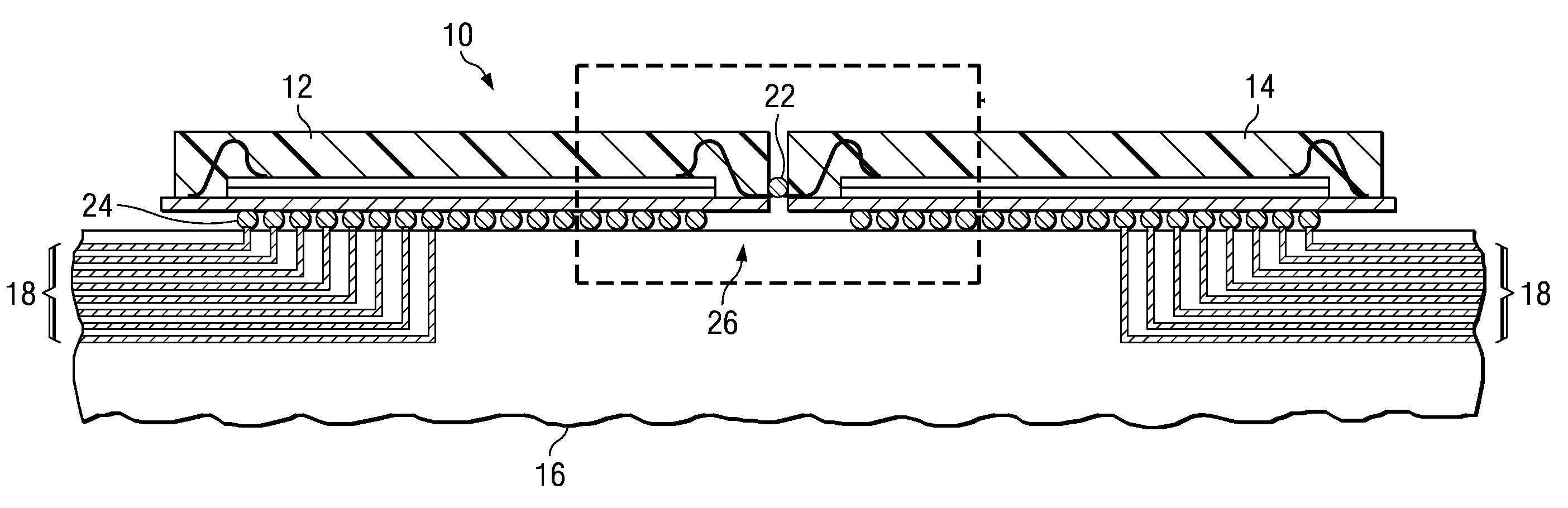

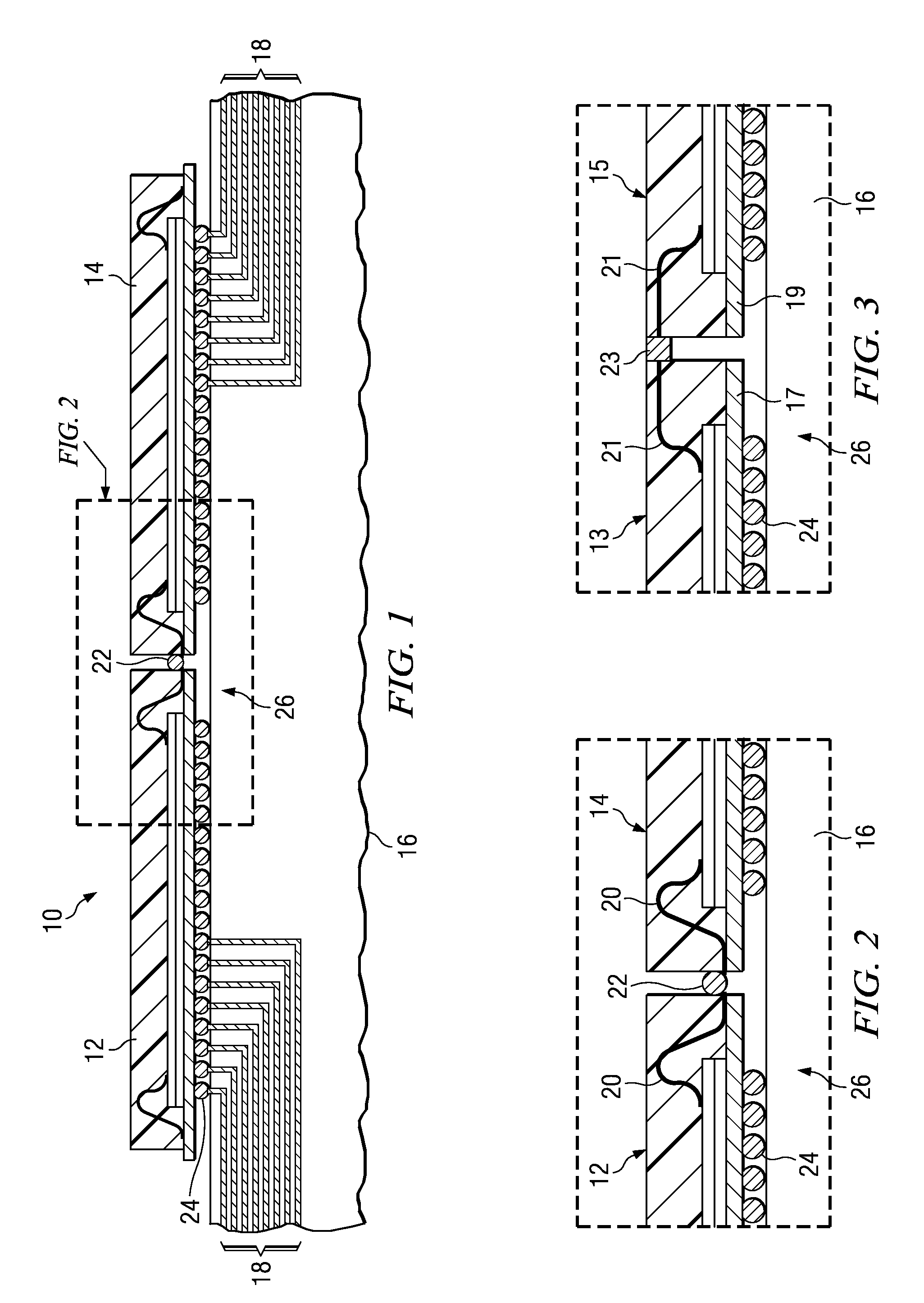

[0019]Now referring primarily to FIG. 1, an example of preferred embodiments of the invention are shown. A multi-package semiconductor device system 10 has a first packaged semiconductor device 12 and a second packaged semiconductor device 14. The first and second devices 12, 14, are adjacent to one another in a coplanar configuration, preferably affixed on a substrate 16, in this case a PCB, although other suitable substrates may be used, such as a PWB, or in the context of a PoP system, another packaged device or coplanar grouping of packaged devices. The substrate 16 typically includes subsurface metallic traces 18 within. The first device 12, and the second device 14, each have at least one late...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More