Dynamic termination logic driver with improved impedance control

a technology of impedance control and driver, applied in the direction of pulse technique, oscillation generator, reliability increasing modifications, etc., can solve the problems of limiting the overall system performance, and affecting the settling time of the signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Other embodiments are within the following claims. For example, one of ordinary skill in the art appreciates that the stated limits are approximations and a function of tolerances in power supply variation, in the number of supplemental bits employed, and a host of other factors affecting that the driver herein disclosed. Further, one of ordinary skill in the art will appreciate that the driver circuitry may be implemented in a complementary fashion whereby N-channel transistors are replaced with P-channel transistors and vice versa, where appropriate.

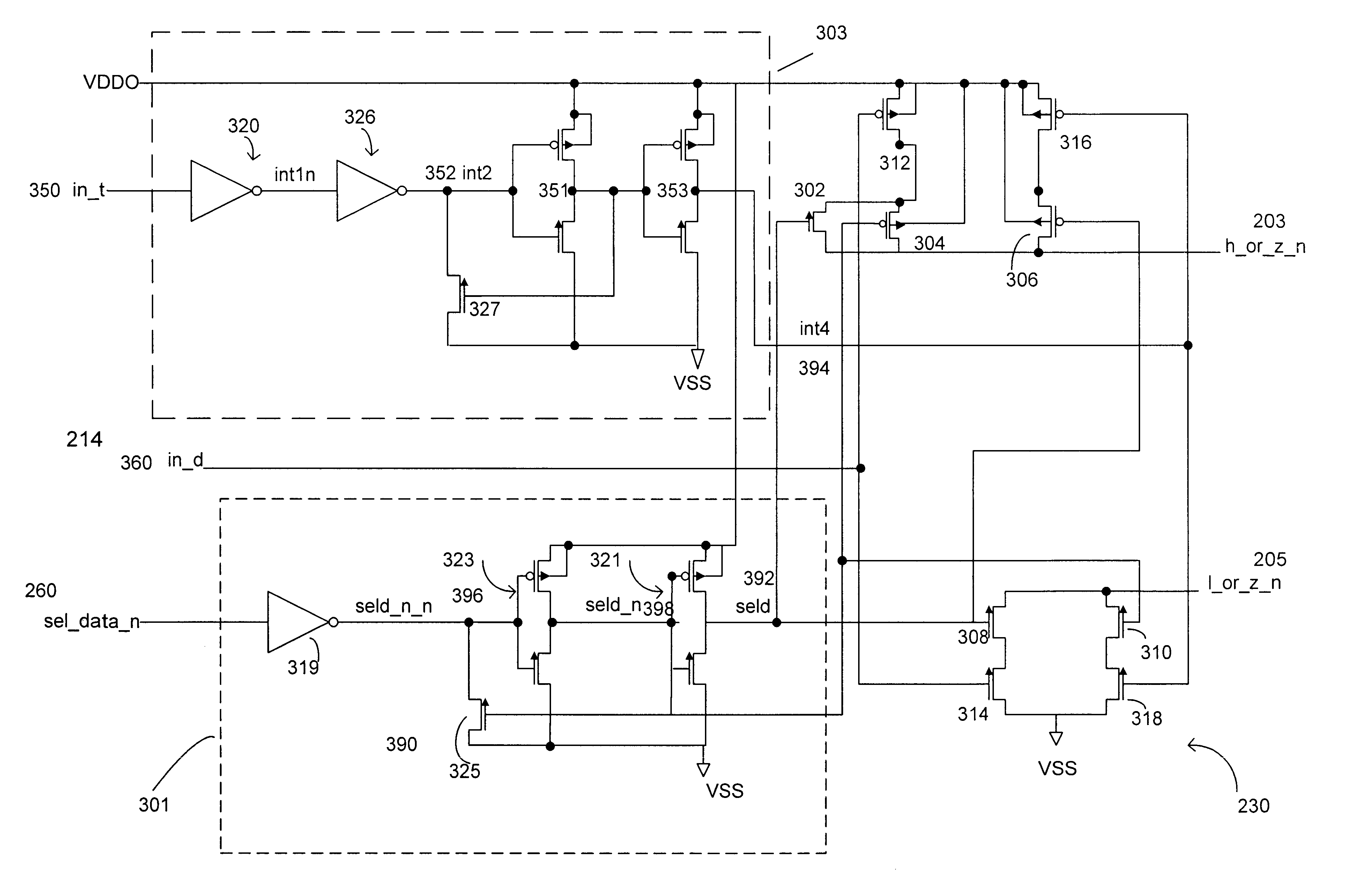

Additionally, the driver alternatively includes either or both slew rate control circuitry and impedance control circuitry within the driver.

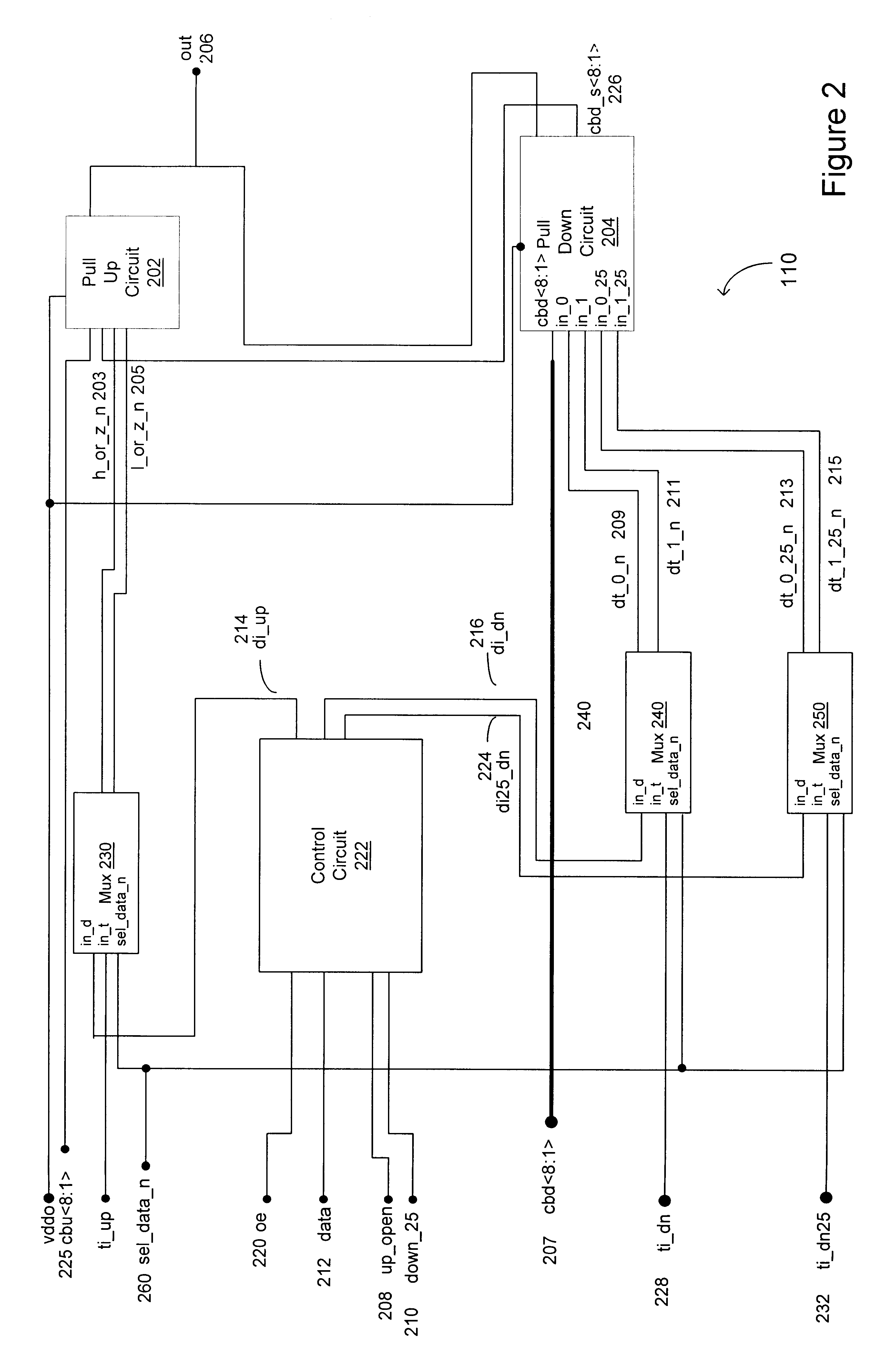

Additionally, one skilled in the art appreciates that components within both the pull up circuit 202 and the pull down circuit 204 may optionally be represented by multiplexors. In one embodiment, for example, pull up circuit 202 and pull down circuit 204 are represented by multiplexors wherein a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More