Patents

Literature

644 results about "Settling time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In control theory the settling time of a dynamical system such as an amplifier or other output device is the time elapsed from the application of an ideal instantaneous step input to the time at which the amplifier output has entered and remained within a specified error band.

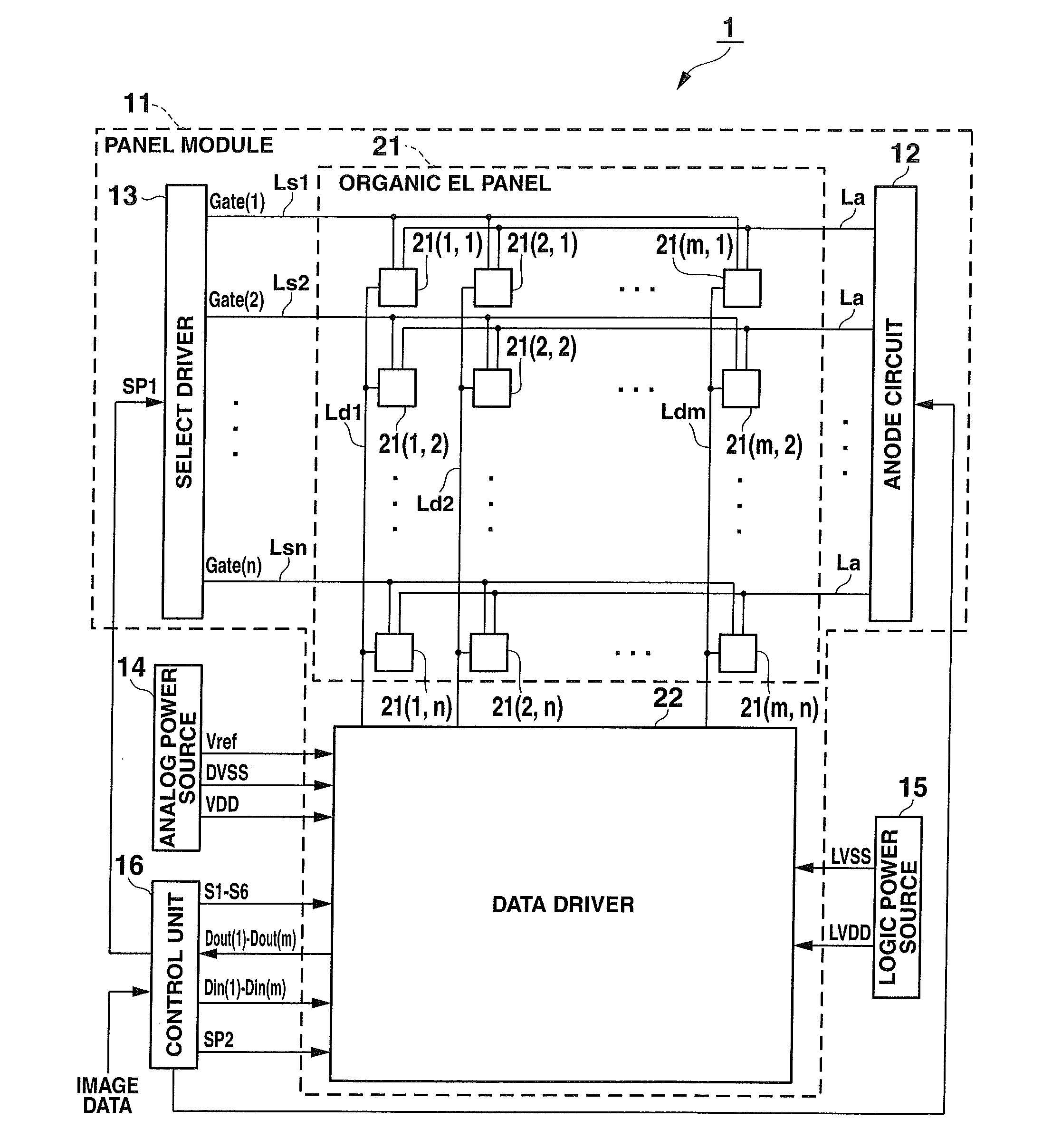

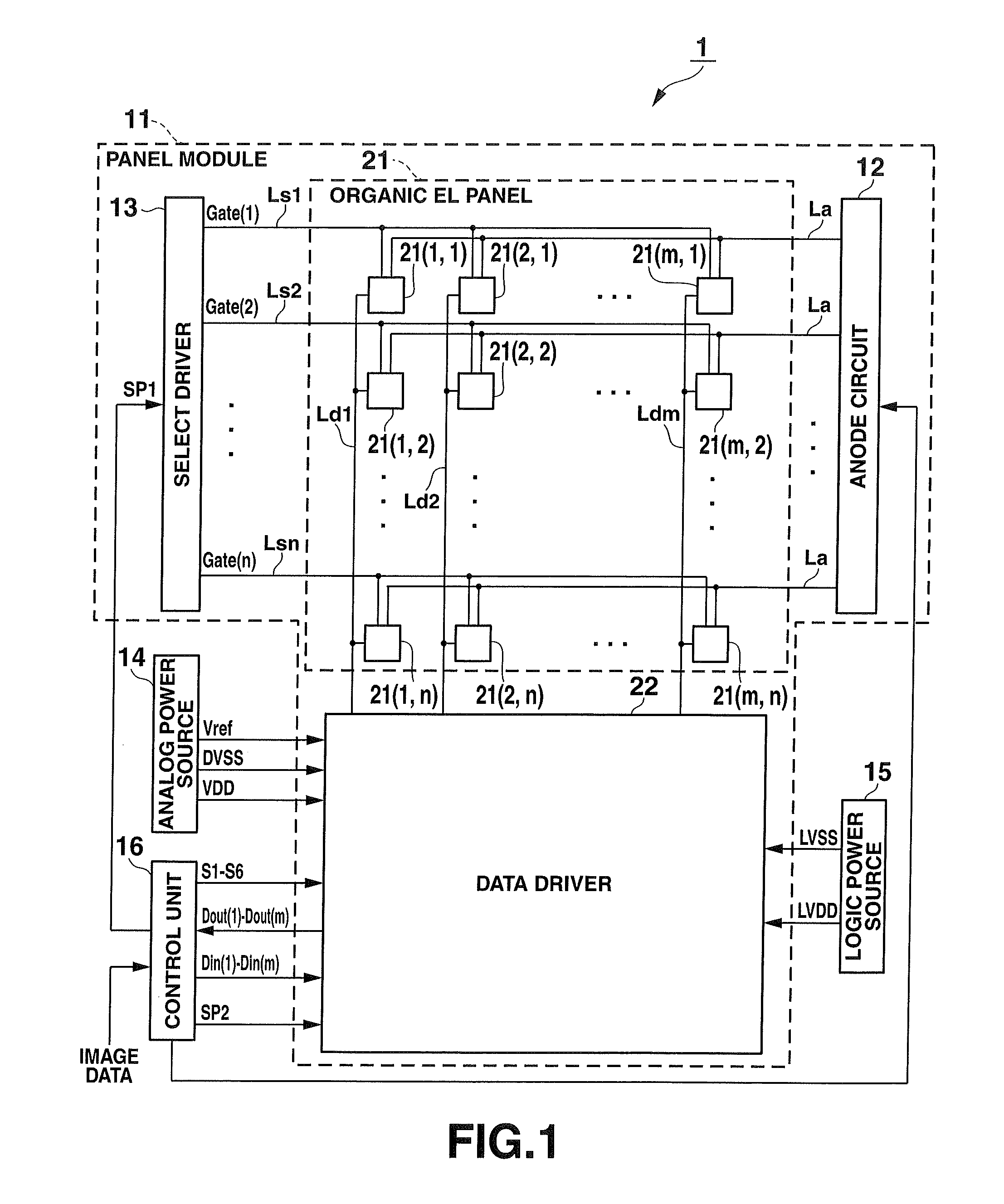

Method and system for driving a pixel circuit in an active matrix display

ActiveUS8223177B2Reduced settling timeEasy to chargeCathode-ray tube indicatorsInput/output processes for data processingActive matrixSignal on

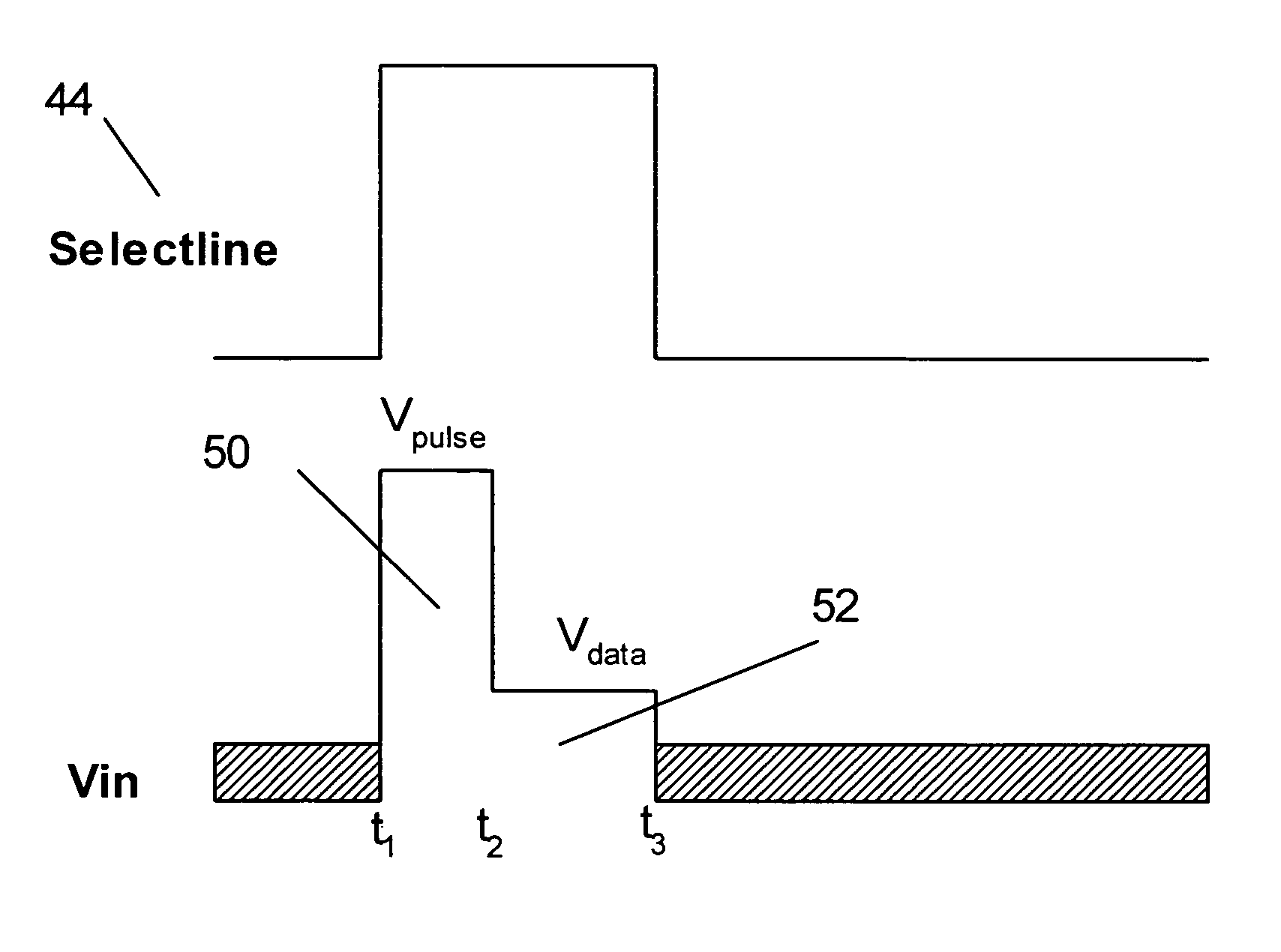

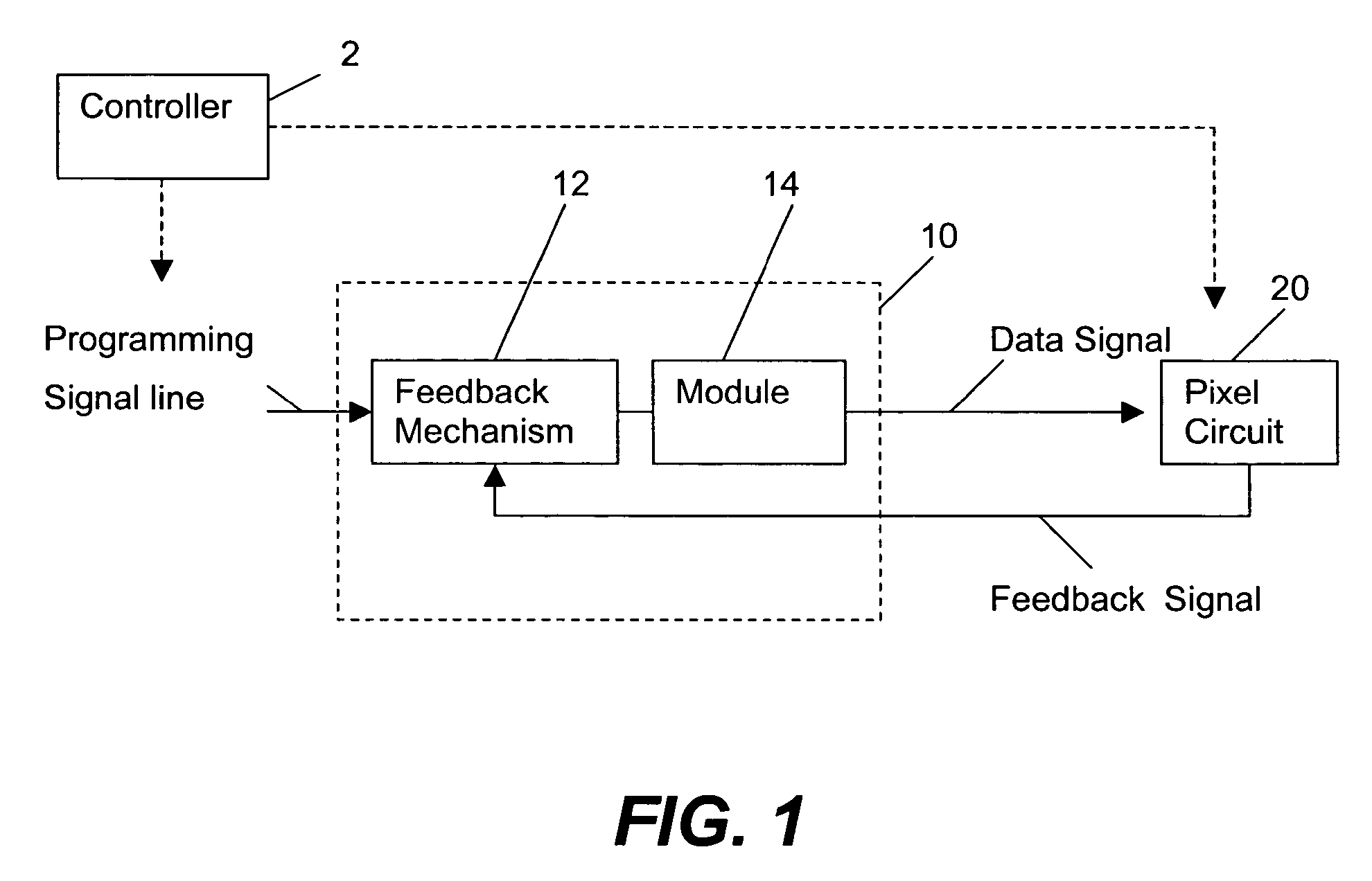

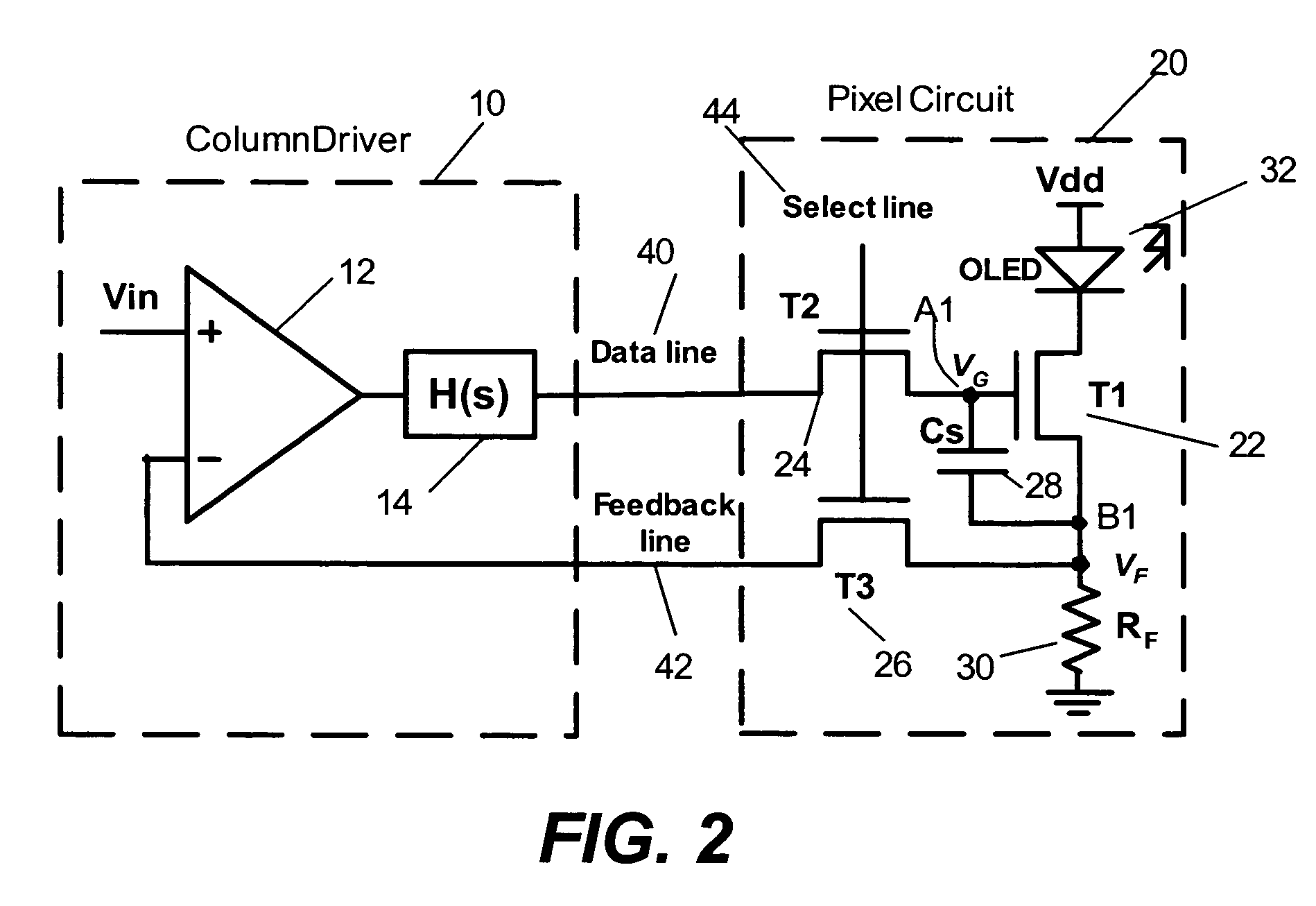

A method and system for driving a pixel circuit in an active matrix display is provided. The system implements a feedback driving scheme to enhance programming speed of the pixel circuit. The system includes a column driver for driving the pixel circuit with feedback. A controller controls a signal on a programming signal line during a programming cycle. For example, the driver may include a model for reducing the settling time of a pixel current. During the programming mode, an accelerating pulse may be provided to accelerate the programming of the pixel circuit.

Owner:IGNIS INNOVATION

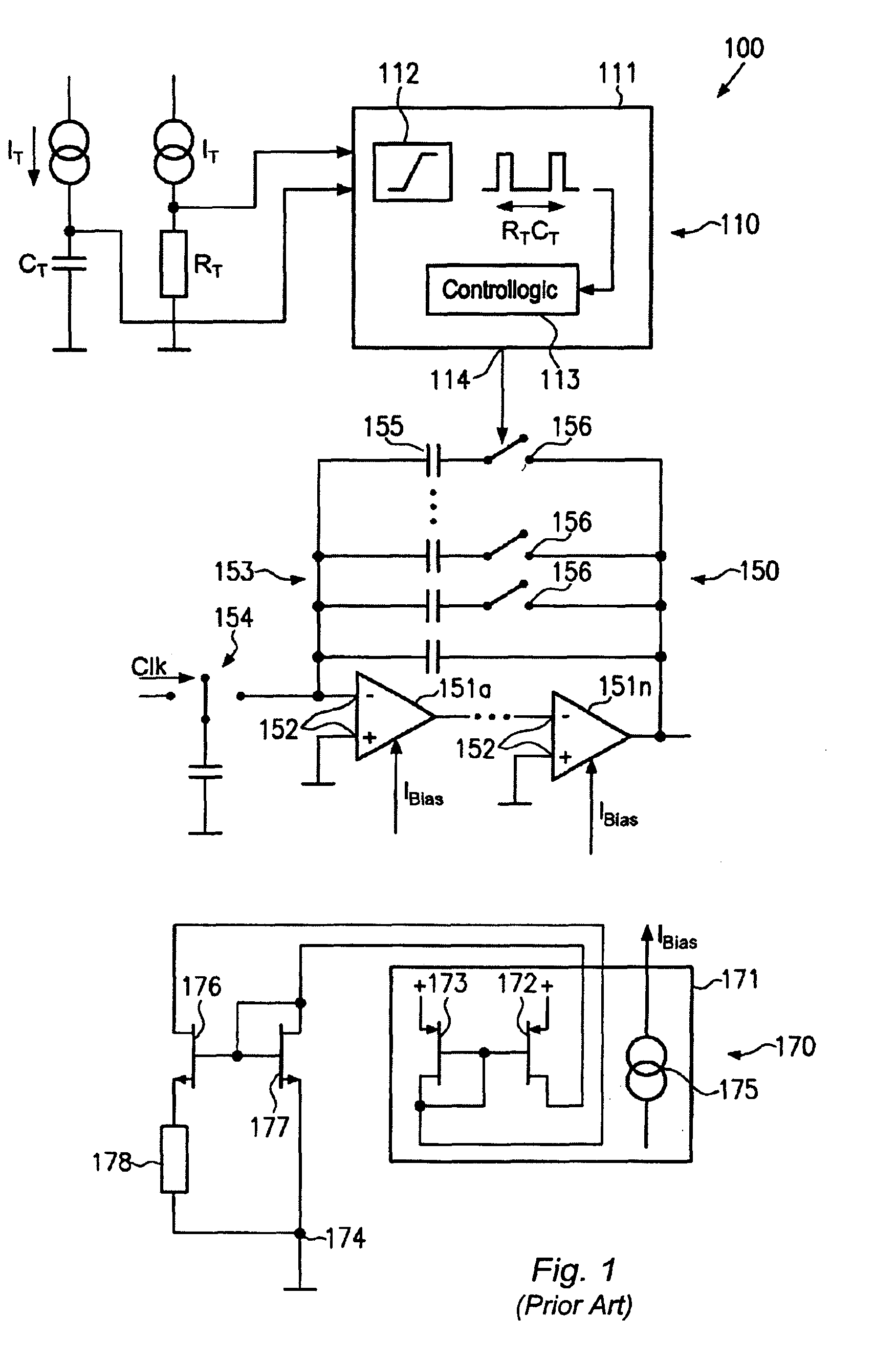

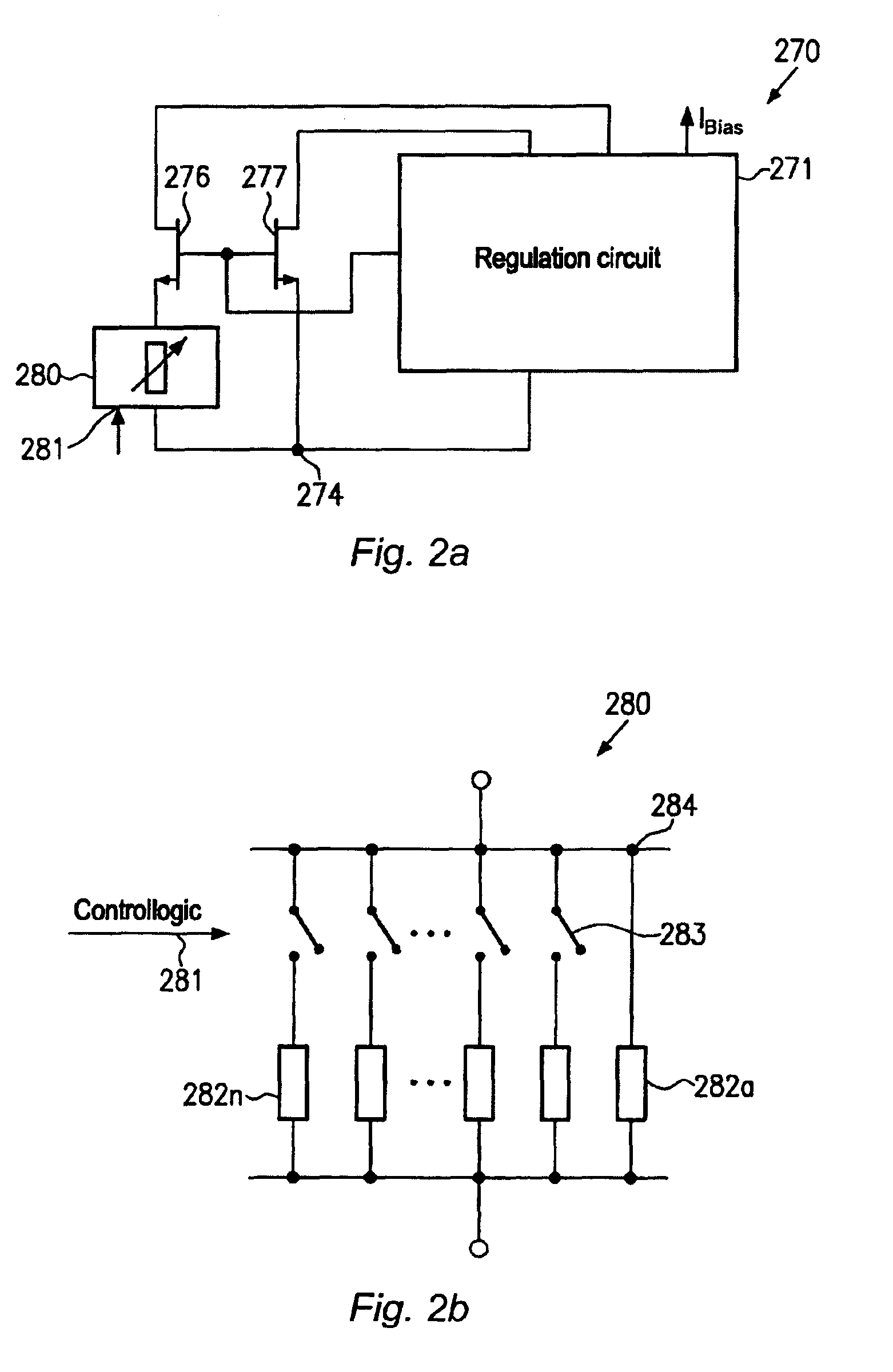

Circuit and a method for controlling the bias current in a switched capacitor circuit

InactiveUS6891439B2Effective compensationAmplifier modifications to reduce temperature/voltage variationAmplifier modifications to raise efficiencyElectrical resistance and conductanceAudio power amplifier

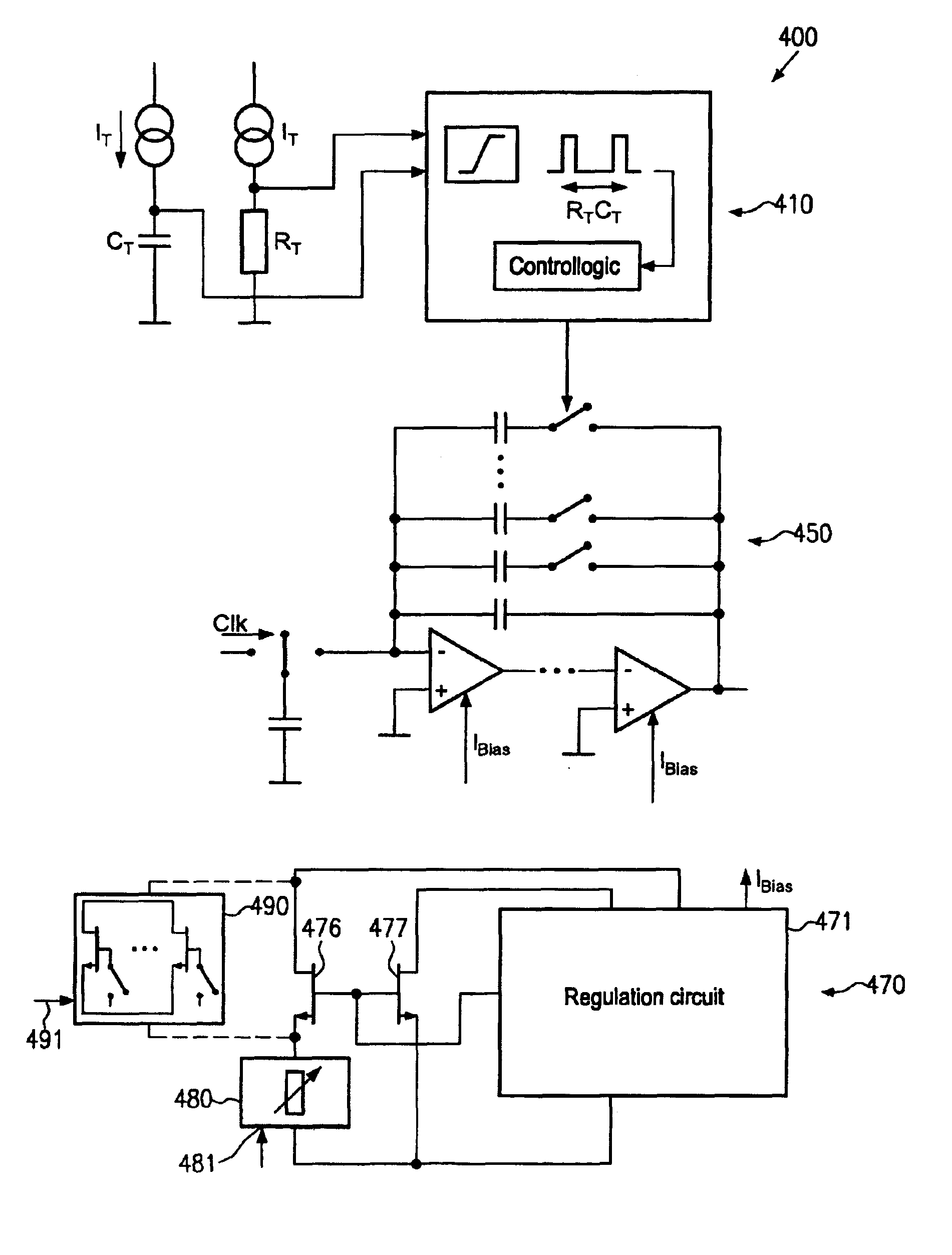

A tunable constant GM circuit allows to compensate for temperature and process variations with high precision by correspondingly adjusting a resistance value and / or the ratio of transistor widths. Thus, in switched capacitor circuits the frequency behaviour, such as the settling time, may be controlled by providing a compensated bias to the transconductance amplifiers typically used in these circuits.

Owner:ADVANCED MICRO DEVICES INC

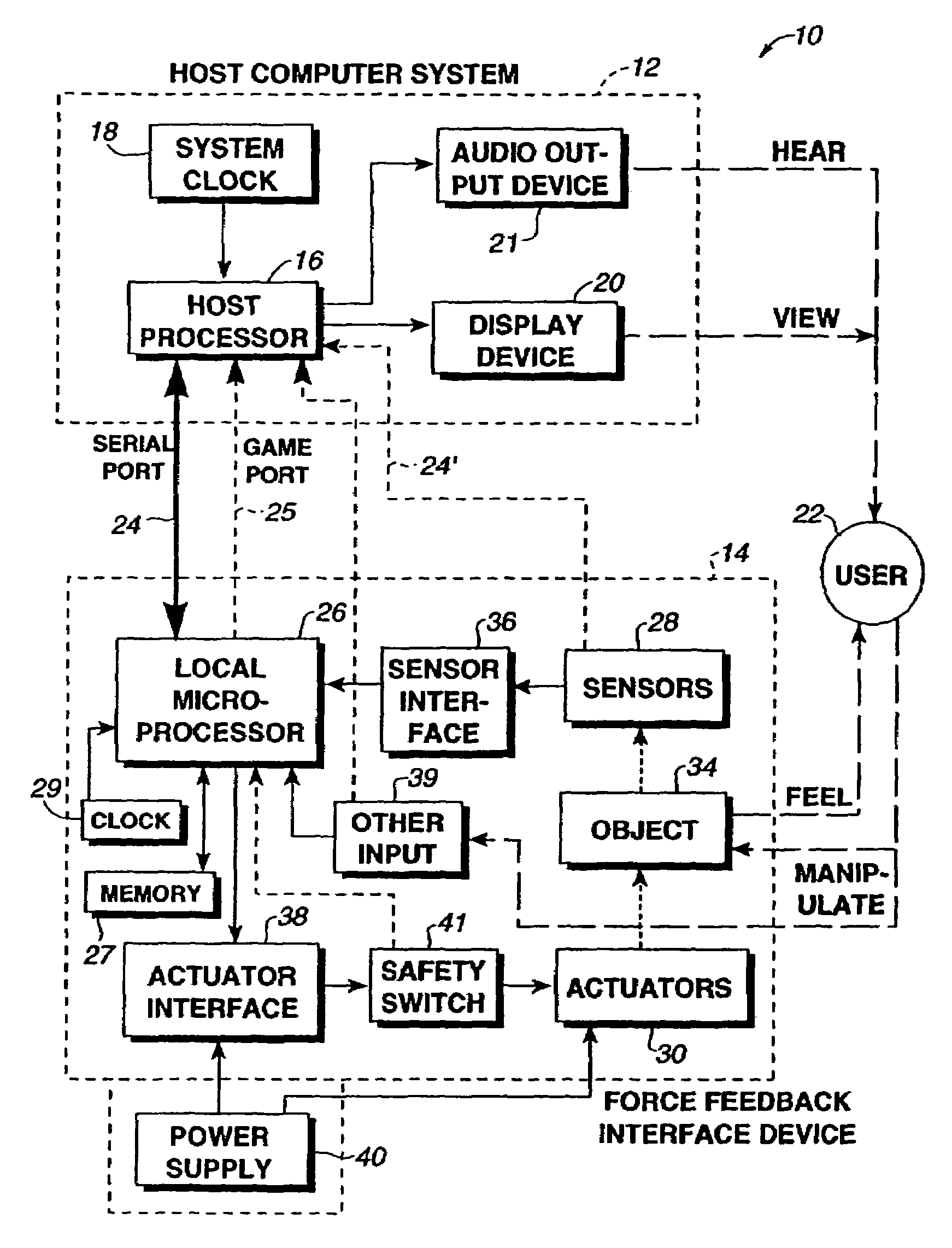

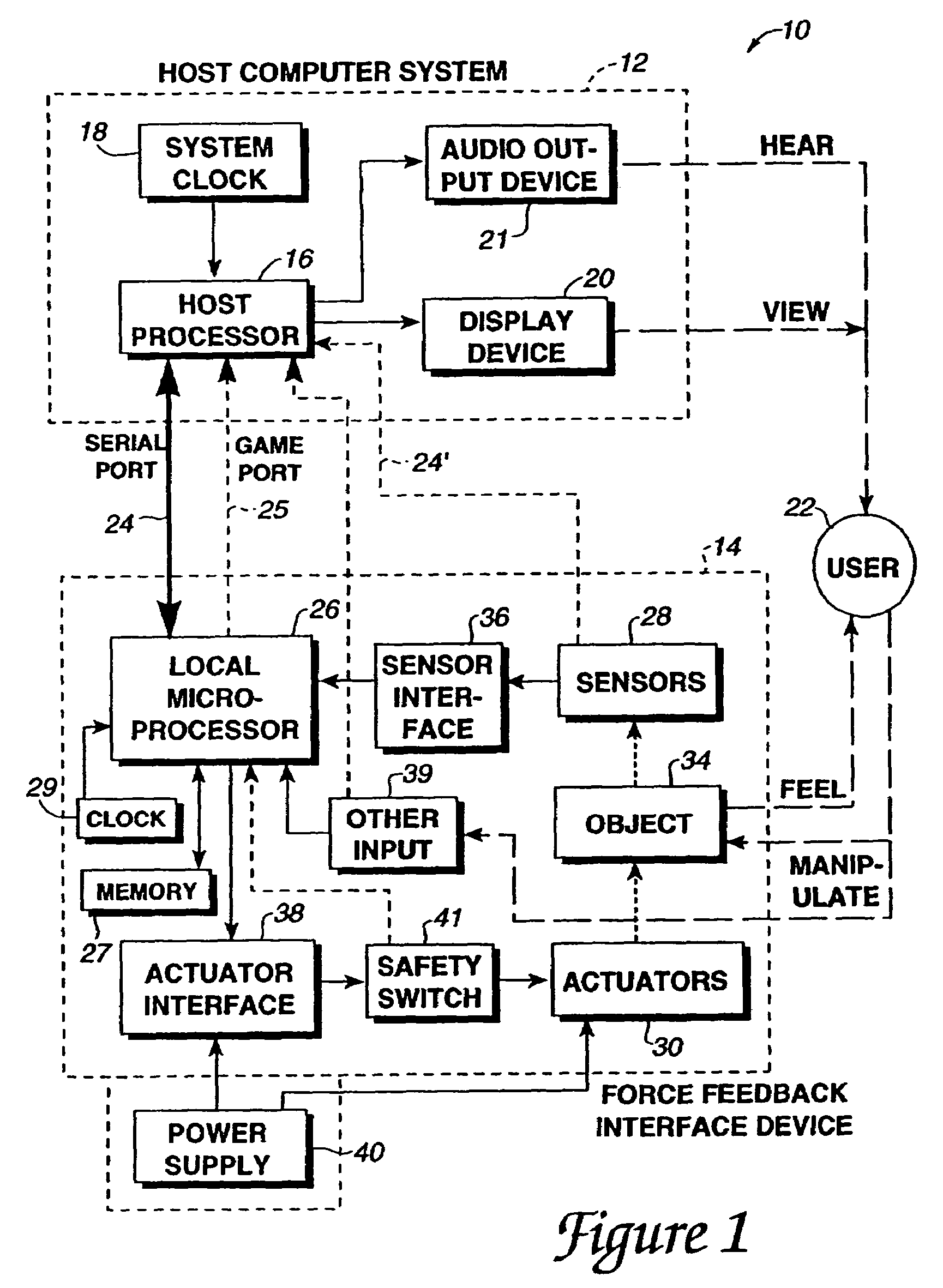

Method and apparatus for streaming force values to a force feedback device

InactiveUS7209117B2Minimal reduction in realismLess forceInput/output for user-computer interactionManual control with multiple controlled membersPulse parameterEngineering

A method and apparatus for shaping force signals for a force feedback device. A source wave is provided and is defined by a set of control parameters (including a steady state magnitude, a frequency value and a duration value) and modified by a set of impulse parameters (including an impulse magnitude, and a settle time representing a time required for the impulse magnitude to change to the steady-state magnitude). Optionally, application parameters specifying a direction of force signal and trigger parameters specifying activating buttons can also be provided for the source wave. Using a host processor or a local processor, the force signal is formed from the source wave and the sets of control parameters and impulse parameters, where the force signal includes an impulse signal followed by a continual steady-state signal after an expiration of the settle time. A feel sensation is generated to a user of the force feedback device as physical forces produced by actuators on the force feedback device in response to the force signal. The steady-state magnitude value is lower than a magnitude value of a non-impulse-shaped force signal required to create a corresponding feel sensation having a similar apparent sensation to the user.

Owner:IMMERSION CORPORATION

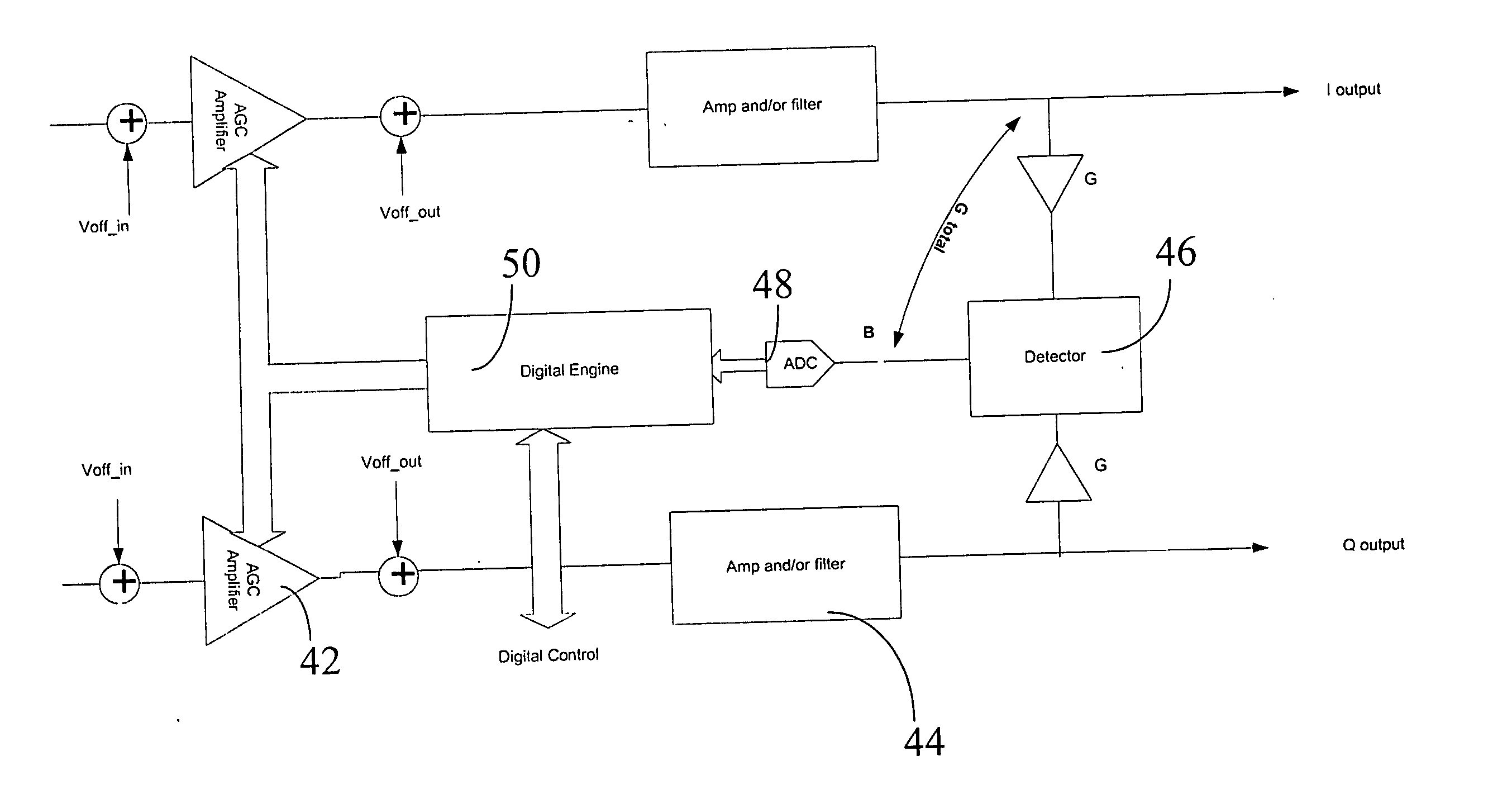

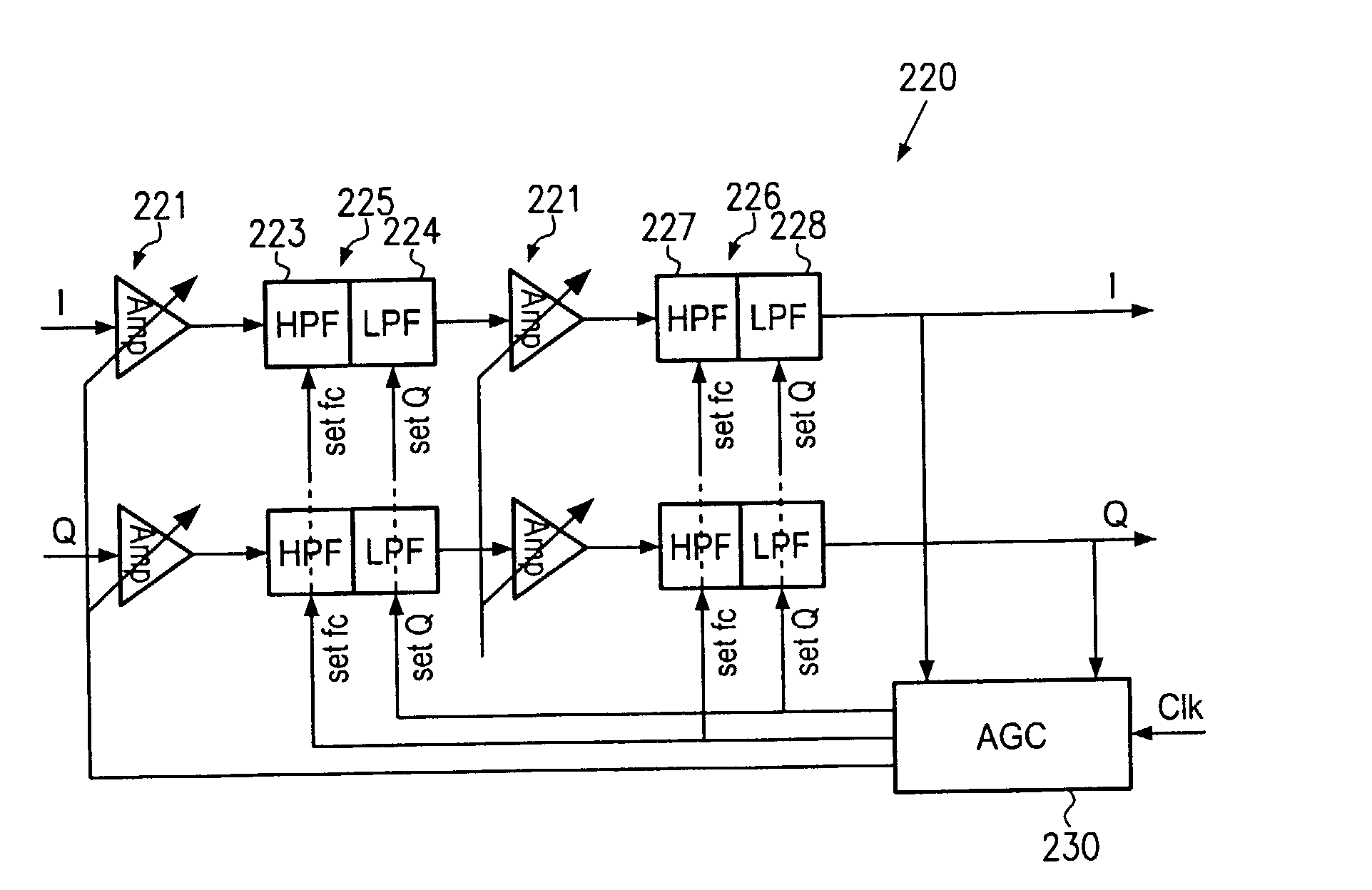

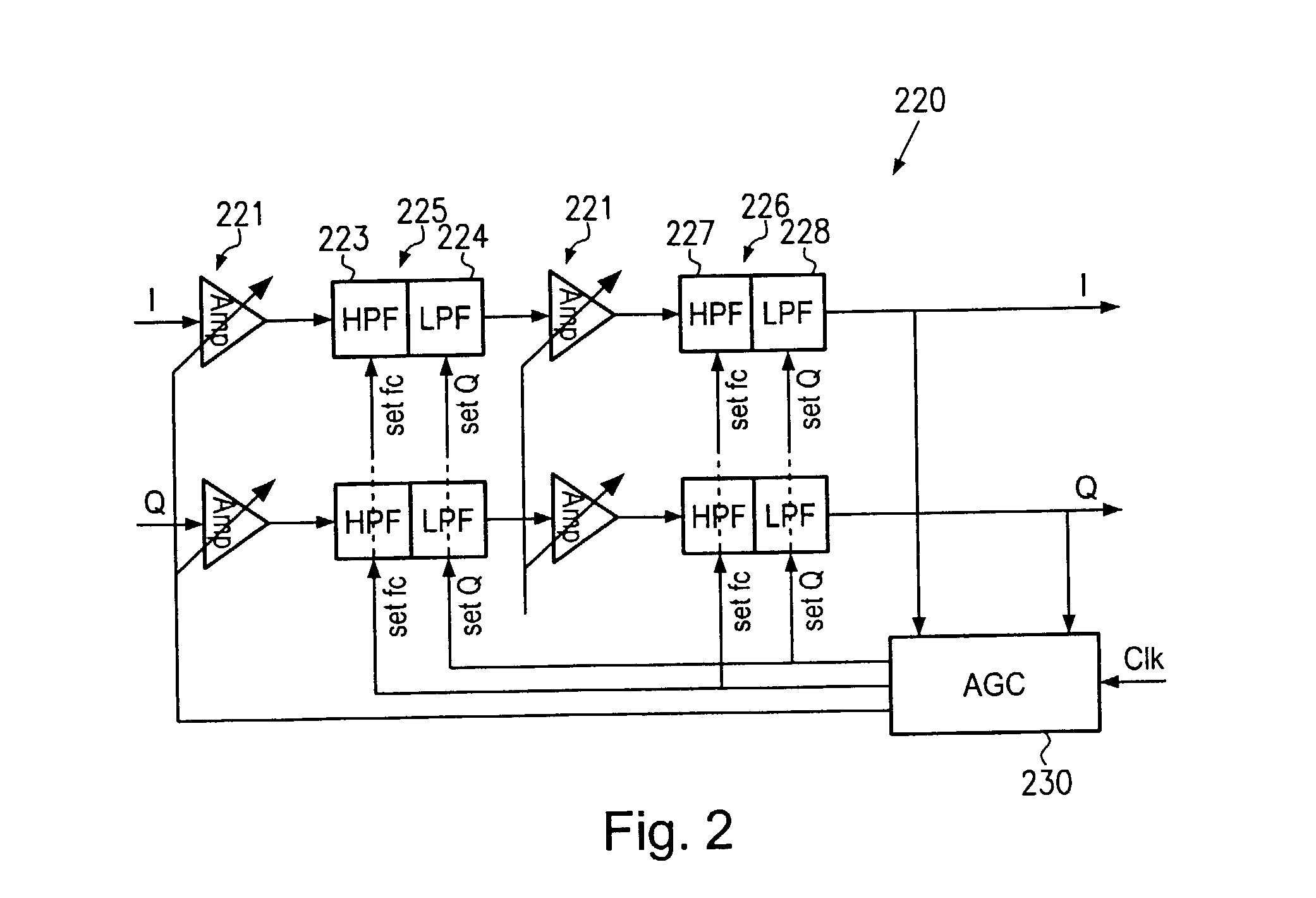

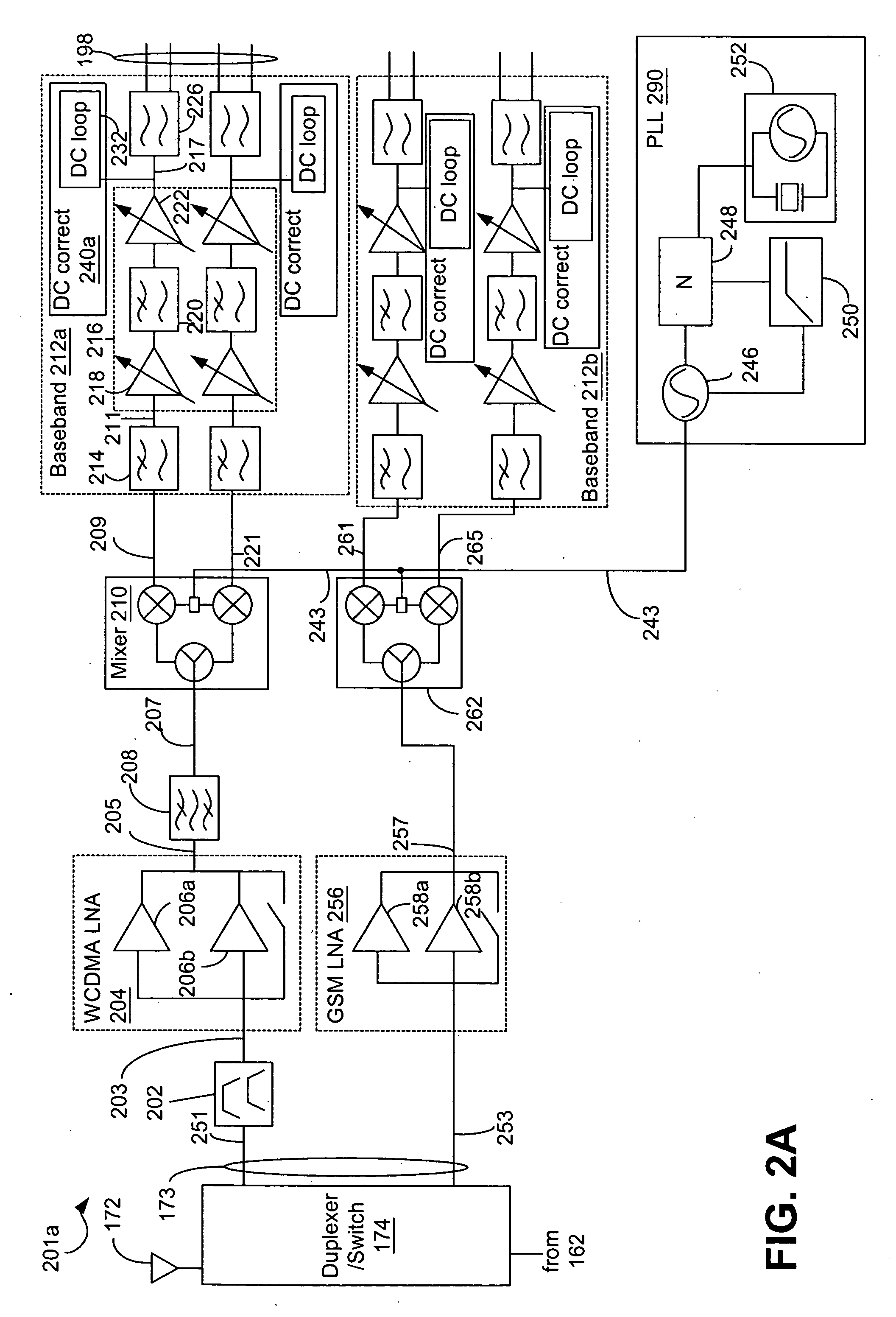

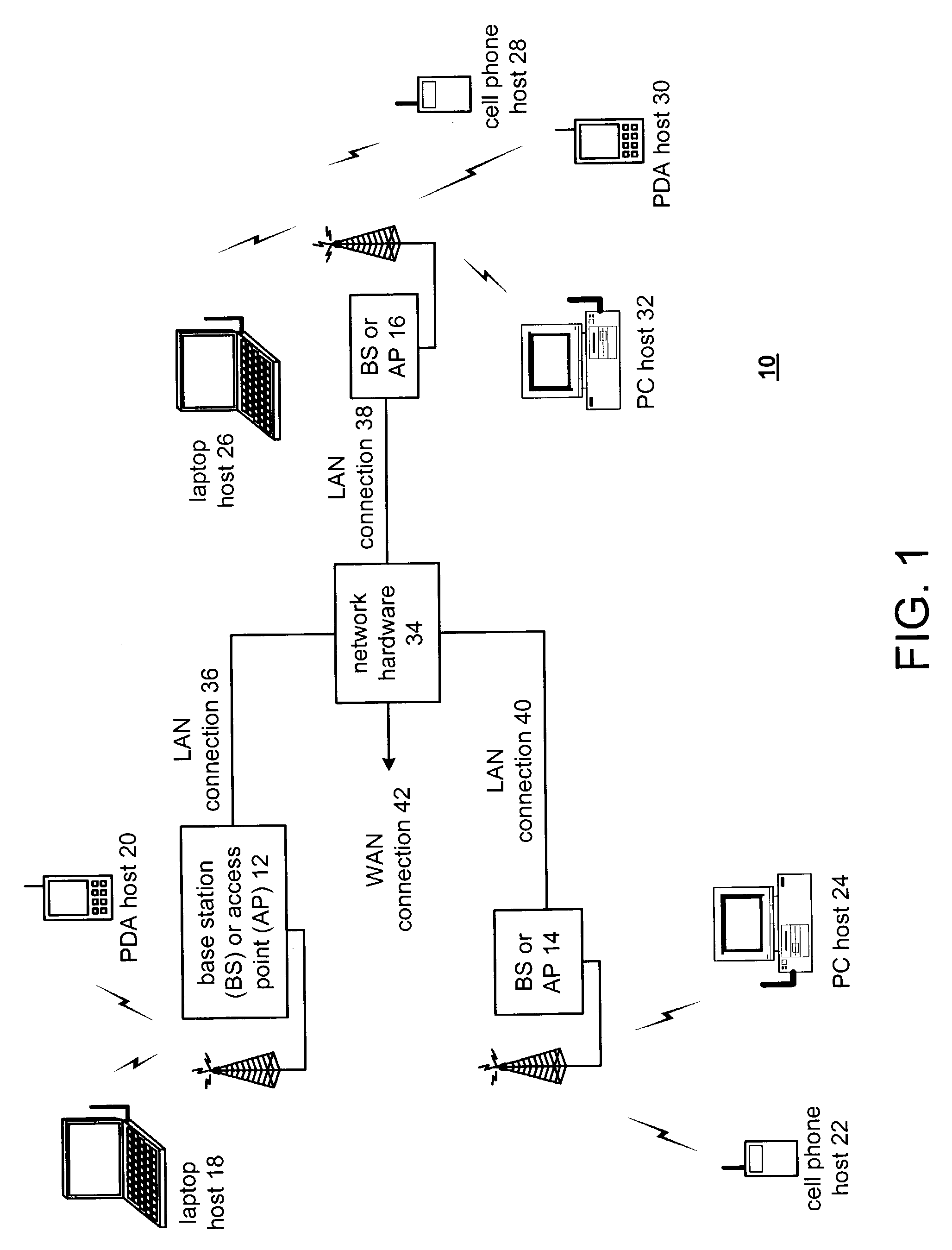

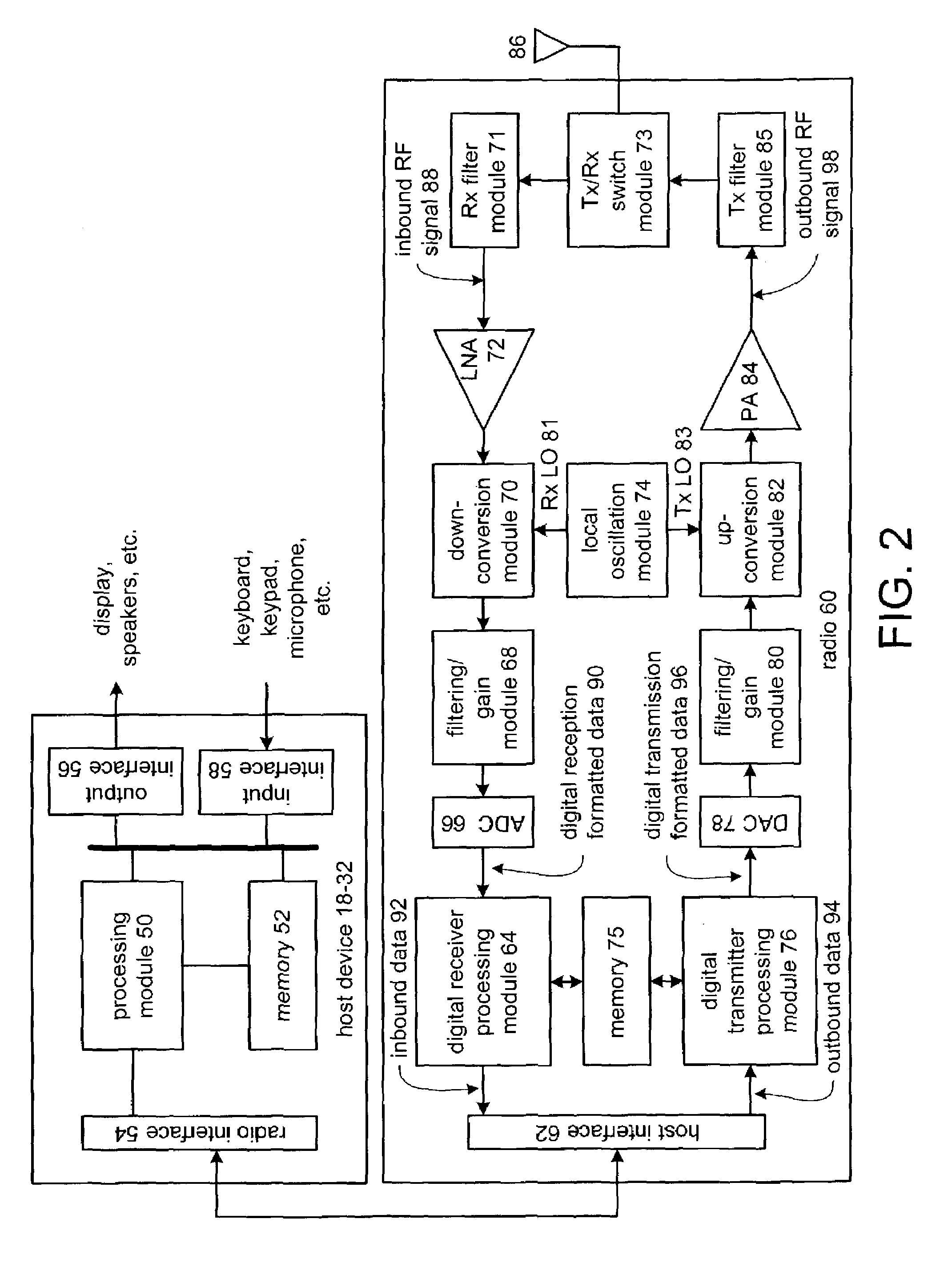

Staggered AGC with digitally controlled VGA

ActiveUS20050058228A1Reduce gain requirementsSimple designDc level restoring means or bias distort correctionLine balance variation compensationVariable-gain amplifierA d converter

The invention relates to the field of wireless communications, more particularly to a method of and device for automatic gain control (AGC) incorporating digitally controlled variable gain amplifiers (VGAs). The invention provides an AGC circuit comprising an I / Q baseband strip comprising multiple AGC stages wherein each of the AGC stages comprises: respective I and Q VGAs; a detector for detecting respective I and Q output signals received from the respective I and Q VGAs; an analogue to digital converter (ADC) for converting the detected I and Q output signals; and a digital engine for adjusting the respective I and Q VGAs for differences between the detected I and Q output signals and a reference signal. The use of staggered AGCs incorporating respective I and Q VGAs means that the total dynamic range is split between n-stages, thereby allowing for reduced gain requirements in the VGAs. Additionally, the use of digital control for setting the VGA gains means that analogue variations and I / Q gain imbalances are reduced. Additionally, the use of multiple update rates or magnitudes in the VGA control improves the dynamic settling time.

Owner:ZARBANA DIGITAL FUND

Light emitting device and a drive control method for driving a light emitting device

ActiveUS20100134469A1The voltage value is accurateCathode-ray tube indicatorsInput/output processes for data processingSignal correctionEngineering

A light emitting device has a plurality of pixels, each of which includes a drive transistor, a light emitting element and signal lines, a property parameter acquisition circuit which acquires property parameter, a signal correction circuit that generates a corrected gradation signal by correcting the image data based on the property parameter, and a drive signal impressing circuit that impresses a drive signal, generated based on the corrected gradation signal, on the pixel to drive it. The property parameter is constituted of a threshold voltage, a current amplification factor and its irregularity of the drive transistor, and is acquired based on measured voltages of the signal lines after each of a plurality of predetermined settling times elapses from the time when the light emitting device cuts off a voltage subsequent to impressing the voltage on each pixel for a predetermined length of time.

Owner:SOLAS OLED LTD

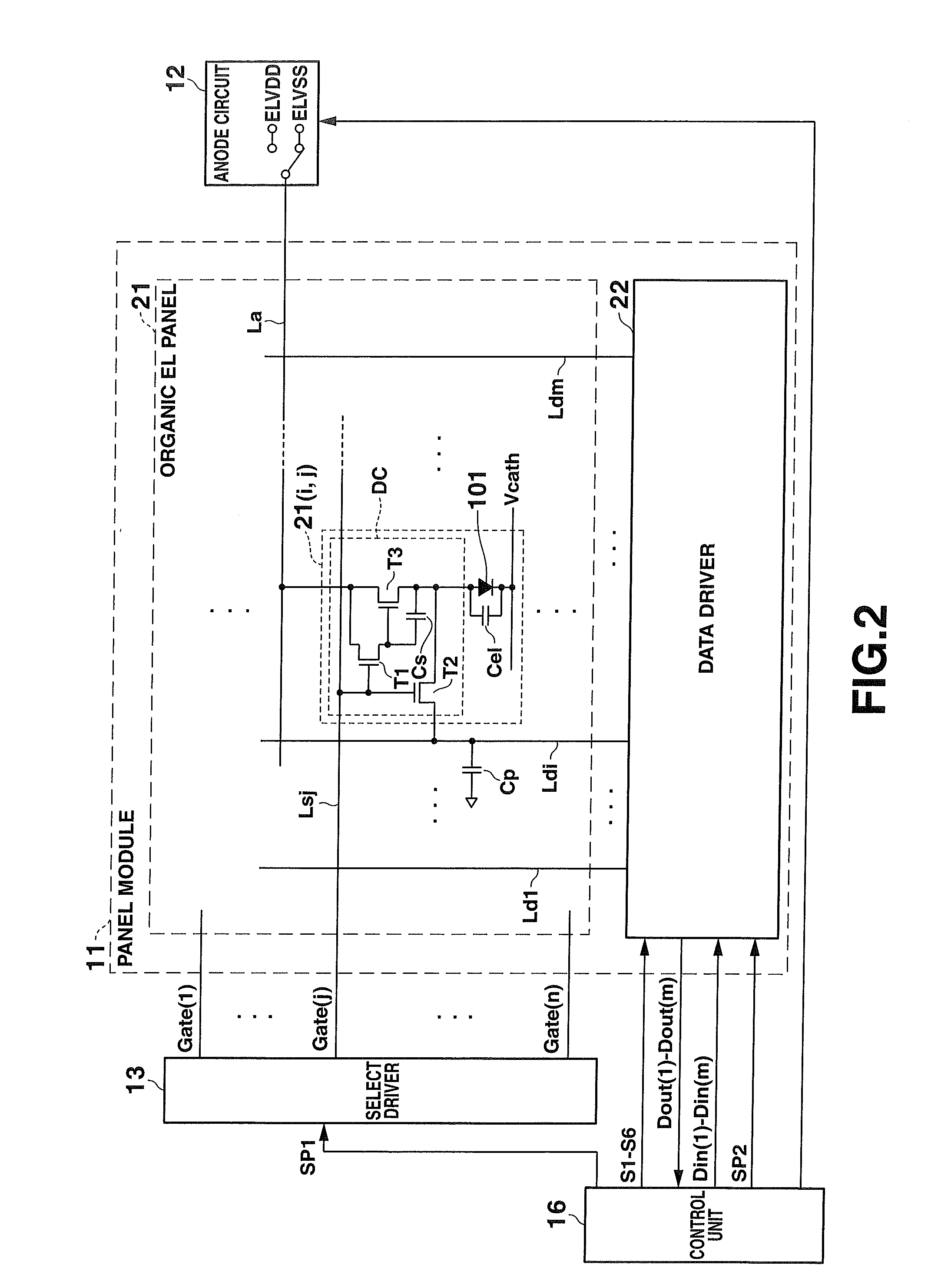

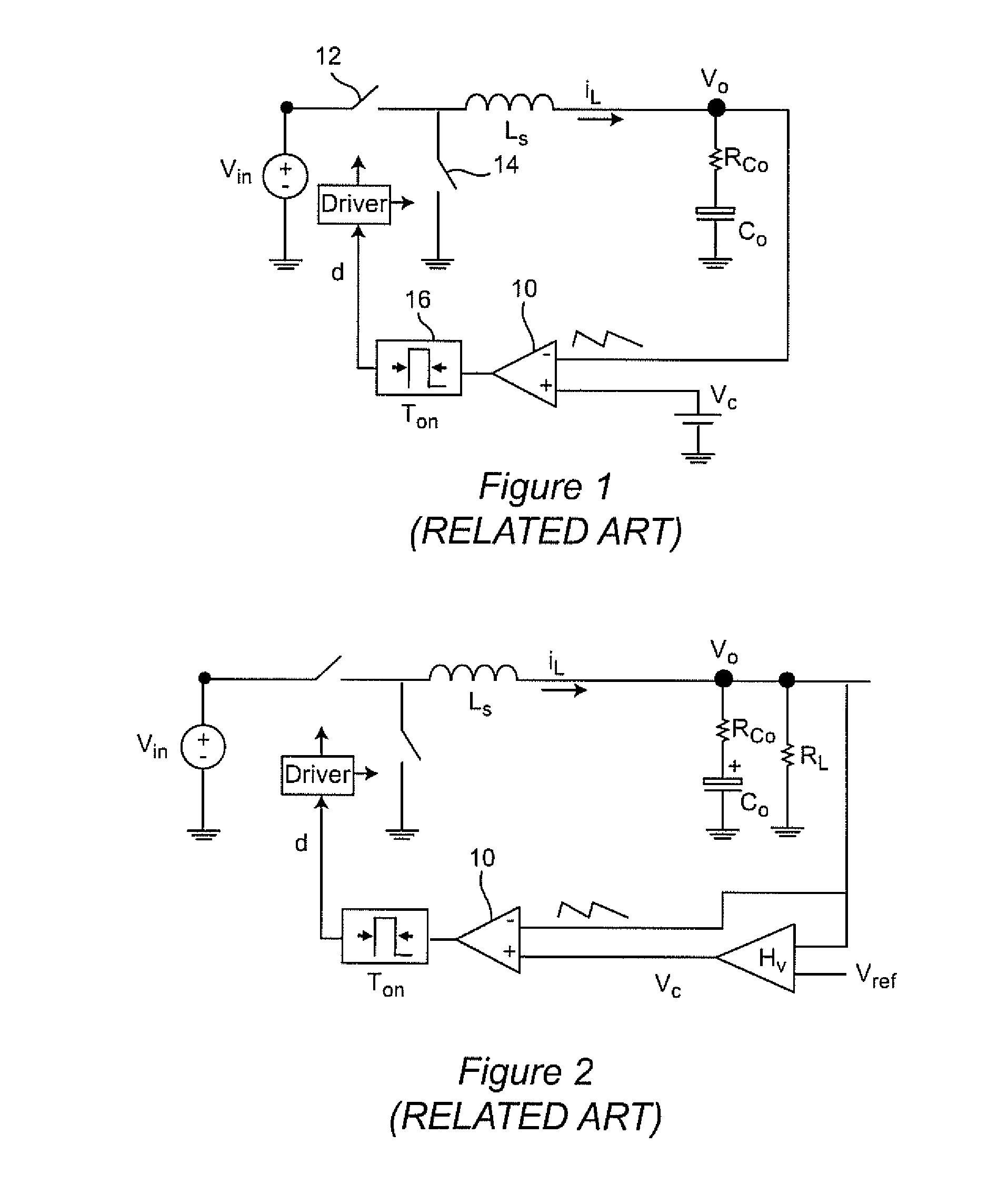

V+hu 2 +l Power Converter Control with Capacitor Current Ramp Compensation

Operation of a switching power converter having an output capacitor having a small equivalent series resistance (ESR) is stabilized and jitter reduced by sensing capacitor current with gain and combining the resulting signal with the output voltage signal to provide a feedback signal to control switching of the power converter. capacitor current can be sensed without interfering with operation of the filter capacitor by providing a branch circuit having a time constant matched to the output or filter capacitor but an arbitrarily high impedance so as to be effectively lossless. The gain provided in the capacitor current signal can be tuned to provide optimally short settling time after load transients; generally within one switching cycle. Matching of time constants and / or tuning of gain can be performed automatically.

Owner:VIRGINIA TECH INTPROP INC

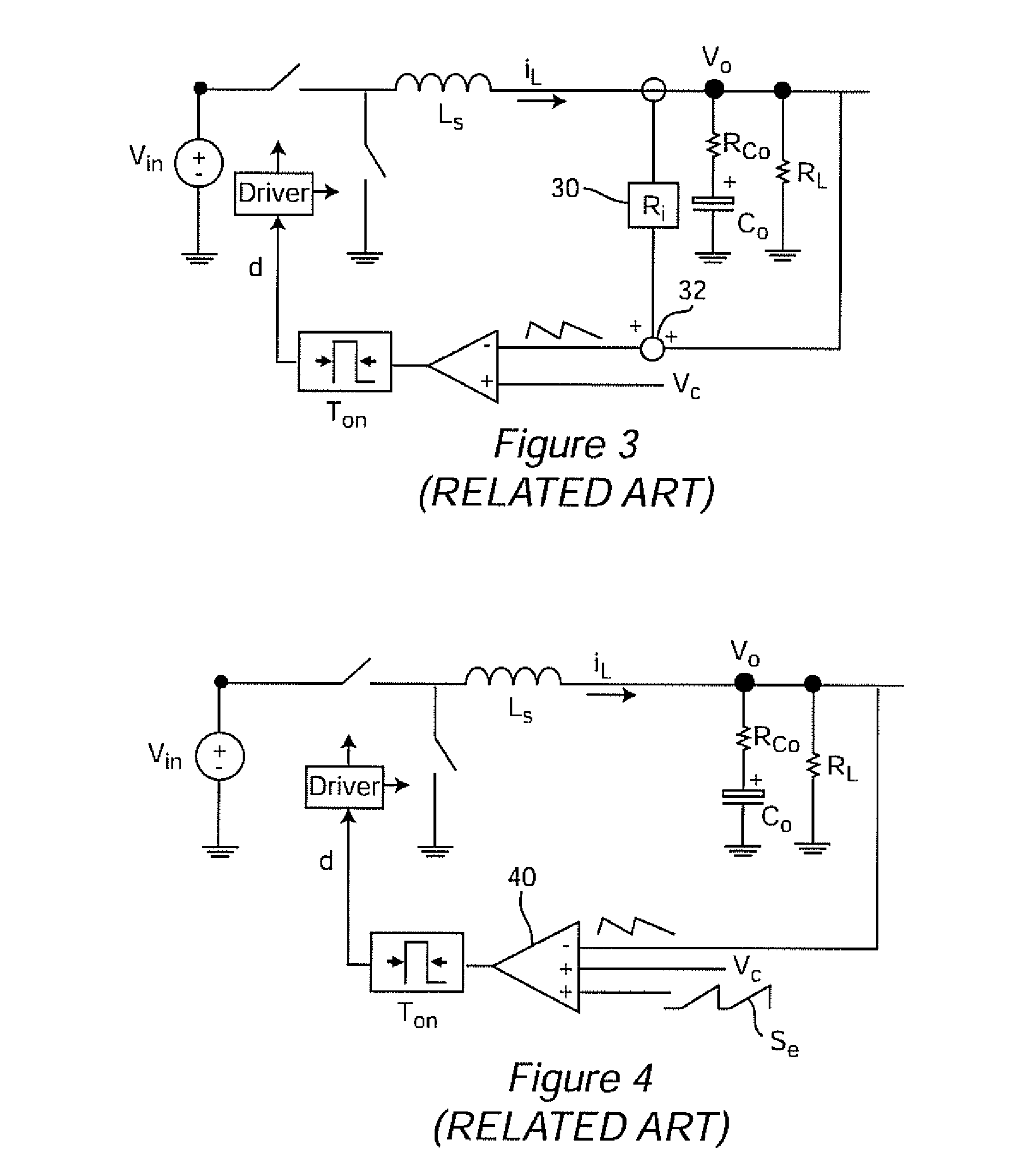

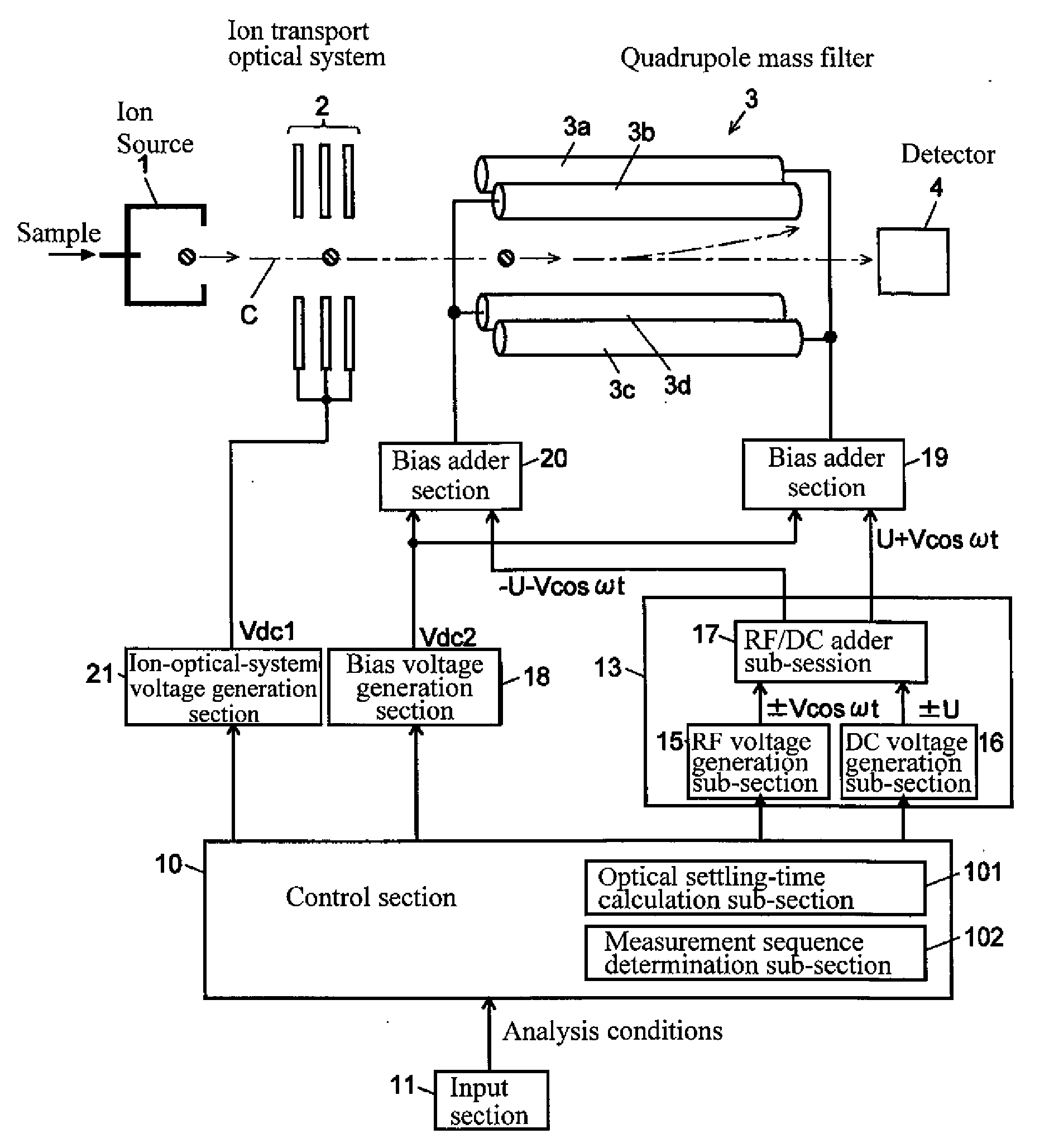

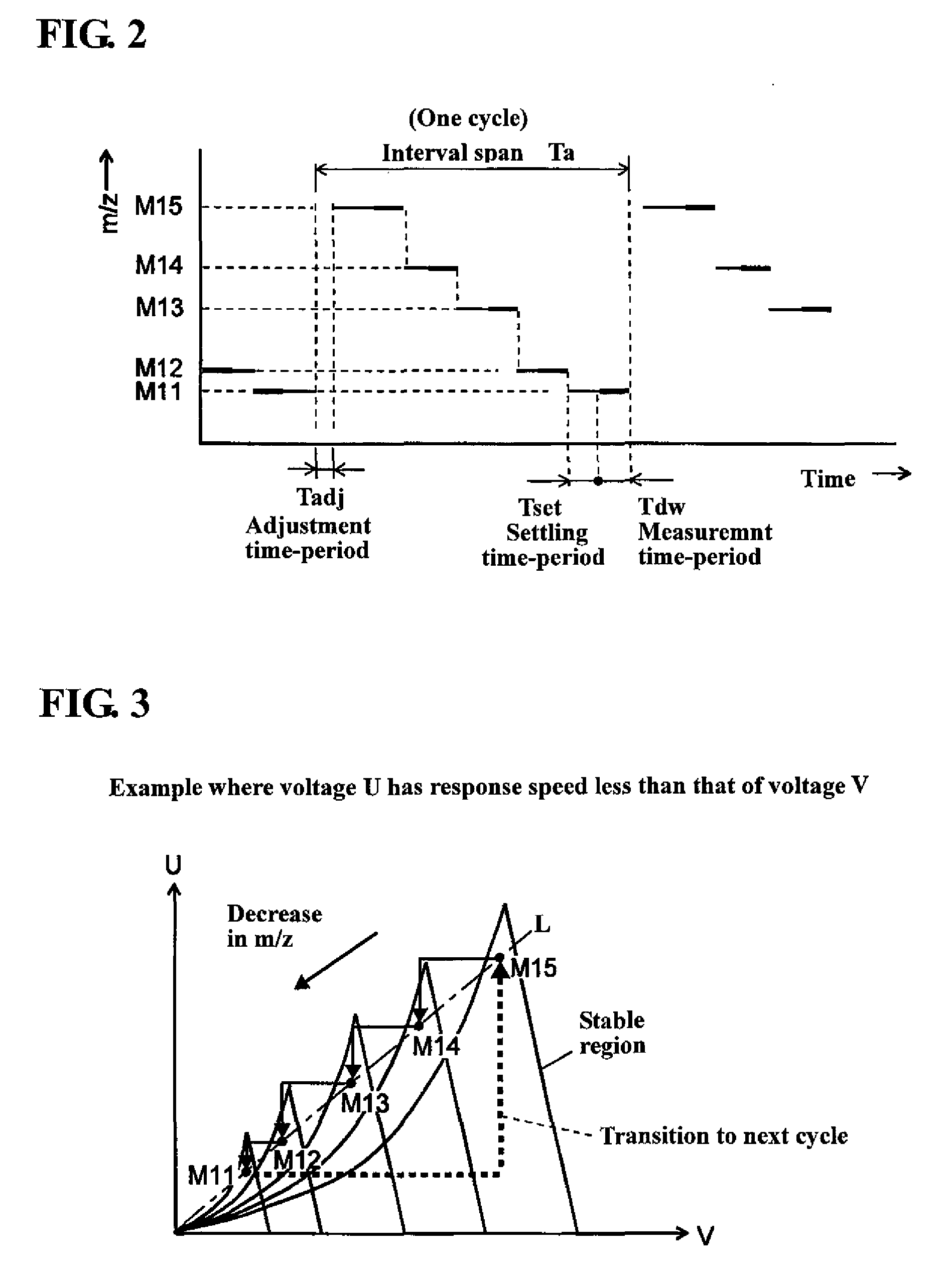

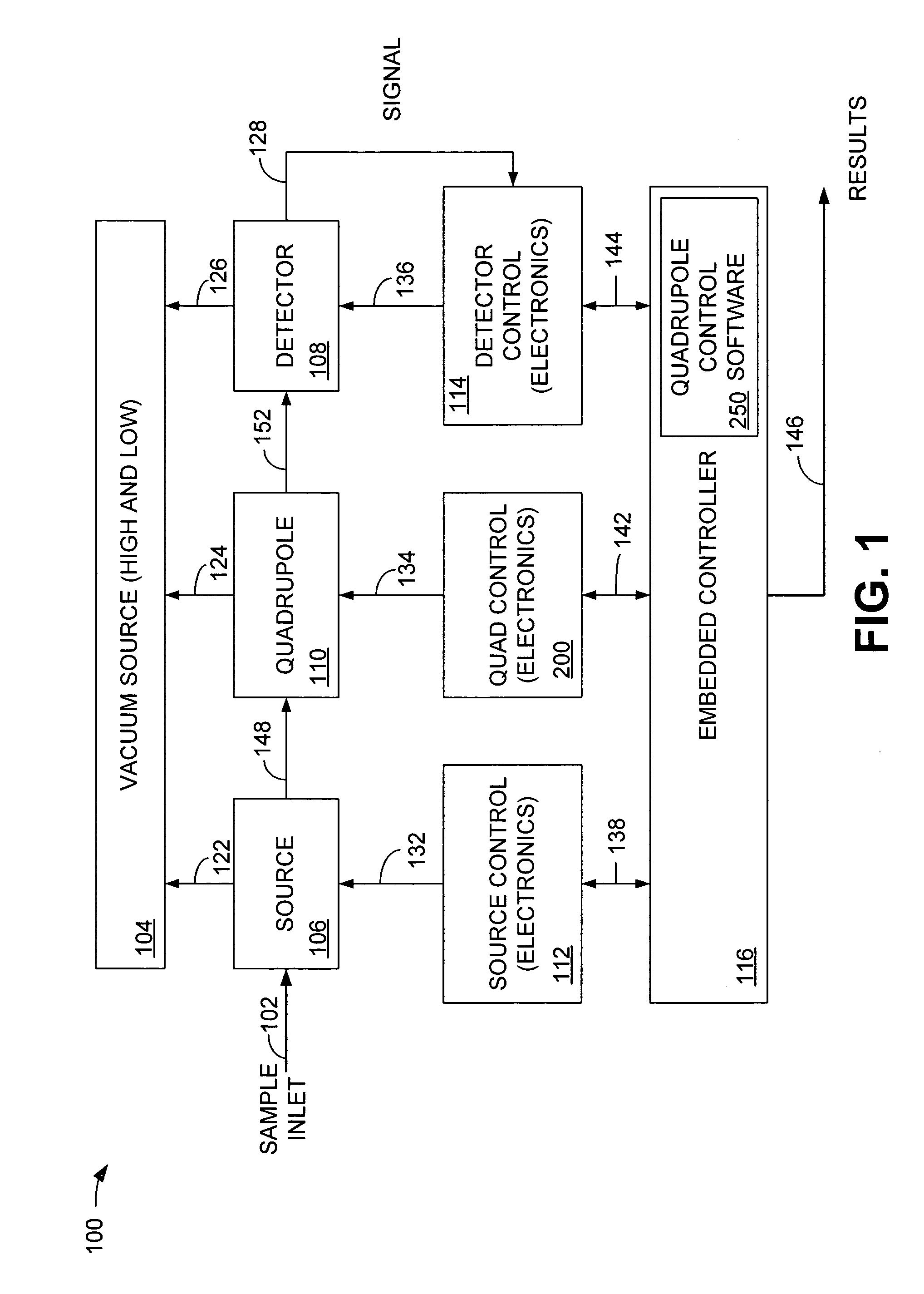

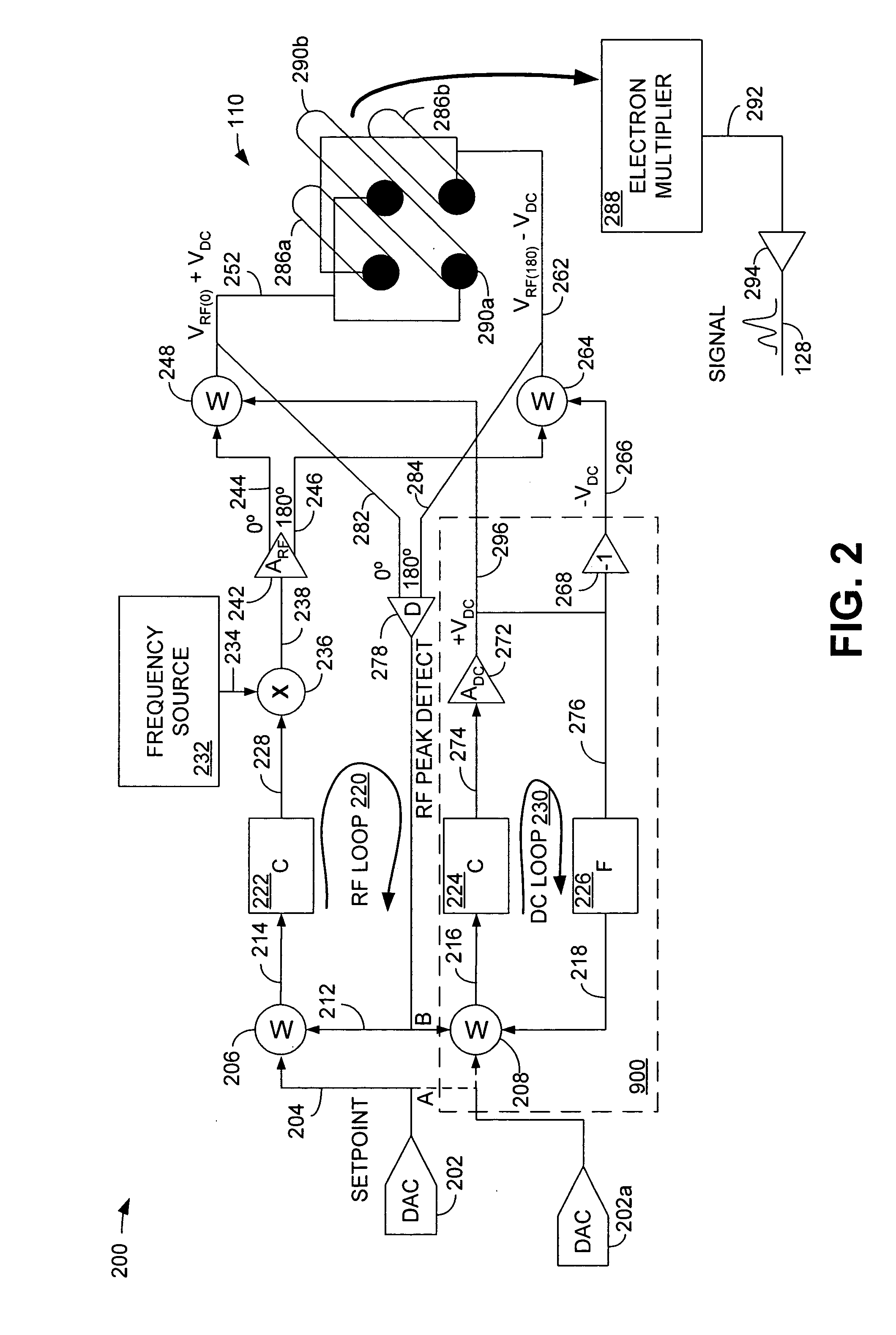

Quadrupole mass spectrometer

ActiveUS20100084552A1Improve time resolutionRaise the ratioStability-of-path spectrometersSamples introduction/extractionClassical mechanicsQuadrupole

Disclosed is a quadrupole mass spectrometer, which is capable of, during an SIM measurement, maximally reducing a settling time-period necessary for an operation of changing an input voltage to a quadrupole mass filter in a staircase pattern, and preventing unwanted ions from excessively entering a detector during a course of changing between a plurality of mass values. Under a condition that a response speed of a DC voltage U to be applied to quadrupole electrodes is less than that of an amplitude of a high-frequency voltage V, a control section 10 is operable to rearrange the mass values in descending order of mass value, and an optimal settling-time calculation sub-section 101 is operable to determine a settling time-period for each of the mass values, based on a mass-value difference and a post-change mass value.

Owner:SHIMADZU CORP

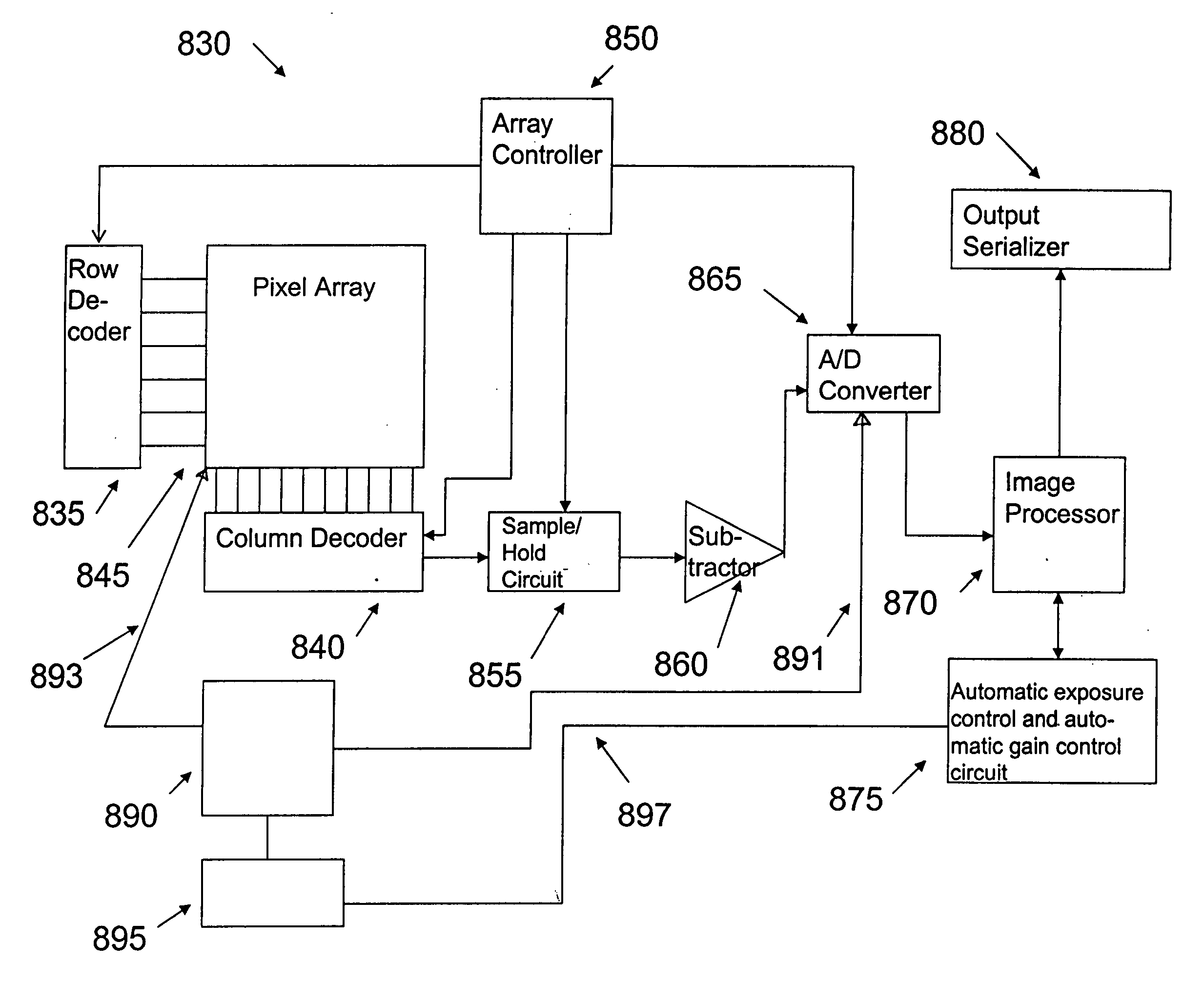

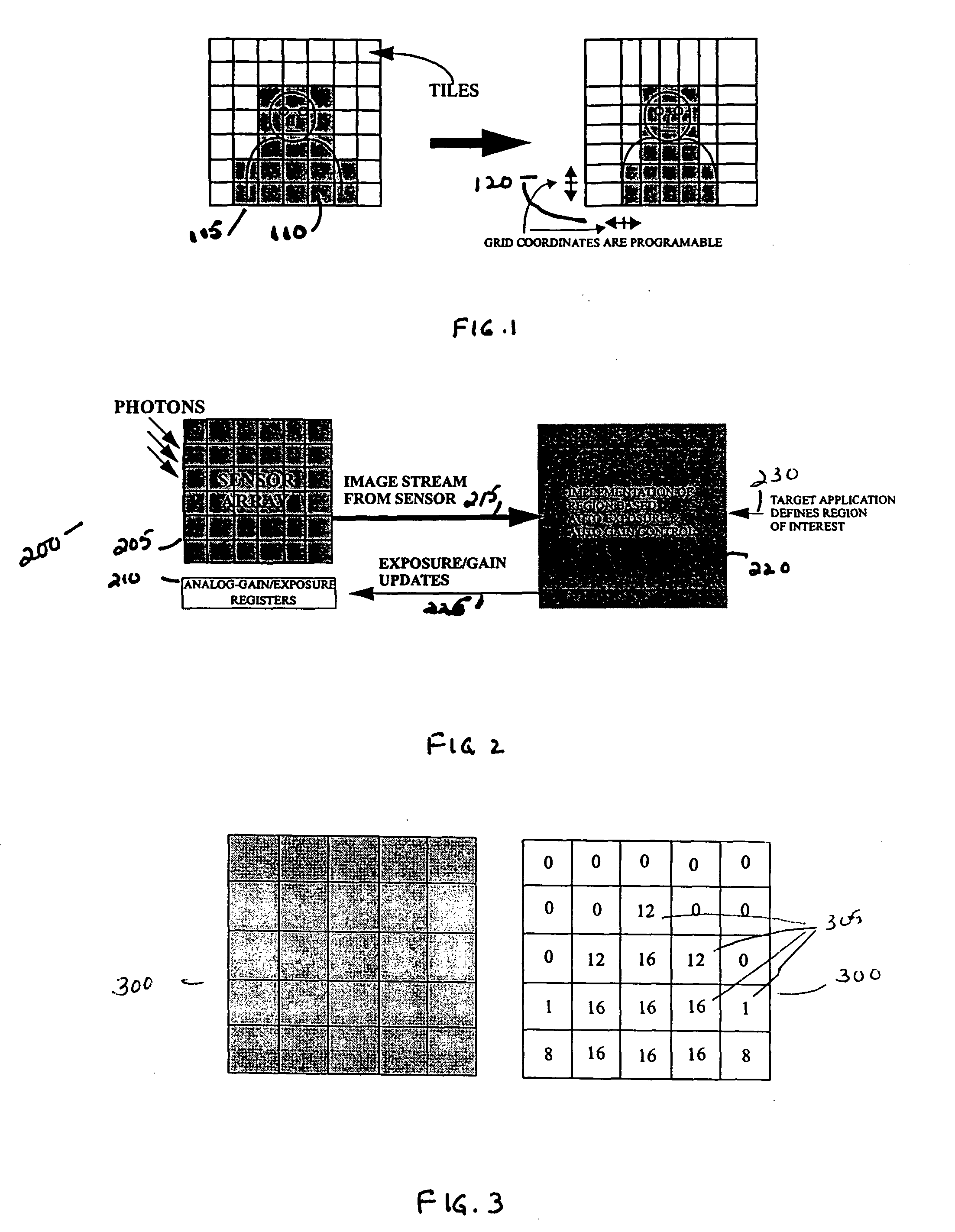

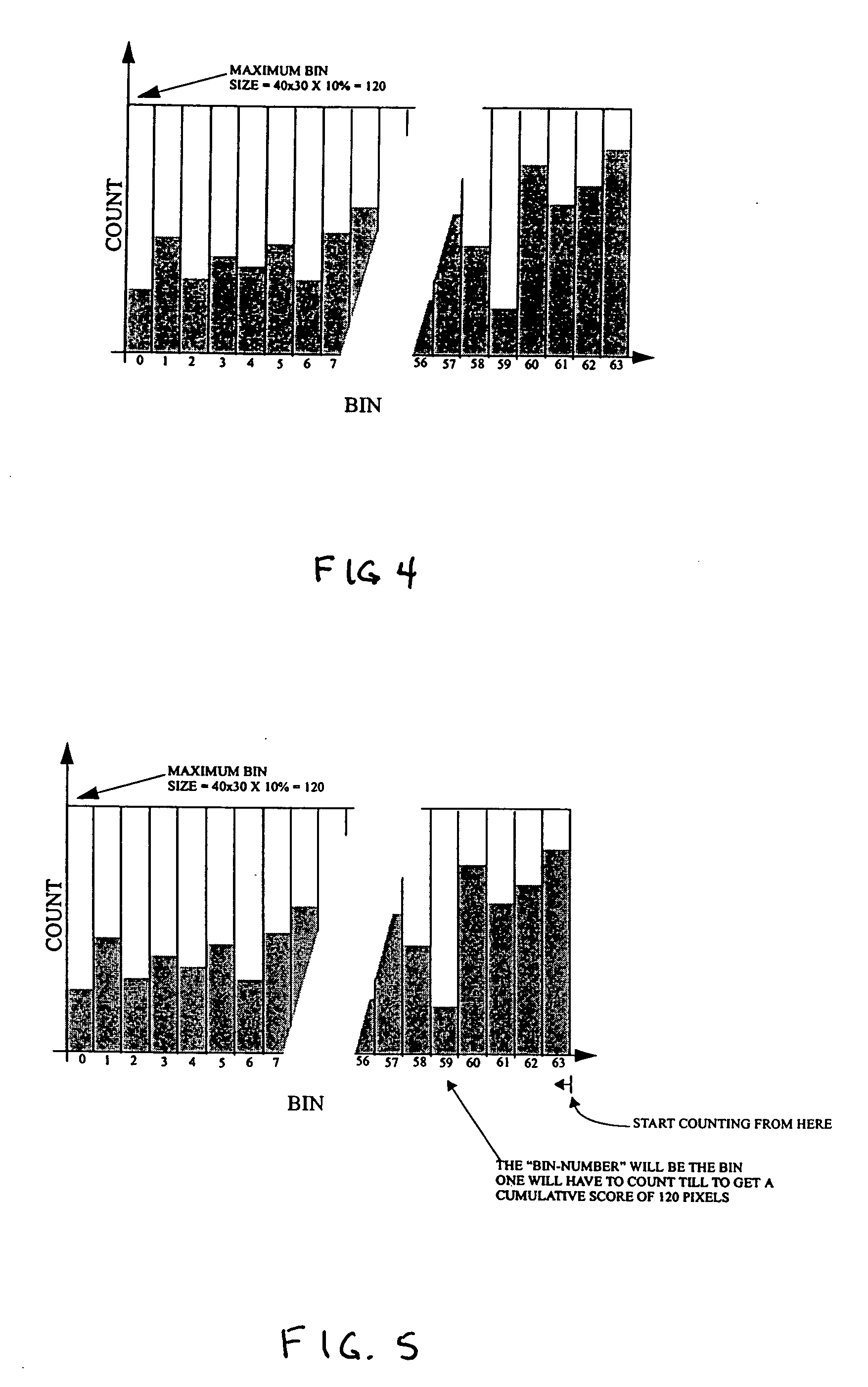

Region-based auto gain control and auto exposure control method and apparatus

ActiveUS20050057666A1Television system detailsCharacter and pattern recognitionSensor arrayExposure control

An apparatus and method for performing automatic exposure and gain control while minimizing oscillations as well as providing a good response time, for example, a lag time or a settling time of about one frame. The automatic exposure and gain controls are performed not only on the image as a whole but on a weighted region of interest. If the contrast in the image exceeds the dynamic range of the sensor array, then the image in the region of interest will improve at the expense of the remainder of the image. A region of interest is a selected subset of tiles upon which automatic exposure and gain control will be based. The tiles are defined by a grid system having grid coordinates, which are programmable. Image sensors have to receive feedback with regular updates of exposure and gain settings based on ever changing light conditions.

Owner:MICRON TECH INC

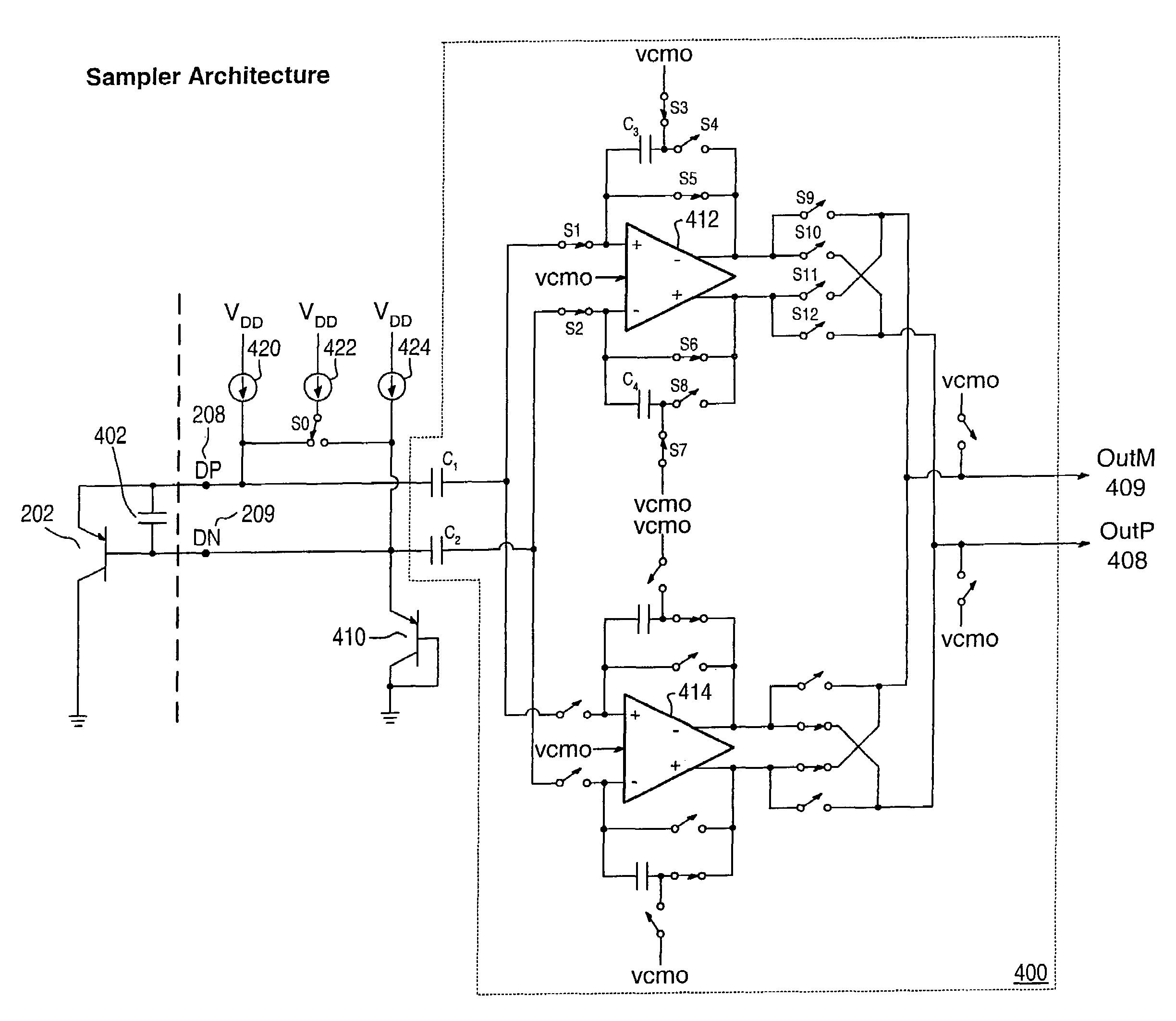

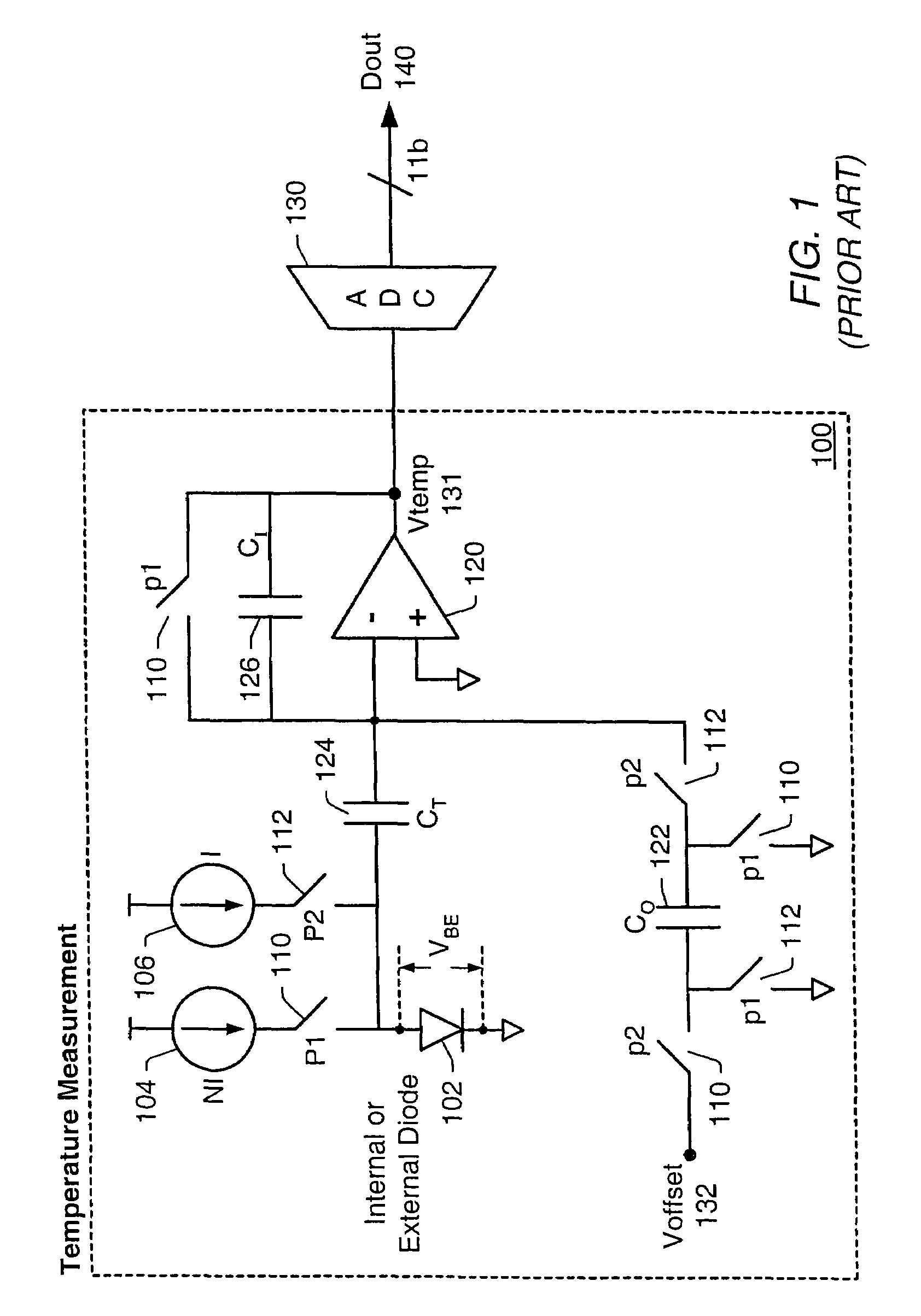

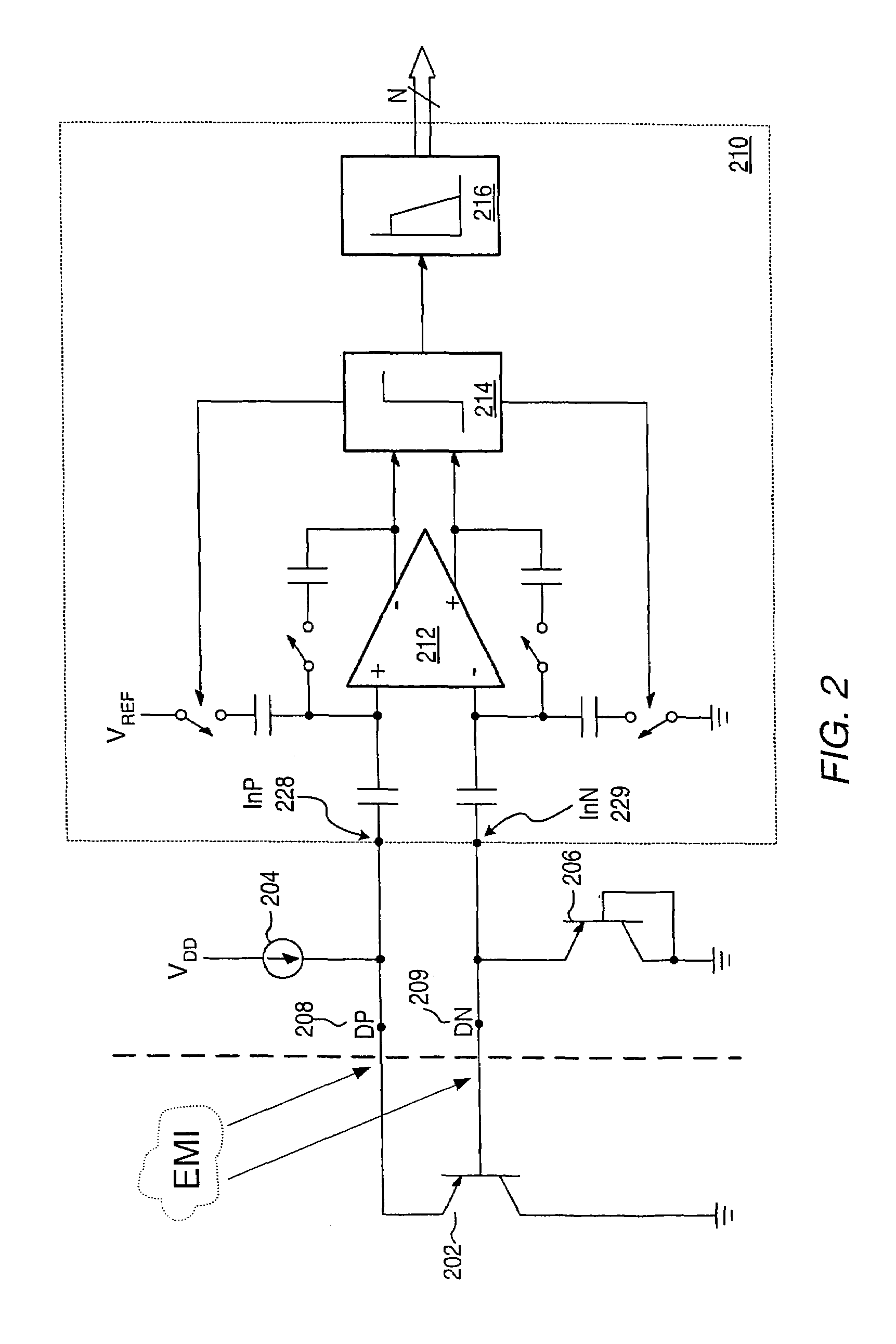

Proportional settling time adjustment for diode voltage and temperature measurements dependent on forced level current

ActiveUS7429129B2Increase conversion rateMinimizing temperature measurementThermometer detailsThermometers using material expansion/contactionAc componentsShunt capacitors

A temperature sensor circuit and system providing accurate digital temperature readings using a local or remote temperature diode. In one set of embodiments a change in diode junction voltage (ΔVBE) proportional to the temperature of the diode is captured and provided to an analog to digital converter (ADC), which may perform required signal conditioning functions on ΔVBE, and provide a digital output corresponding to the temperature of the diode. DC components of errors in the measured temperature that may result from EMI noise modulating the junction voltage (VBE) may be minimized through the use of a front-end sample-and-hold circuit coupled between the diode and the ADC, in combination with a shunt capacitor coupled across the diode junction. The sample-and-hold-circuit may sample VBE at a frequency that provides sufficient settling time for each VBE sample, and provide corresponding stable ΔVBE samples to the ADC at the ADC operating frequency. The ADC may therefore be operated at its preferred sampling frequency rate without incurring reading errors while still averaging out AC components of additional errors induced by sources other than EMI.

Owner:MICROCHIP TECH INC

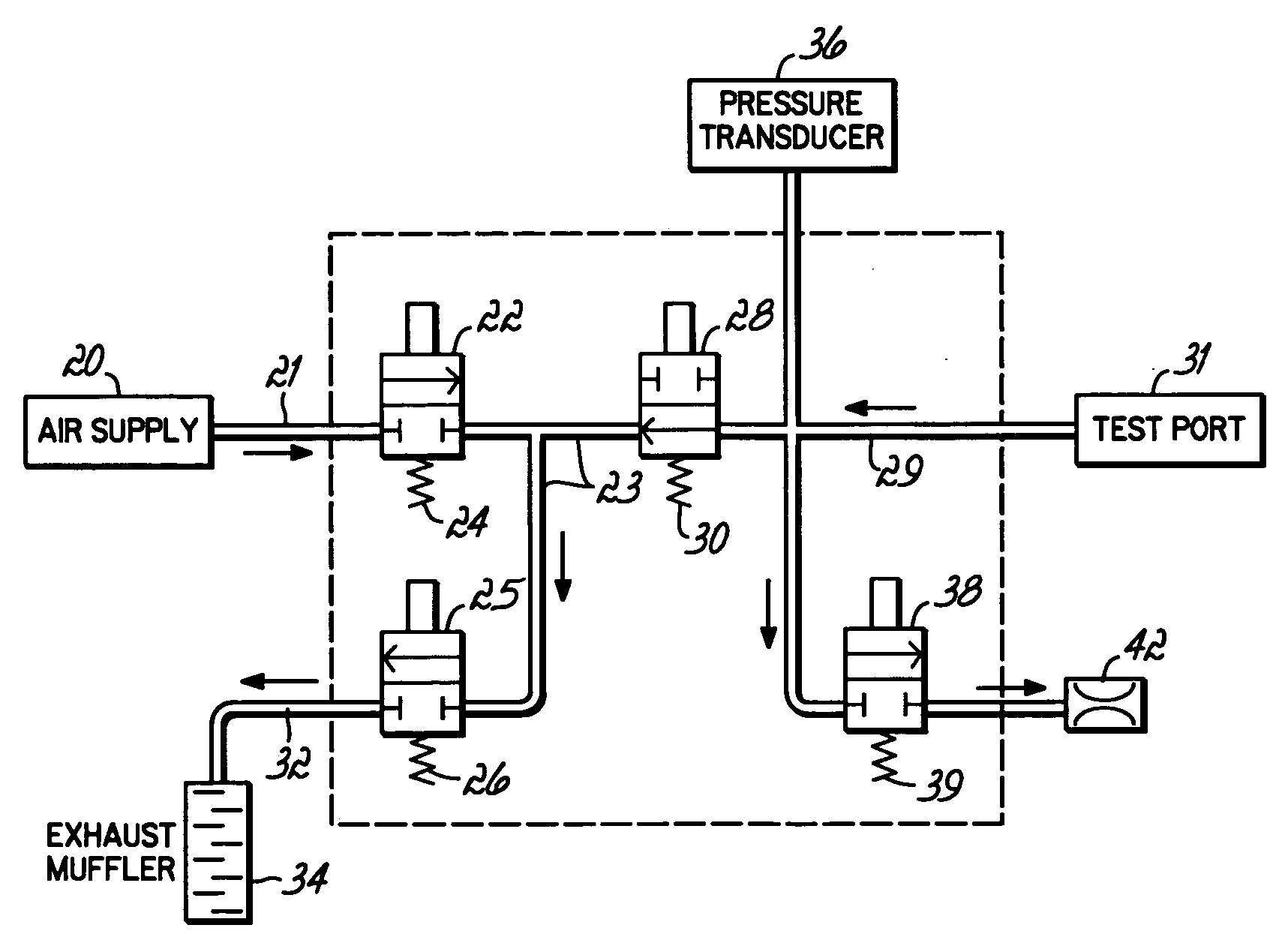

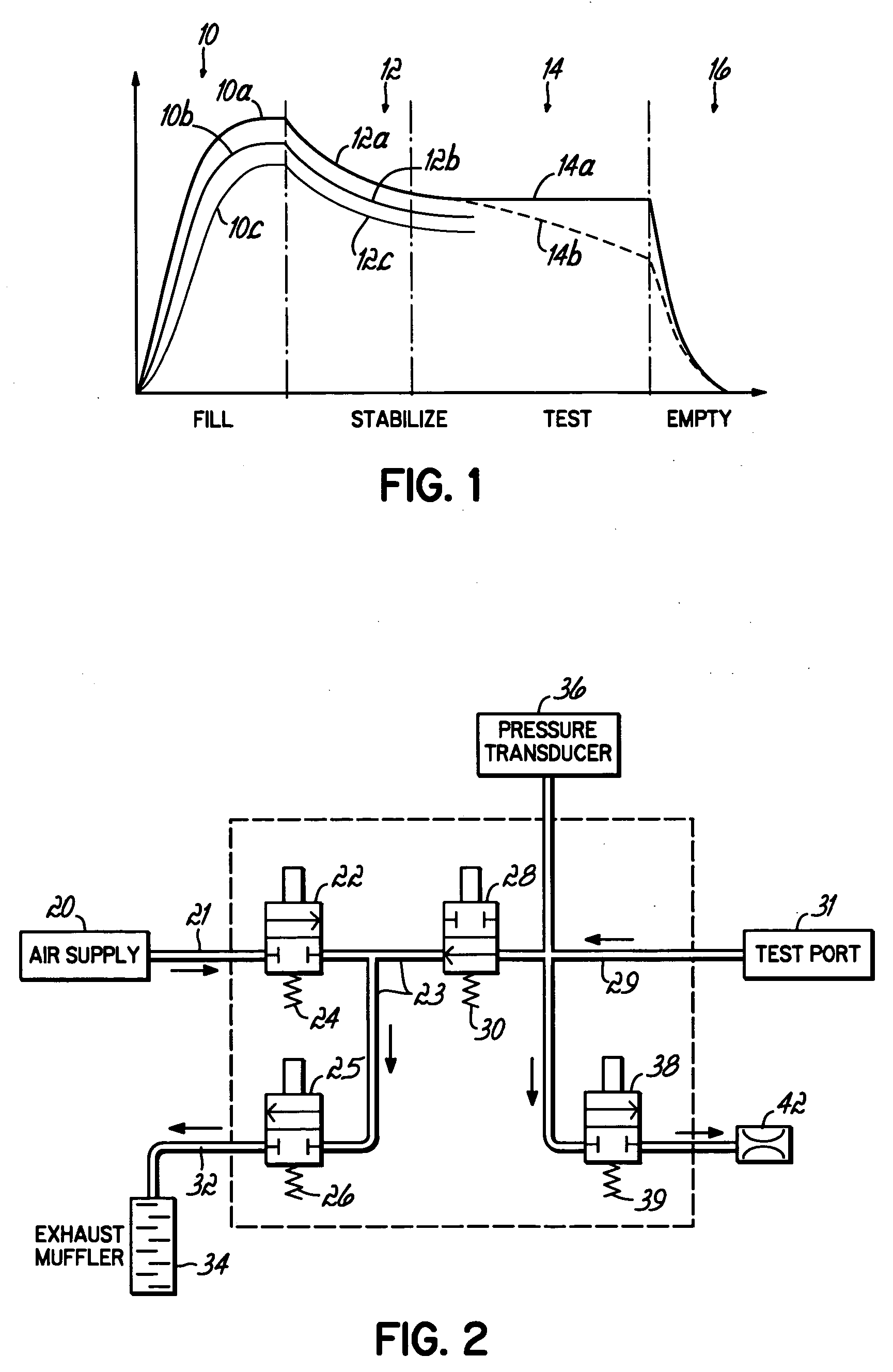

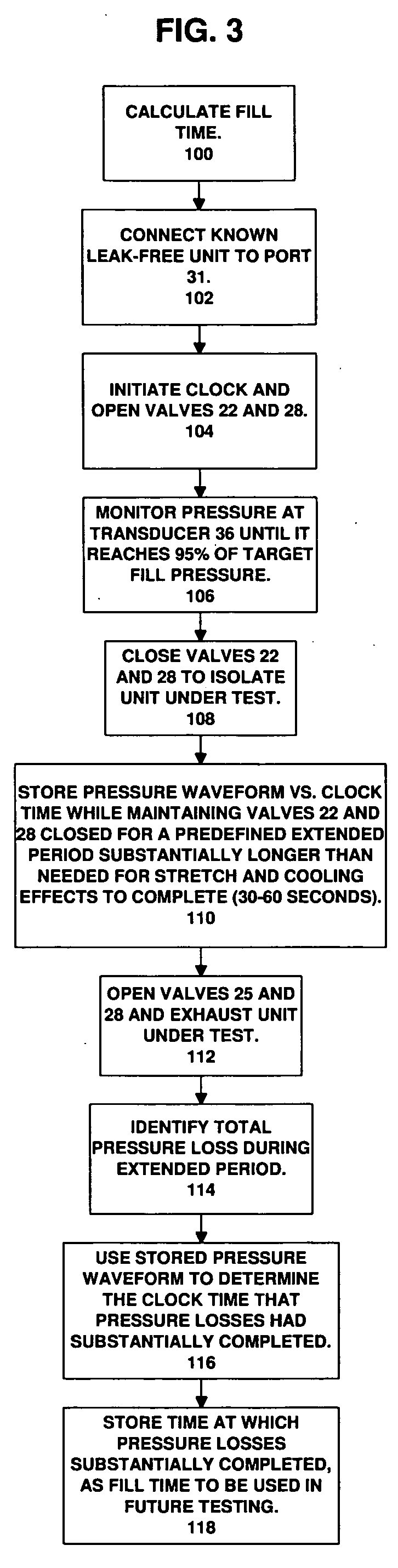

Automated timer and setpoint selection for pneumatic test equipment

ActiveUS20070169543A1Acceptable performanceDetection of fluid at leakage pointEngineeringTest procedures

A fill time and stabilize and measurement time are determined for a pneumatic testing procedure. The fill time is computed by identifying, in the filling of a sample unit, a time when a substantial portion of variations of a measured variable (due to stabilization) are completed. The stabilize and measurement time is determined by comparison of the measurement variable behavior when filling sample unit(s) that do not leak, to the measurement variable behaviors when filling a sample unit that is in communication with an orifice simulating a leak. A measurement performance factor may be computed from this data at each of several possible times after a unit is filled. A gauge repeatability factor may be computed based on variance of nonleaking units at each possible time, compared to the variable change made on a sample unit when coupled to a leak-simulating orifice. Either factor may be used to select a stabilize and measurement time.

Owner:CINCINNATI TEST SYST

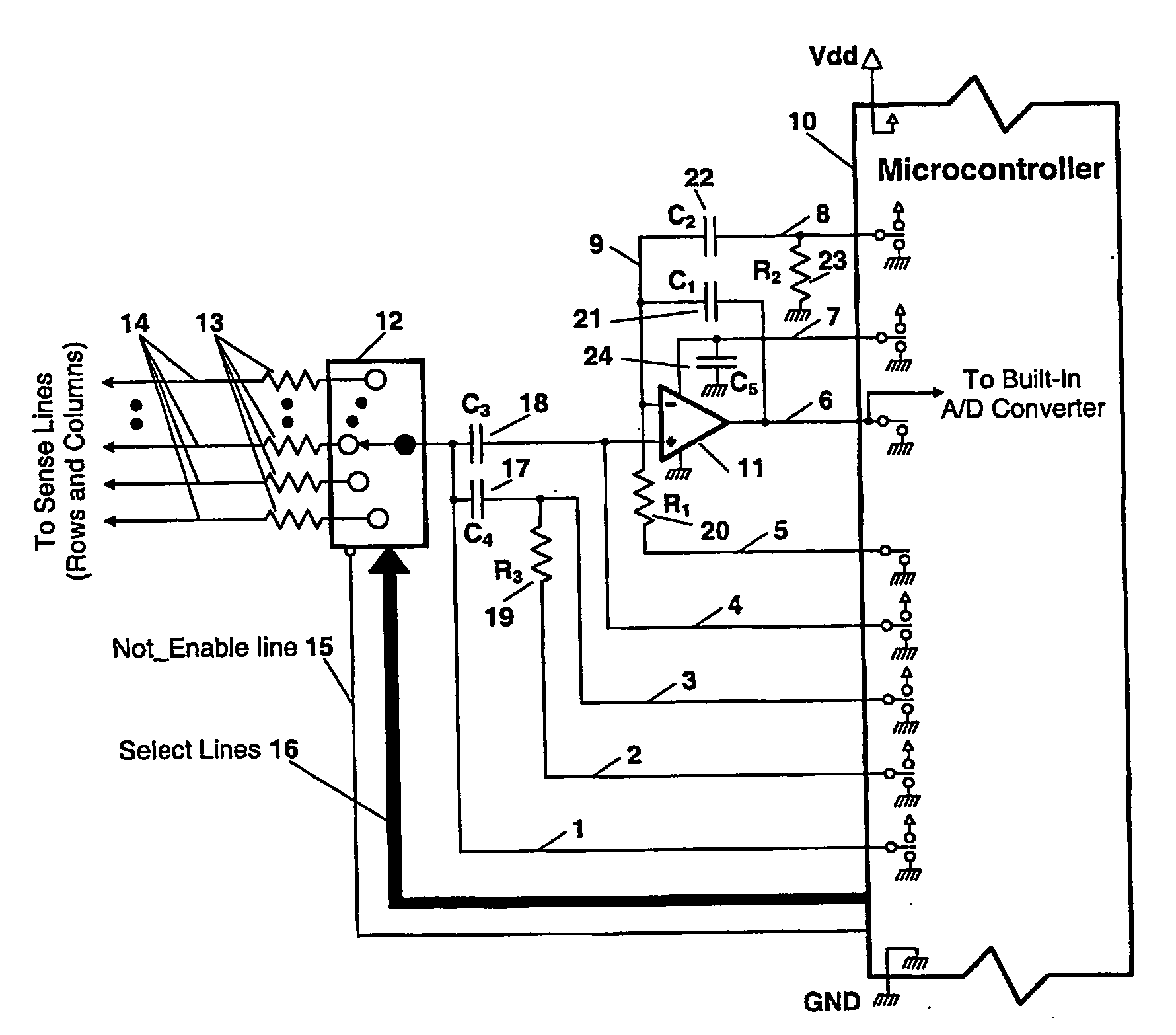

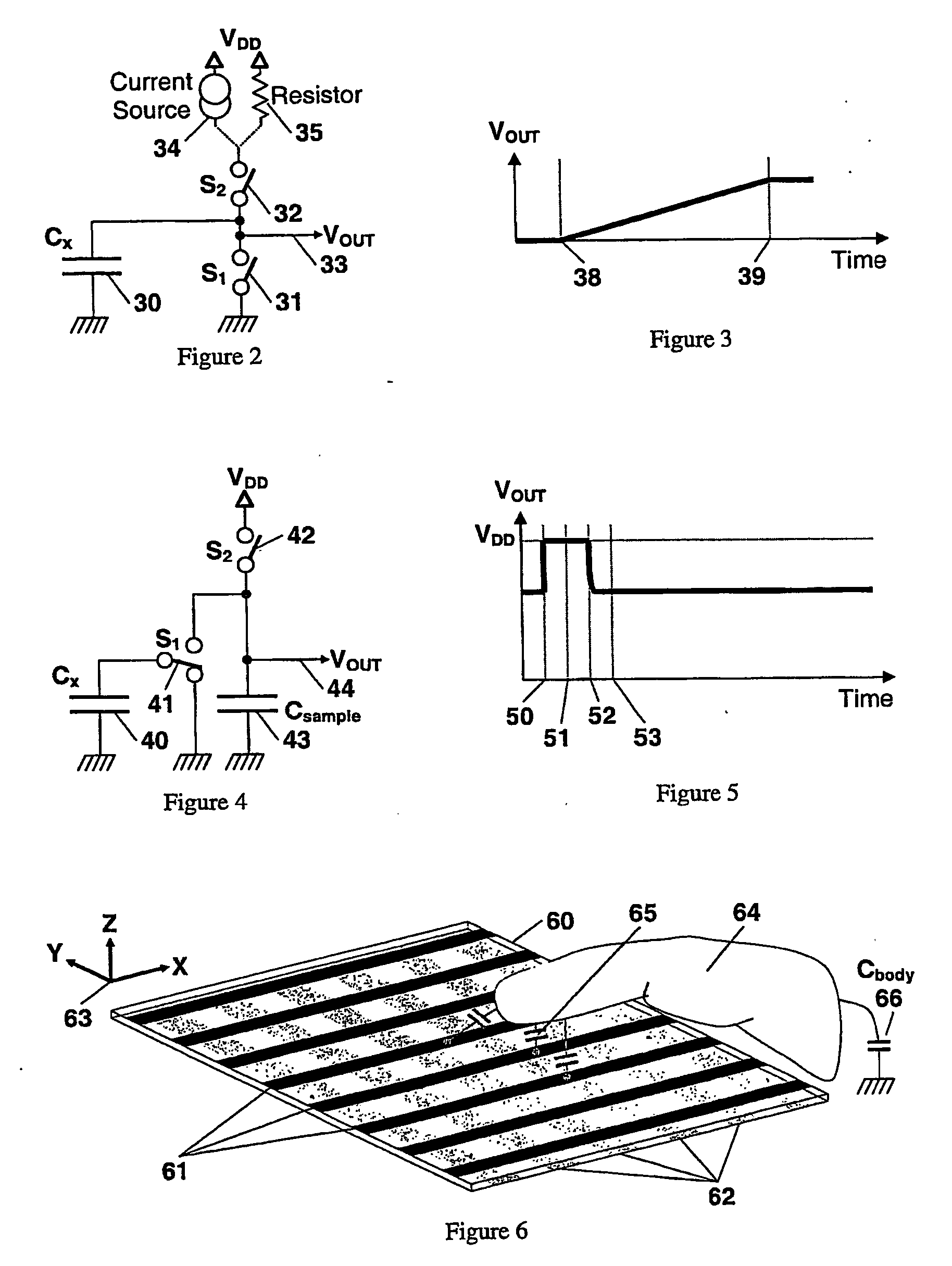

Data acquistion from capacitive touch pad

InactiveUS20060017701A1Reduce sensitivityFast settling timeCathode-ray tube indicatorsInput/output processes for data processingMicrocontrollerGeneral purpose

A Circuit (in FIG. 1) and an Algorithm for Data Acquisition from Capacitive Touch Pad Sensor employs charge transfer to sense capacitance. The circuit has high degree of noise rejection from both system and externally generated noises; it is resistant to the effects of ESD; utilizes a general purpose “off the shelf” components and programmable microcontroller (element providing flexibility for changes and adjustments without incurring the high costs of a custom IC design. A settling time and low sensitivity to the noise.

Owner:SEMTECH CORP

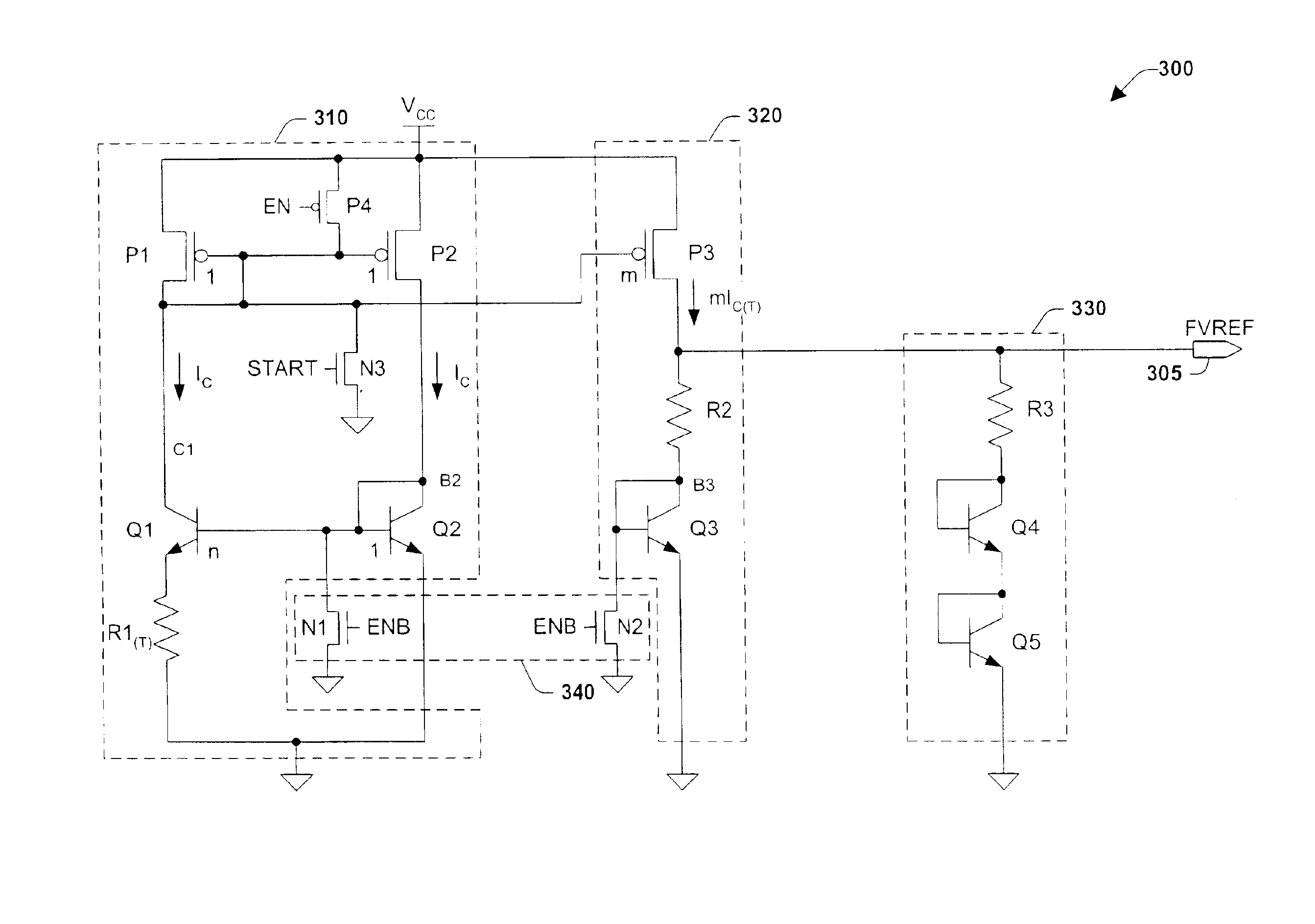

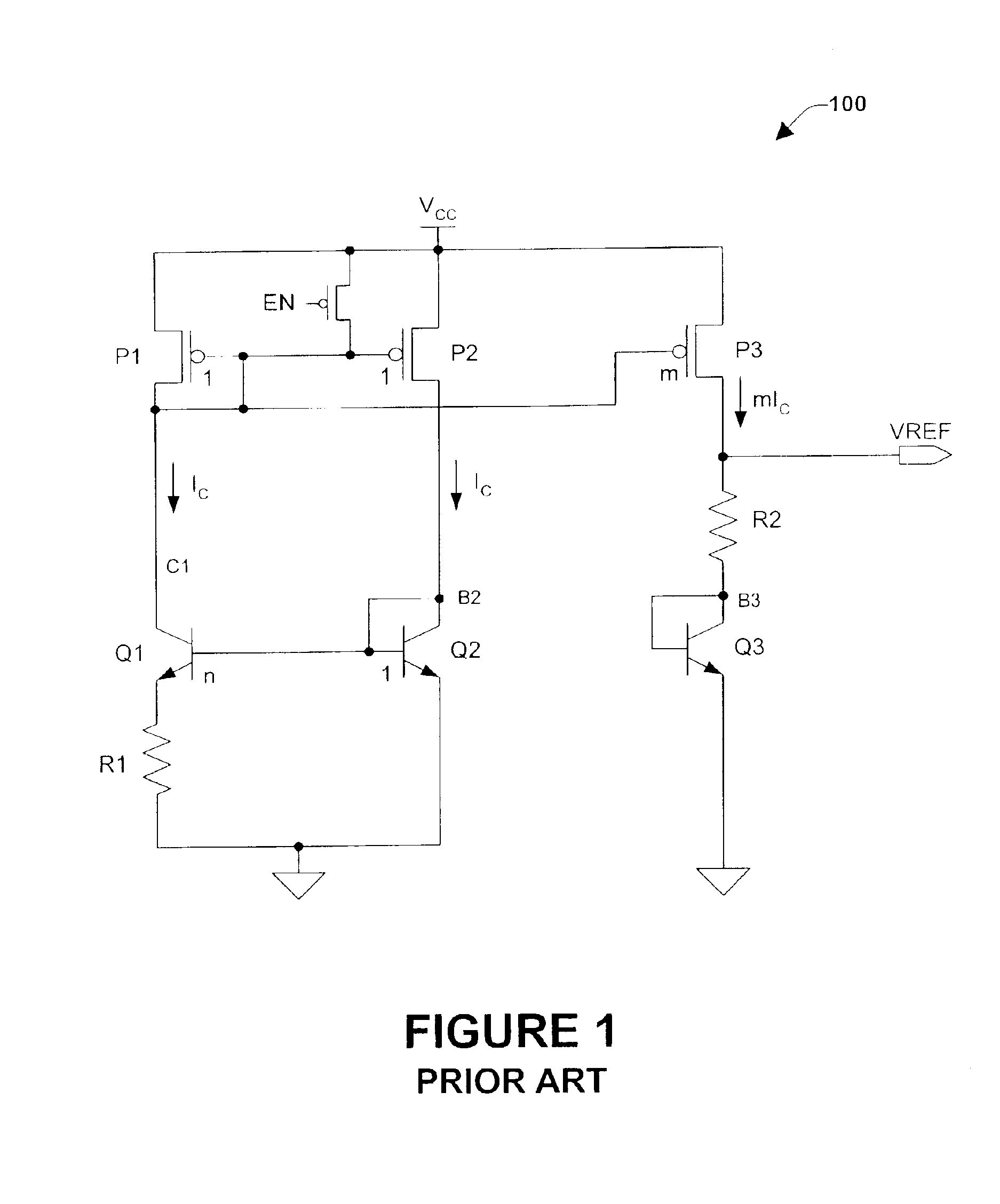

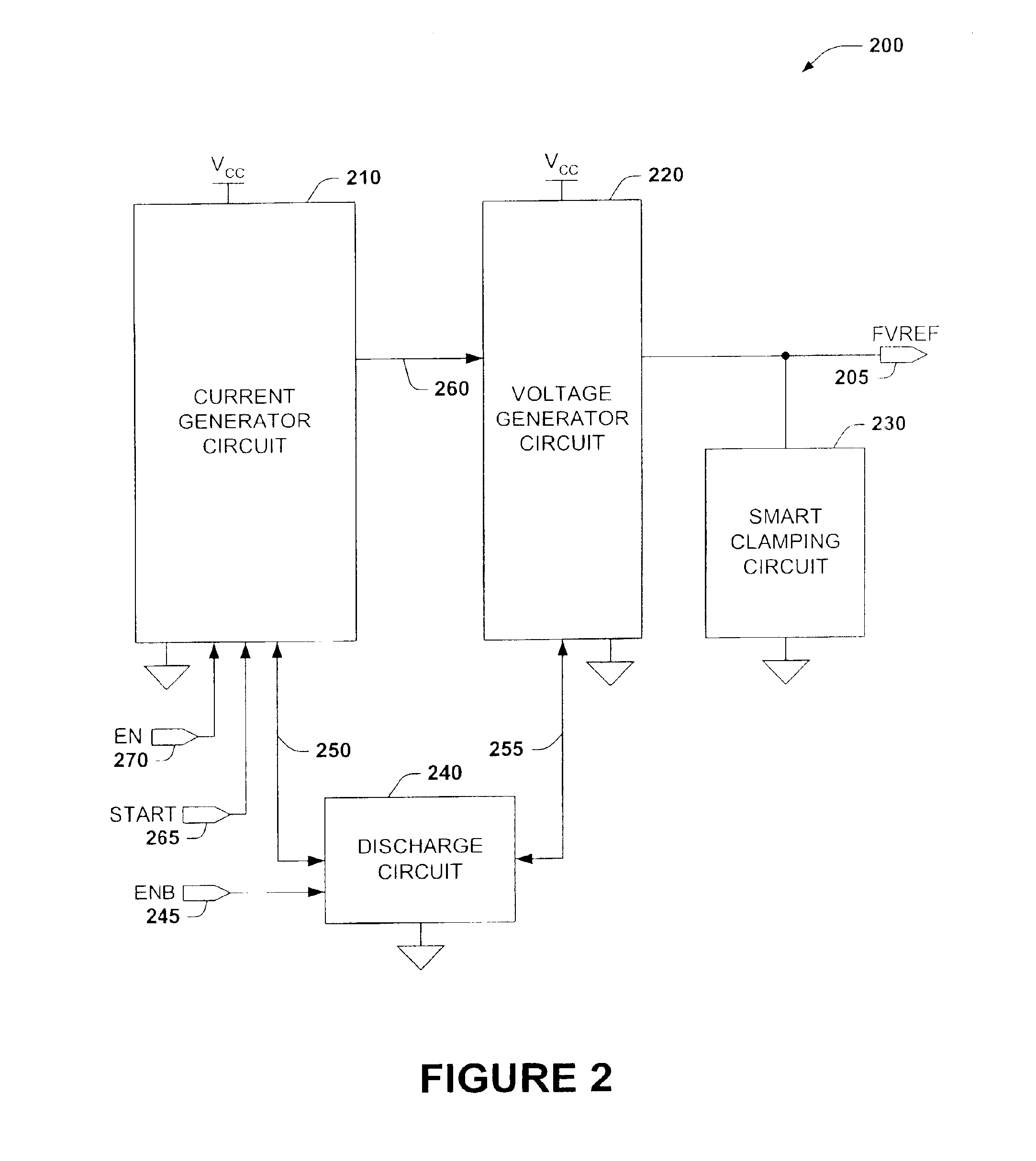

Fast bandgap reference circuit for use in a low power supply A/D booster

InactiveUS6894473B1Lower FVREFGuaranteed normal operationElectric variable regulationElectrical resistance and conductanceLoad resistance

A bandgap reference circuit includes a current generation circuit connected to a voltage generation circuit connected to a smart clamping circuit, and a discharge circuit connected to the current generation circuit and the voltage generation circuit. The discharge circuit initially discharges a potential in the current and voltage generation circuits to improve repeatability. A start circuit within the current generation circuit then initializes the reference output at about the supply voltage to improve the speed and settling time of the output signal. The current generation circuit sources a current to the voltage generation circuit that translates the current having a positive function of temperature +TC into a reference voltage. The smart clamping circuit further generates a clamping voltage having a negative function of temperature −TC and a load resistance. The clamping voltage and the load resistance are applied across the reference voltage quickly reducing the reference voltage particularly at high temperatures and during start-up to a final level, thereby producing a fast and stable reference voltage.

Owner:INFINEON TECH LLC

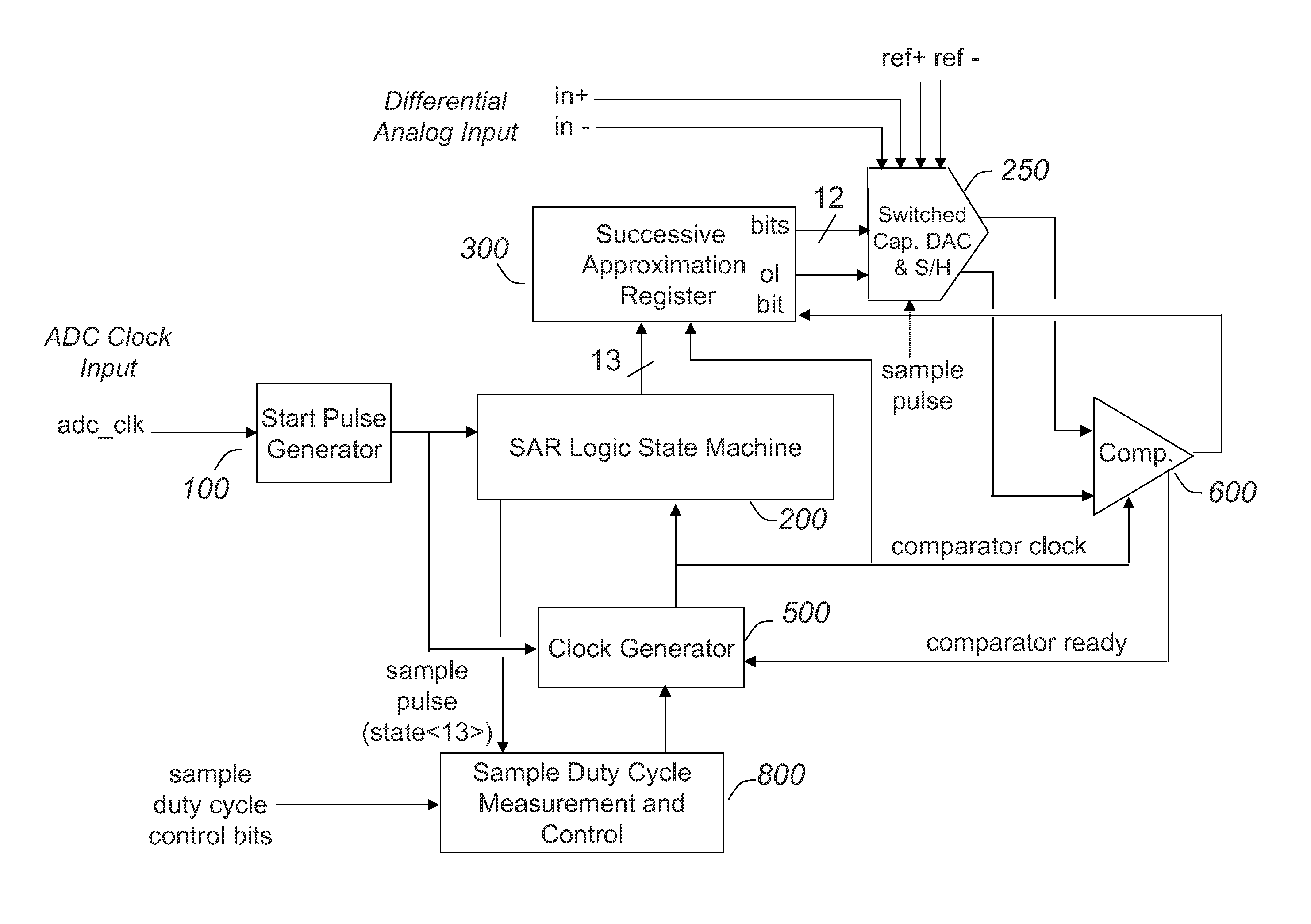

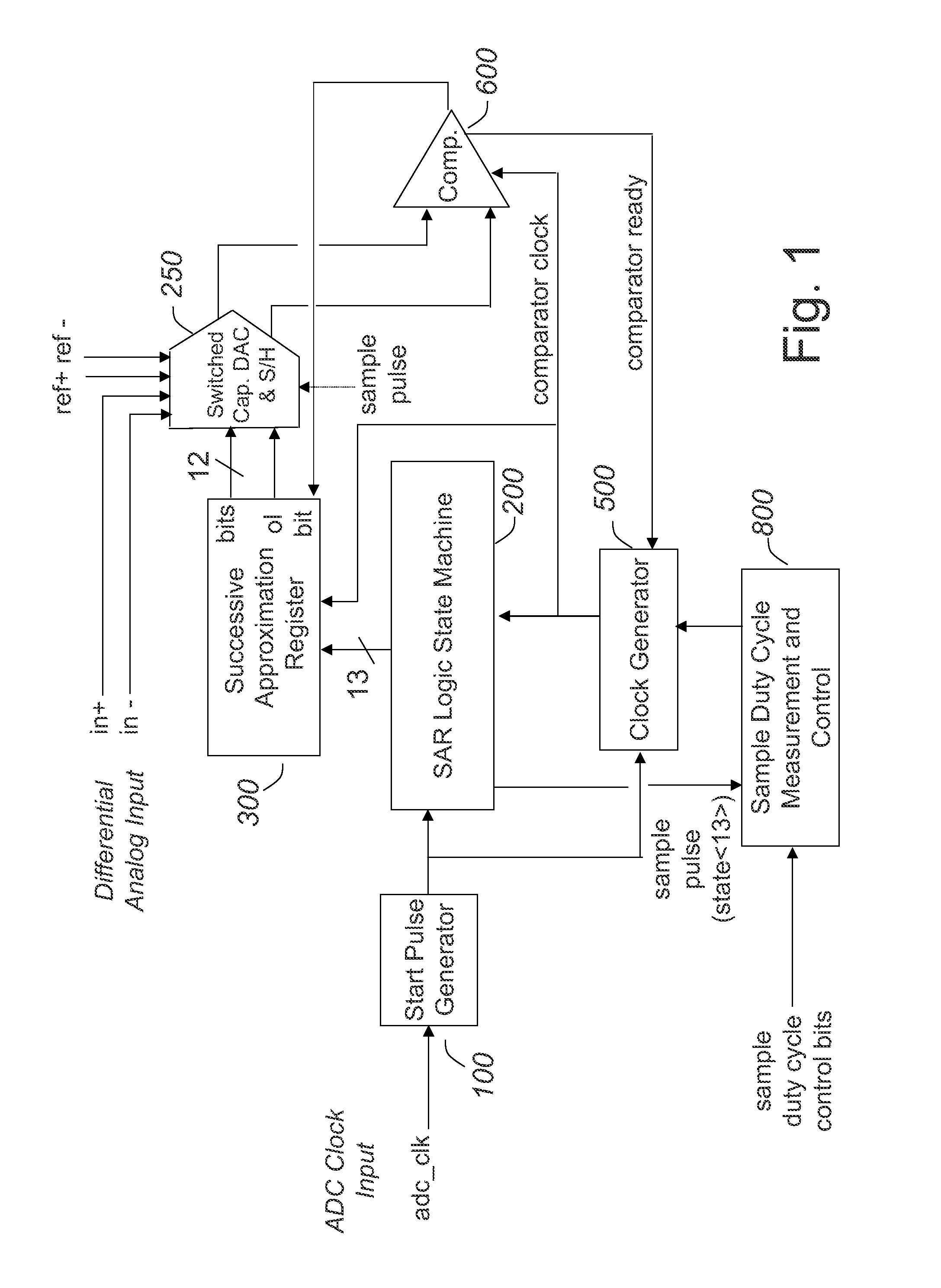

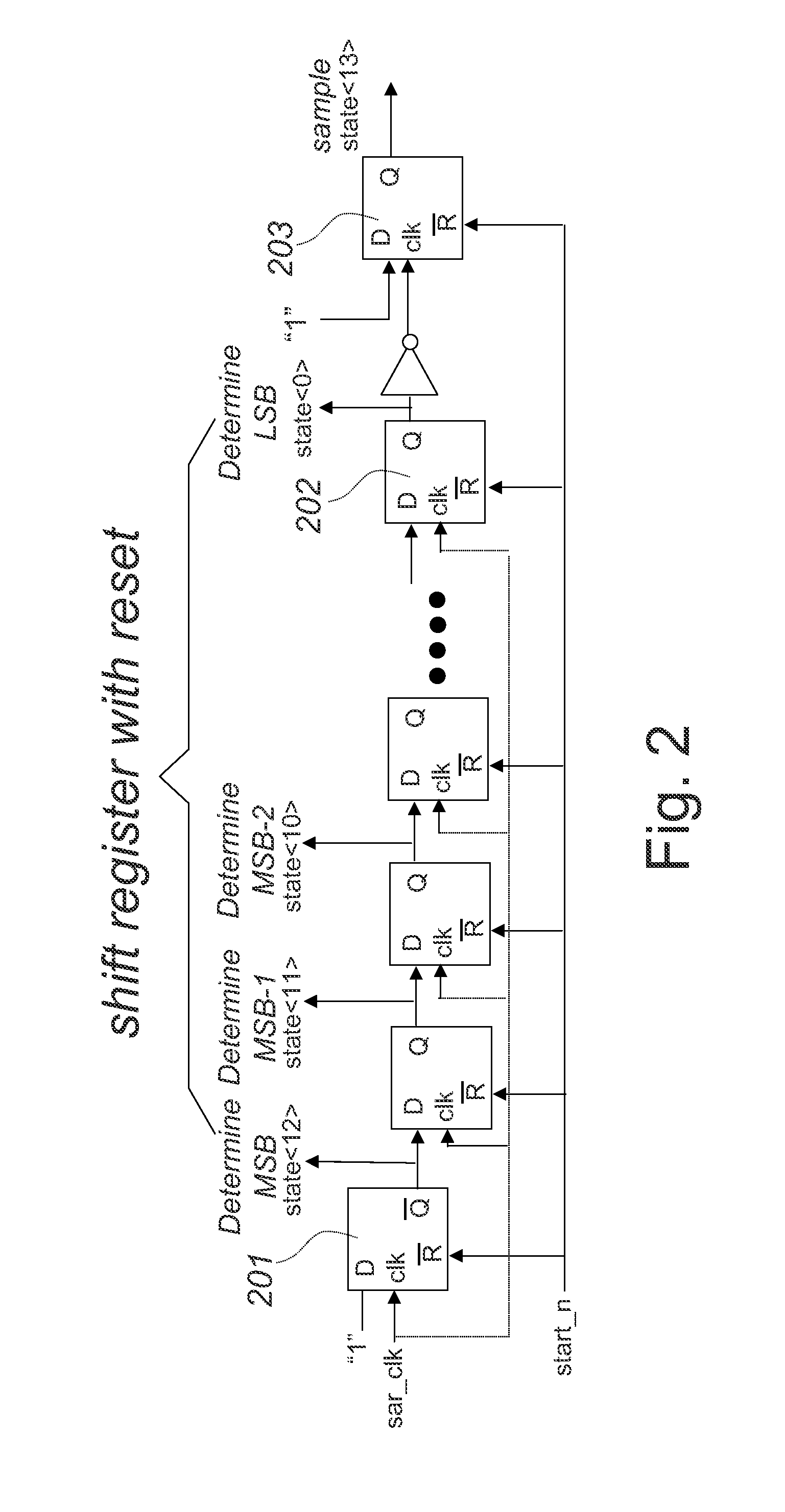

System and method for adaptive timing control of successive approximation analog-to-digital conversion

ActiveUS8344925B1Enough timeEnable selectivityElectric signal transmission systemsAnalogue-digital convertersPropagation timeAnalog signal

A system and method are provided for adaptively controlling timing in SAR ADC of a sampled analog signal within a conversion period. A state machine maintains a set of SAR states including a sampling state and a plurality of bit conversion states. A reference generator generates a quantization level reference for each of the bit conversion states within a parametric settling time thereof. A comparator compares the sampled analog signal with the quantization level reference over a parametric propagation time for determining a hit value for each hit conversion state. A clock generator adaptively defines signals for clocking the state machine and comparator for each SAR state, thereby adaptively delaying bit determination in each bit conversion state by an integration period not less than the settling time, while adaptively delaying quantization level reference generation for a next bit conversion state by a regeneration period not less than the propagation time.

Owner:CADENCE DESIGN SYST INC

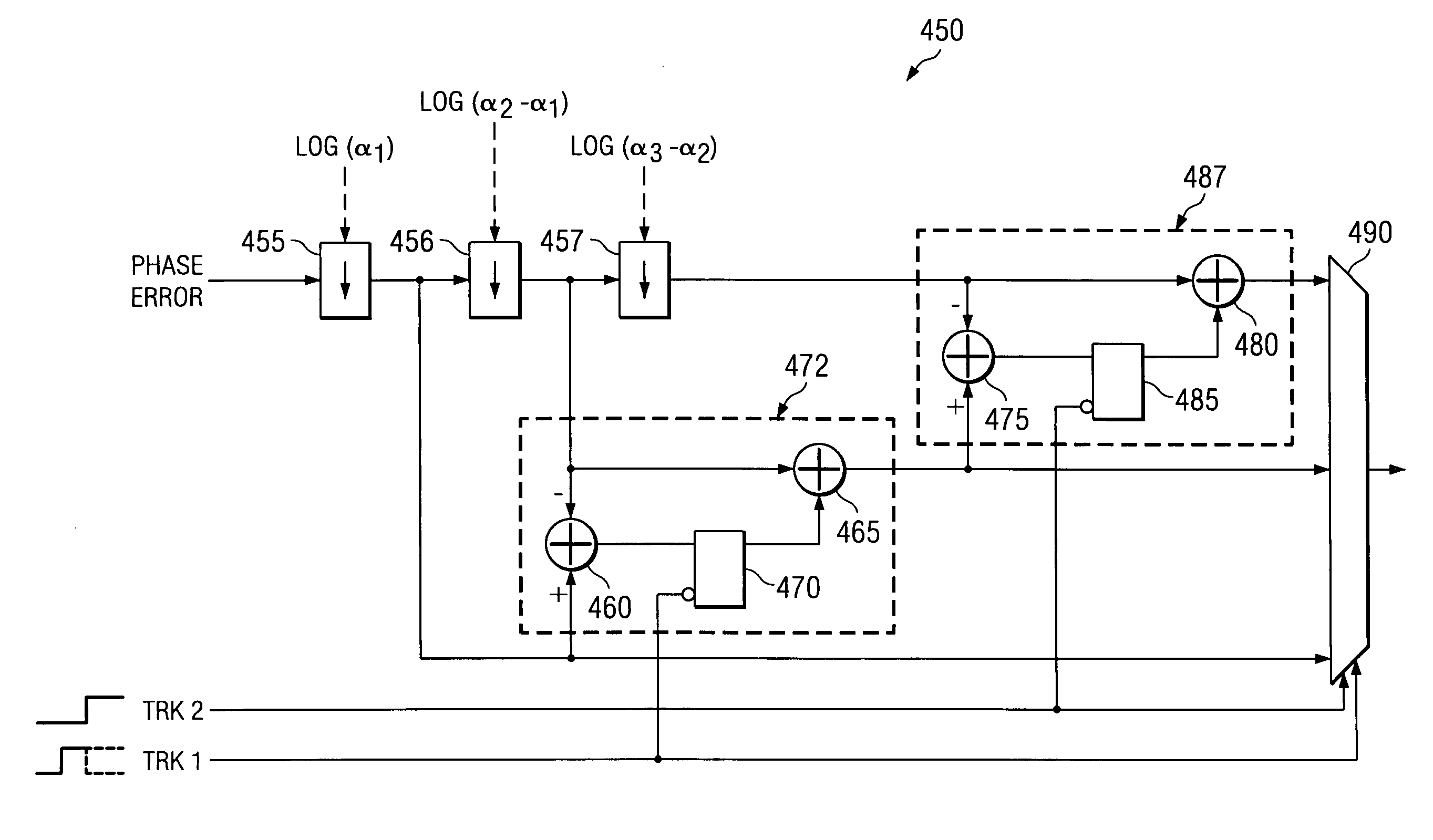

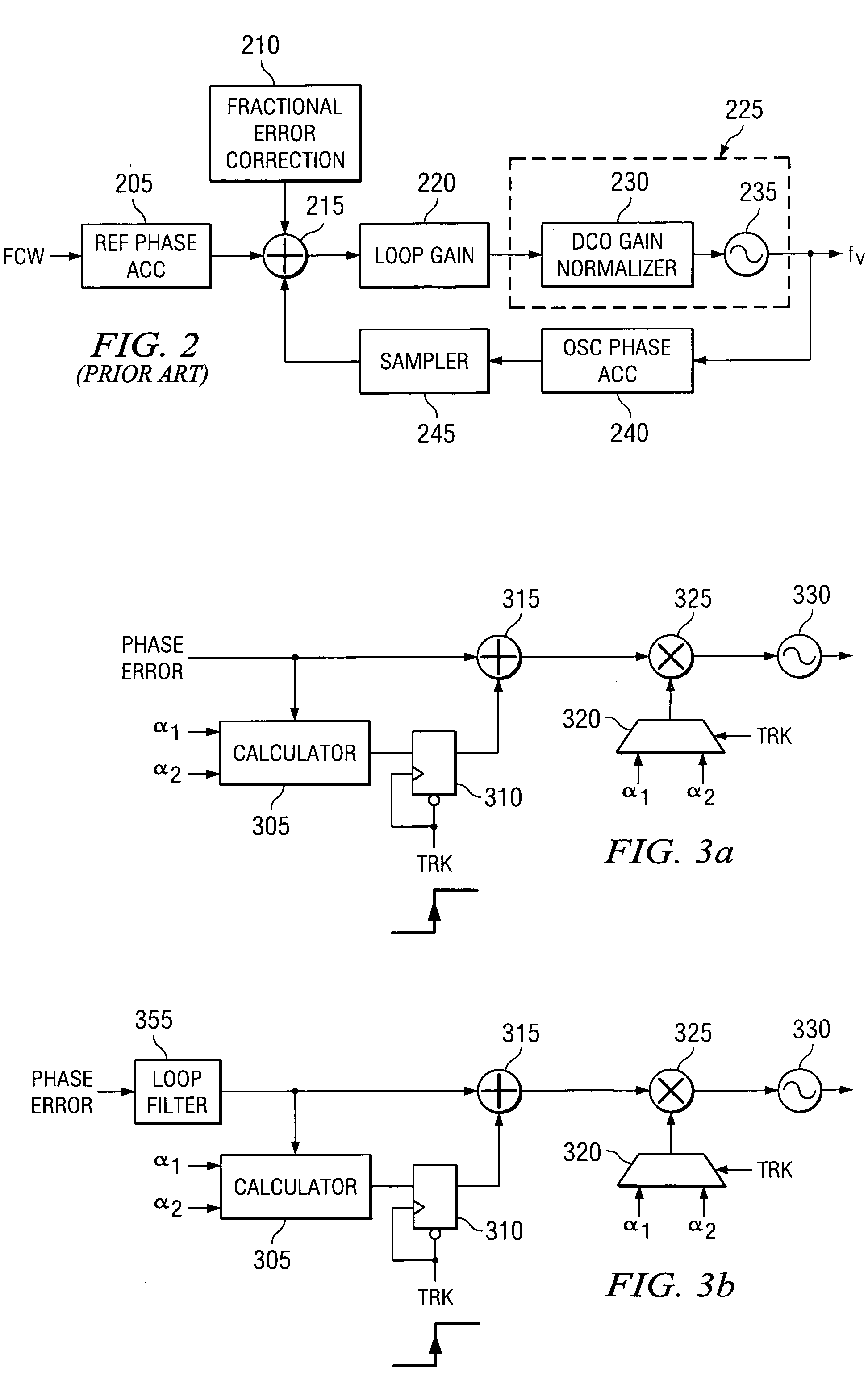

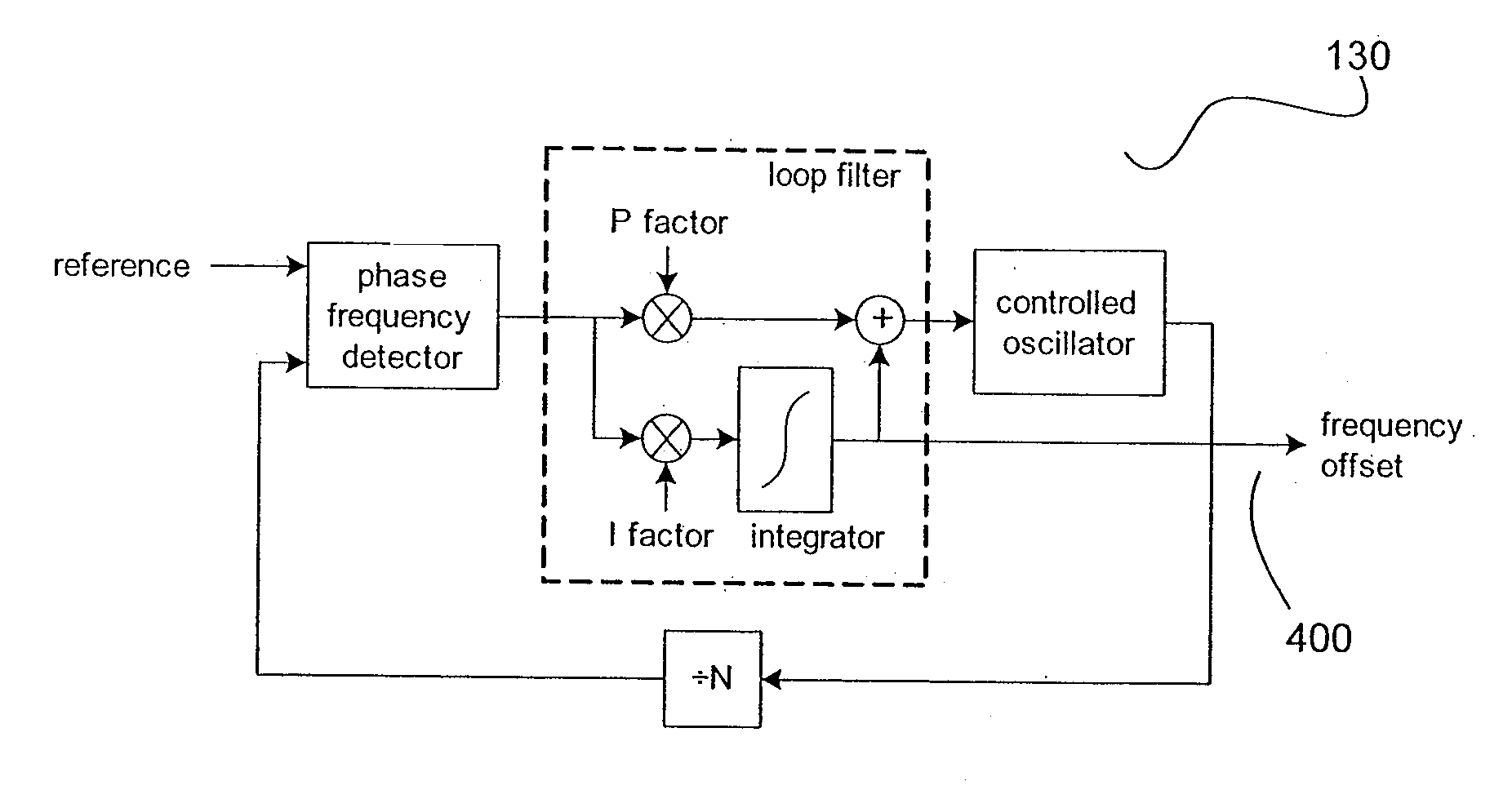

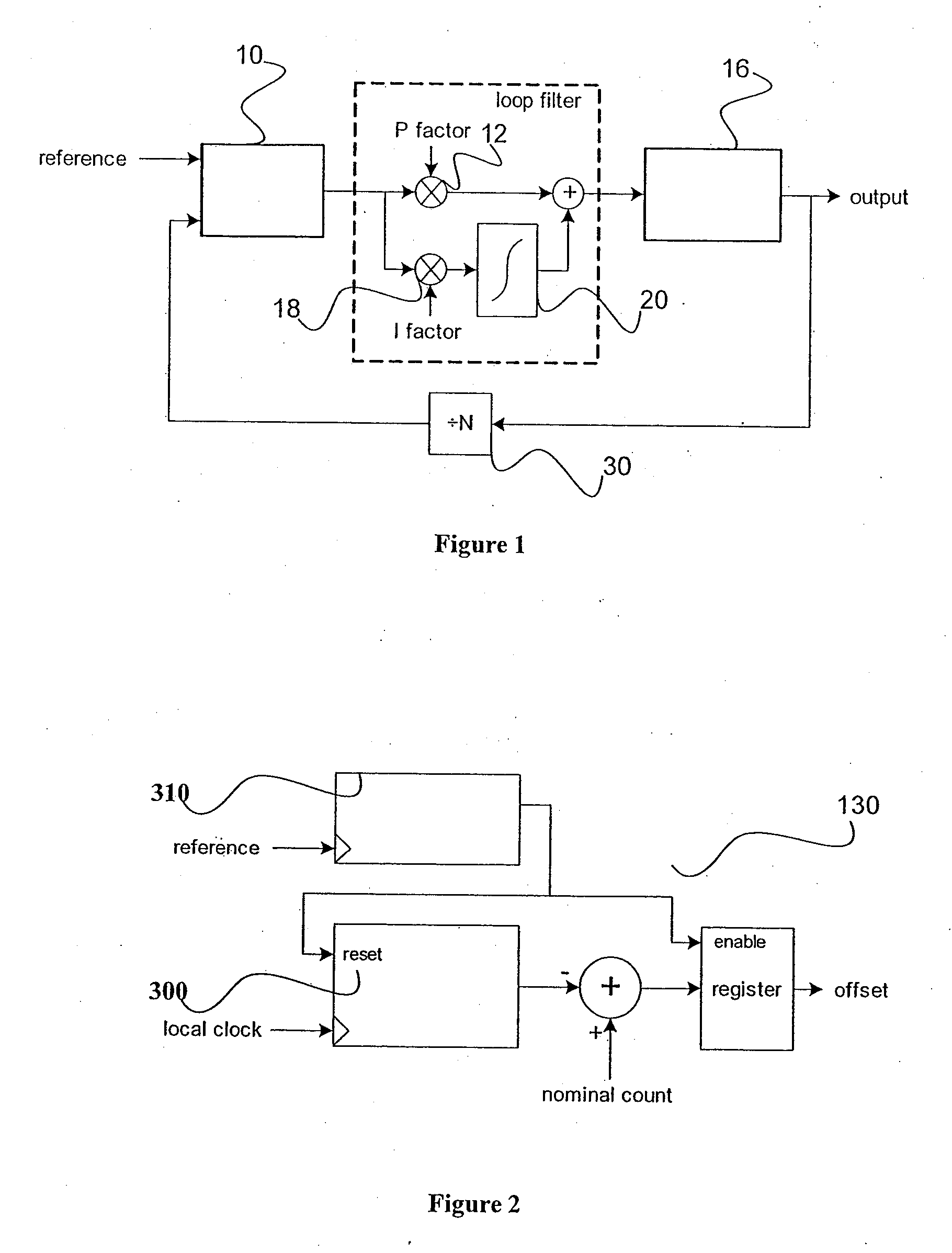

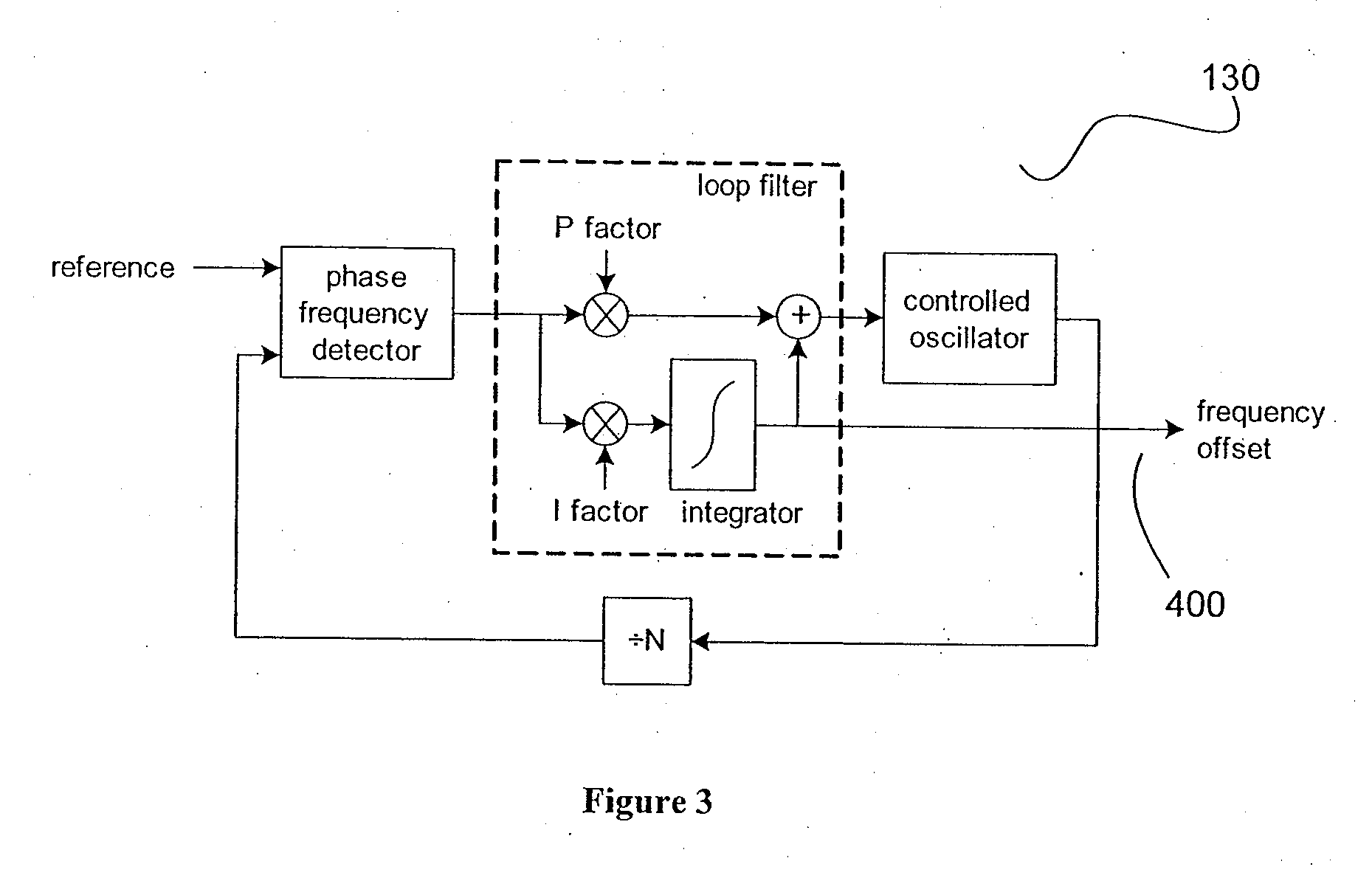

Type-II all-digital phase-locked loop (PLL)

InactiveUS7145399B2Improving signal acquisition performanceFast signal acquisitionAmplifier modifications to reduce non-linear distortionPulse automatic controlLoop filterLoop bandwidth

System and method for providing type-II (and higher order) phase-locked loops (PLLs) with a fast signal acquisition mode. A preferred embodiment comprises a loop filter with a proportional loop gain path (proportional loop gain circuit 1115) and an integral loop gain block (integral loop gain block 1120). The proportional loop gain path is used during signal acquisition to provide large loop bandwidth, hence fast signal acquisition of a desired signal. Then, during the PLL's signal tracking phase, the integral loop gain block is enabled and its output is combined with output from the proportional loop gain path to provide higher order filtering of the desired signal. An offset that may be present due to the use of the proportional loop gain path can be measured and subtracted to help improve signal tracking settling times.

Owner:TEXAS INSTR INC

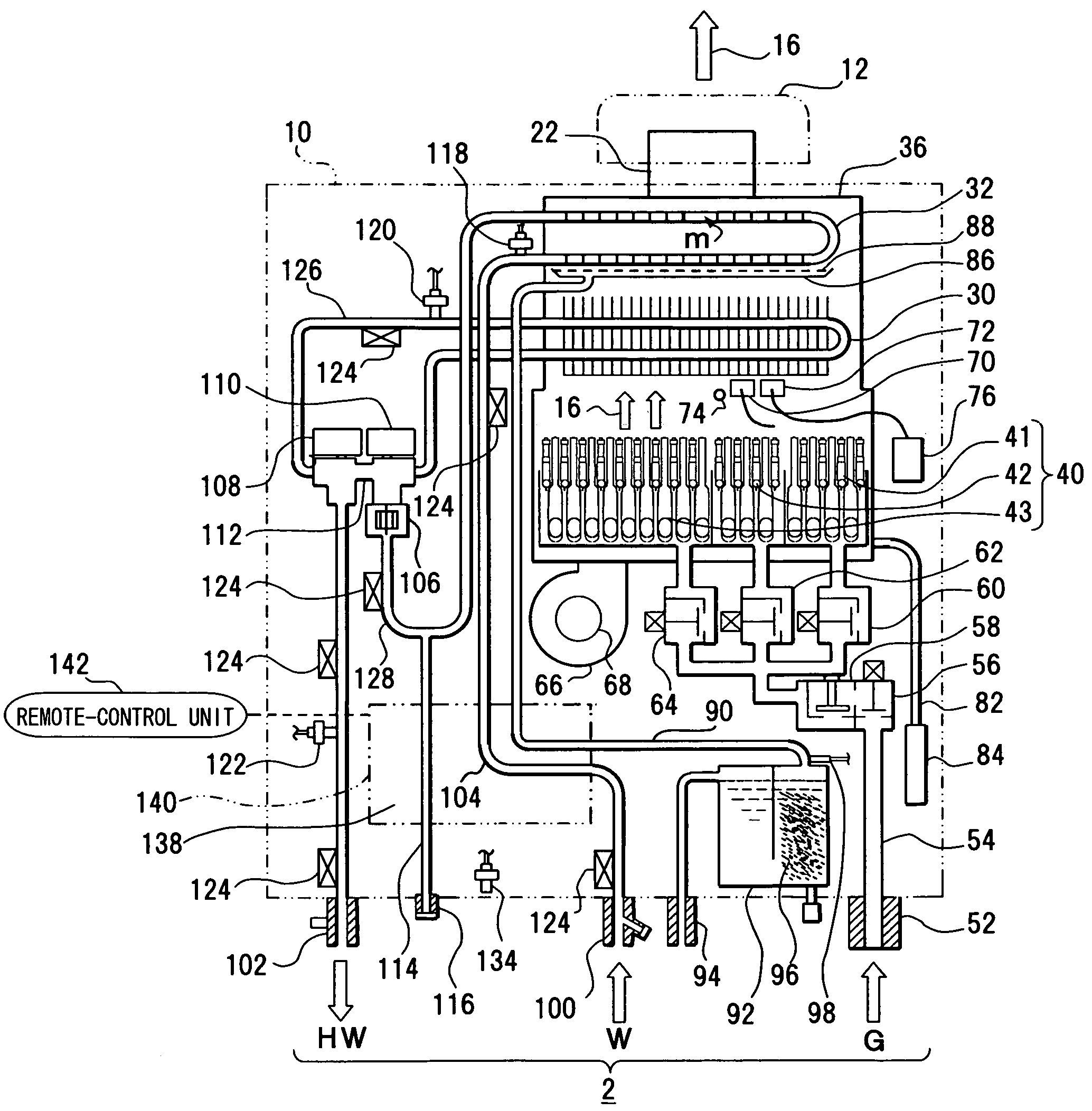

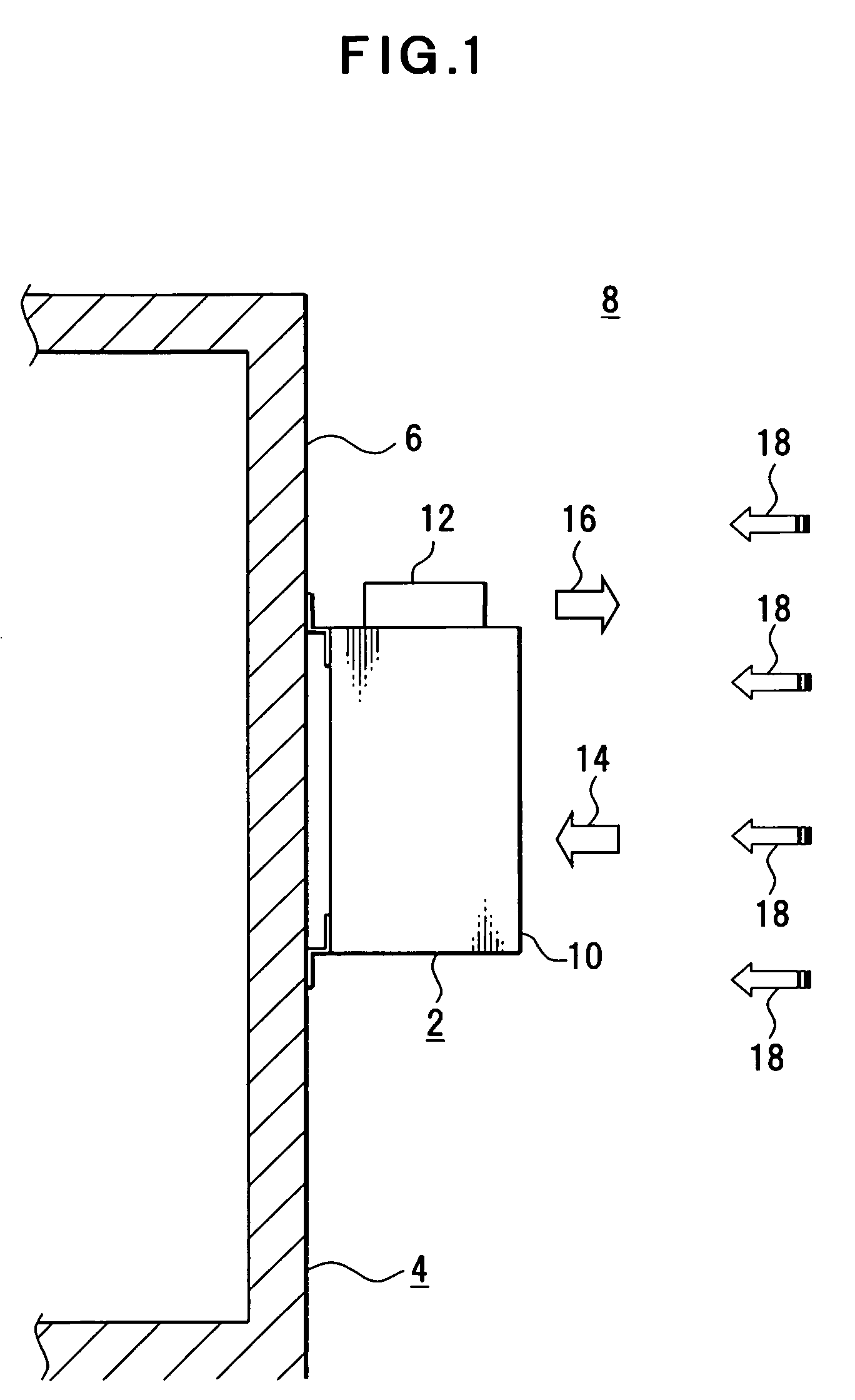

Hot-water supply apparatus, anti-freezing method thereof, and anti-freezing program thereof

ActiveUS7322532B2Function increaseAir-treating devicesVehicle heating/cooling devicesCombustionAnti freezing

A hot-water supply apparatus is an apparatus which has a primary heat exchanger absorbing sensible heat of combustion exhaust and a secondary heat exchanger absorbing latent heat of the combustion exhaust, and improves a freezing prevention function of the hot-water supply apparatus at a cold period. Further, this apparatus has a temperature detection means (temperature sensors) which detects a freezing prevention temperature, a combustion means (a burner group) which supplies combustion exhaust generated by combustion to the primary and secondary heat exchangers, an air supply means which supplies air to the combustion means, and a control means (a control unit) which makes the combustion means burn and drives the air supply means based on a detected temperature of the temperature detection means. When the temperature detection means detects the freezing prevention temperature, the combustion means is burned for a settled time to heat the primary heat exchanger, and the air supply means is driven to stream air from a side of the primary heat exchanger to the secondary heat exchanger for a given time after a combustion stop of the combustion means. By this, a side of the secondary heat exchanger is heated by remaining heat of the side of the primary heat exchanger.

Owner:PURPOSE CO LTD

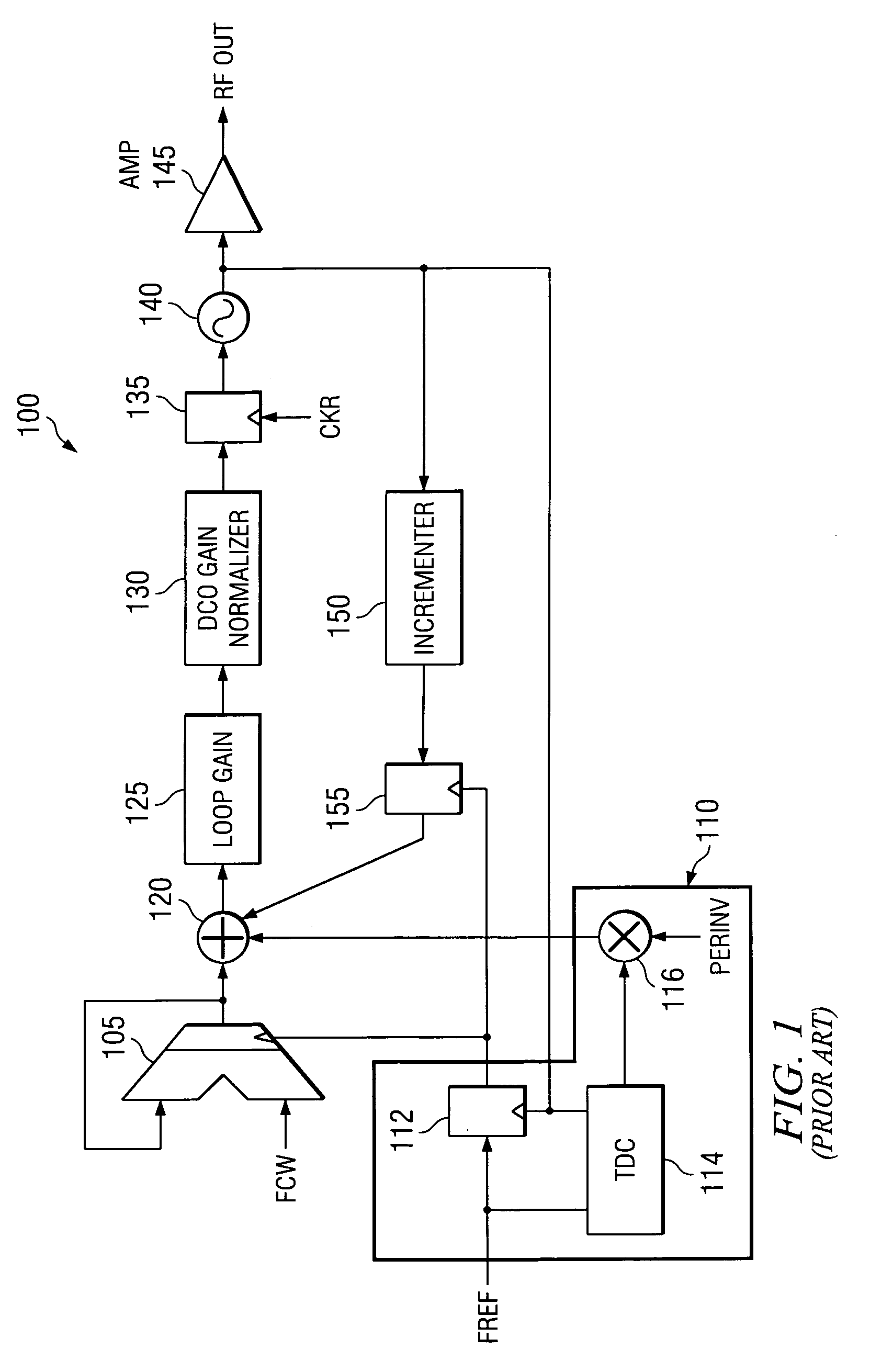

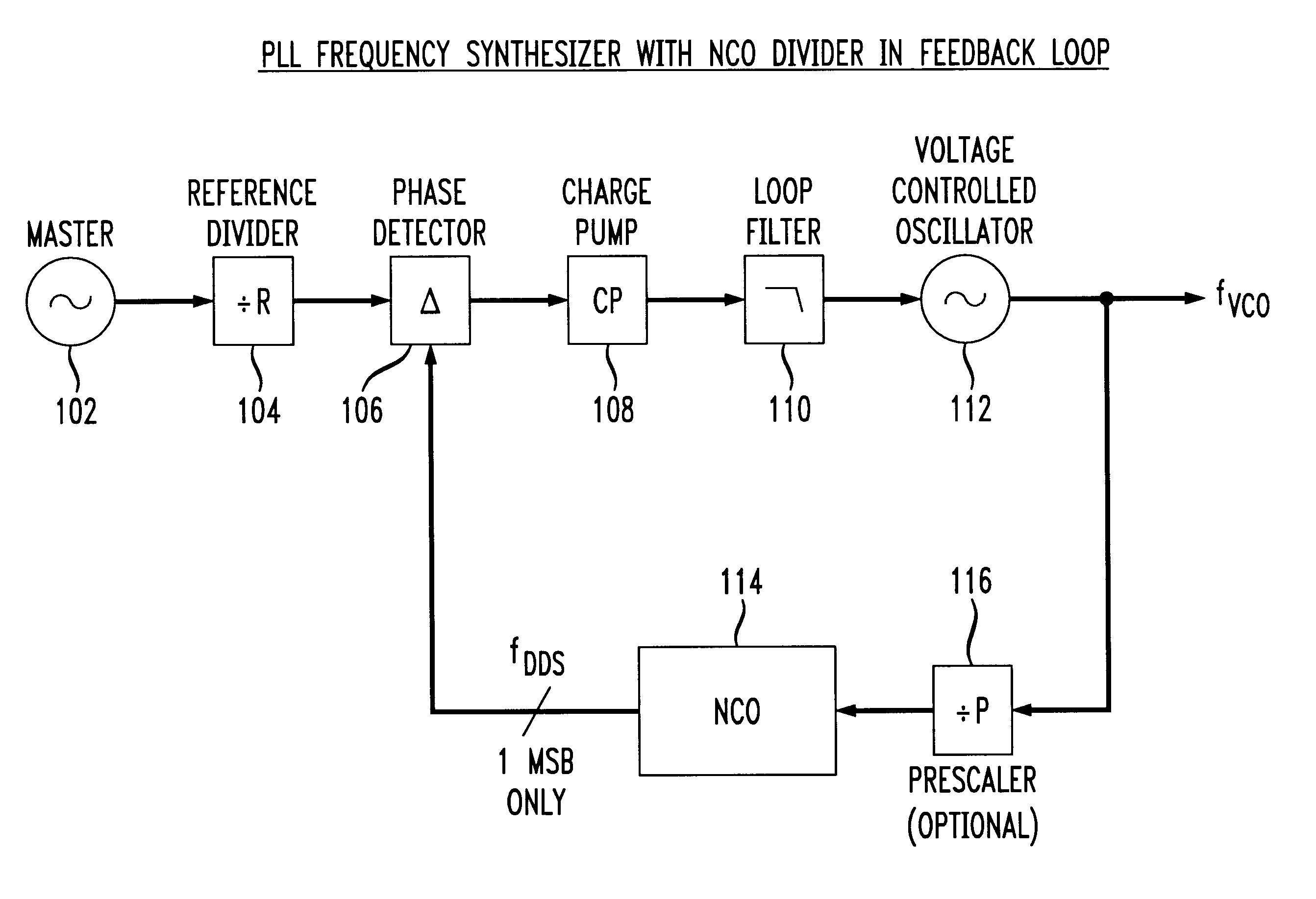

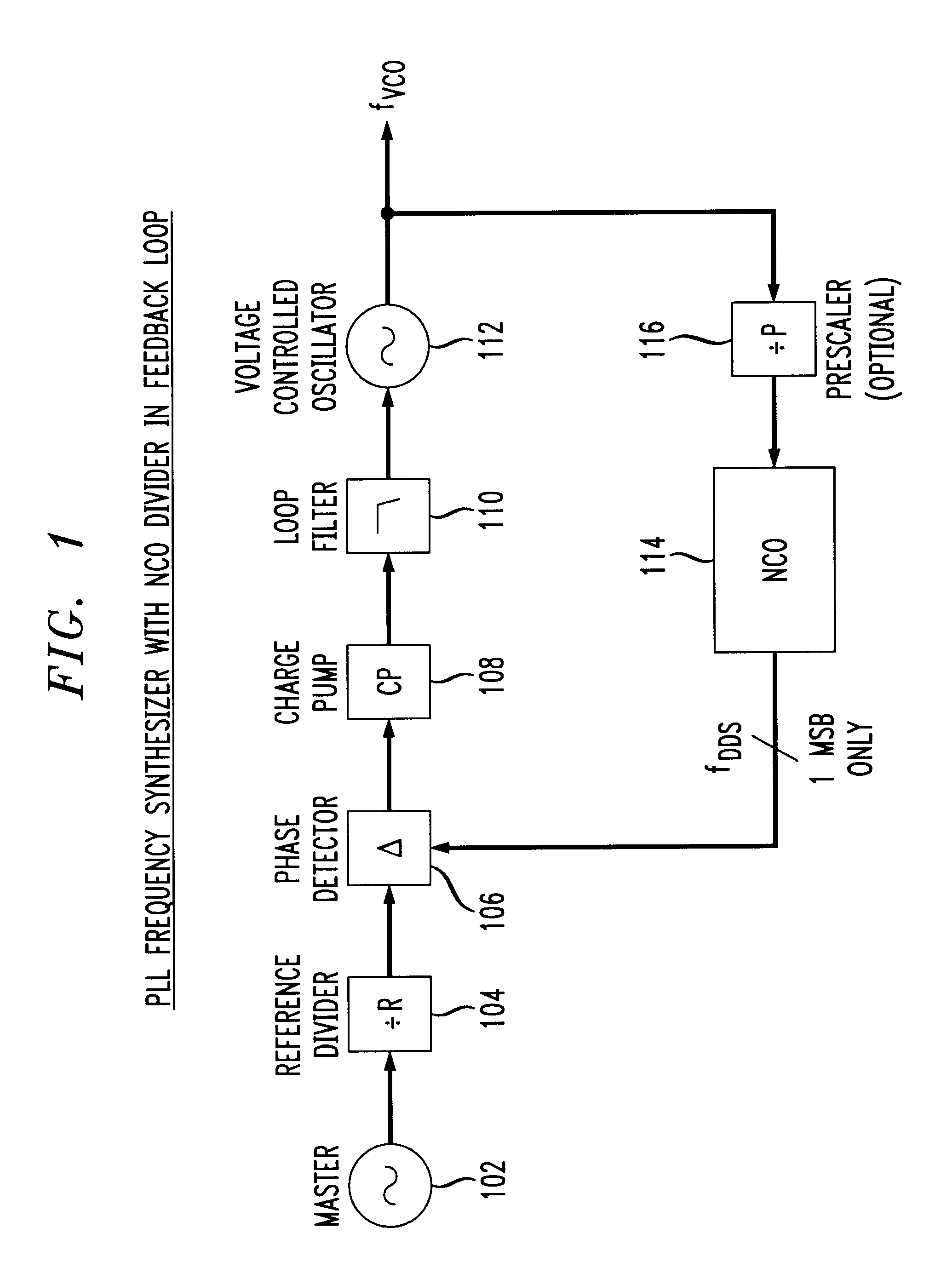

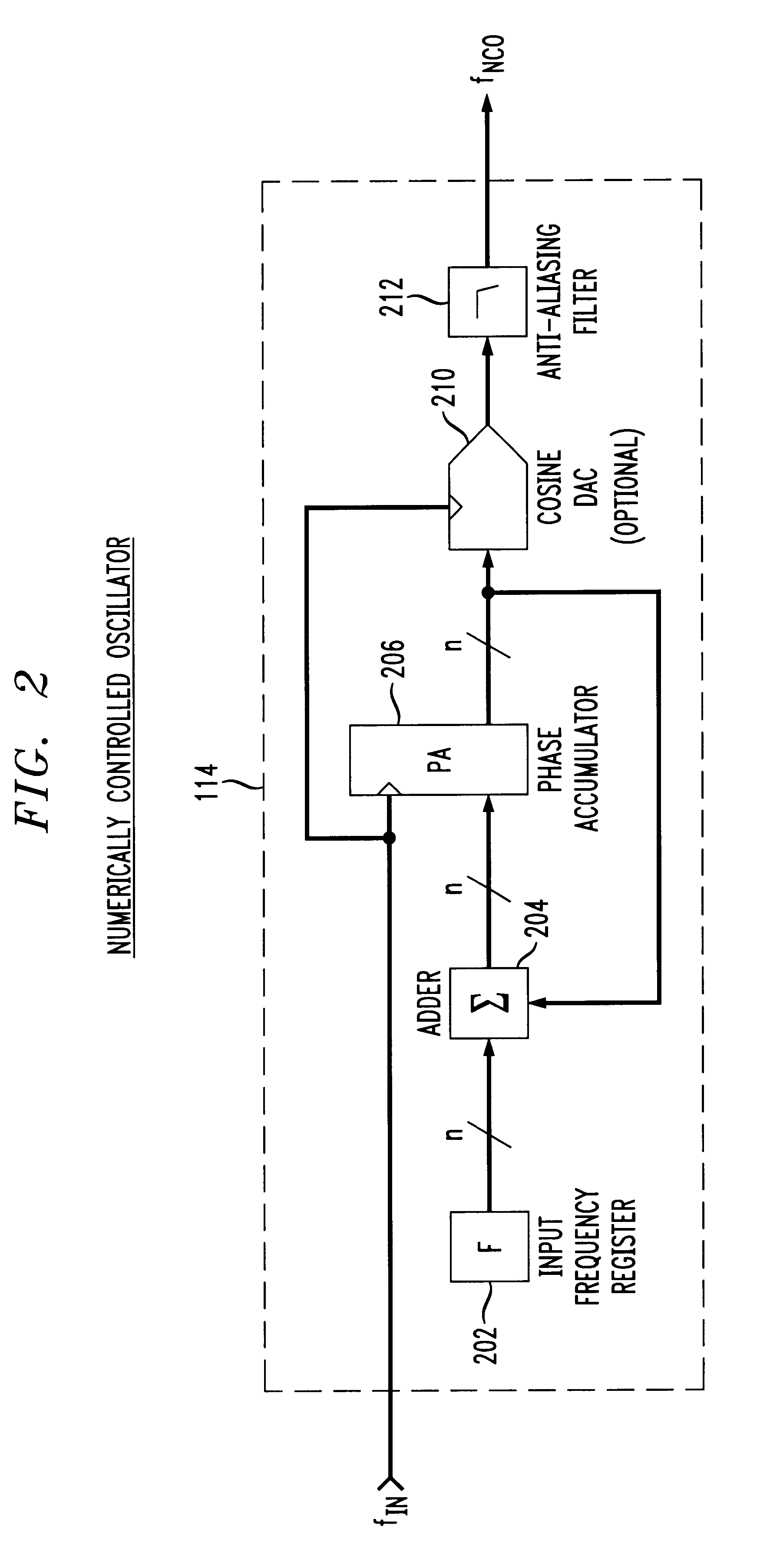

Phase locked loop with numerically controlled oscillator divider in feedback loop

A digital phase locked loop (PLL) frequency synthesizer includes a 1-bit numerically controlled oscillator (NCO) to negate the requirement that a VCO frequency be an integer multiple of its reference frequency. Thus, in accordance with the principles of the present invention, a direct digital synthesizer (DDS) or numerically controlled oscillator (NCO) is used to form a frequency divider in a feedback path of a PLL. Thus, a synthesizer with fine frequency control and very fast settling time is disclosed. The conventional integer-ratio relationship between the reference frequency fREF and the synthesized output frequency signal fVCO is overcome by replacement of a conventional VCO divider in a feedback path of a digital PLL with a 1-bit NCO. This allows the reference frequency fREF to be greater than the channel spacing, i.e., the channel spacing can be smaller than the reference frequency fREF. Thus, a much quicker settling time and improved VCO phase noise are provided, either of which results in a significant improvement in the performance of virtually any communications system.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

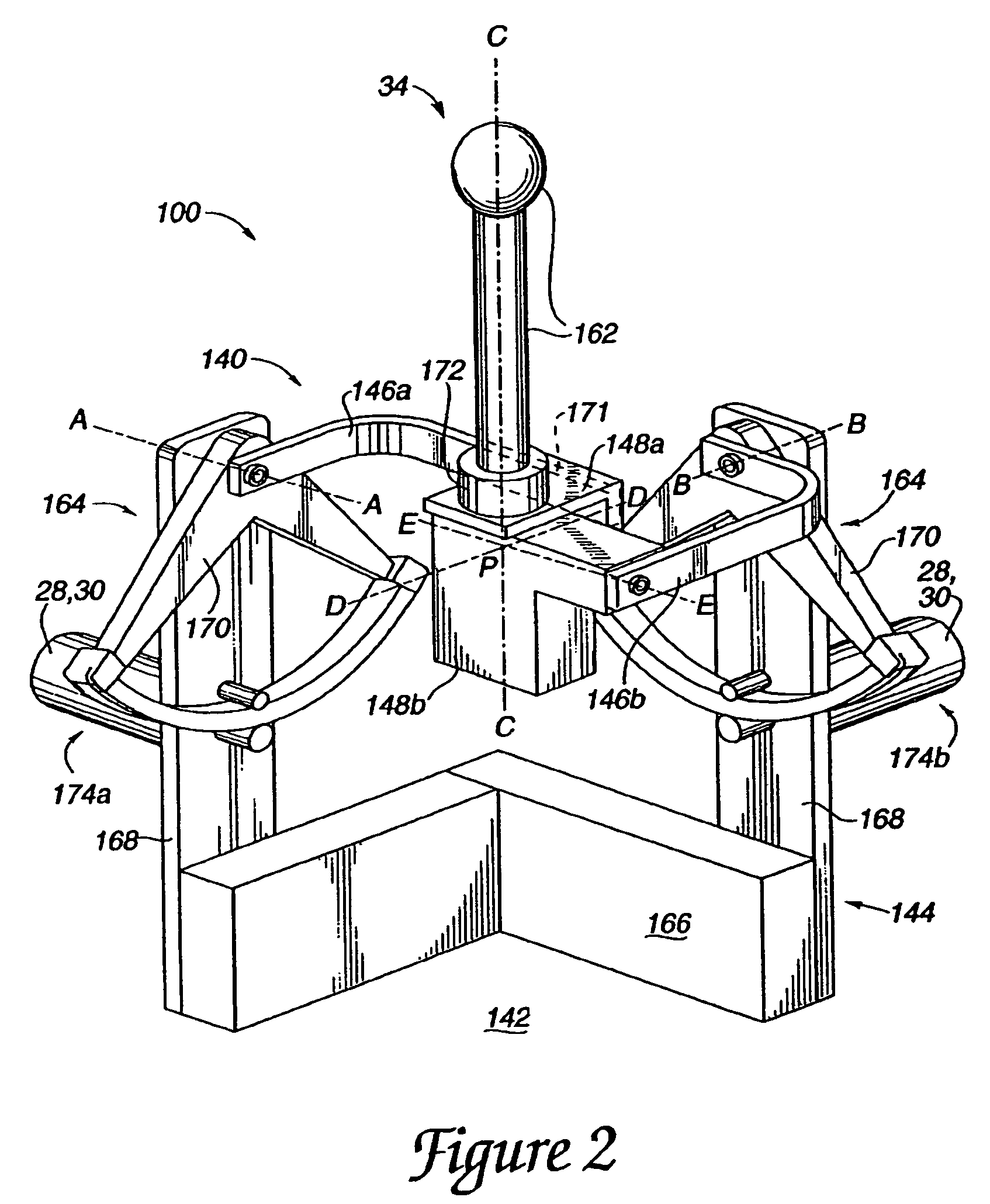

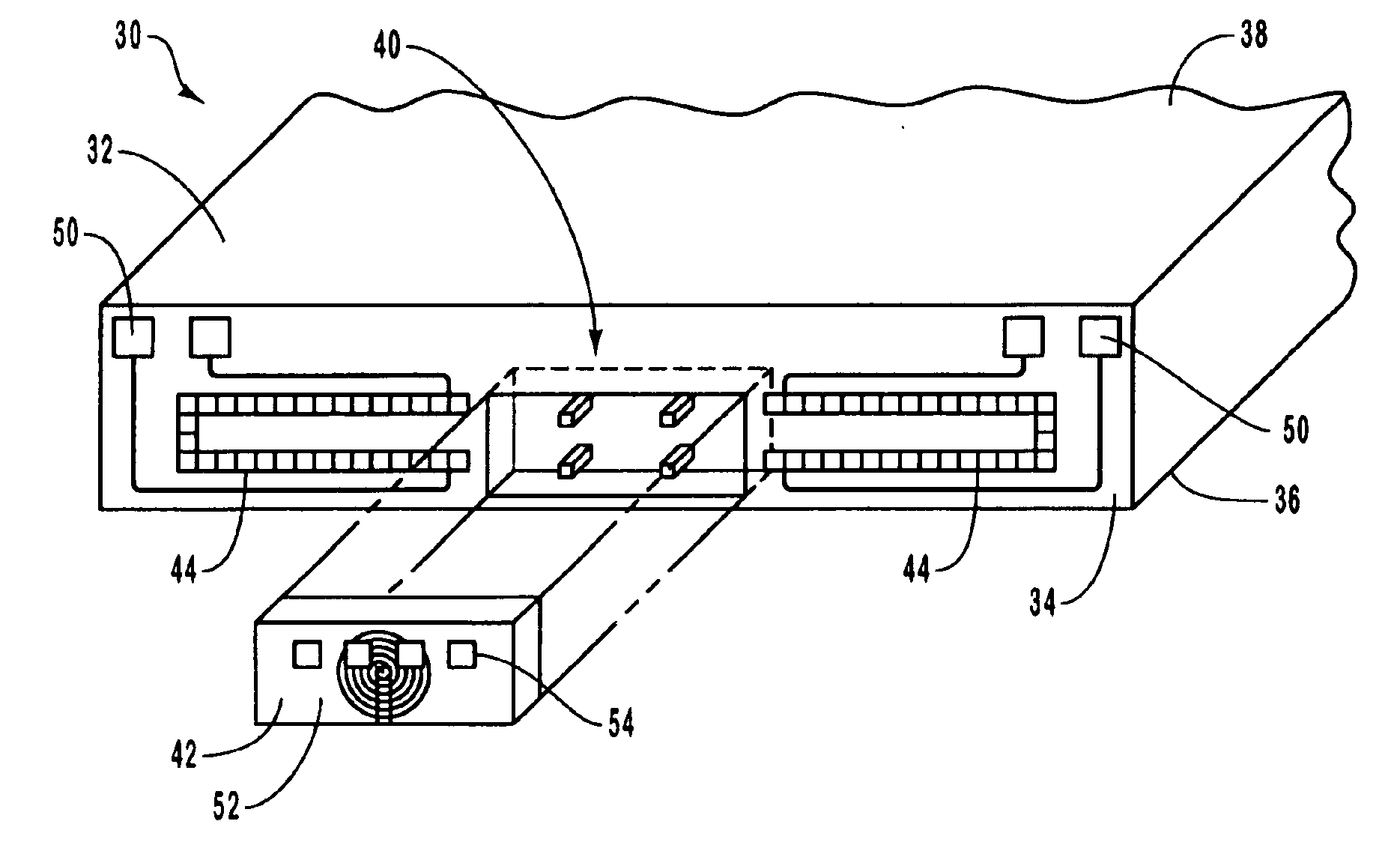

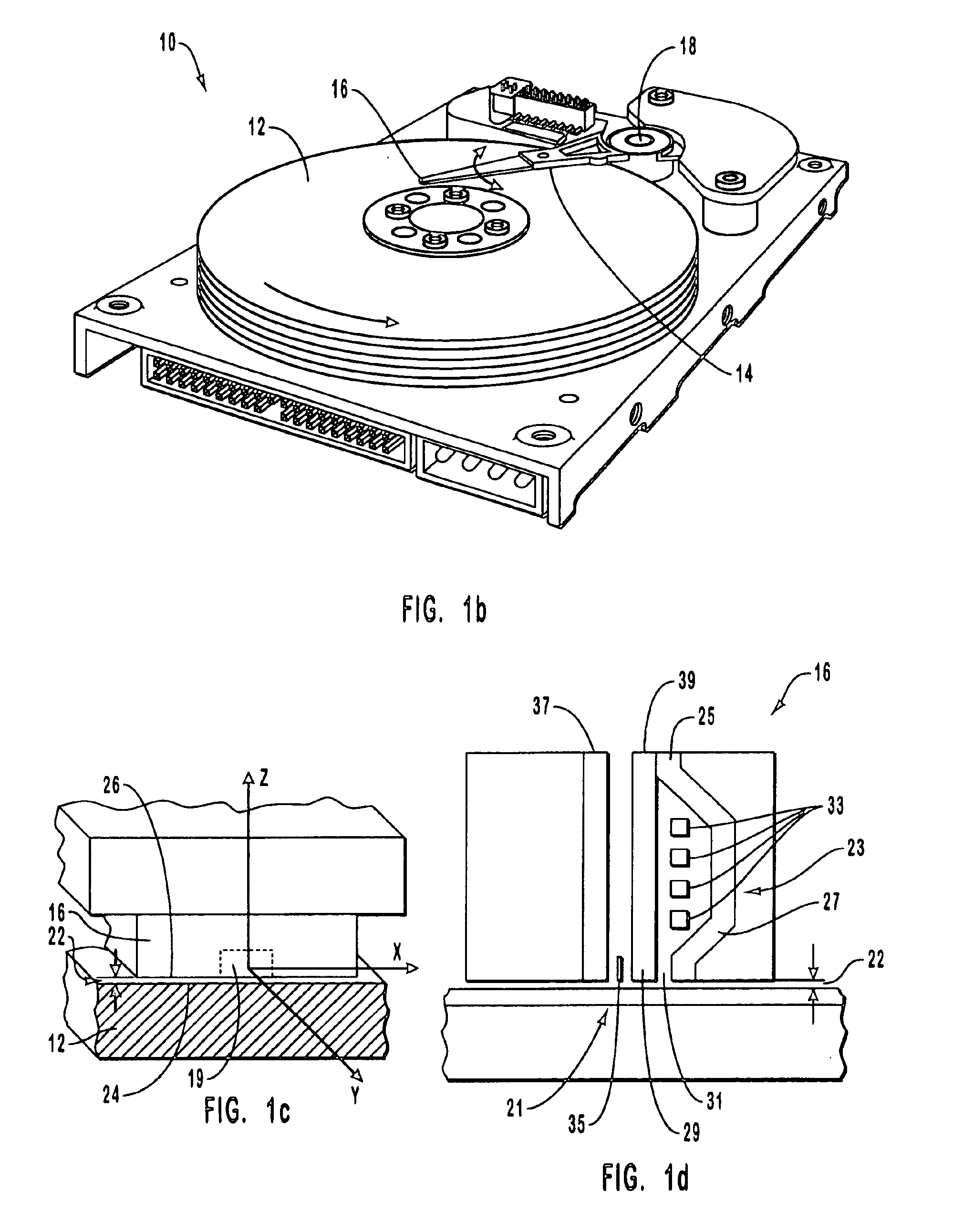

Integrated bidirectional Recording head micropositioner for magnetic storage devices

InactiveUS6859346B1Fast trackReliable trackingConstruction of head windingsFluid-dynamic spacing of headsMagnetic storageAmbient pressure

Transducer elements of recording heads for magnetic storage media are moved independently in either of two directions with respect to the slider of the recording head. The motion is controlled using a micropositioner having magnetic coils integrated into the recording head. The transducer moves in the x direction between data tracks and in the z direction perpendicular to the surface of the magnetic storage medium. The micropositioners are used for small-scale positioning of the transducers over data tracks and to adjust fly heights. Because of the high minimum resonant frequencies and the low mass of the transducers, the micropositioners also improve settling times associated with track following. The micropositioners can be used during fabrication for dimensional control of recording head components. The motion of the transducers in the z direction enables the recording heads to be used reliably in the presence of asperities and changing ambient pressures and temperatures.

Owner:MEYER DALLAS W

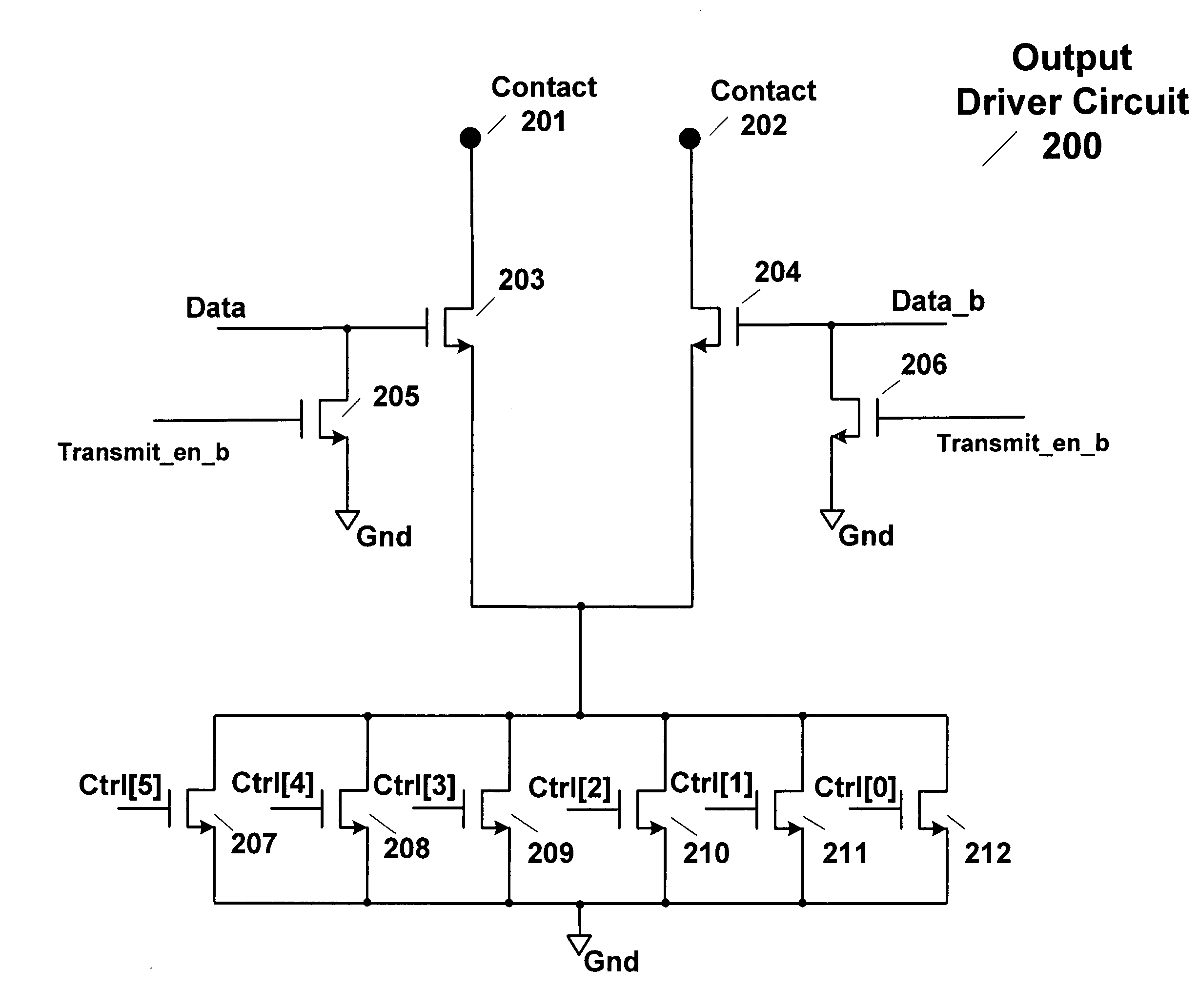

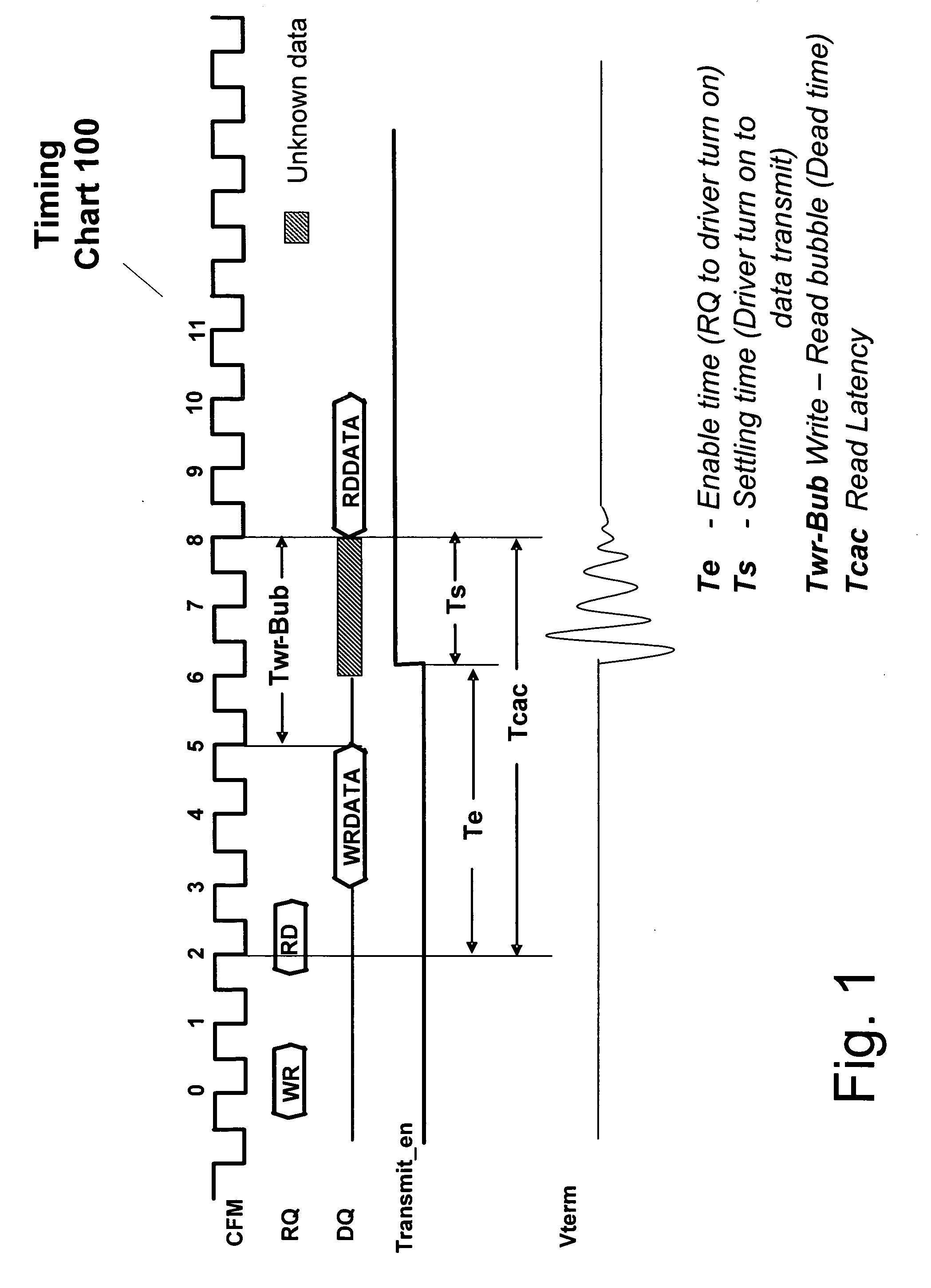

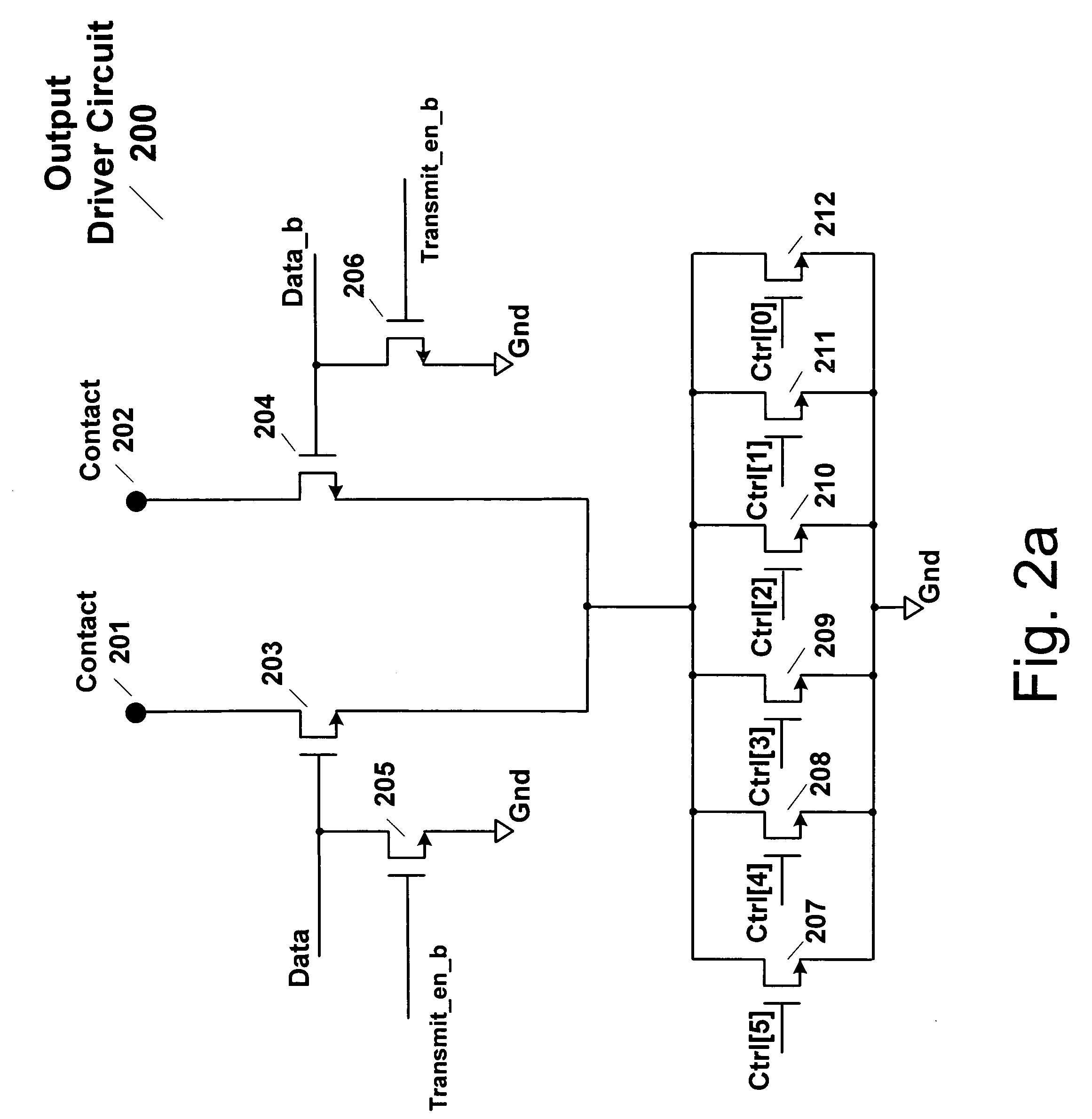

Programmable output driver turn-on time for an integrated circuit memory device

An integrated circuit memory device, system and method turns on an output driver in response to a stored value that represents an amount of time from when the output driver is in an operational state to when the output driver begins to output valid read data in various embodiments. An output driver outputs valid read data after a settling amount of time. The sum of the amount of time from when the memory device receives a read command to when the output driver is turned-on and the settling amount of time, is approximately the time from receiving the read command, to at least beginning to provide valid read data at the output of the integrated circuit memory device. A read command is provided to the integrated circuit memory device by a memory controller. In an embodiment, the memory controller also provides or programs the value that represents the amount of time from when the output driver is in an operational state to when the output driver begins to output valid read data.

Owner:RAMBUS INC

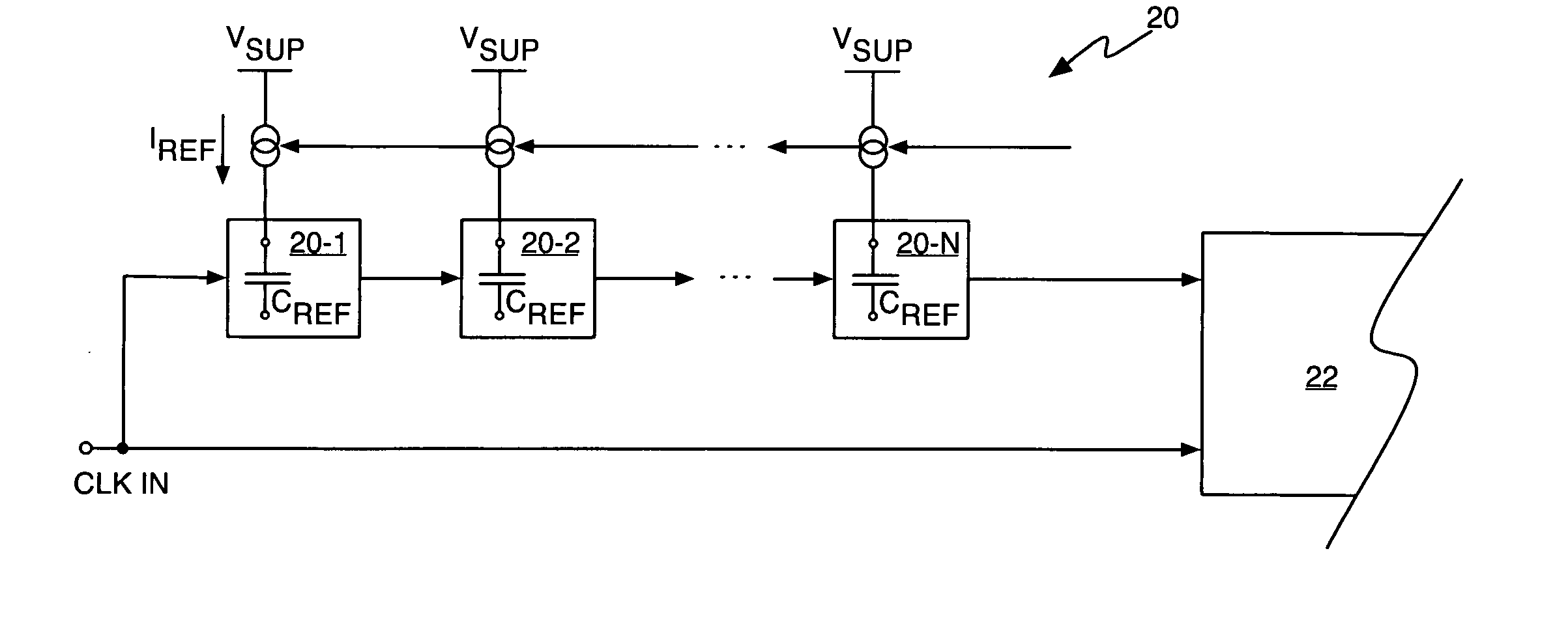

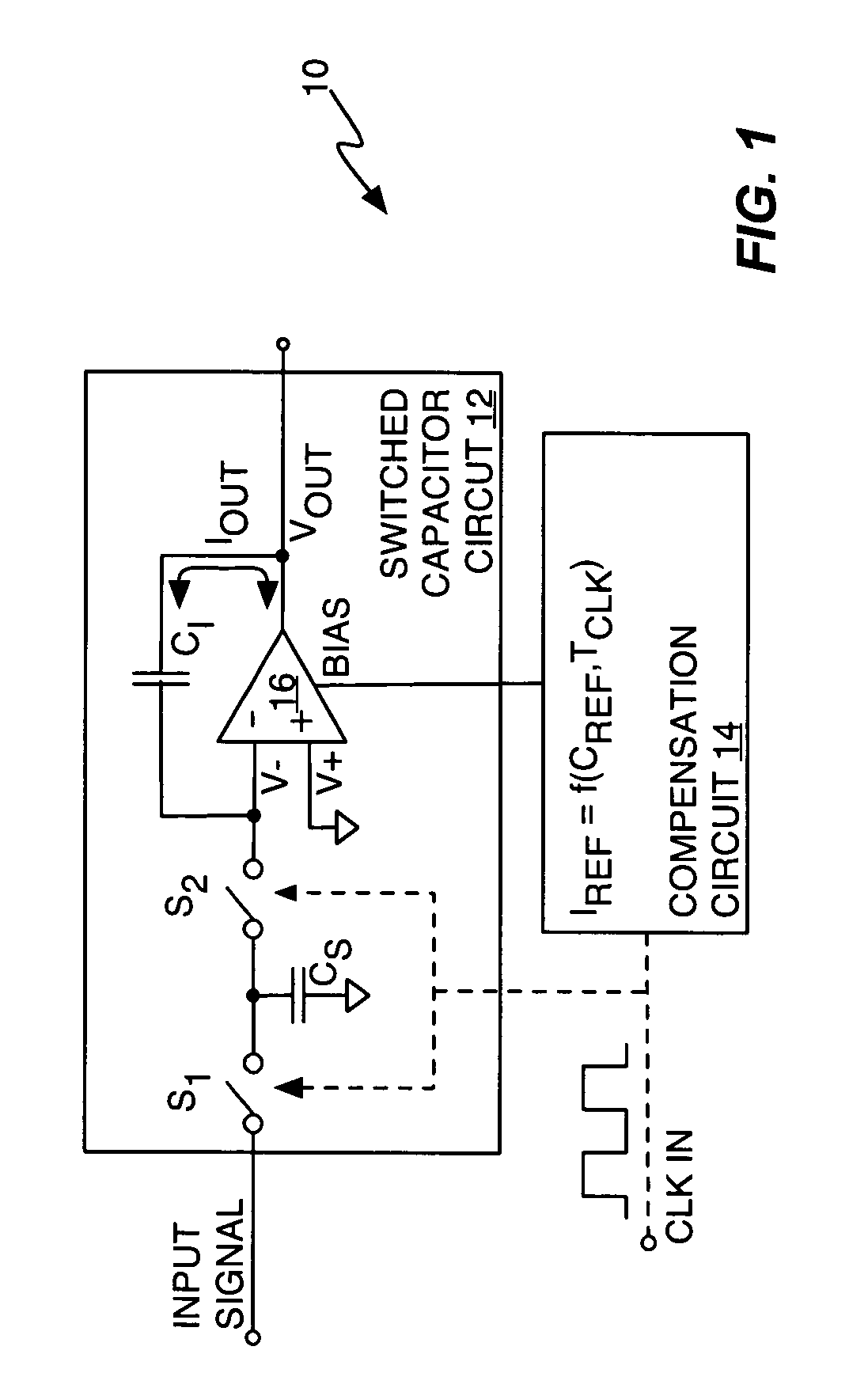

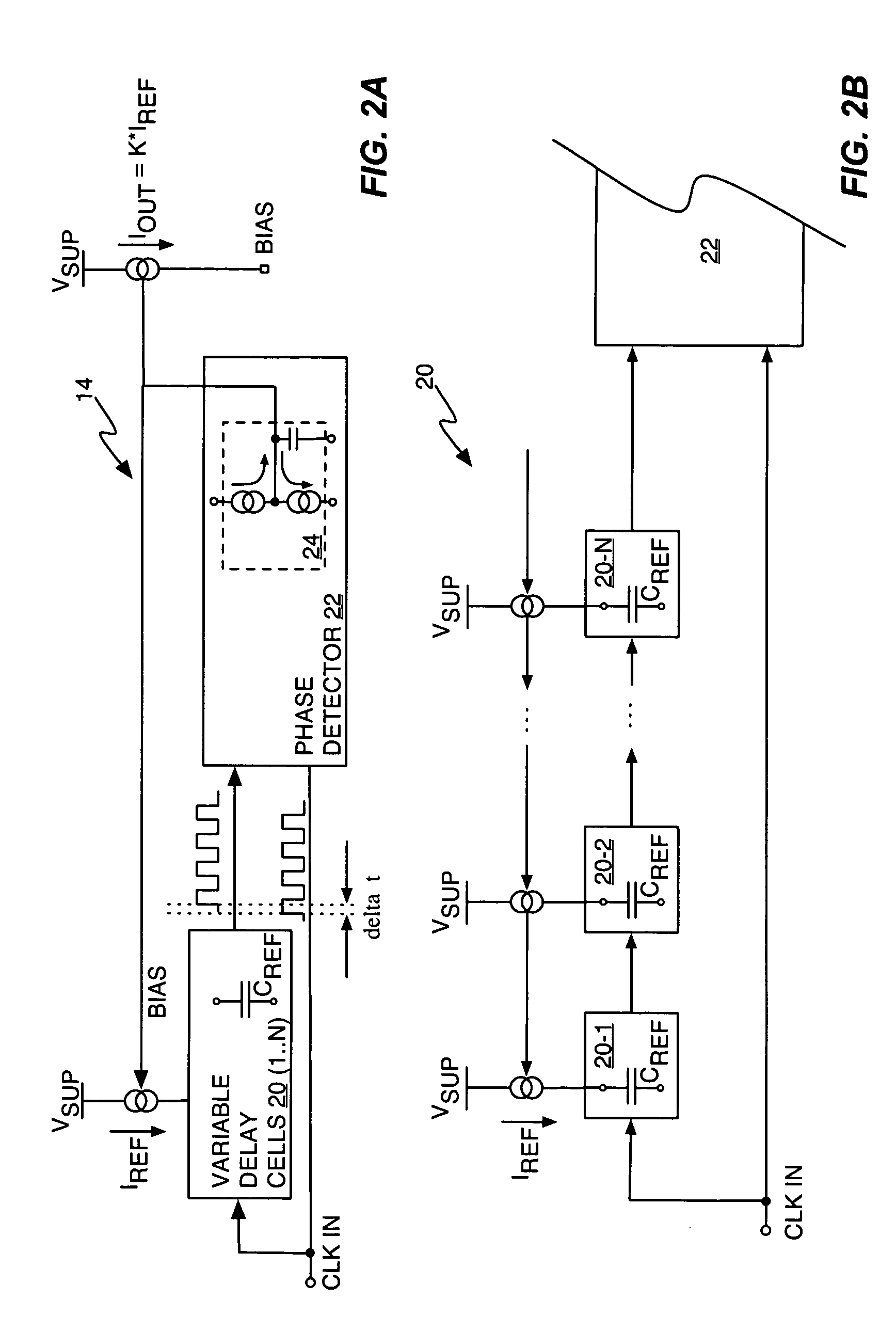

Switched capacitor circuit compensation apparatus and method

ActiveUS20050140422A1Easy to useIncrease currentElectric analogue storesDigital differential analysersCapacitanceLoop control

A compensated switched capacitor circuit comprises a switched capacitor circuit and a compensation circuit. The compensation circuit generates a reference current that varies under closed loop control to maintain a targeted slew rate for charging a reference capacitor that is determined by the input clock frequency. The switched capacitor circuit's output amplifier is configured such that its output current varies in proportion to the reference current. Thus, by configuring the reference capacitor to track the effective capacitance of the switched capacitor circuit, the settling time of the switched capacitor circuit may be made relatively insensitive to the value of and changes in the effective capacitance over a range of clock frequencies. The compensation circuit may include a clock reconditioning circuit to ensure that the switched capacitor circuit is clocked at a desired duty cycle.

Owner:TELEFON AB LM ERICSSON (PUBL)

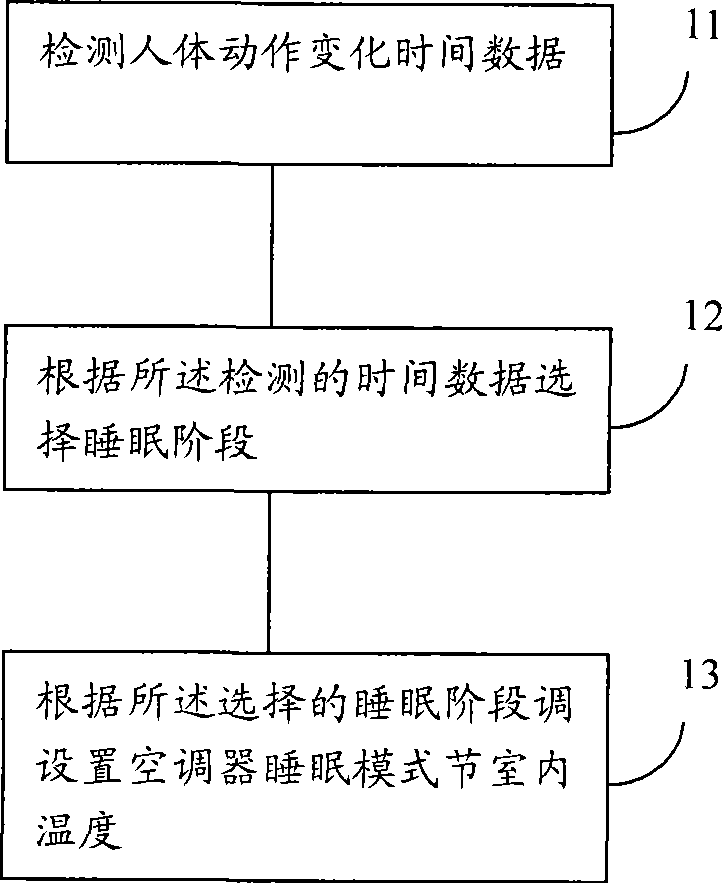

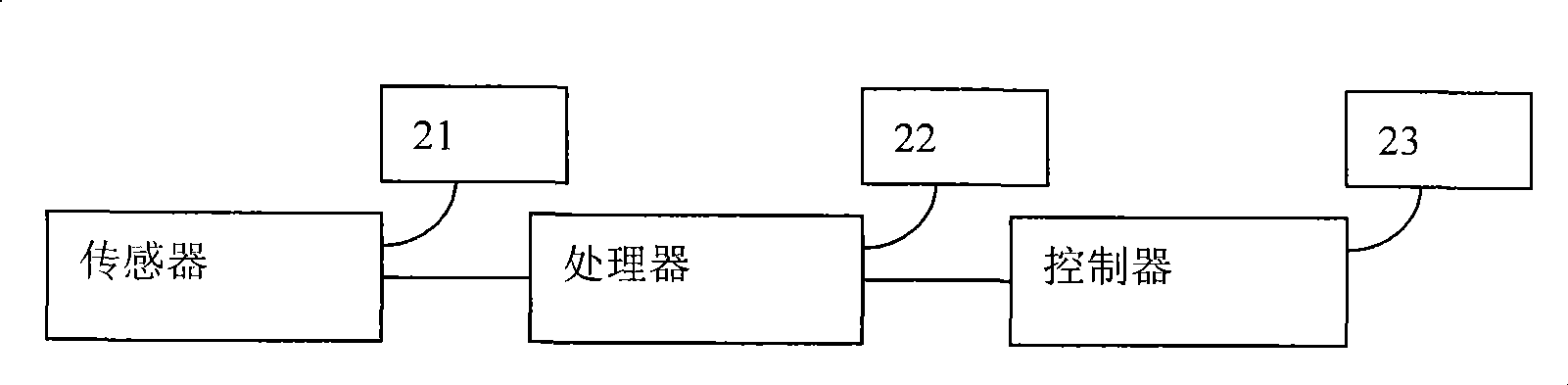

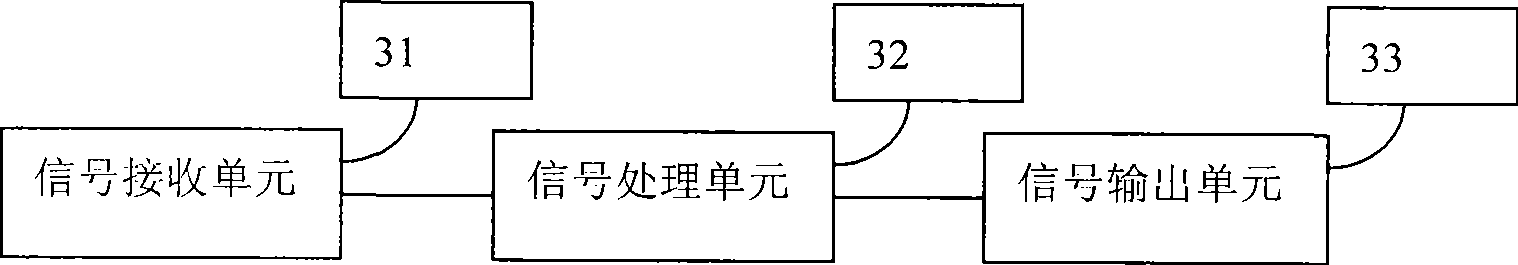

Air conditioner and method for setting sleeping mode of the same

ActiveCN101440992AControl and adjust the indoor temperatureSpace heating and ventilation safety systemsLighting and heating apparatusRegulation temperatureEngineering

The present invention discloses a method for setting sleeping mode of an air conditioner and an air conditioner, the method is characterized by selecting and actuating a sleeping stage corresponding to the dissipative time though detecting single actuating duration time or twice actuating spacing interval of each user or simultaneously detecting the single actuating duration time and the twice actuating spacing interval, setting sleeping mode of the air conditioner according to the dissipative time of different sleeping stage, controlling the air conditioner to regulate the indoor temperature, thereby the problem of the indoor temperature of the single sleeping mode which can but regulated according to the settled time is avoided, the requirement of the air conditioner regulation temperature for each user at the sleeping stage is fully satisfied according to the different dissipative time of different user at each sleeping stage.

Owner:GUANGDONG CHIGO AIR CONDITIONING

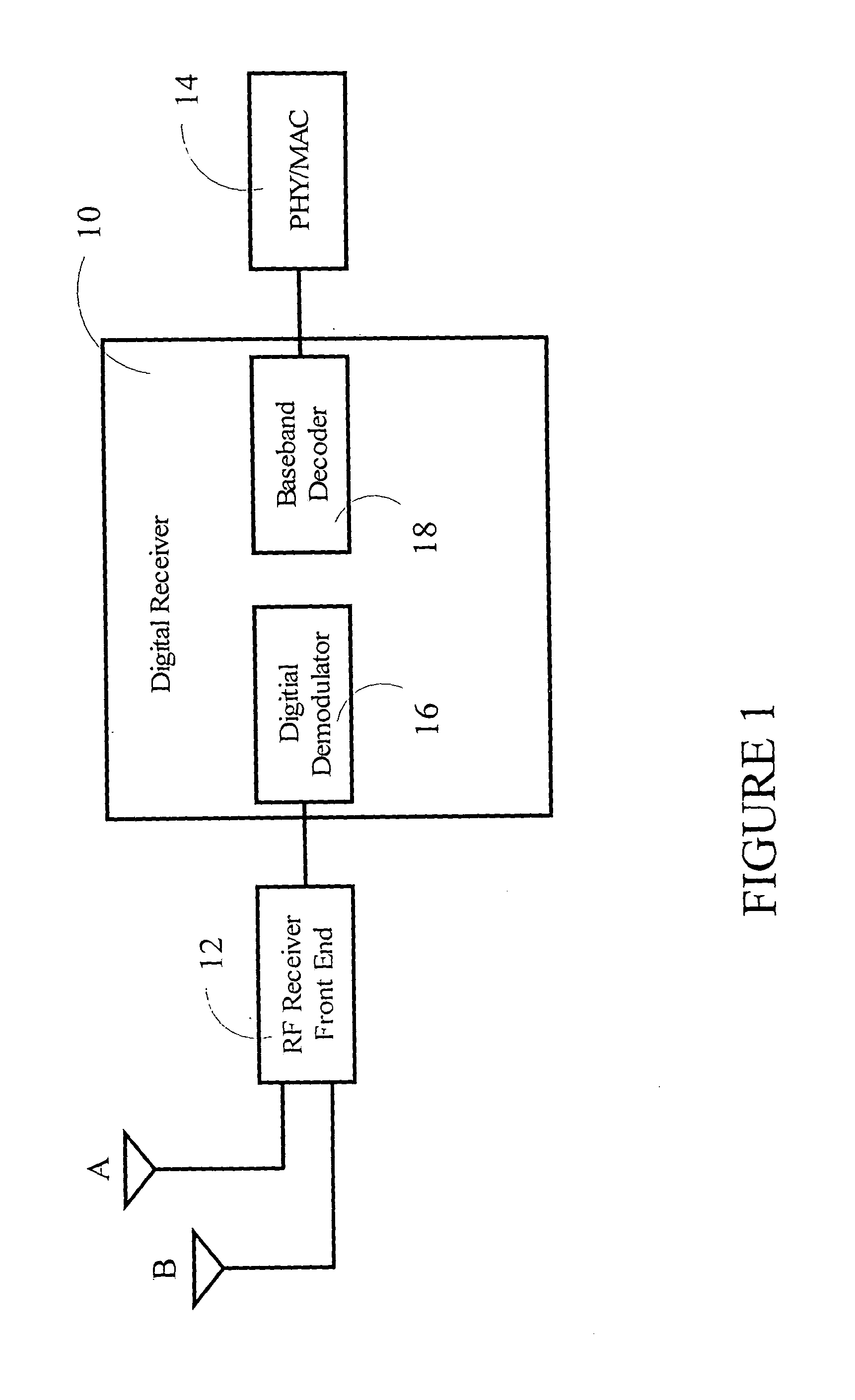

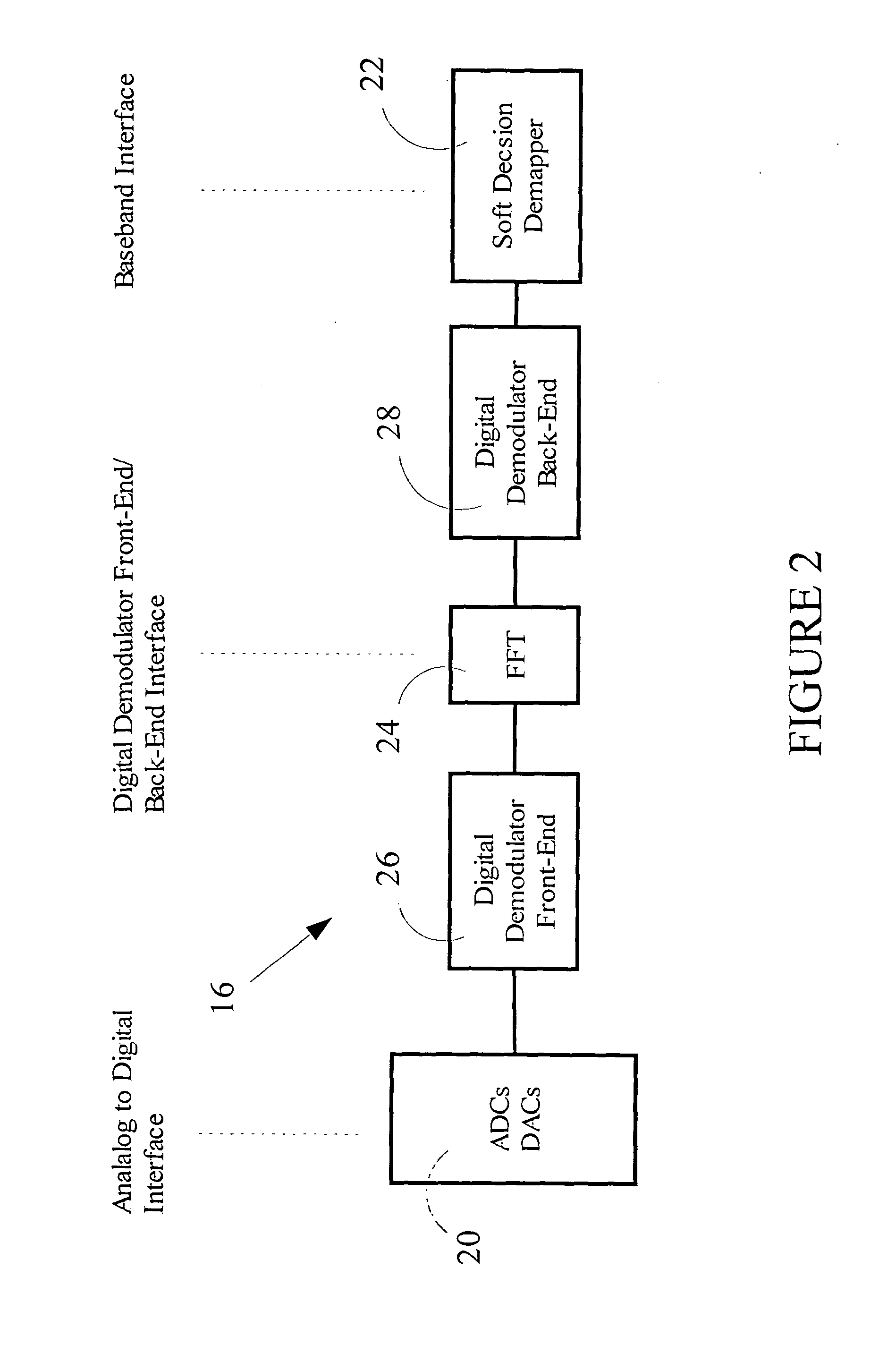

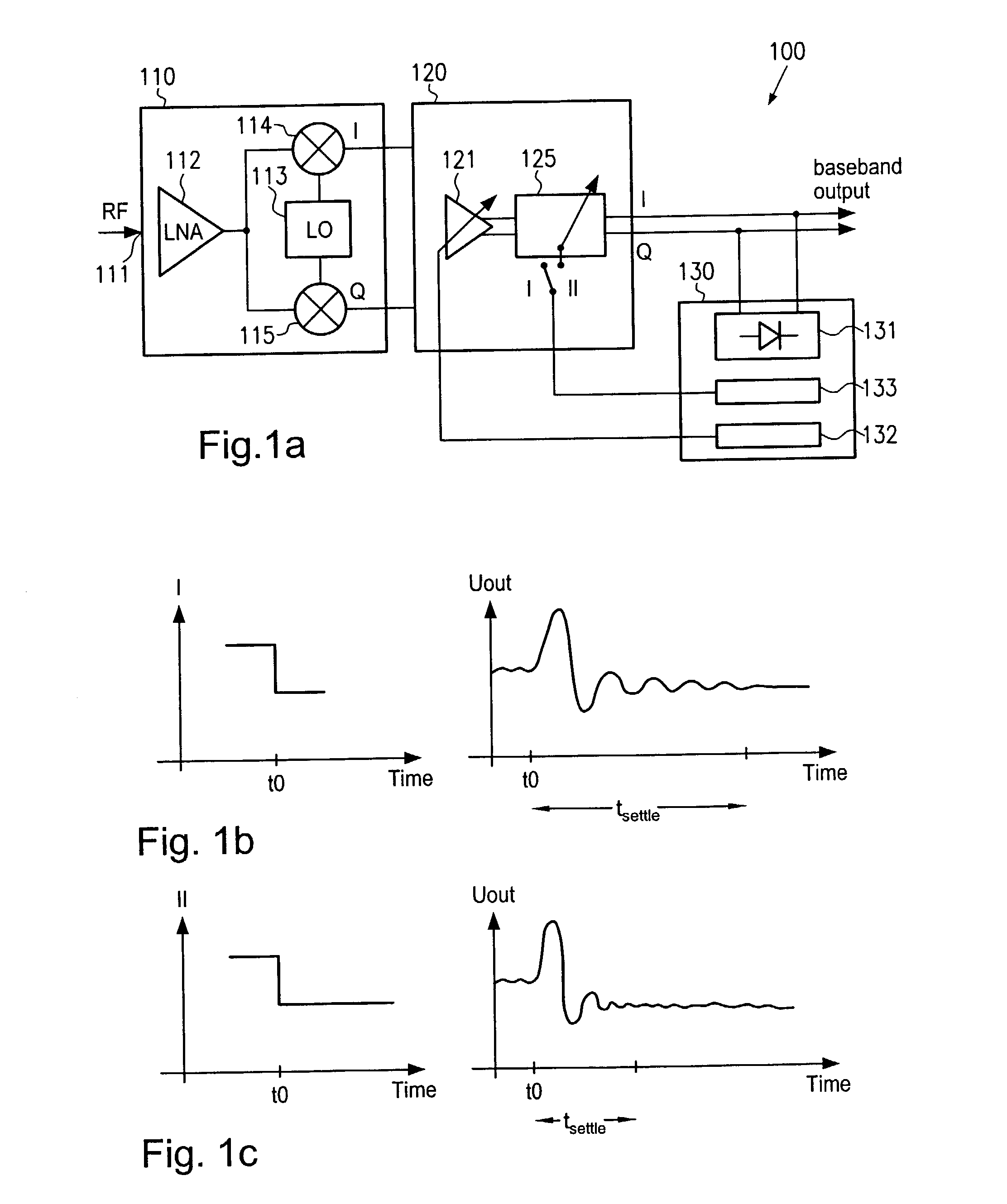

Digital automatic gain controlling in direct-conversion receivers

In a direct conversion radio frequency receiver, an automatic gain control is implemented that allows changing the operation mode of a filter unit in the baseband section of the receiver such that in a first operation mode filter capacities are selected to provide desired output signal characteristics, whereas in a second operation mode the filter settling time is significantly reduced in order to speed up gain adaptation and to improve gain loop stability. In one embodiment the cut-off frequency of a high pass filter and the Q-factor of a subsequent low pass filter are increased and decreased respectively upon changing the gain setting of a variable gain amplifier to accelerate settling of the filter.

Owner:MEDIATEK INC

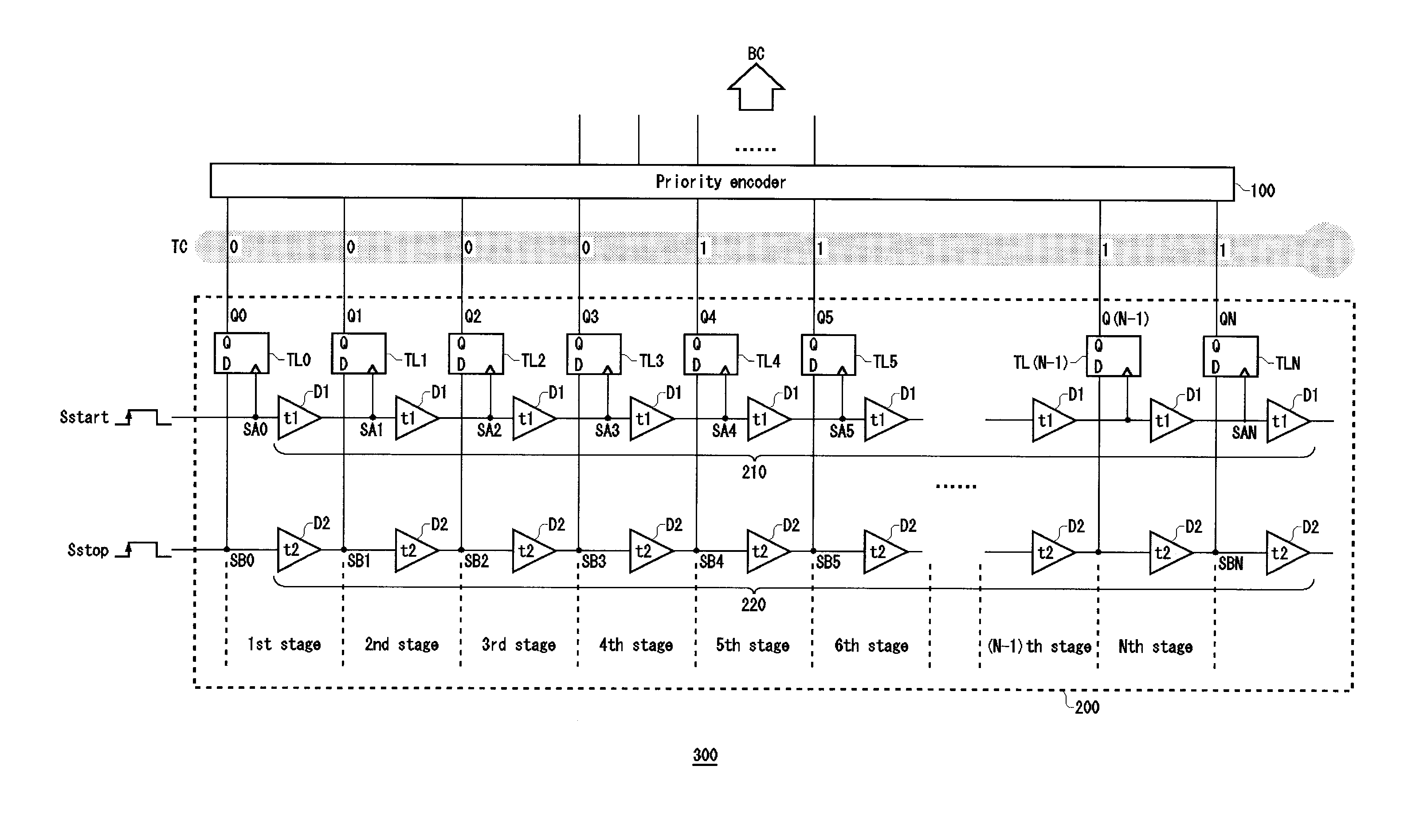

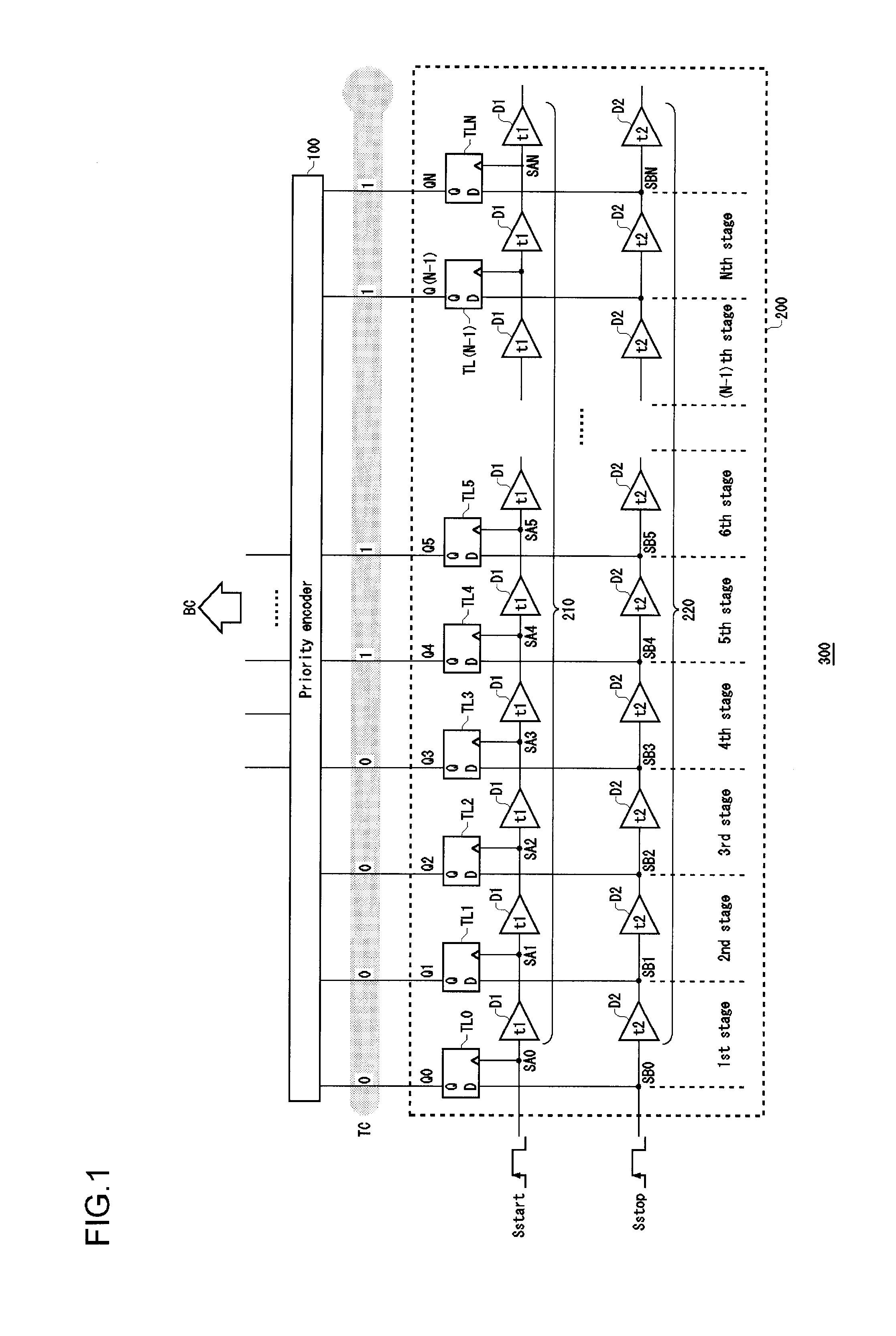

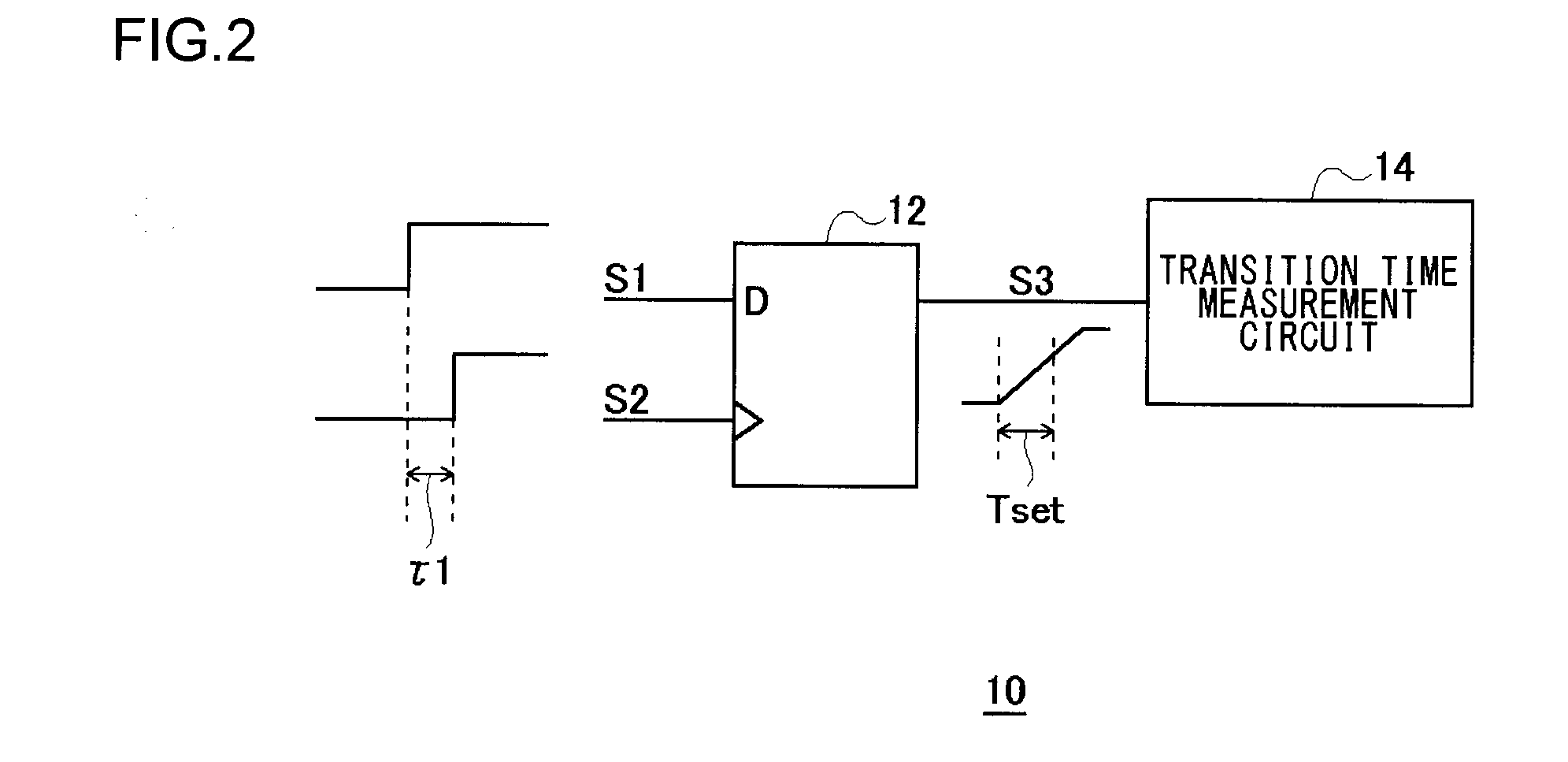

Time measurement circuit

InactiveUS20110133973A1Reduce resolutionMaintain resolutionElectric signal transmission systemsElectrical testingTime differenceTransition time

A time measurement circuit measures the time difference between edges of a first signal and a second signal. A sampling circuit acquires the logical level of the first signal at a timing of the edge of the second signal. When a sampling circuit enters a metastable state, an output signal thereof transits with a long time scale. A transition time measurement circuit measures a transition time (settling time) of the output signal of the sampling circuit in the metastable state.

Owner:ADVANTEST CORP

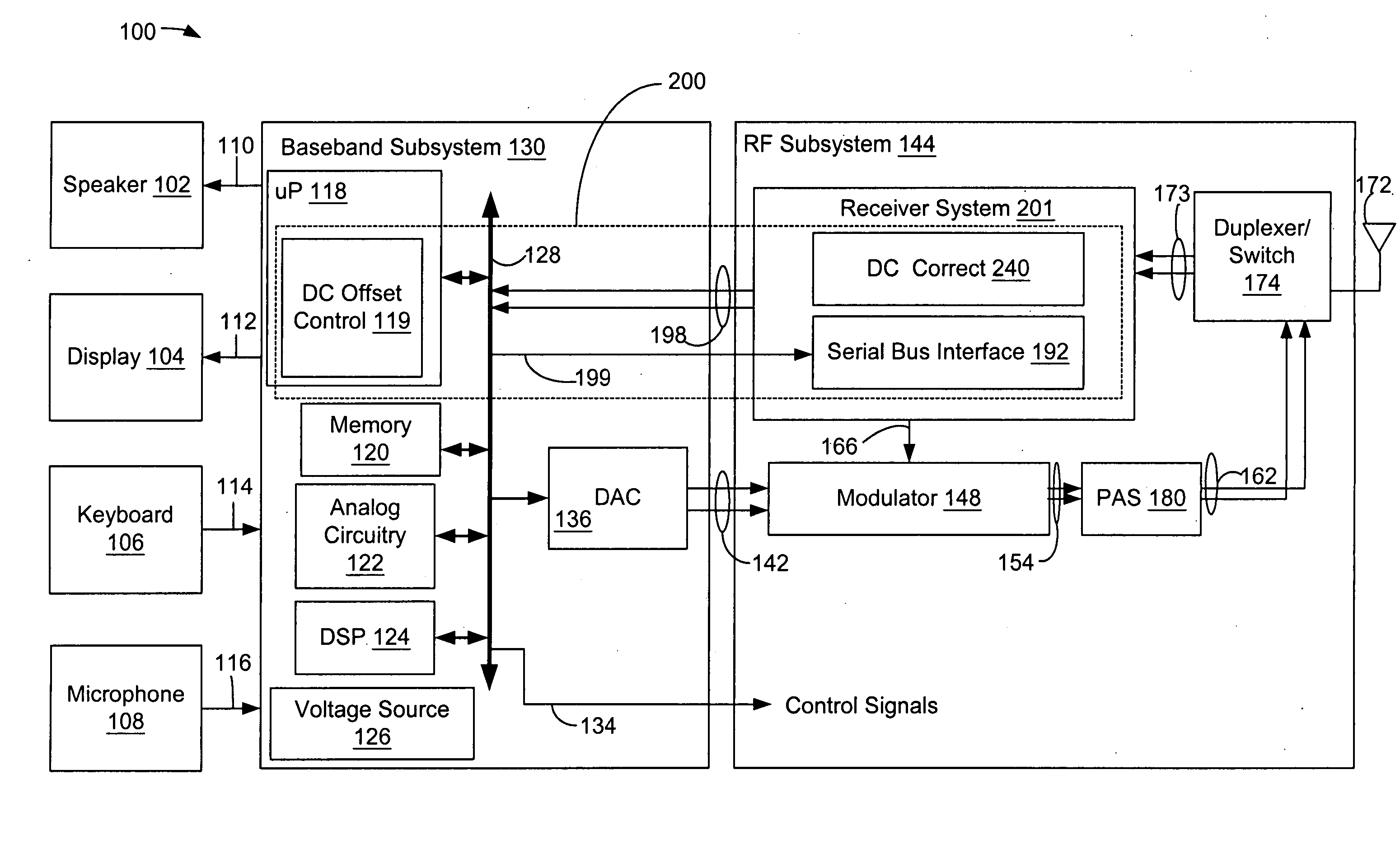

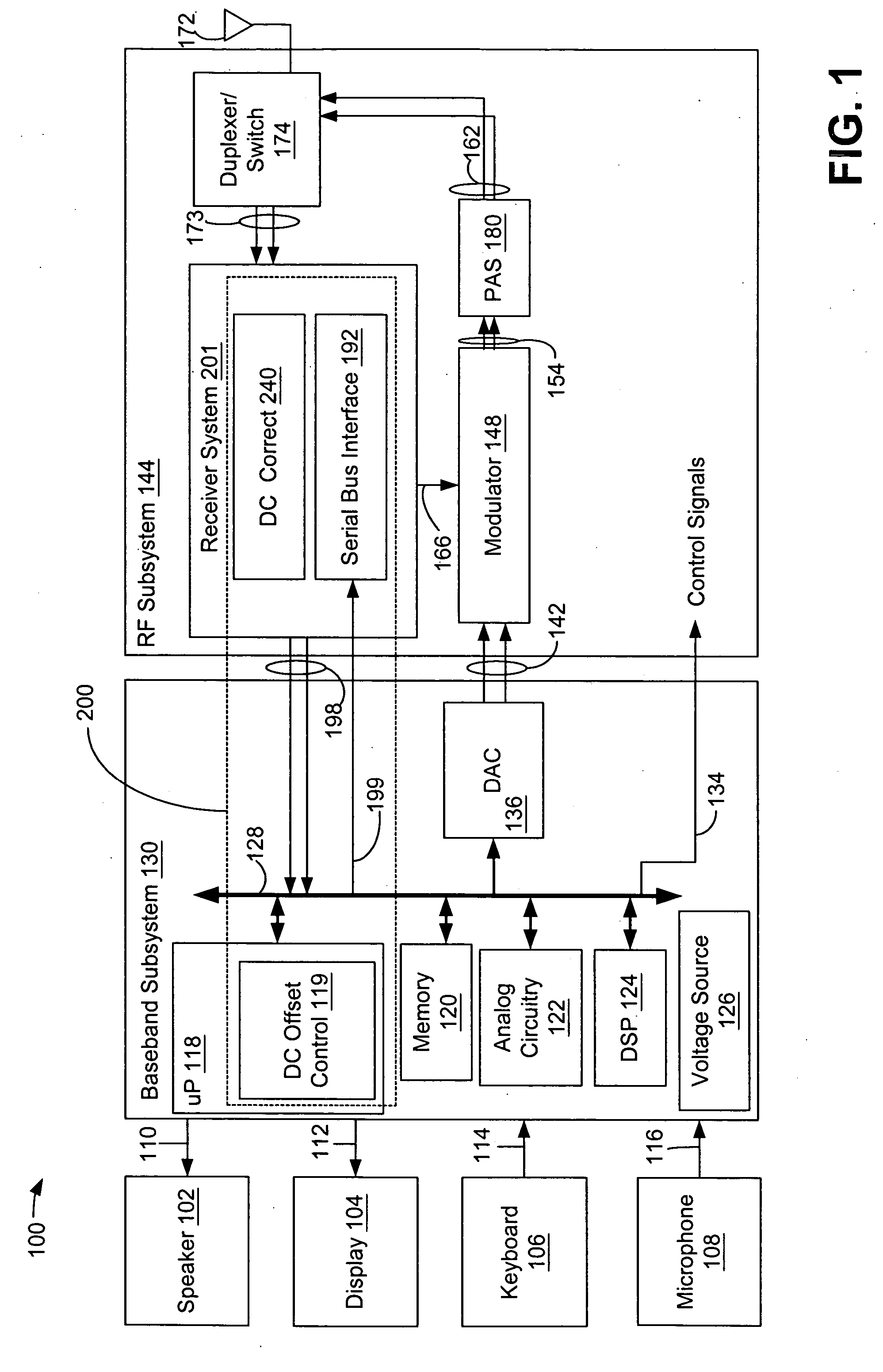

Direct current offset correction systems and methods

ActiveUS20050225388A1Speed up settlingSettling timeAmplifier modifications to reduce temperature/voltage variationDc level restoring means or bias distort correctionControl logicDirect current

A system and method for direct current offset correction are disclosed. One embodiment of the system includes a direct current offset correction circuitry having an adjustable bandwidth and control logic configured to effect a bandwidth change of the direct current offset correction circuitry to speed up warm-up and settling time of the direct current offset correction circuitry.

Owner:MEDIATEK INC

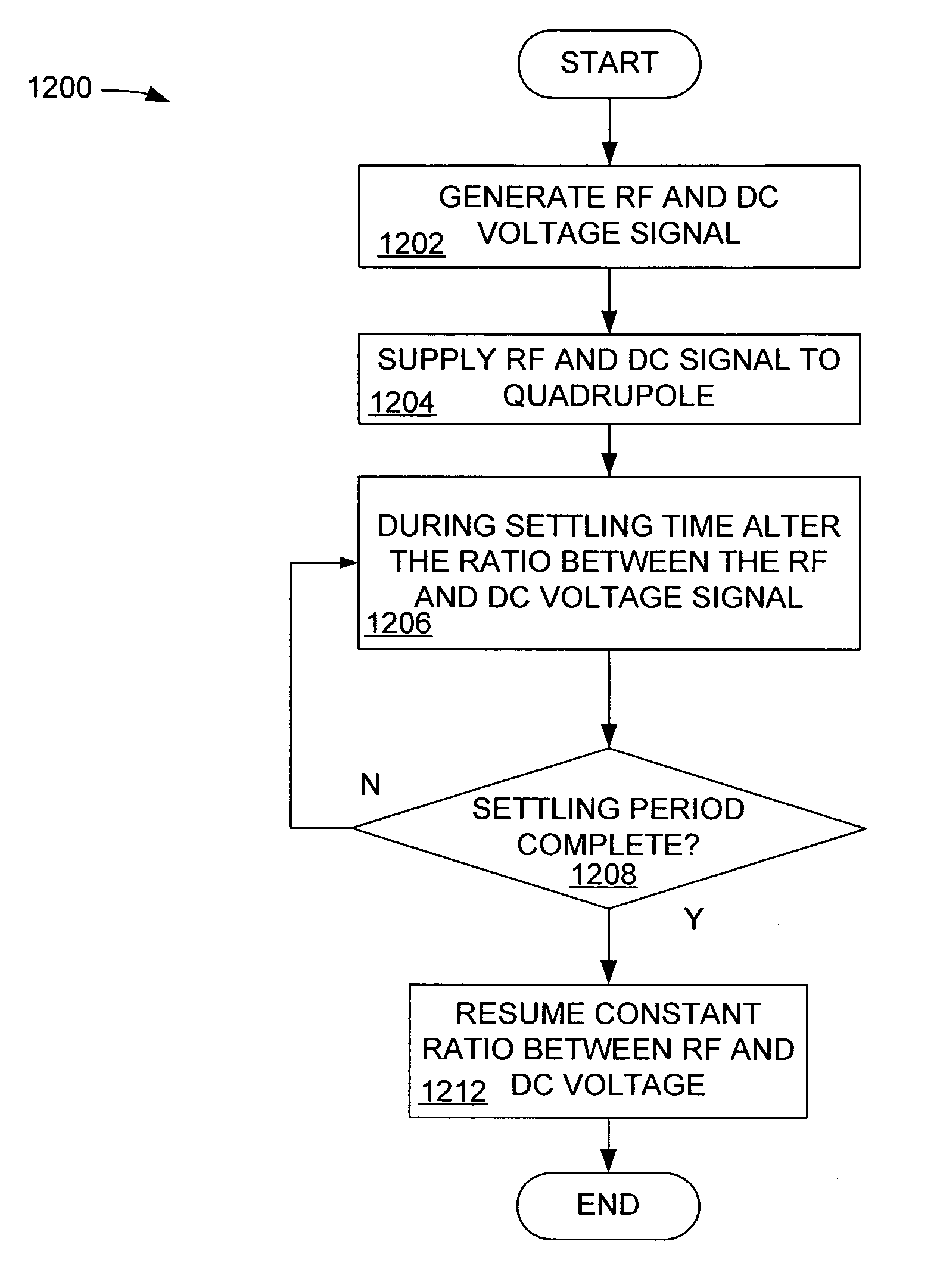

Apparatus and method for electronically driving a quadrupole mass spectrometer to improve signal performance at fast scan rates

ActiveUS20060016985A1Altering responseStability-of-path spectrometersSpectrometer circuit arrangementsEngineeringMass analyzer

An apparatus for electronically controlling a quadrupole in a mass spectrometer, comprises radio frequency (RF) drive circuitry and direct current (DC) drive circuitry coupled to a quadrupole, an RF control loop associated with the RF drive circuitry, a DC control loop associated with the DC drive circuitry, and control loop circuitry associated with the DC control loop, the control loop circuitry configured to alter a response of the DC control loop during a settling time period of a step response such that ion transmission through the quadrupole is greater during the settling time than if the response of the DC control loop during the settling time is unaltered.

Owner:AGILENT TECH INC

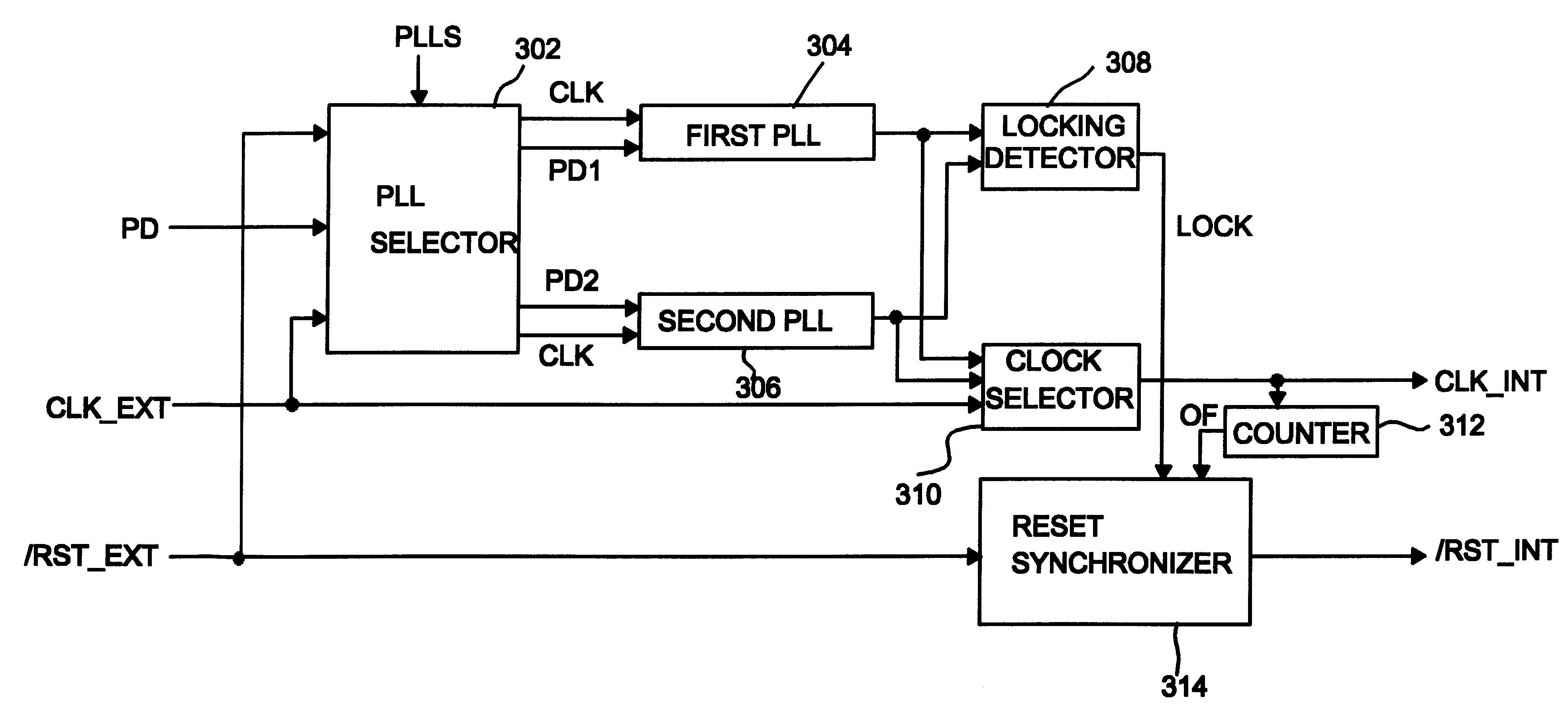

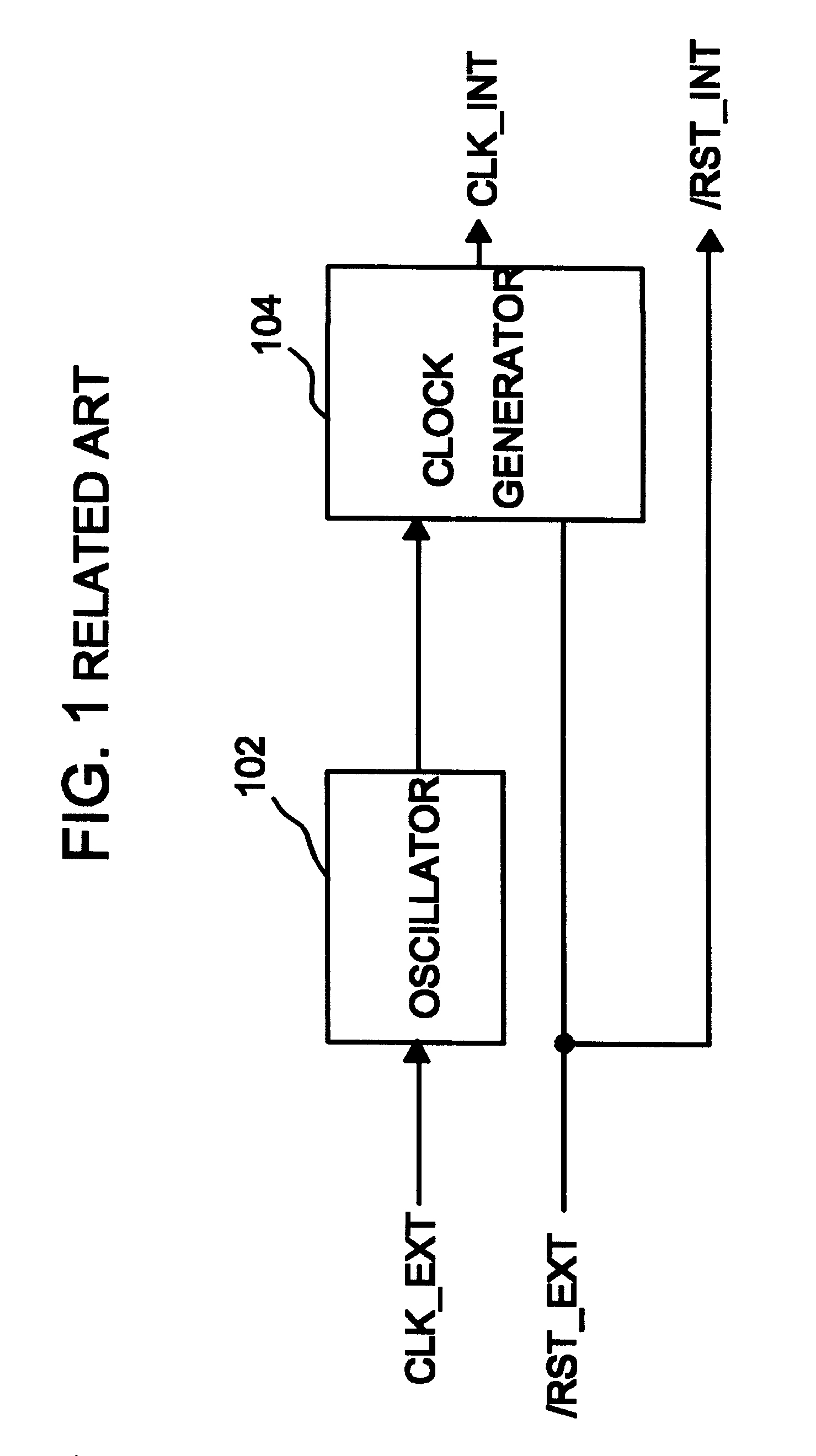

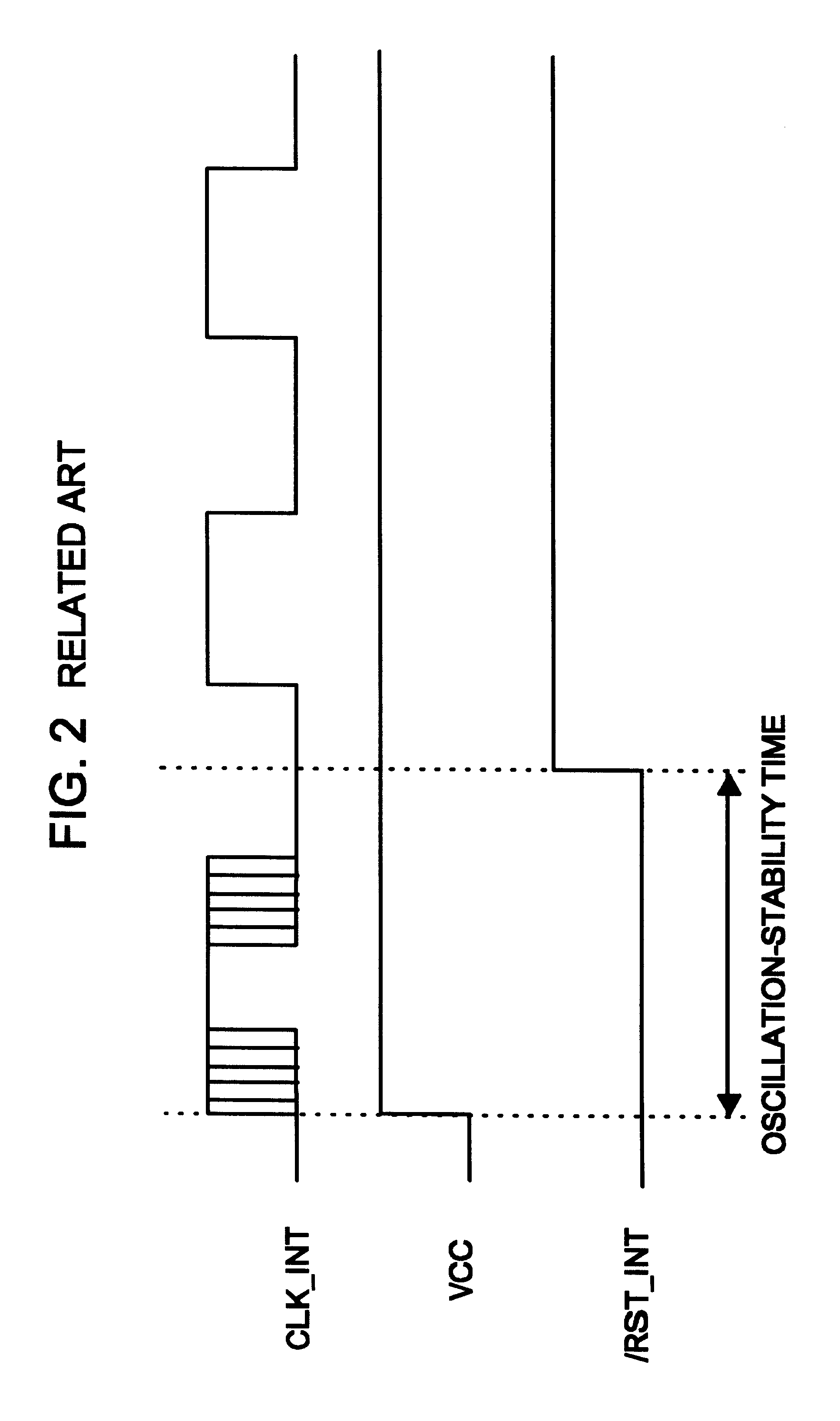

Reset signal generation circuit

A reset signal generation circuit of the present invention includes a phase locked loop (PLL) selector, a plurality of PLLs, a locking detector, a clock selector, a counter, and a reset synchronizer. The PLL selector is activated when an external reset signal is high and provides a signal for selecting one of the plurality of PLLs according to a power down control signal and a PLL selection signal. The plurality of PLLs have different input frequency signals and different output frequency signals. They are activated in response to an external clock signal and inactivated in response to the power down control signal. The locking detector detects locking / unlocking of the PLLs based upon the output frequency signals of the PLLs and generates a locking signal. The clock selector selectively provides one of the output signals of the PLLs and the external clock signal. The counter is coupled to the clock selector and generates an overflow signal after completing count of a predetermined number. In response to the overflow signal of the counter, the reset synchronizer generates an internal reset signal synchronizing with the locking signal. The present invention controls the stable reset mode release time regardless of the settling time of the oscillation signal by controlling the reset signal using the locking signal of the PLL. A current state is maintained even though the locking state of the PLL is released, so the operation of the chip is not influenced by the reset of the PLL.

Owner:MAGNACHIP SEMICONDUCTOR LTD

Phase Locked Loop Fast Lock Method

ActiveUS20070024383A1Quality improvementReduced settling timePulse automatic controlOscillator tubesLoop filterIntegrator

The present invention is a method to rapidly lock a type II phase locked loop (PLL) after a frequency jump without degrading the output signal much. The method to decrease the settling time and improve the quality of the output clock during the settling disclosed herein comprises of the following broad steps: Estimate new frequency offset with a separate circuit outside the PLL loop to measure the frequency of the input signal accurately. Ramp integrator to the new frequency offset. Do phase build out or phase pull-in. The remaining phase offset is build out when no edge to edge alignment is required. Otherwise, the remaining phase offset is pulled in while the integrator in the PLL's loop filter is disabled. Reduce the PLL bandwidth and / or lower damping to let the PLL settle. Switch the PLL to final bandwidth and damping required by the application.

Owner:ZARLINK SEMICON LTD

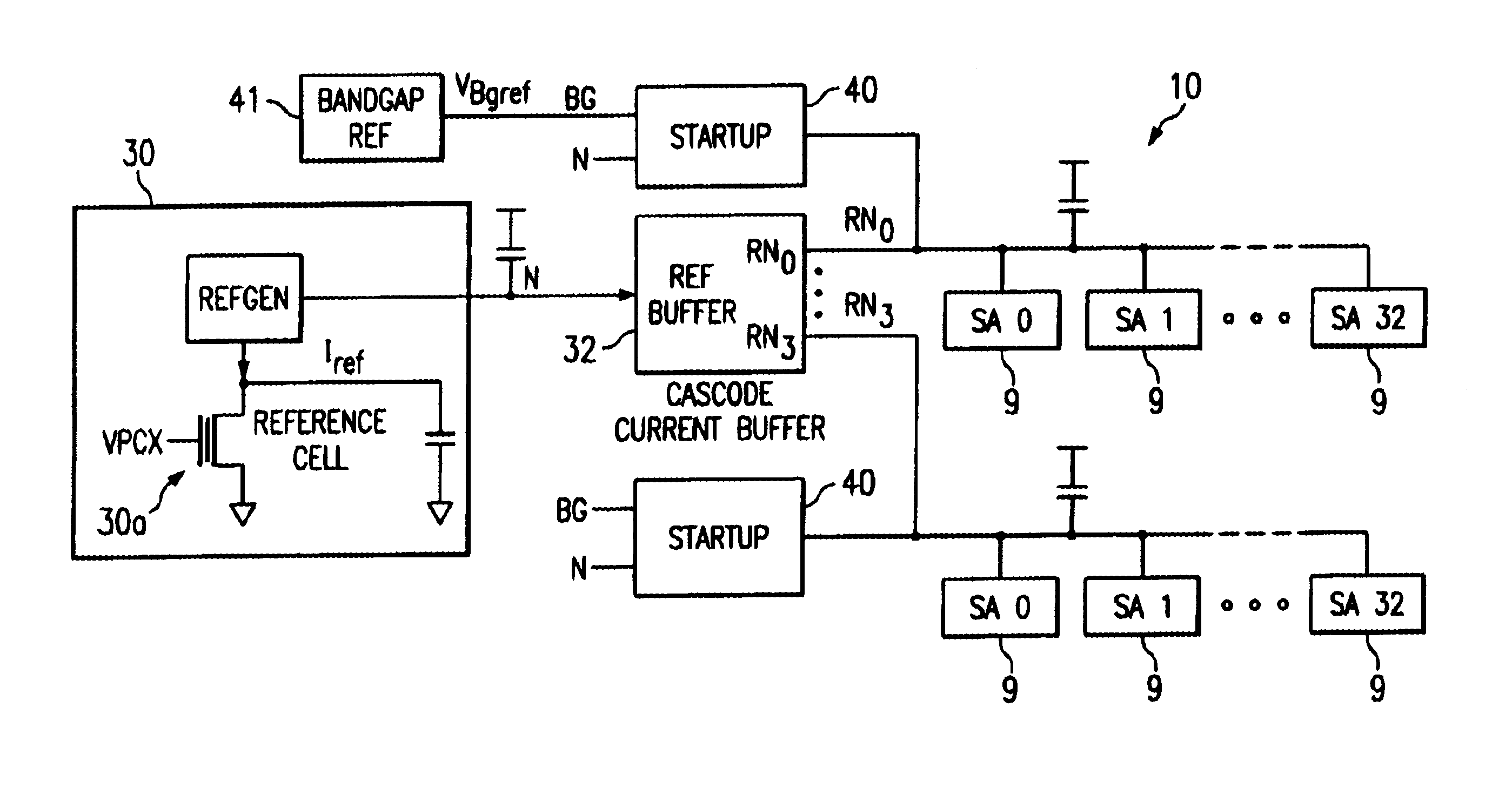

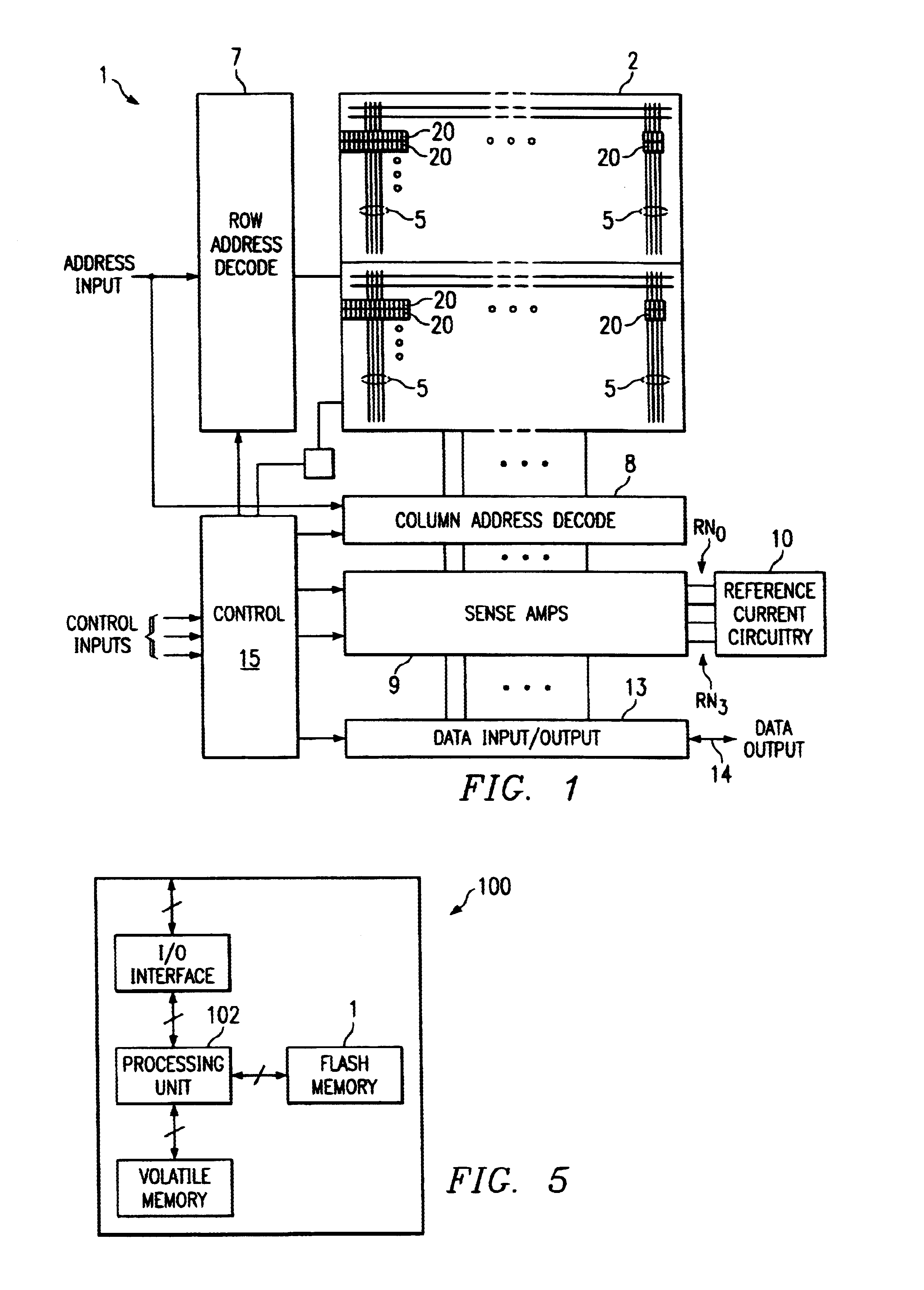

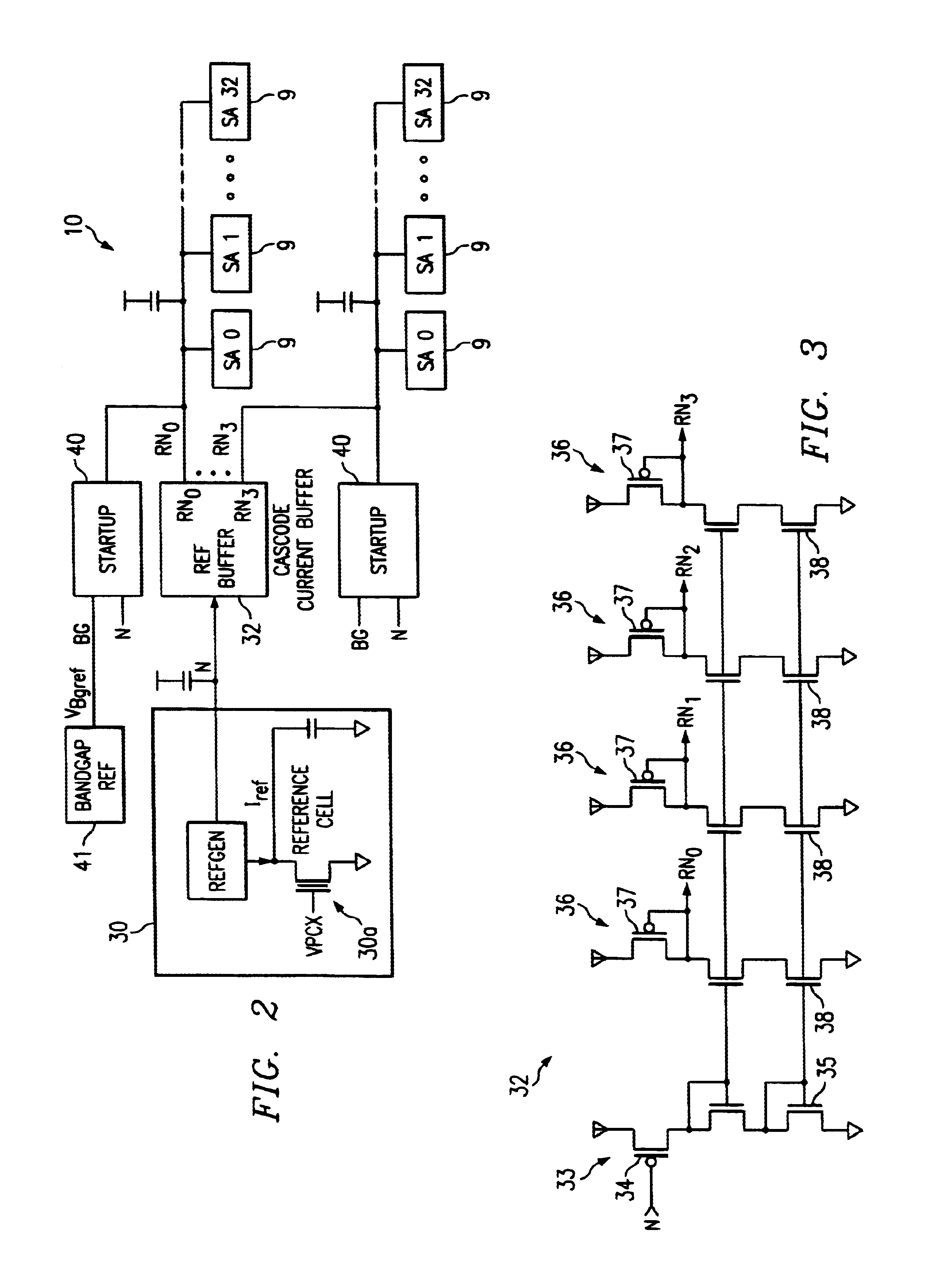

Reference generator circuit and method for nonvolatile memory devices

Reference generator circuitry for providing a reference to sense amplifiers in a flash memory device. The circuitry includes a reference current generator for generating a reference current for use by the sense amplifier circuits. A current buffer circuit in the flash memory device mirrors the reference current and applies a plurality of mirrored reference currents to the reference inputs of the sense amplifiers. A startup circuit is utilized in order to provide a fast settling time of the reference node appearing at the input of the sense amplifiers. The startup circuit includes first and second discharge current stages, with the first discharge current stage discharging the charge appearing at the reference node input of the sense amplifiers based upon a bandgap reference current. The second discharge current stage discharging the charge appearing at the reference node input of the sense amplifiers based upon the reference current. Each discharge current stage utilizes feedback to gradually decrease the rate of discharge by the discharge current stage so that the discharge current stages are disabled by the time the voltage appearing at the reference node input of the sense amplifiers reaches the desired voltage level.

Owner:STMICROELECTRONICS SRL

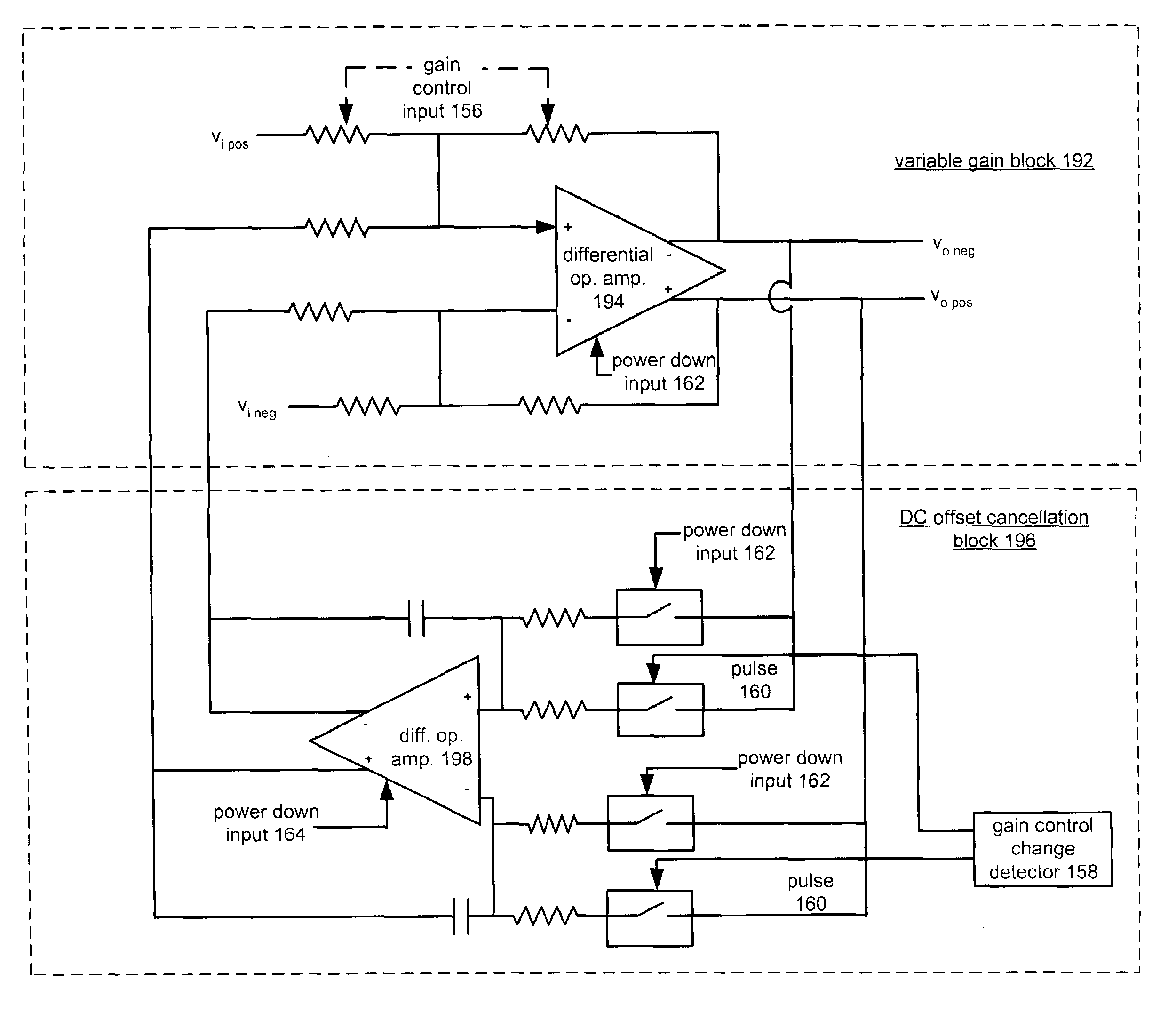

Fast settling variable gain amplifier with DC offset cancellation

ActiveUS7020449B2Minimize power consumptionReduce power consumptionEnergy efficient ICTGain controlTransceiverOffset cancellation

A variable gain amplifier includes circuit elements that may be partially powered down during transmit modes of operation and that may be powered back up whenever the radio transceiver receives a data packet within a specified settle time even for high throughput RF communications. The radio transceiver circuit may be powered down even in high throughput communications during a transmit mode to reduce power consumption. A DC offset cancellation block is operably coupled to the variable gain block to substantially remove any DC offset from the amplified output. The variable gain amplifier is further able to provide DC offset cancellation within the required settle time by holding the offset value during a dormant mode of operation. Further, the variable gain amplifier transitions from a first gain control value to a second gain control value and further modifies its internal settle time from a first value to a second value to enable the variable gain amplifier to reach a steady state within the required settle time whenever required. The settle time transitions from the second value back to the first value after a specified period of time.

Owner:AVAGO TECH INT SALES PTE LTD

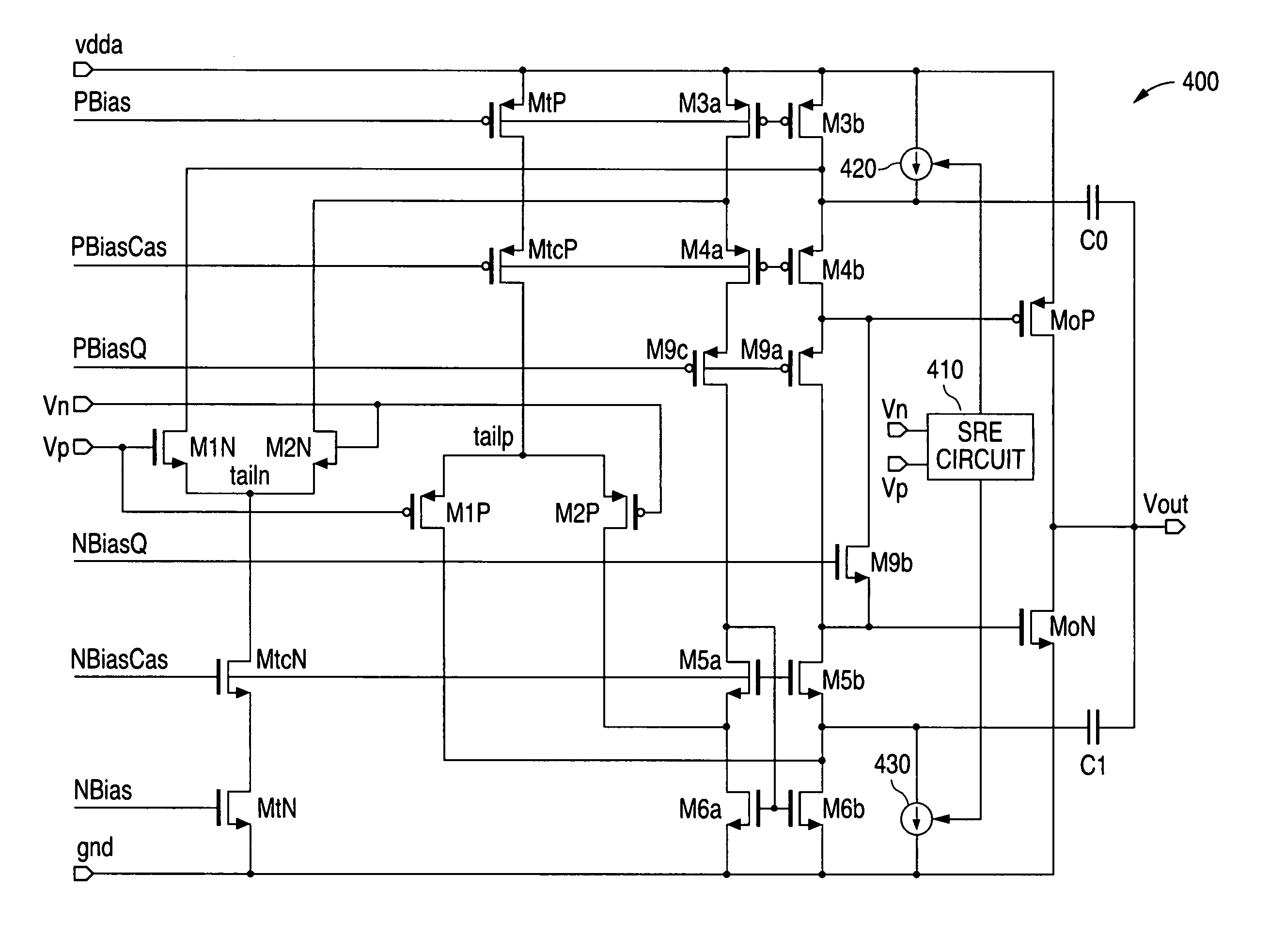

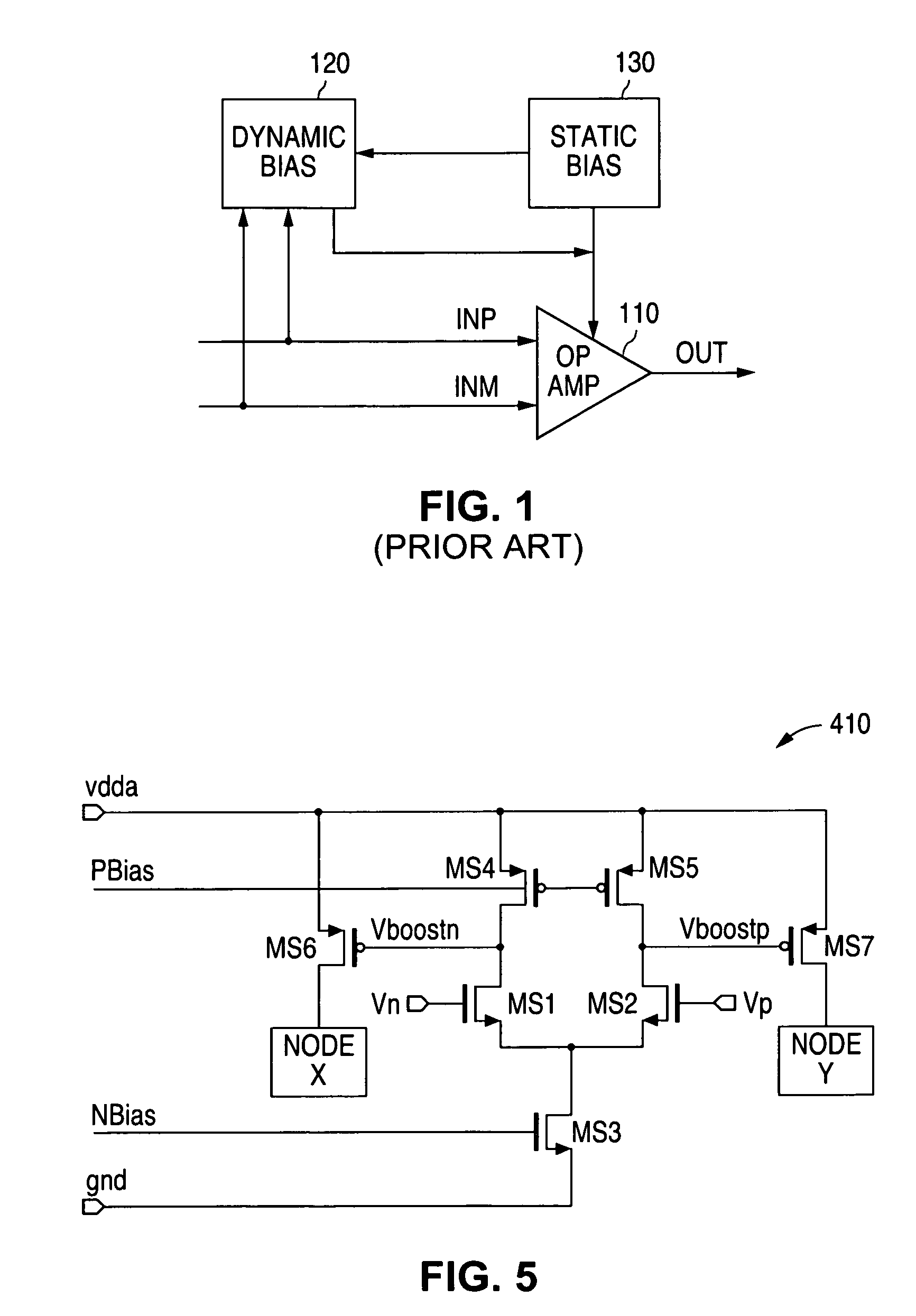

Low noise amplifier running fast at ultra low currents

ActiveUS10491167B1Lowering minimum operating power supplyReduce offsetAmplifier modifications to reduce noise influenceGain controlAudio power amplifierSlew rate

Methods, circuits, and apparatuses are disclosed that provide a buffer amplifier with lower output noise by narrow banding the amplifier. To reinvigorate the speed of the narrow-banded amplifier, a boost-on signal is initiated. The boost-on signal dynamically and rapidly injects a substantial current into the amplifier's bias current network to speed up its slew rate, when the amplifier's inputs get unbalanced when being subjected to a large transient differential input signal. Subsequently, after the amplifier regulate itself and as the amplifier's inputs approach substantial balance, a boost-off signal dynamically injects a slow and decaying current (that converges to the level of static steady-state bias current) into amplifier's bias circuitry, instead of turning off the boost current rapidly, which improves the amplifier's settling time.

Owner:FAR ALI TASDIGHI

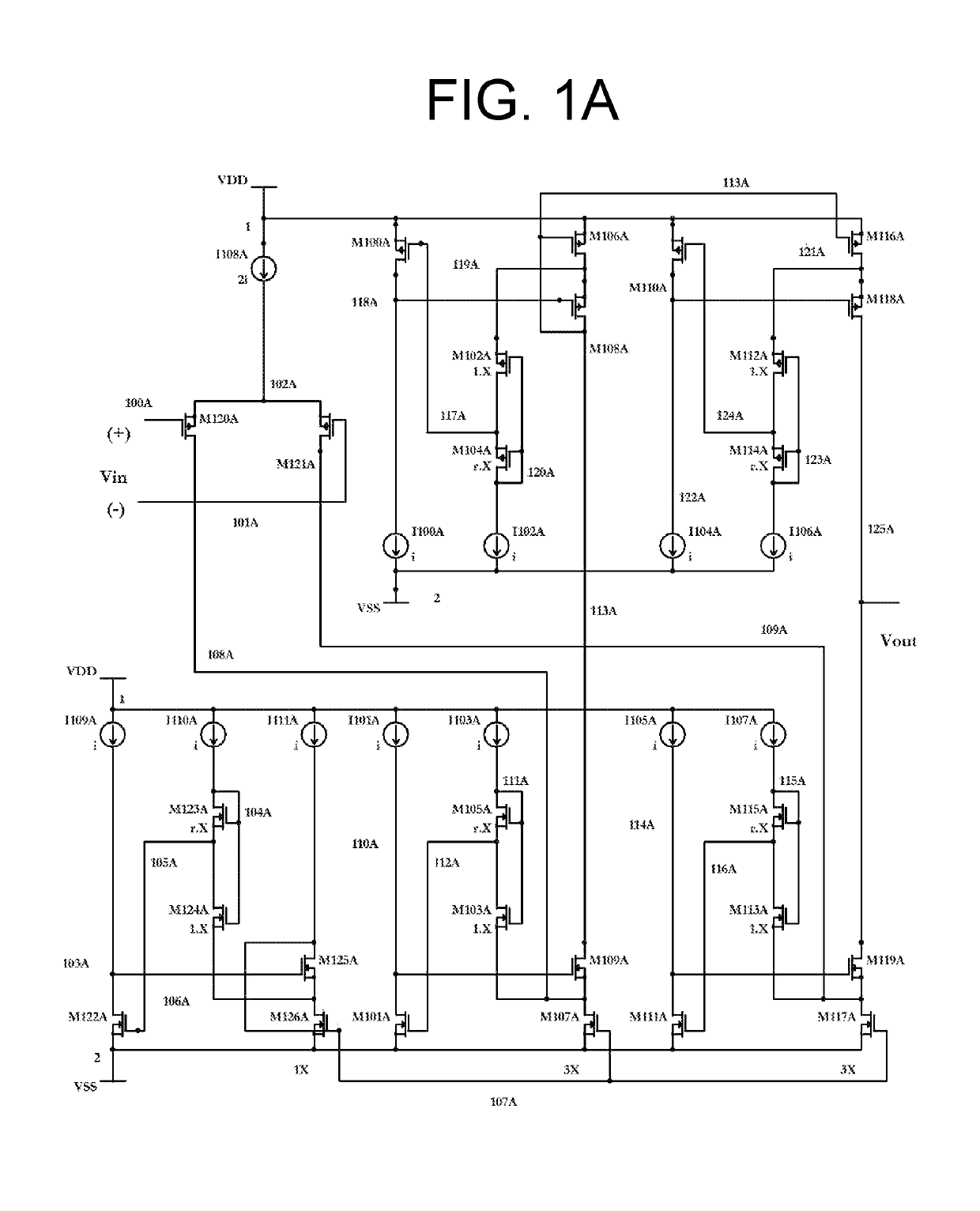

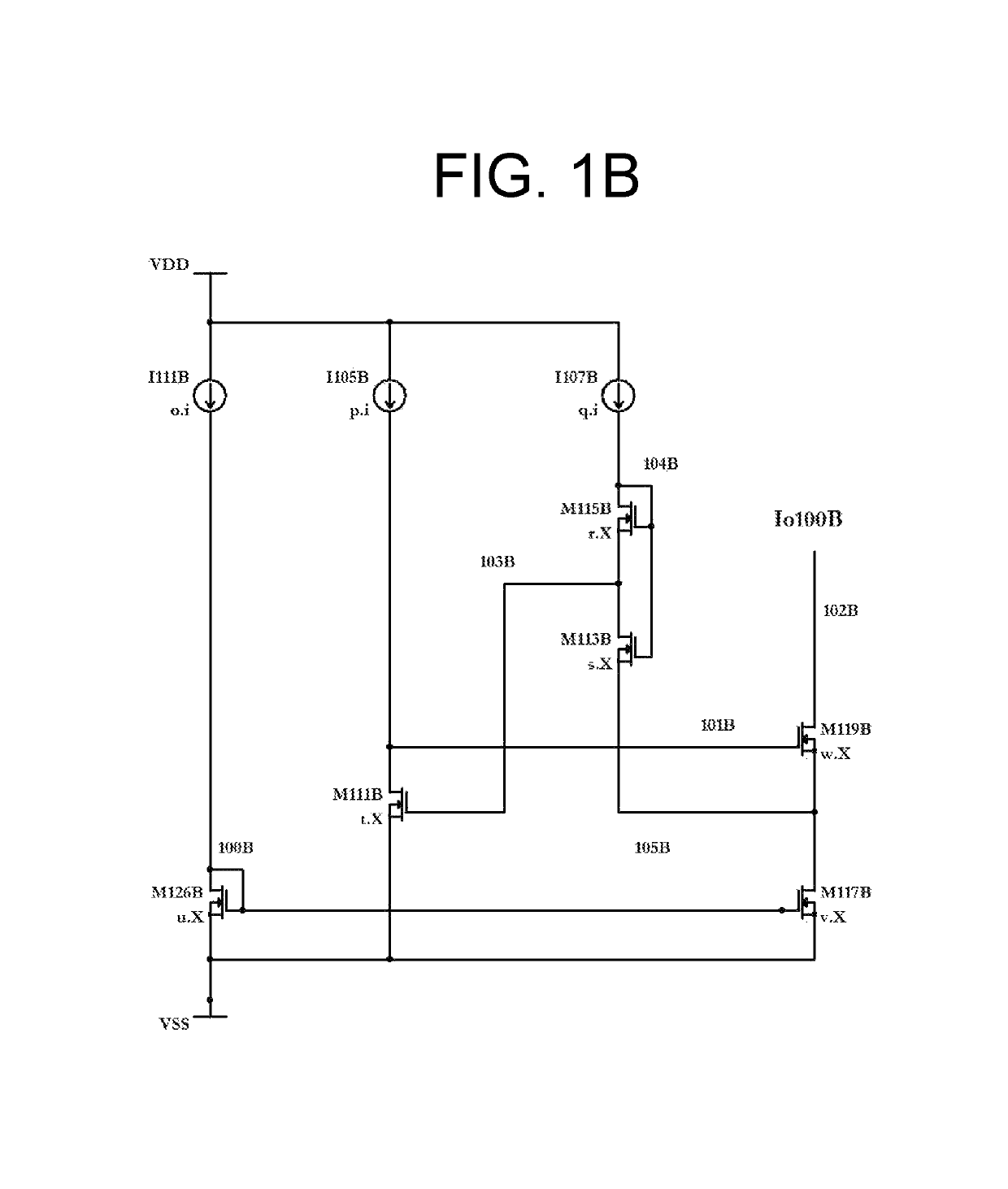

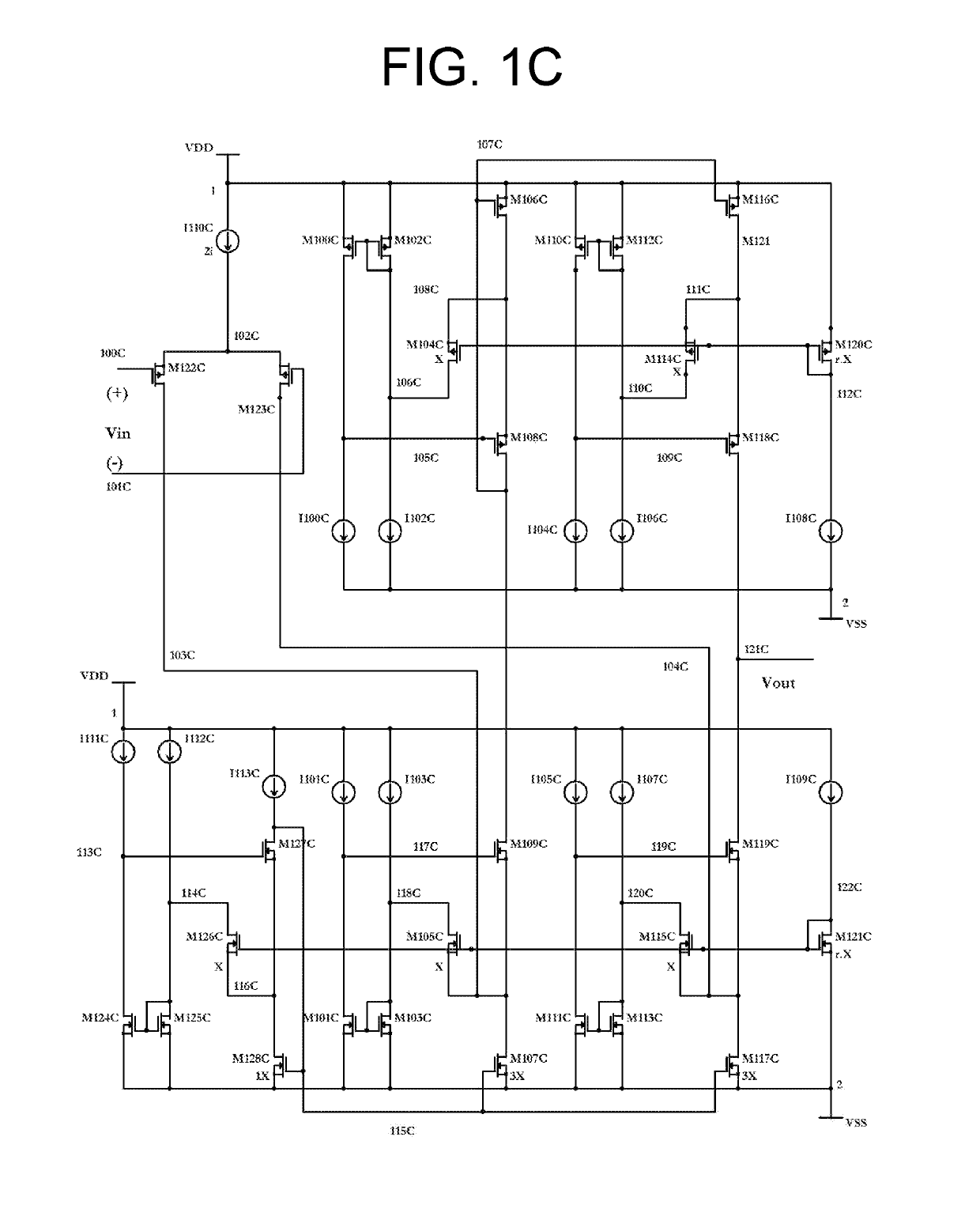

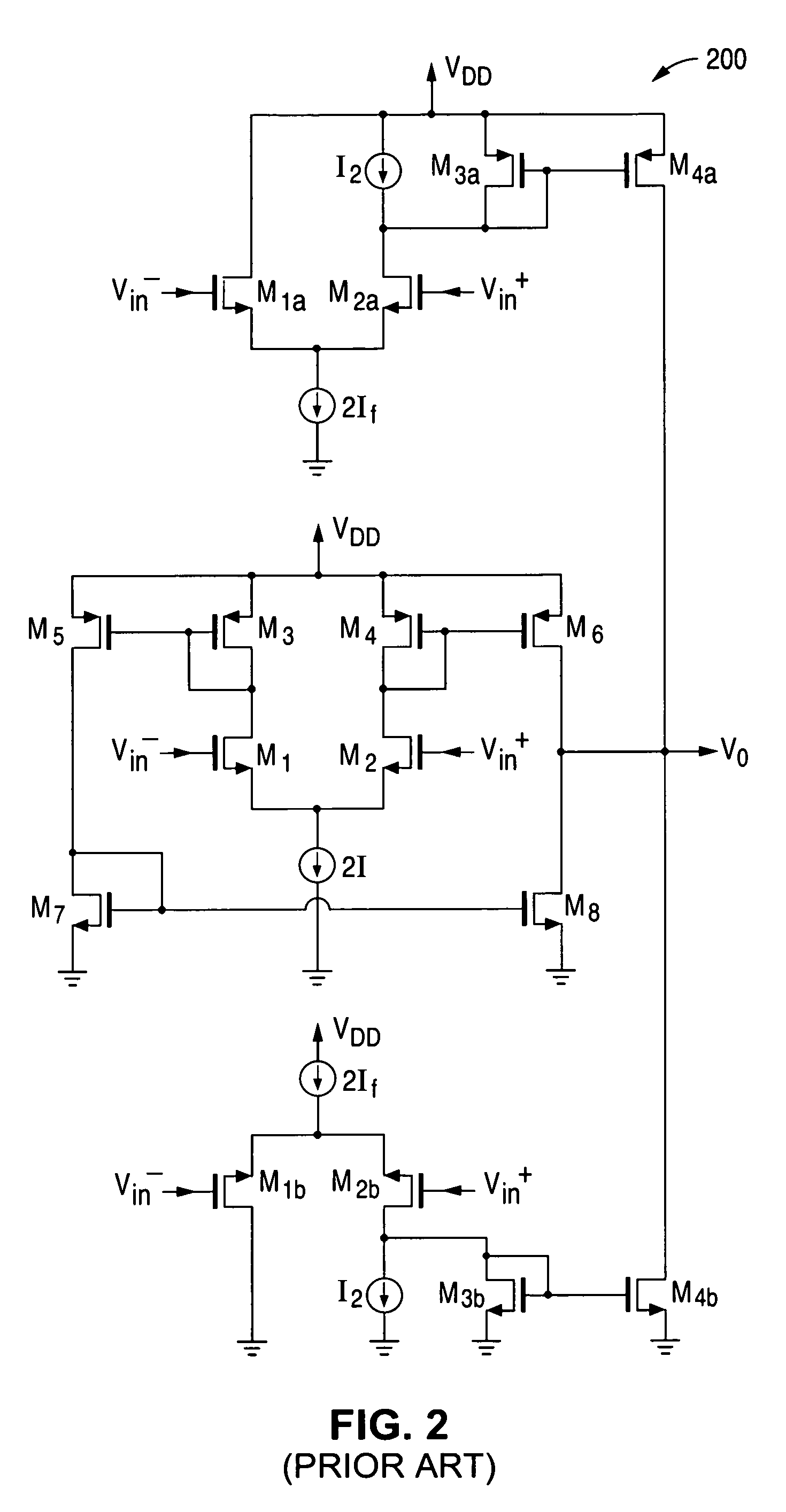

System and method for providing slew rate enhancement for two stage CMOS amplifiers

A slew rate enhancement circuit is disclosed for increasing a slew rate in a two stage CMOS amplifier. The slew rate enhancement circuit detects an input signal transition in the two stage CMOS amplifier. Depending on the polarity of the input signal transition the slew rate enhancement circuit turns on either (1) a first current source to charge a first compensation capacitor, or (2) a second current source to charge a second compensation capacitor. The slew rate enhancement circuit increases the slew rate by a factor of four to five and decreases the settling time of a voltage transition by a factor of three.

Owner:NAT SEMICON CORP