Non-volatile semiconductor memory device and multi-block erase method thereof

a memory device and non-volatile technology, applied in static storage, digital storage, instruments, etc., can solve the problems of limiting the performance of a system that includes flash memory devices, memory blocks are required to erase, and it is not easy for general users to update stored contents, etc., to achieve the effect of improving the operation of erase verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

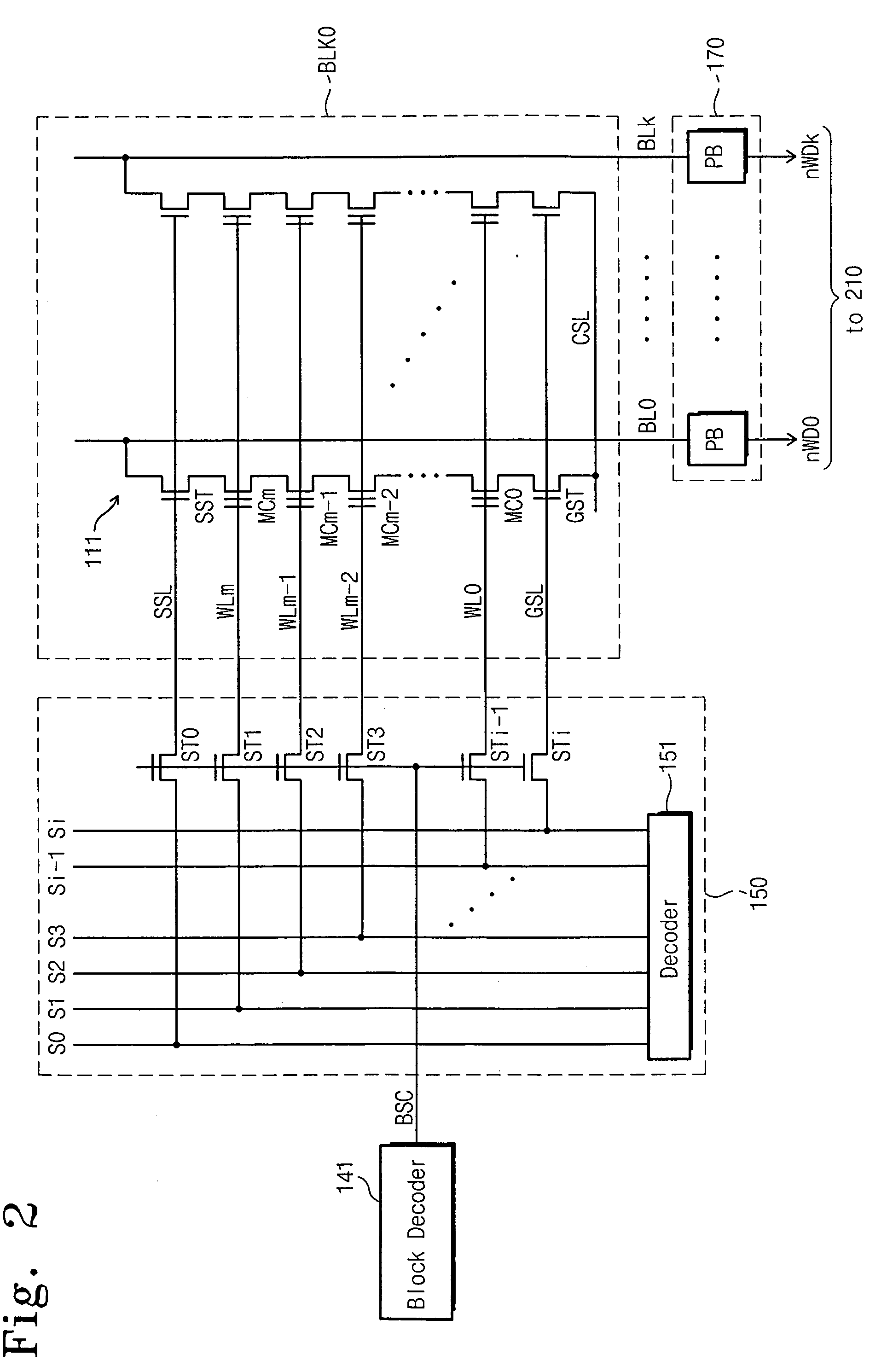

[0024]A non-volatile semiconductor memory device according to some embodiments of the invention provides a novel erase verify manner after simultaneously erasing a plurality of memory blocks. An erase verify operation of each of erased memory blocks may be carried out according to an erase verify command and a block address that are externally supplied. For example, to select a set of N erased memory blocks, N cycles of an erase command and a block address are externally provided, which will be more fully described below. Furthermore, according to some embodiments of the invention, a time required to simultaneously erase memory blocks is automatically varied according to the number of memory blocks to be erased, which will be more fully described blow.

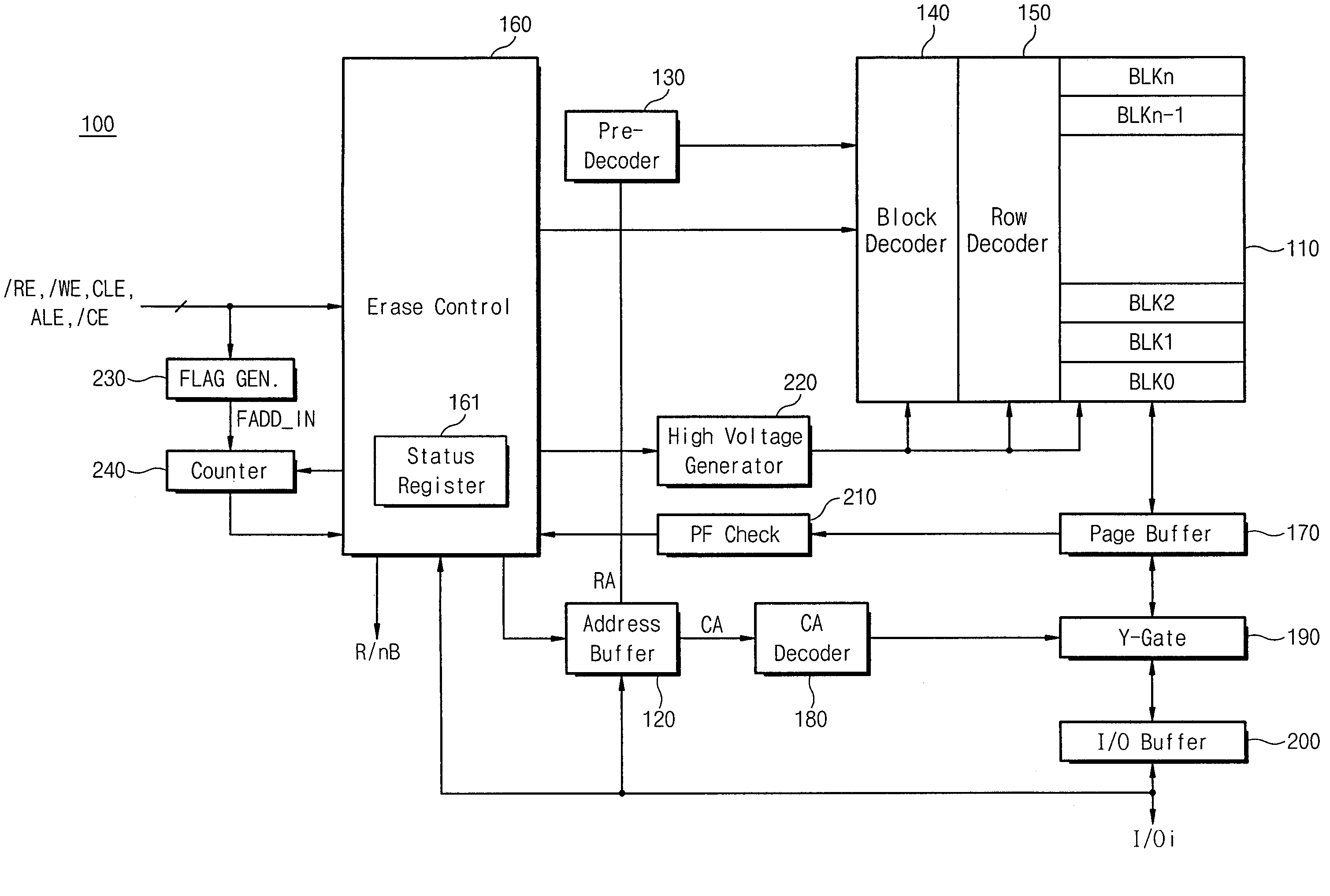

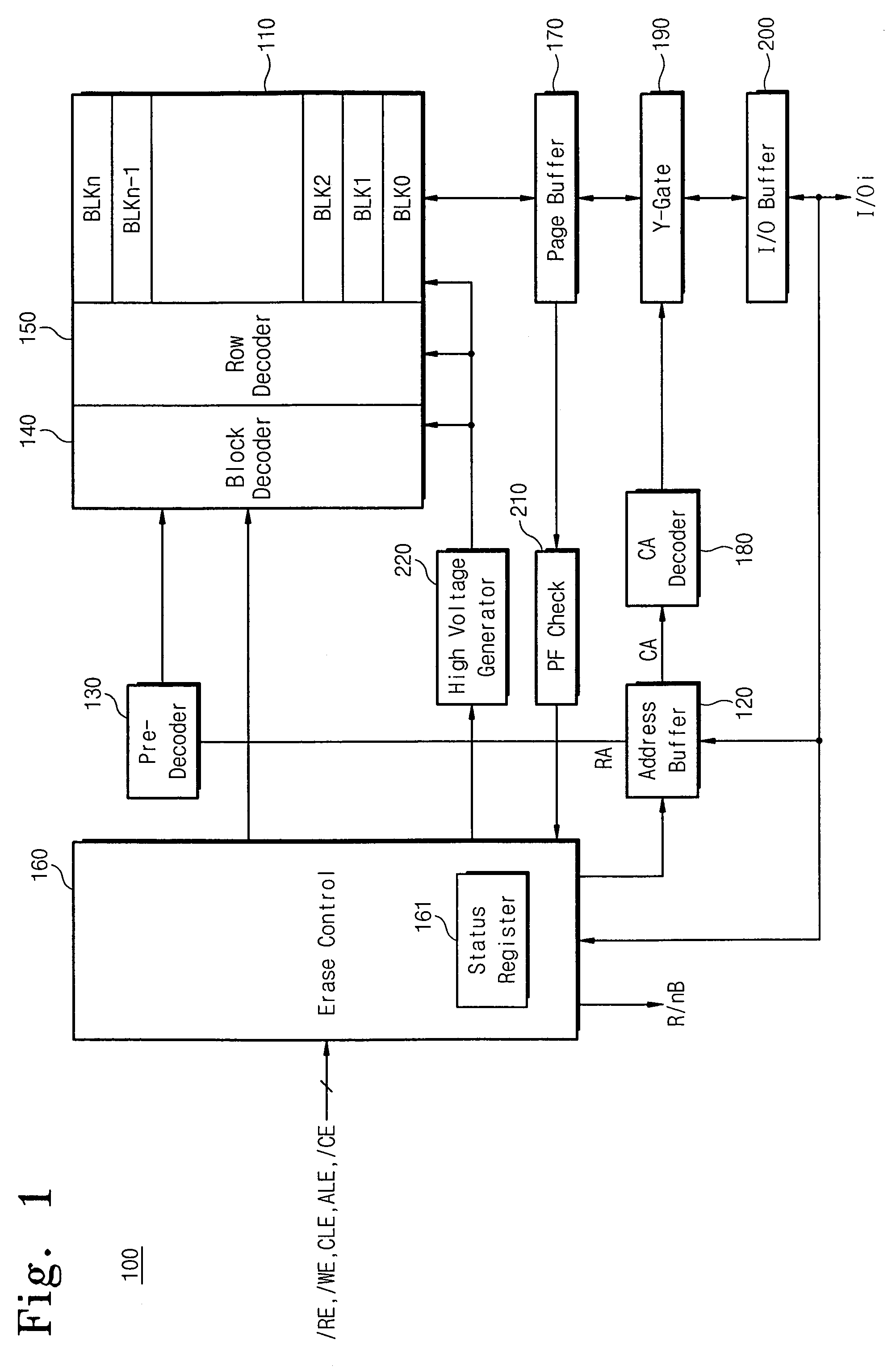

[0025]FIG. 1 is a schematic block diagram illustrating a non-volatile semiconductor memory device according to some embodiments of the invention. The non-volatile semiconductor memory device illustrated in FIG. 1 is a NAND-type flash m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More