Learning based logic diagnosis

a logic diagnosis and learning technology, applied in the field of identifying defects in semiconductor devices, can solve problems such as the inability to accurately detect and analyze faults, the failure of numerous devices to operate normally, and the difficulty of identifying and analyzing faults, etc., to achieve the effect of costly physical analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

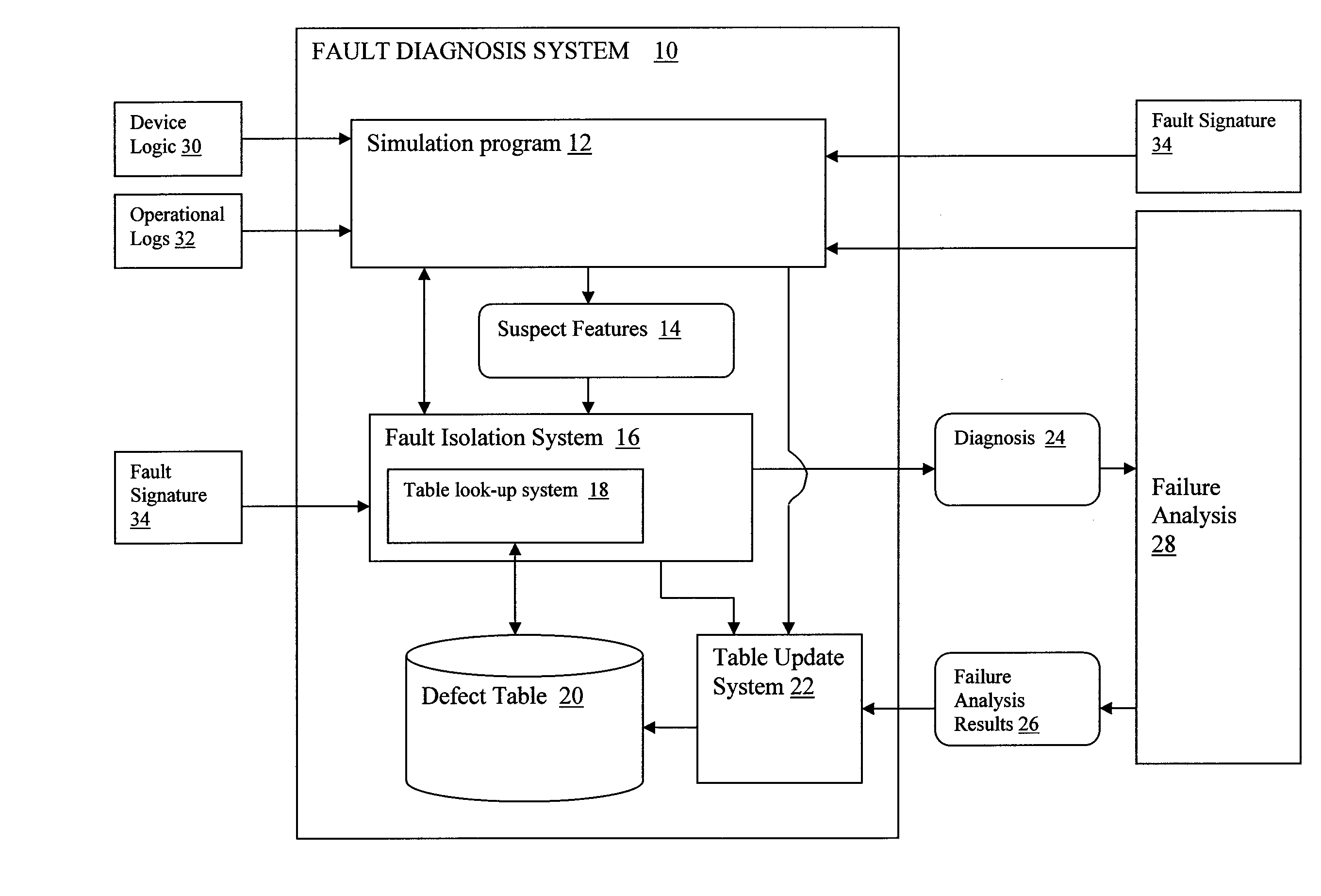

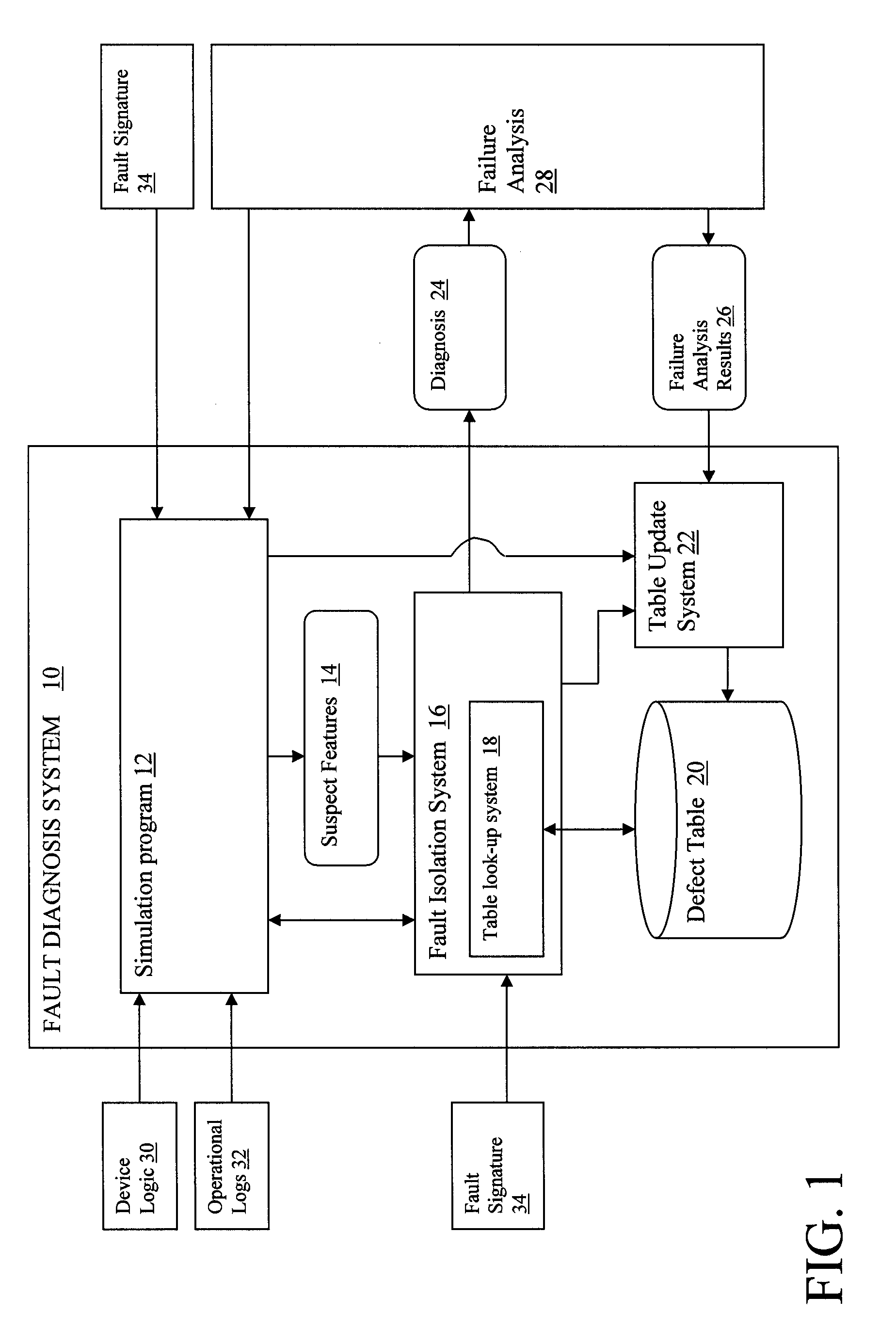

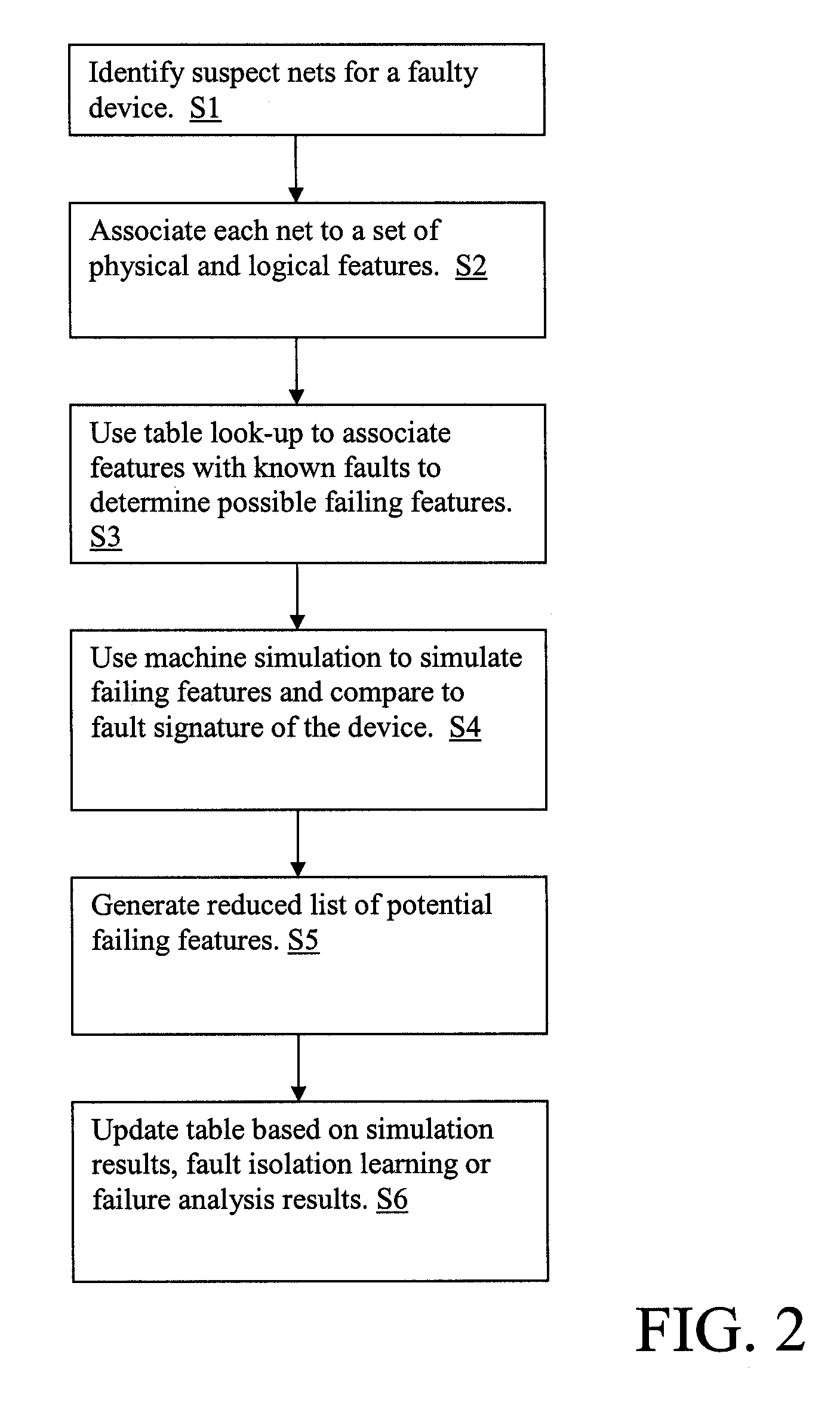

[0014]Referring now to the drawings, FIG. 1 depicts a fault diagnosis system 10 that facilitates the diagnosis of faults in an electronic device, such as an integrated circuit. Fault diagnosis system 10 utilizes an adaptive defect table 20, which includes a list of features that are associated with known failures, to facilitate the diagnosis process. The defect table 20 is utilized to help narrow down or identify one or more features that are likely to be causing a failure in a device currently being studied. For instance, defect table 20 may indicate that a particular net design is known to cause a short circuit. If the current device being analyzed includes the particular net and is exhibiting a failure that could be the result of a short circuit by that net, then the net design could be focused on as a highly likely cause of the failure.

[0015]As depicted, fault diagnosis system 10 comprises a simulation program 12 that generates a set of suspect features 14, which may cause a fai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com