Design flow for shrinking circuits having non-shrinkable IP layout

a design flow and layout technology, applied in the field of shrinking integrated circuits, can solve the problems of not being able to uniformly shrink the integrated circuit of a semiconductor chip, not being able to cost effective redesign these circuits for smaller dimensions, and circuits that were typically shrunk, etc., to achieve the effect of changing the size and location of components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017]The making and using of the presently preferred embodiments are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

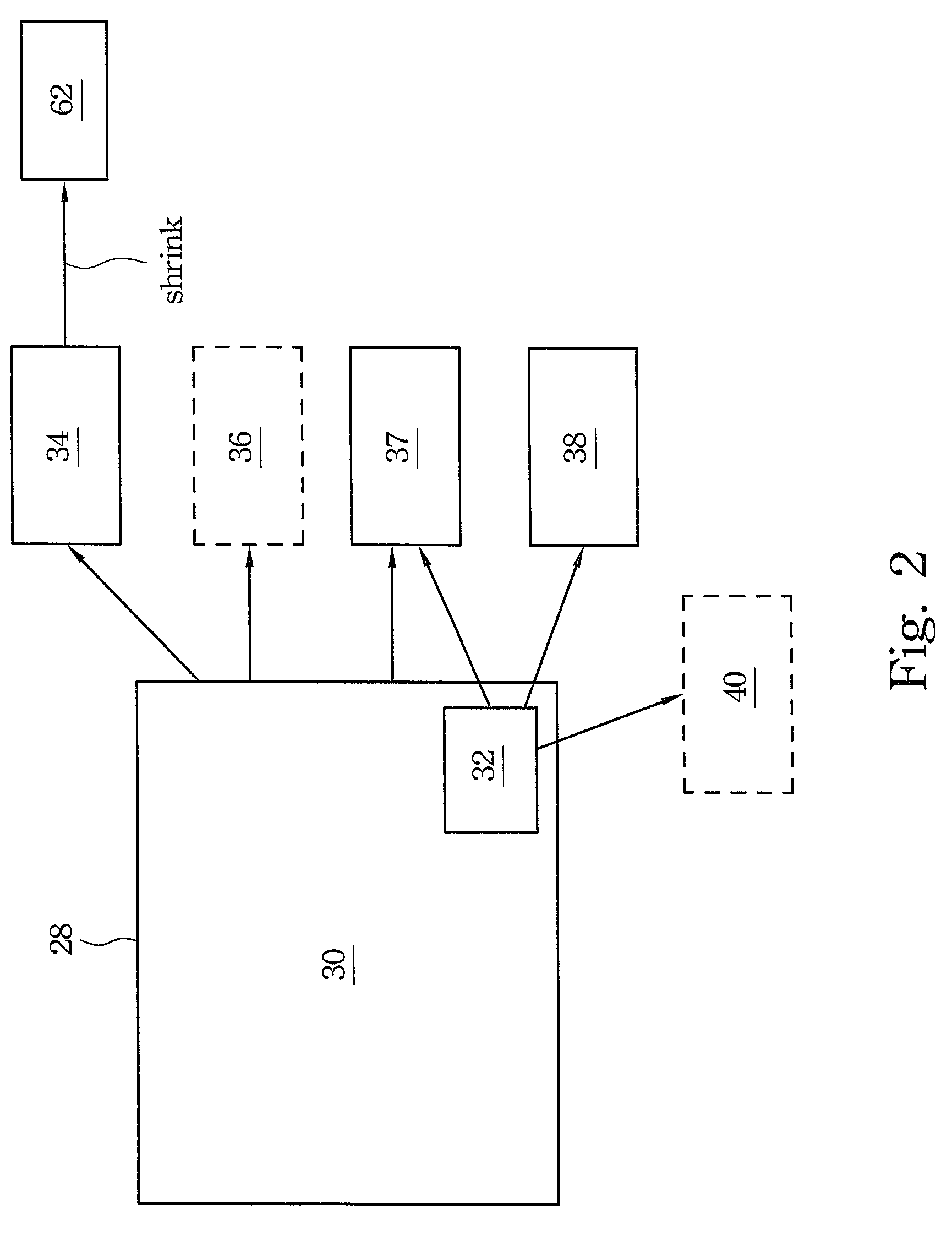

[0018]FIGS. 1 through 4 illustrate an embodiment of the present invention, in which integrated circuits designed using 45 nm scale is shrunk to 40 nm scale. It is noted that the 45 nm scale and 40 nm scale are merely examples, and the teaching of the present invention may be used for the shrinking of integrated circuits between any two technology generations.

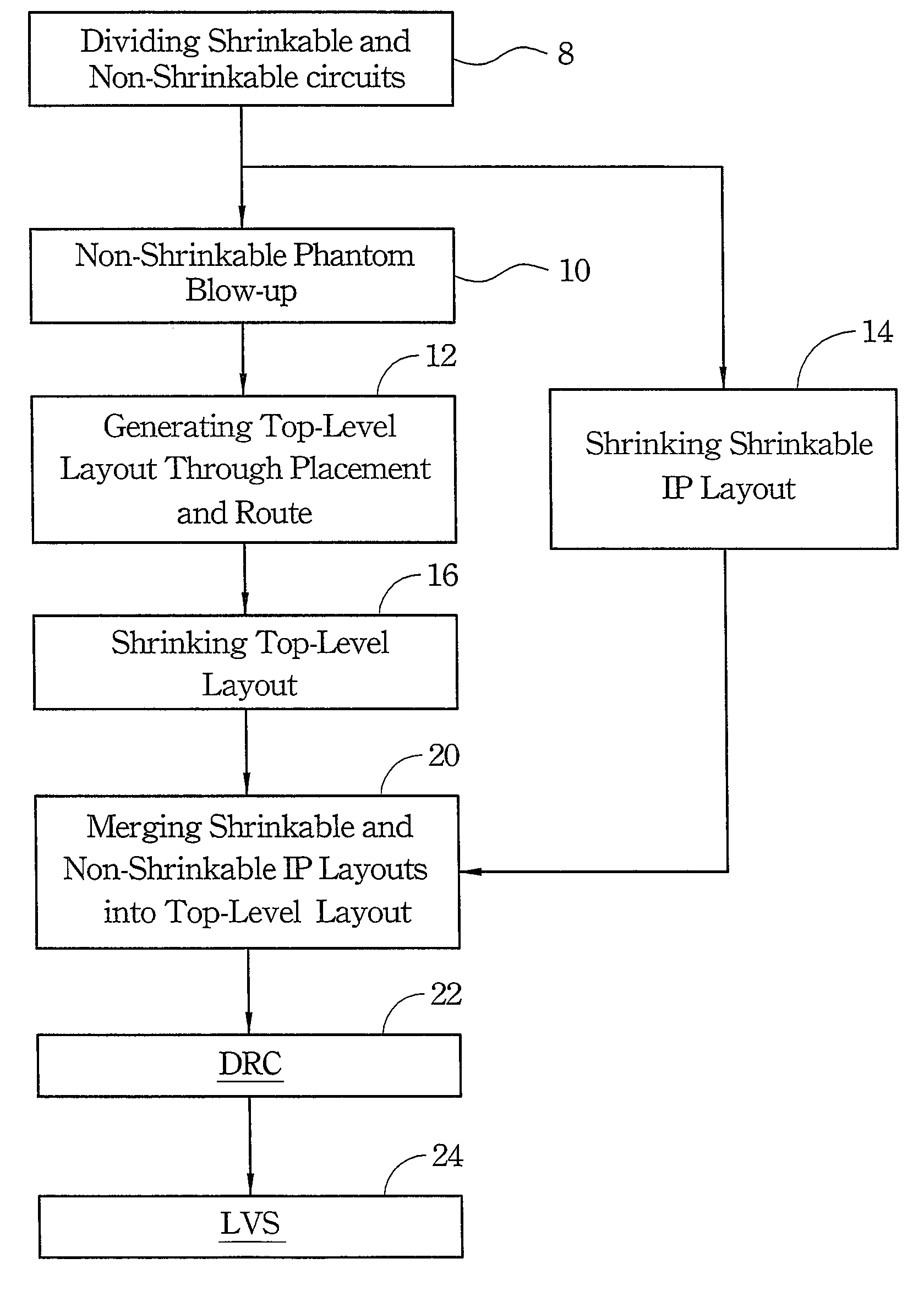

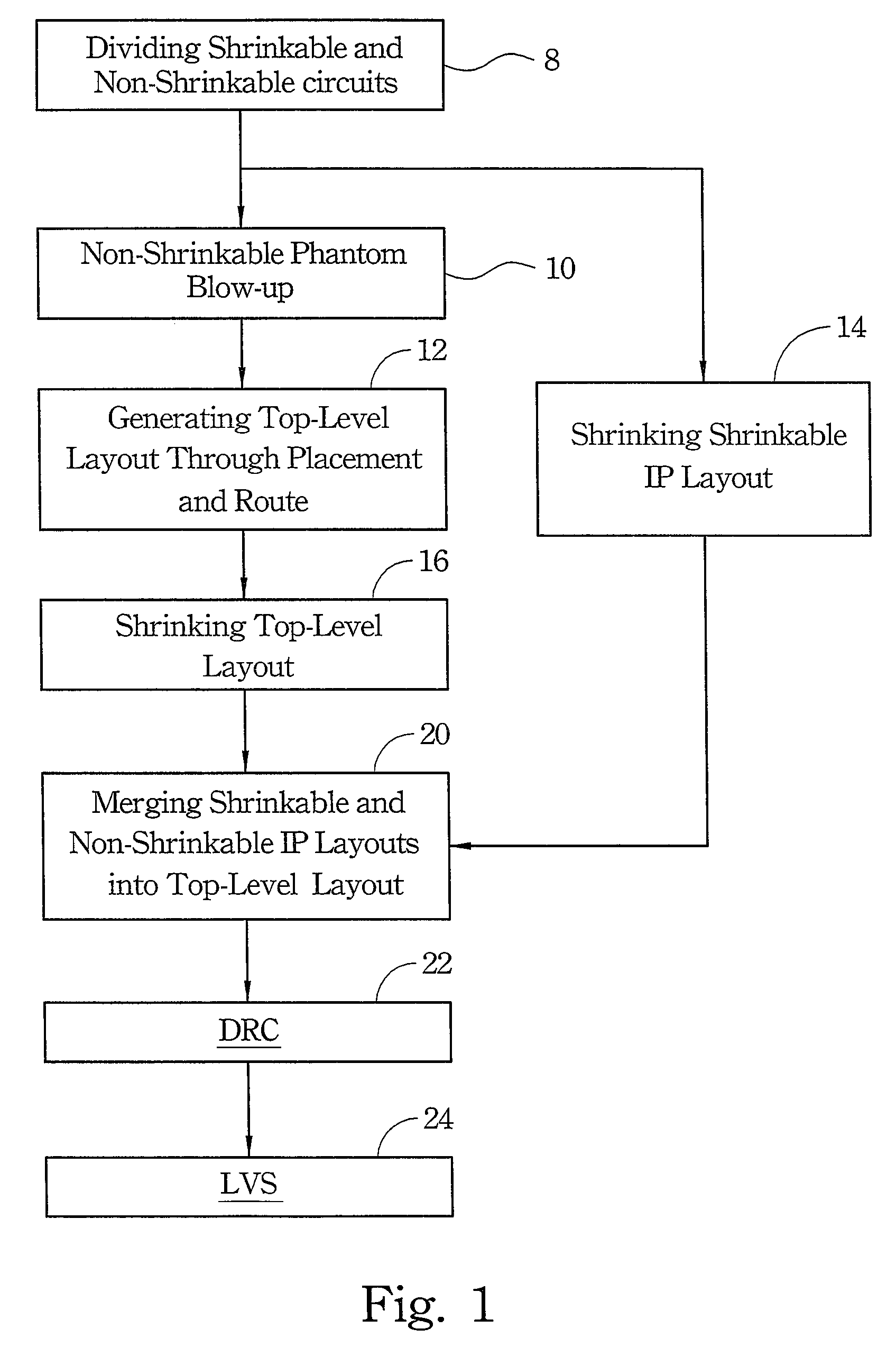

[0019]FIG. 1 illustrates an exemplary flow chart. The steps recited in the flow chart are discussed in detail in the subsequent paragraphs. For simplicity, the embodiments of the present invention recites the scale of 10 / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More