Semiconductor chip and manufacturing method thereof

a technology of semiconductor chips and manufacturing methods, applied in the field of semiconductor chips, can solve the problems of reducing the reliability of the semiconductor device manufactured, affecting the reliability affecting the quality of the semiconductor device, so as to improve the shear intensity of the indium-nickel alloy layer, improve reliability, and ensure the effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

Configuration

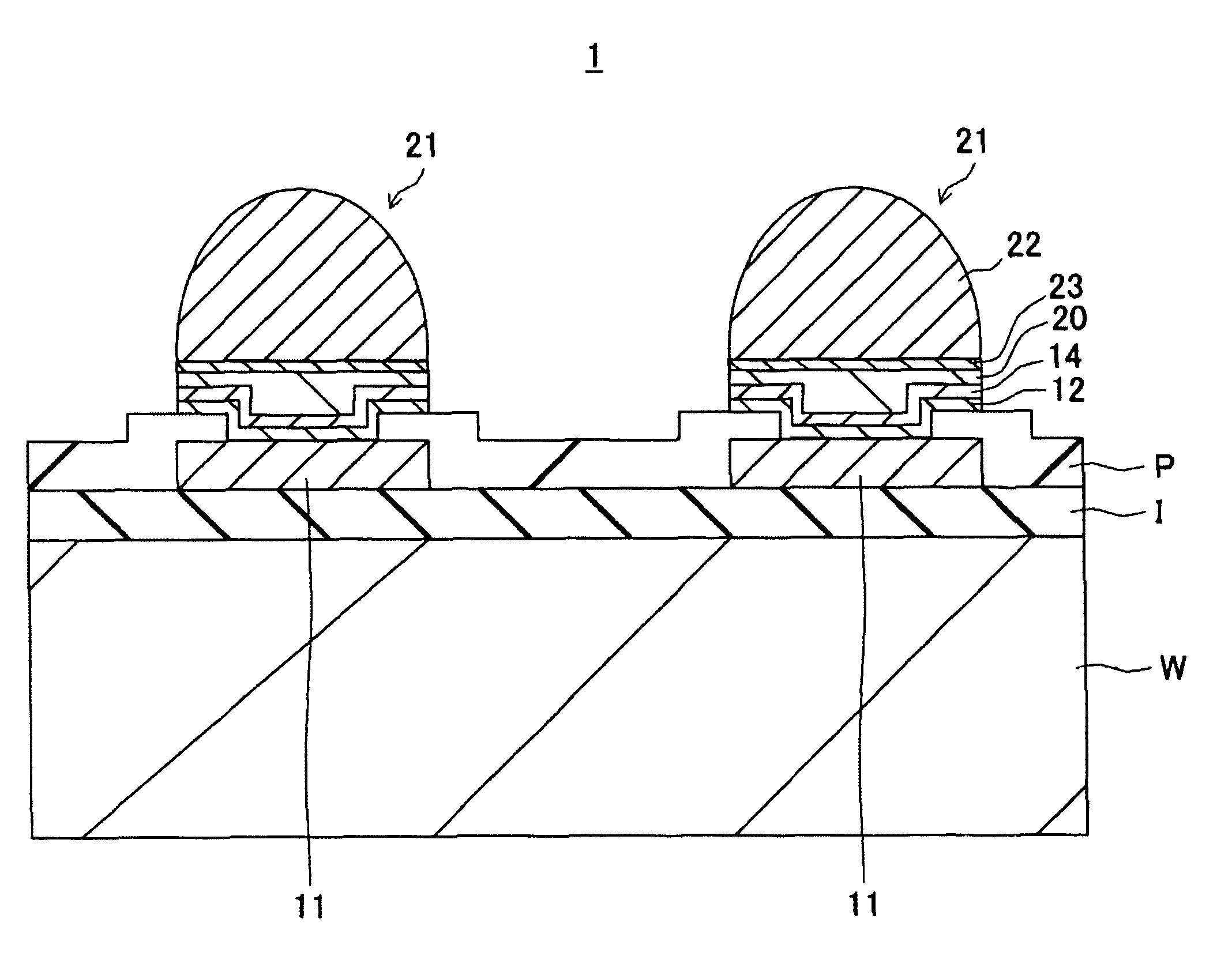

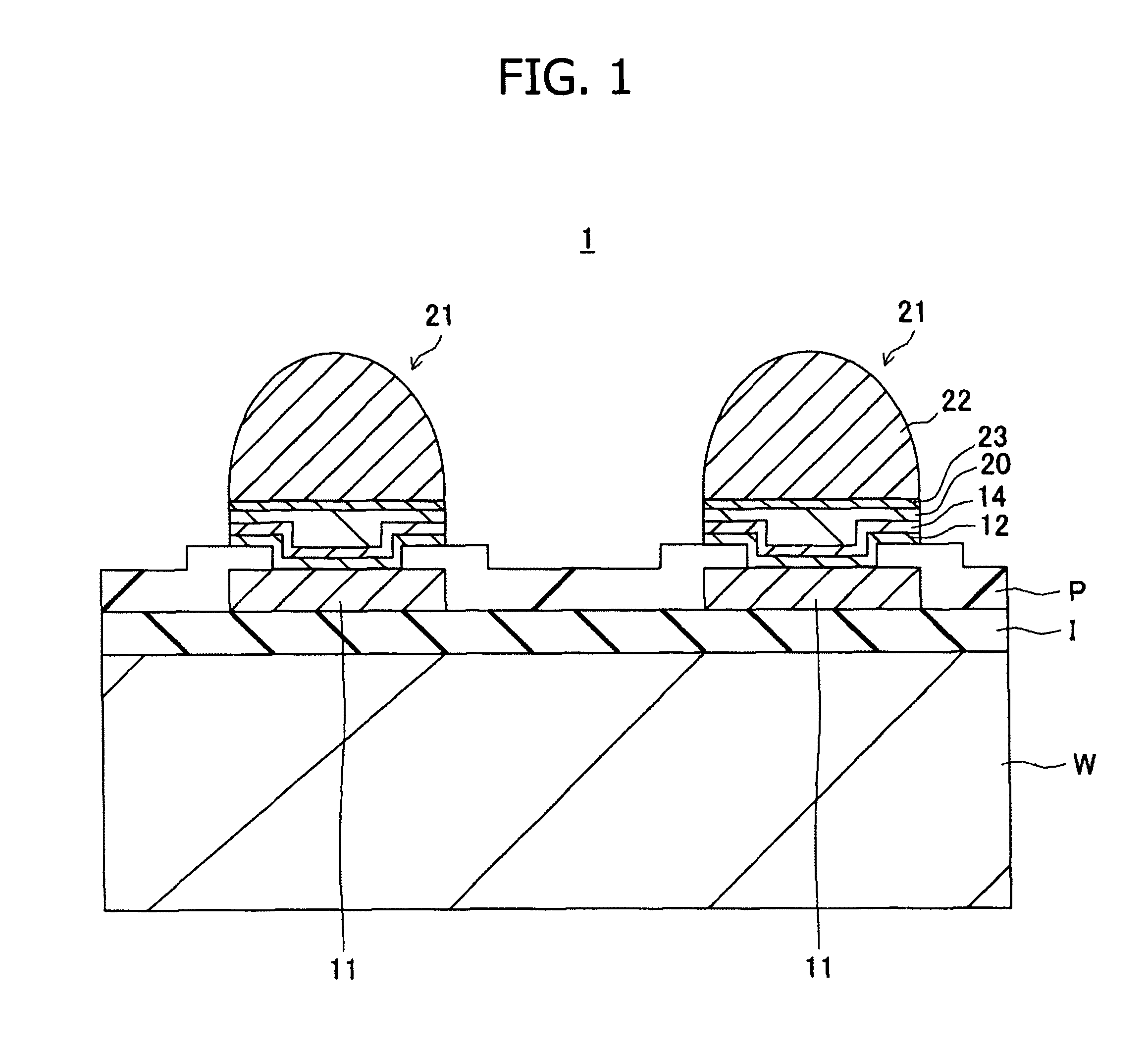

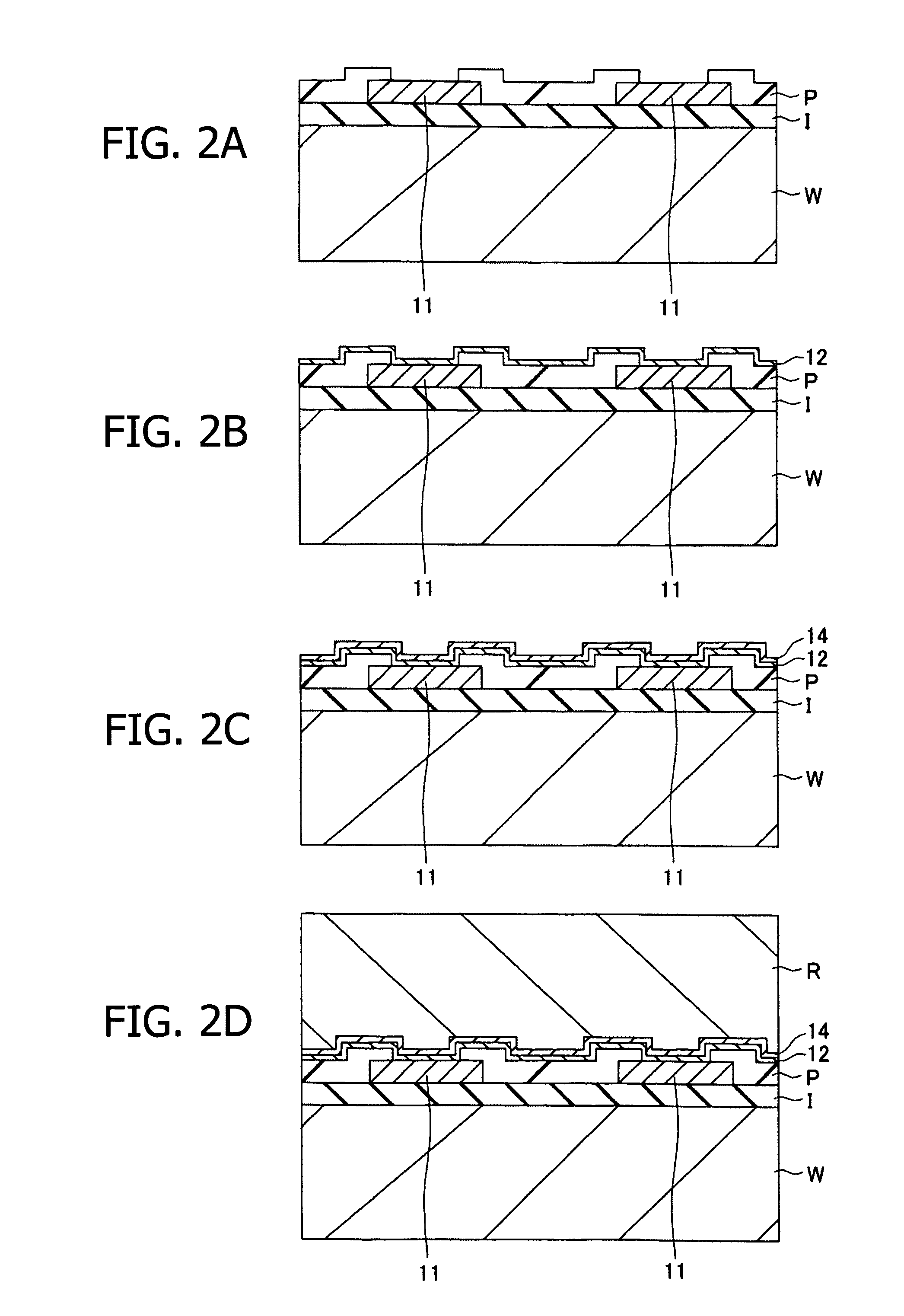

[0042]FIG. 1 is a sectional view showing parts of a semiconductor chip 1 in which a bump 21 is formed on a pad electrode 11 according to a first embodiment of the present invention.

[0043]As shown in FIG. 1, the semiconductor chip 1 has the pad electrode 11 and the bump 21, and the bump 21 is formed such that it corresponds to the pad electrode 11. A titanium layer 12 and a nickel layer 14 are sequentially laminated on the pad electrode 11 so as to cover the surface thereof. The bump 21 includes an indium layer 22 and an intermediate metal compound layer 23, composed of an indium-copper alloy layer interposed between the indium layer 22 and the nickel layer 14.

[0044]The respective components will be described sequentially.

[0045]The pad electrode 11 is made of, for example, aluminum and connected via an interlayer insulating film I to an electric circuit (not shown) formed on a wafer W of the semiconductor chip 1. As shown in FIG. 1, the surface of the pad electrode 11 is...

second embodiment

[0082]A second embodiment of the invention will be described below.

[0083]FIG. 5 is a sectional view showing parts of a semiconductor chip 1b in which a bump 21 is formed on a pad electrode 11 according to the second embodiment of the present invention.

[0084]As shown in FIG. 5, similarly to the first embodiment, the semiconductor chip 1b has the pad electrode 11 and the bump 21. Bump 21 is formed correspondingly to the pad electrode 11. A titanium layer 12, a copper layer 13, and a nickel layer 14 are sequentially laminated on the pad electrode 11 so as to cover the surface thereof. The bump 21 includes an indium layer 22, and an intermediate metal compound layer 23 is interposed between the indium layer 22 and the nickel layer 14.

[0085]In the semiconductor chip 1b of the second embodiment, the copper layer 13 underlies the nickel layer 14, and the nickel layer 14 has a thickness different from that in the first embodiment. Also, the intermediate metal compound layer 23 has a composi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thick | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More