Memory cell

a memory cell and cell technology, applied in the field of memory cells, can solve the problems of difficult application of resistance change elements, and achieve the effect of stable erasing resistance independent of repetition ra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

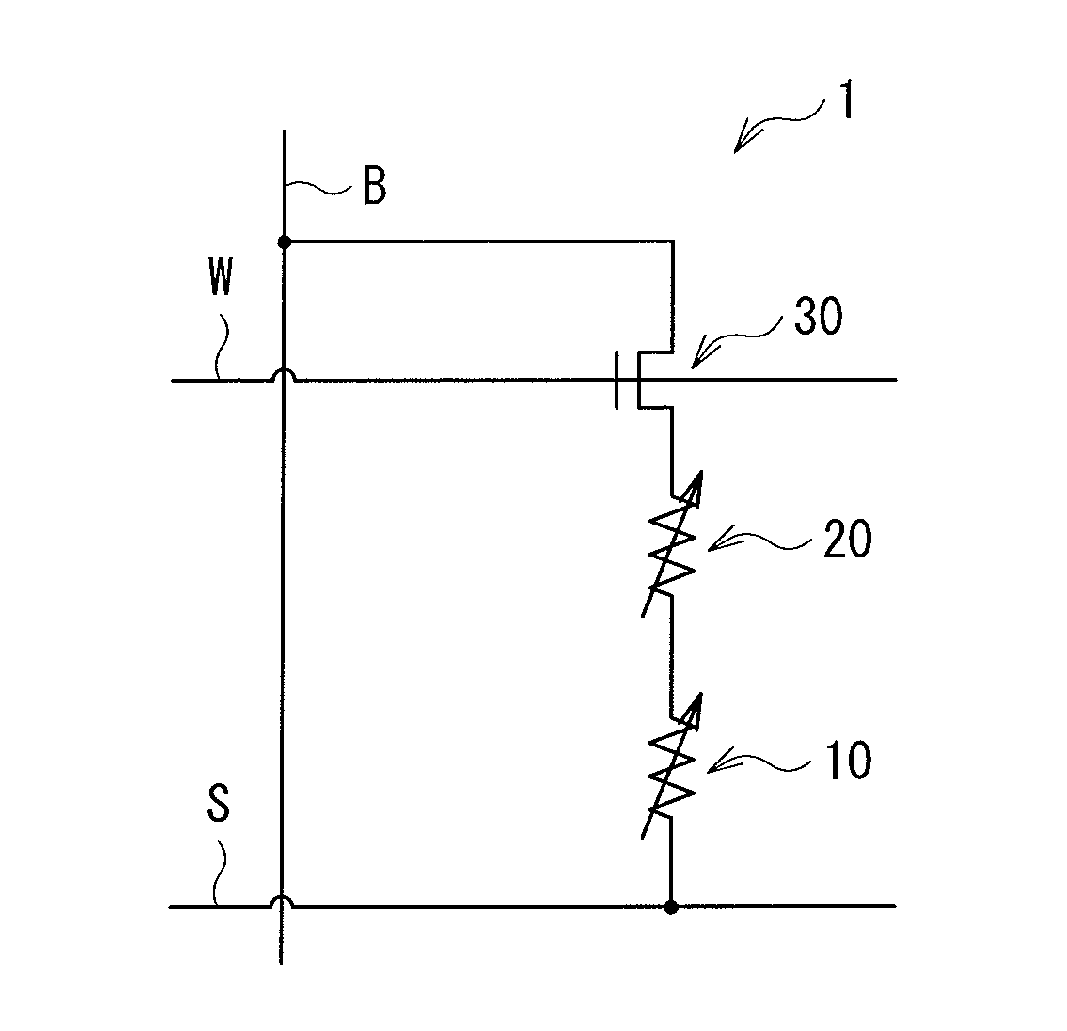

[0054]A storage device according to a first embodiment of the invention includes memory cells 1 arranged in matrix as storage units. FIG. 1 shows the memory cell 1 of the storage device in an enlarged manner. The memory cell 1 is formed by connecting a storage element 10, a nonlinear resistance element 20, and an MOS (Metal Oxide Semiconductor) transistor 30 in series.

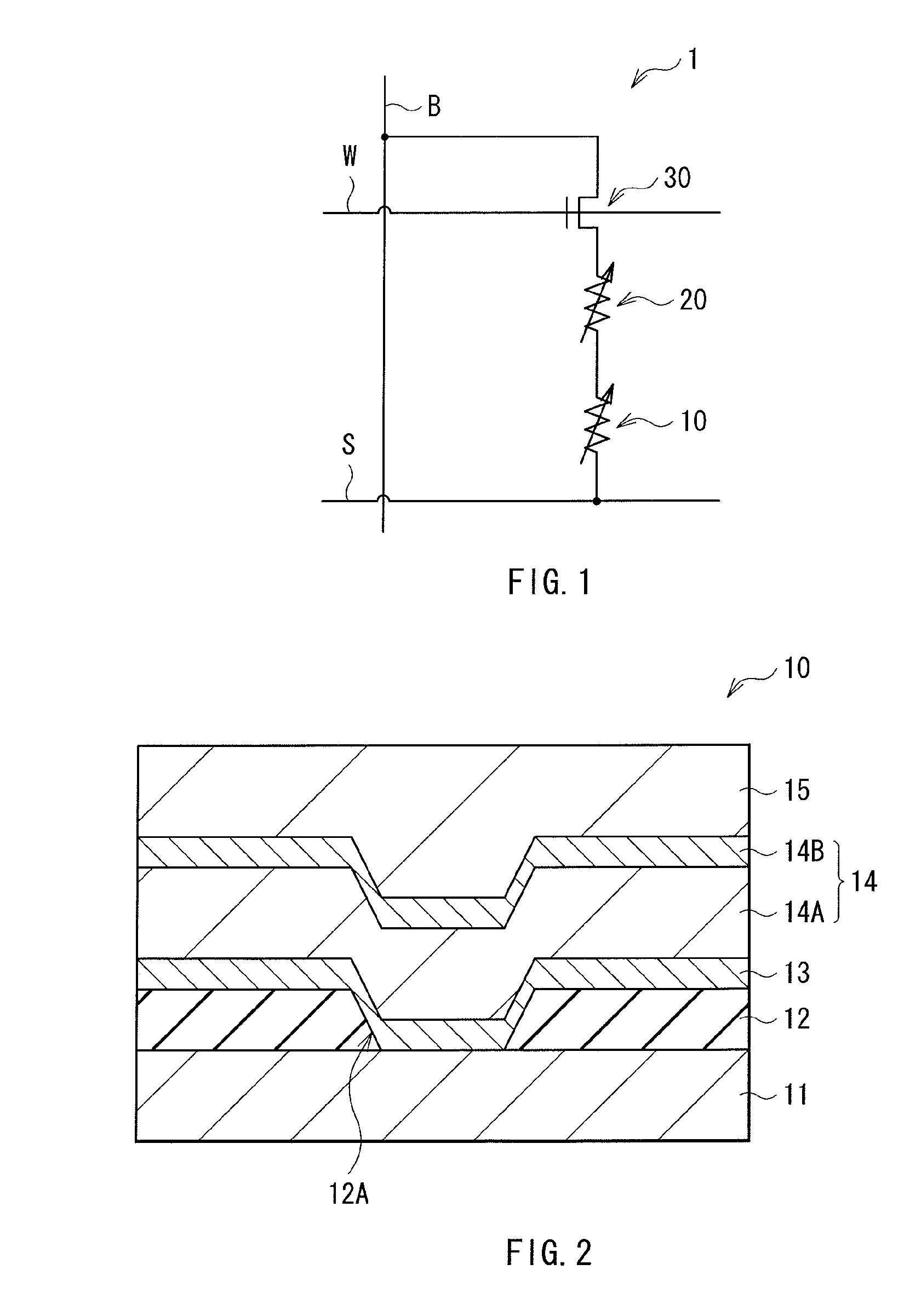

[0055]FIG. 2 shows an example of a sectional configuration of the storage element 10. The storage element 10 is formed by stacking an electrode 11, an interlayer insulating film 12, a resistance change layer 13, an ion source layer 14, and an electrode 15 in this order. The electrode 11 is electrically connected to a source line S, and the electrode 15 is electrically connected to a drain (not shown) of the MOS transistor 30 via the nonlinear resistance element 20. A source (not shown) of the MOS transistor 30 is electrically connected to a bit line B, and a gate (not shown) of the MOS transistor 30 is electrically con...

second embodiment

[0075]A storage device according to a second embodiment of the invention includes memory cells 2 arranged in matrix as storage units. FIG. 7 shows the memory cell 2 of the storage device in an enlarged manner. The memory cell 2 is formed by connecting a storage element 40 and an MOS transistor 30 in series. FIG. 8 shows an example of a sectional configuration of the storage element 40. The storage element 40 is formed by stacking an electrode 11, a voltage control film 41, a resistance change layer 13, an ion source layer 14, and an electrode 15 in this order. That is, the memory cell 2 corresponds to the memory cell 1 of the first embodiment in which the nonlinear resistance element 20 is removed from the memory cell 1, and the interlayer insulating film 12 is replaced by the voltage control film 41 in the storage element 10 of the first embodiment.

[0076]As shown in FIG. 8, the voltage control film 41 has an opening 41A running through the voltage control film 41, and is contacted ...

example of second embodiment

[0083]FIG. 9 shows a schematic configuration of an apparatus where the memory cell 2 of the second embodiment has a switch element 50 on a bit line B, and has an ammeter 60 in parallel with the switch element 50. In the example, resistance distribution in the memory cell 2 was measured using the apparatus. At that time, the voltage control film 41 was configured of SiWN, and a Si / W ratio of SiWN was appropriately adjusted so that a resistance value of the voltage control film 41 was 1 MΩ. In addition, resistance distribution in the memory cell 2 was measured using various voltage waveforms (a bit line voltage VB, a word line voltage VW, and a source line voltage VS) shown in (A) to (C) of FIG. 10.

[0084]In a writing cycle, the bit line voltage VB was changed from V1 (3 V) to zero V, the word line voltage VW was changed from zero V to V2 (1.3 V), and the source line voltage VS was kept to V3 (3 V) while pulse width of the bit line voltage VB was 10 μsec. In an erasing cycle, the bit l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More