Method for realizing SDRAM compatible design

A row address and column address technology, applied in the field of address multiplexing logic and SDRAM implementation compatibility, to achieve the effect of convenient logic implementation and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

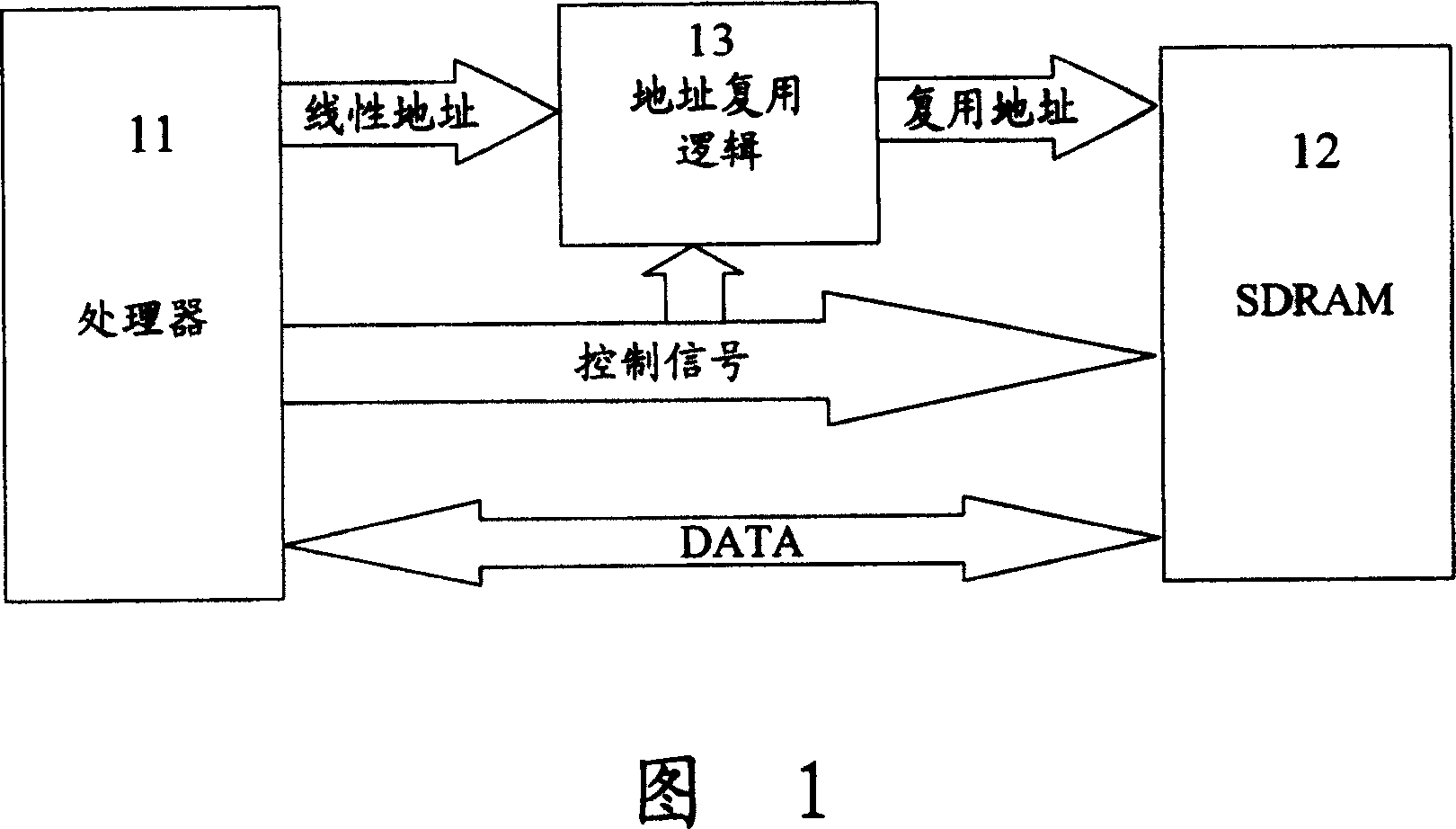

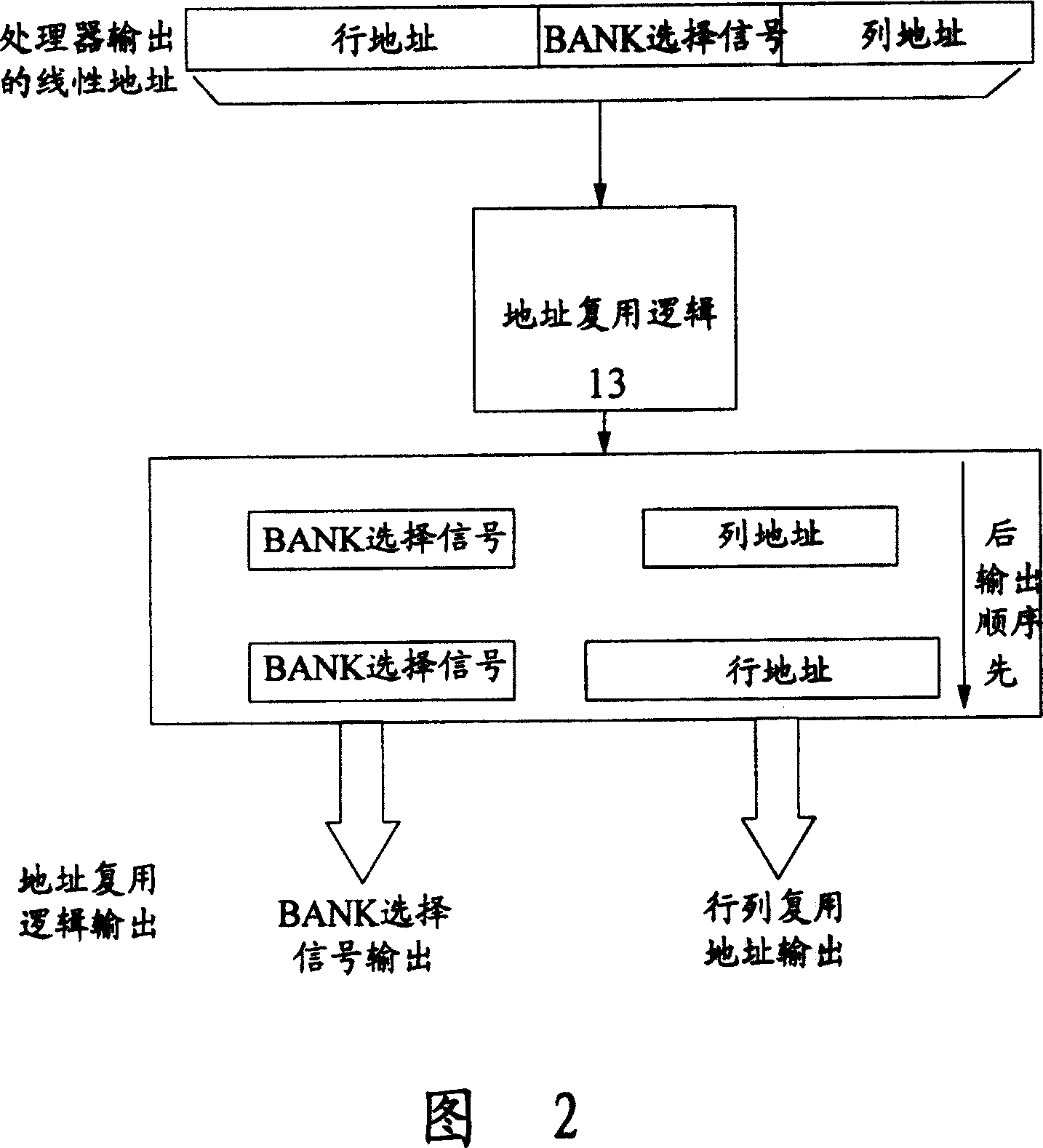

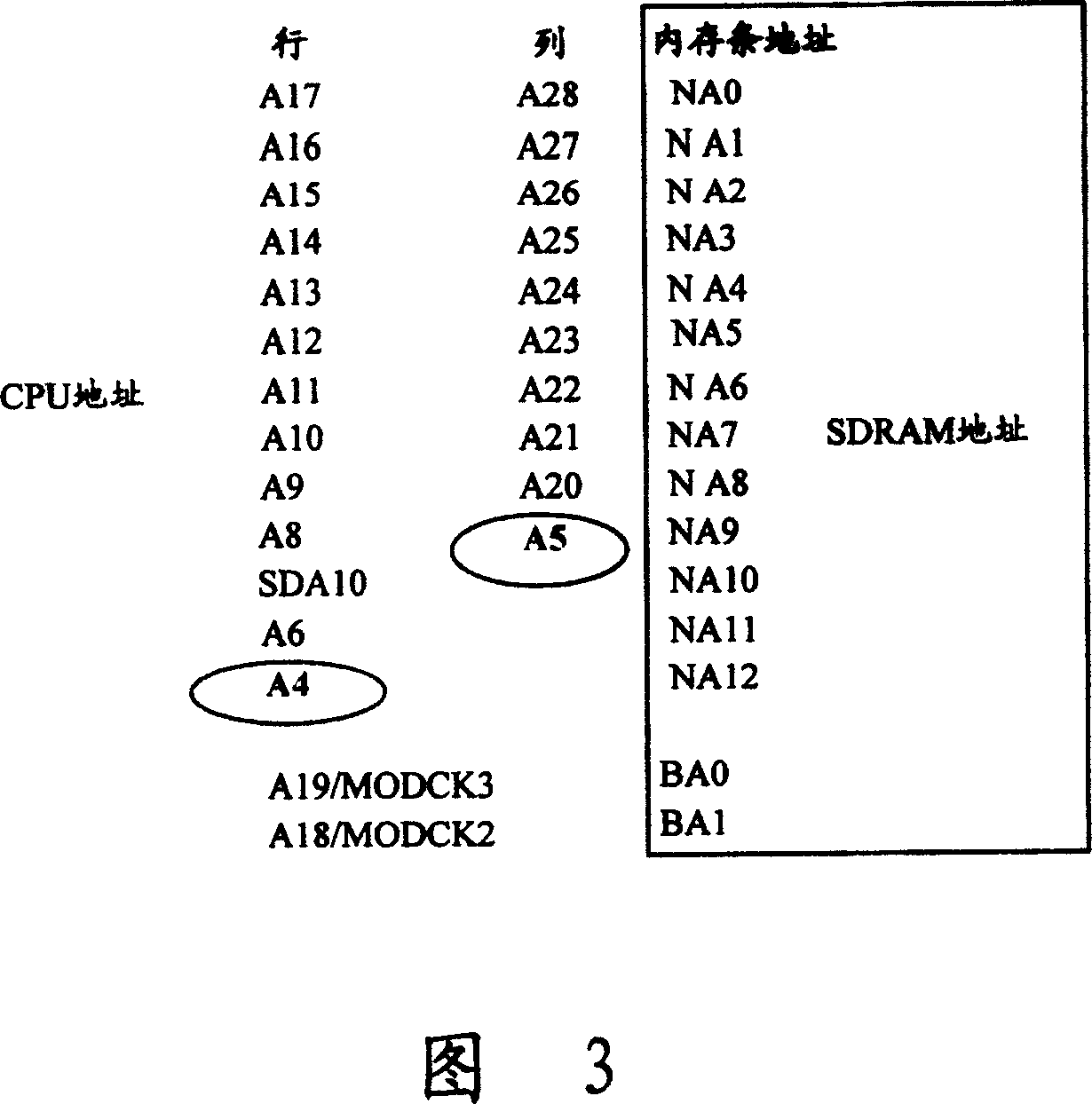

[0025] The technical scheme of the present invention realizes compatibility with SDRAM by adopting the method of row and column address conversion. In the case of an increase in the column address, the processor CPU can increase the row address, and the address multiplexing logic unit converts the row address into a column address, so as to be compatible with SDRAMs of different specifications.

[0026] At present, the development trend of SDRAM has undergone specification changes from 12 rows × 9 columns to 12 rows × 10 columns and then to 13 rows × 10 columns. It can be seen that the row and column addresses have an increasing trend. If it is just a simple increase of the row address, the compatible design of the address multiplexing logic unit can be realized more conveniently, but it is more difficult to realize the increase of the column address, because the increase of the column address will involve the position change of the row address and the bank selection signal. I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More