Method for generating solid memory address configuration

A technology of address configuration and memory lines, applied in static memory, memory address/allocation/relocation, read-only memory, etc., can solve problems such as large physical size, low storage capacity, and poor strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

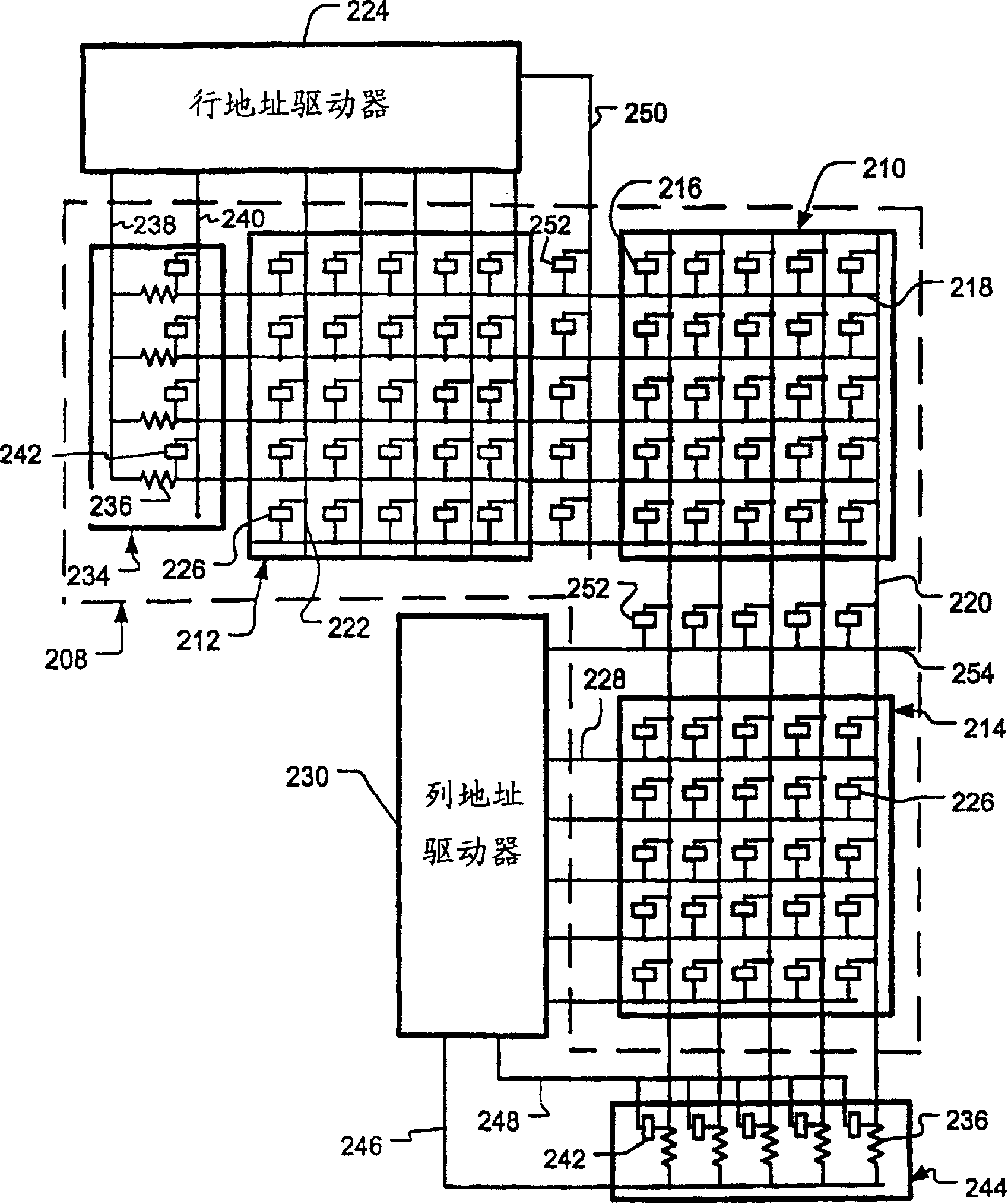

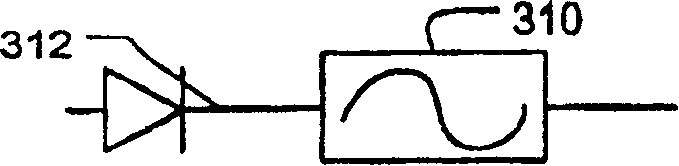

[0021] As shown in the drawings for illustrative purposes, the present invention is implemented in a diode-based OTP memory device. In the following paragraphs, the structure of the OTP storage device will be described, followed by the description of the two address protocols. An address protocol can provide fault-tolerant address configuration. Another address protocol may provide neighborhood disjoint address configuration as well as fault tolerant address configuration. Fault-tolerant address logic can improve manufacturing yields, and neighborhood-disjoint address logic allows memory devices to be formed at high resolution. Following the description of the address protocol is a description of a method of using look-up tables to extend address configuration to large storage arrays.

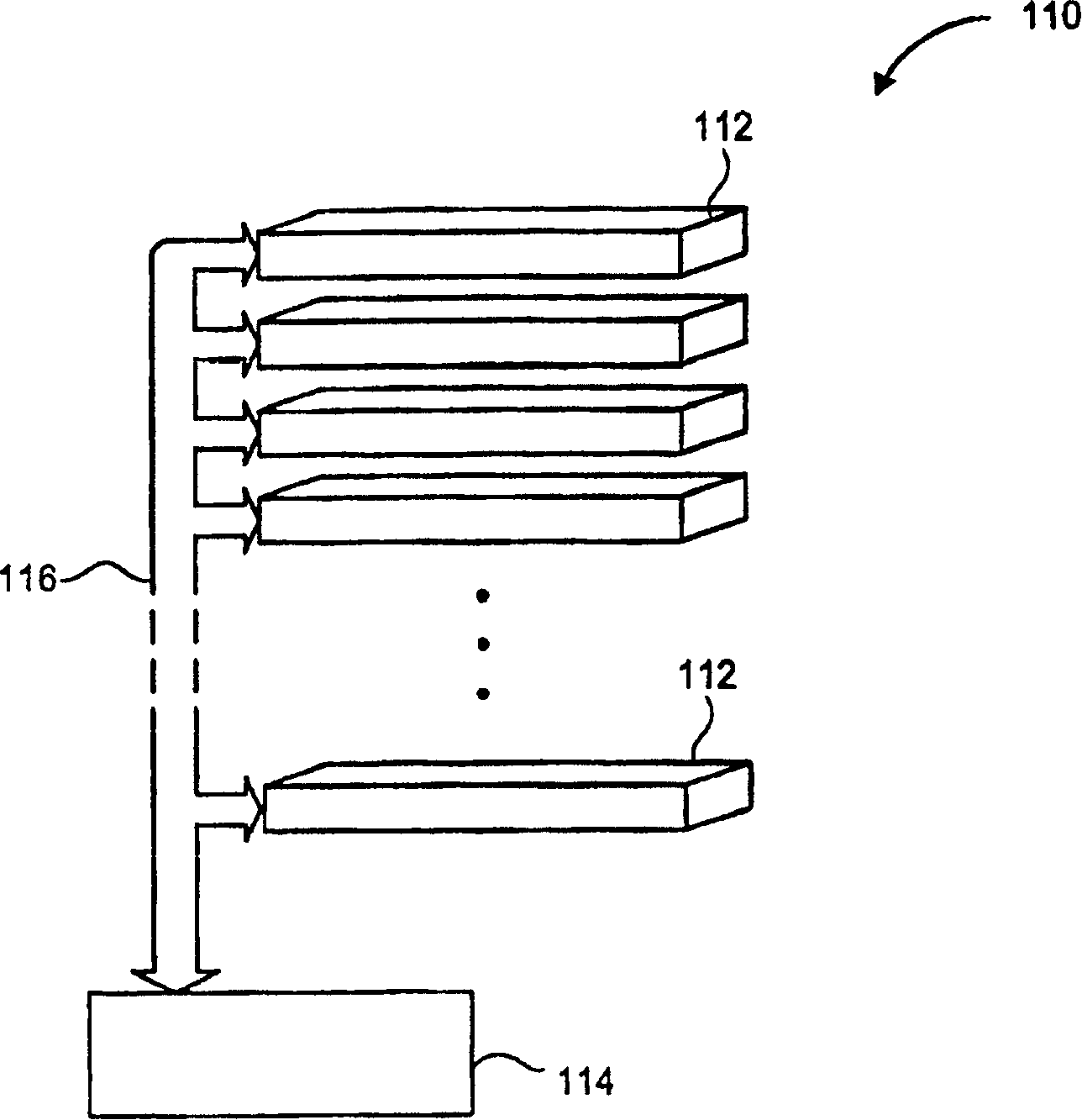

[0022] figure 1 A multi-layer solid state storage device 110 is shown. Multiple layers 112 are stacked on top of each other. Each layer 112 includes main memory and address logic. Layer 1...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap