Testing method of memory address line

A technology of memory address and test method, applied in static memory, instruments, etc., can solve the problem of inability to judge the fault of the address line, and achieve the effect of reducing complexity, simple programming, and simple and intuitive operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

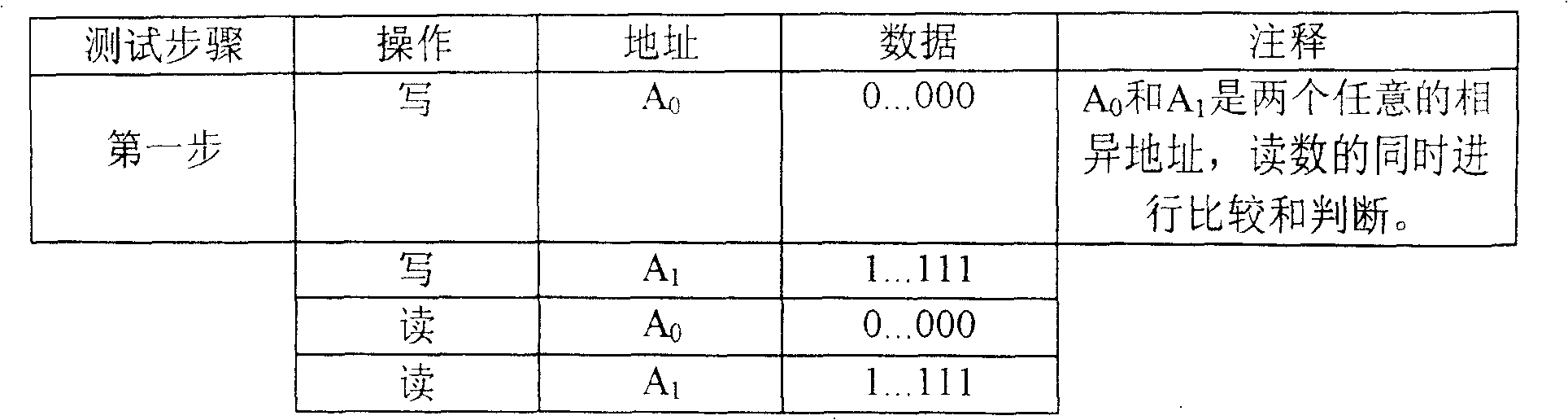

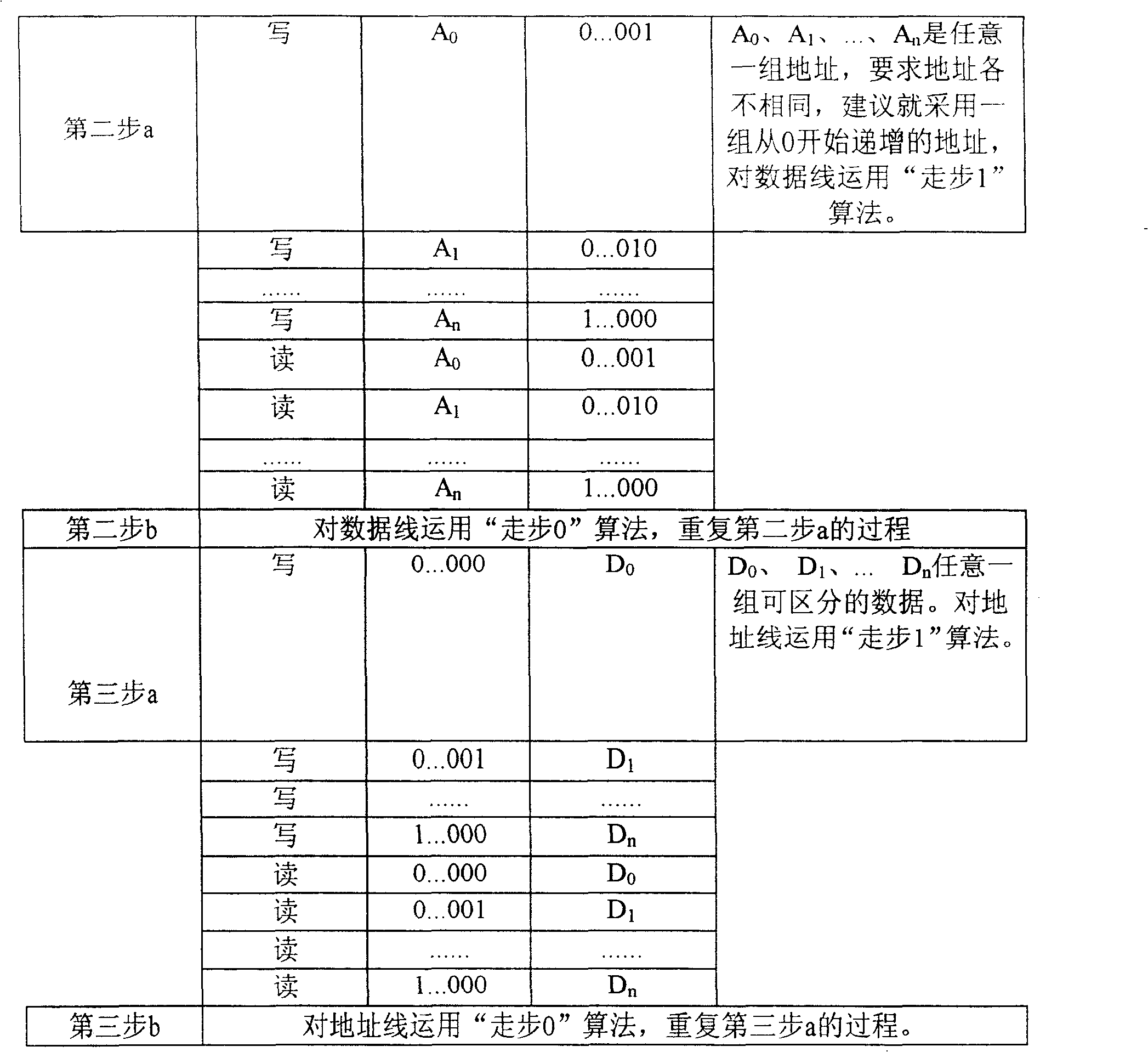

[0094] The present invention locates which address lines have fixed low level and sticky 0-dominant faults with the method of "walking 1" of address lines; uses the method of "walking 0" of address lines to locate which address lines have fixed high level and Sticky 1-dominant type of fault; when performing "walk 1" or "walk 0" test on the address, the data bit corresponding to the test data and the address line to be tested is required to be 0, and the other data bits are 1.

[0095] For the address line "walking 1" test, as shown in Table 4, taking the 8-bit address as an example, first assume that only the same type of connection fault exists, and the fault mode is: a 7 Constantly 0, a 5 and a 4 Short-circuit 0-dominant type, when such a fault occurs, the program will write the test data to the unit with the address 00000000 when writing the test data (when there are multiple address lines faults, it will be written multiple times, if the address line Normally, the addres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More