Laminated semiconductor device

一种半导体、层叠型的技术,应用在半导体器件、半导体/固态器件零部件、电固体器件等方向,能够解决布线效率下降、无法扩大半导体芯片尺寸等问题,达到提高耐噪声特性、提高布线效率及空间利用效率的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

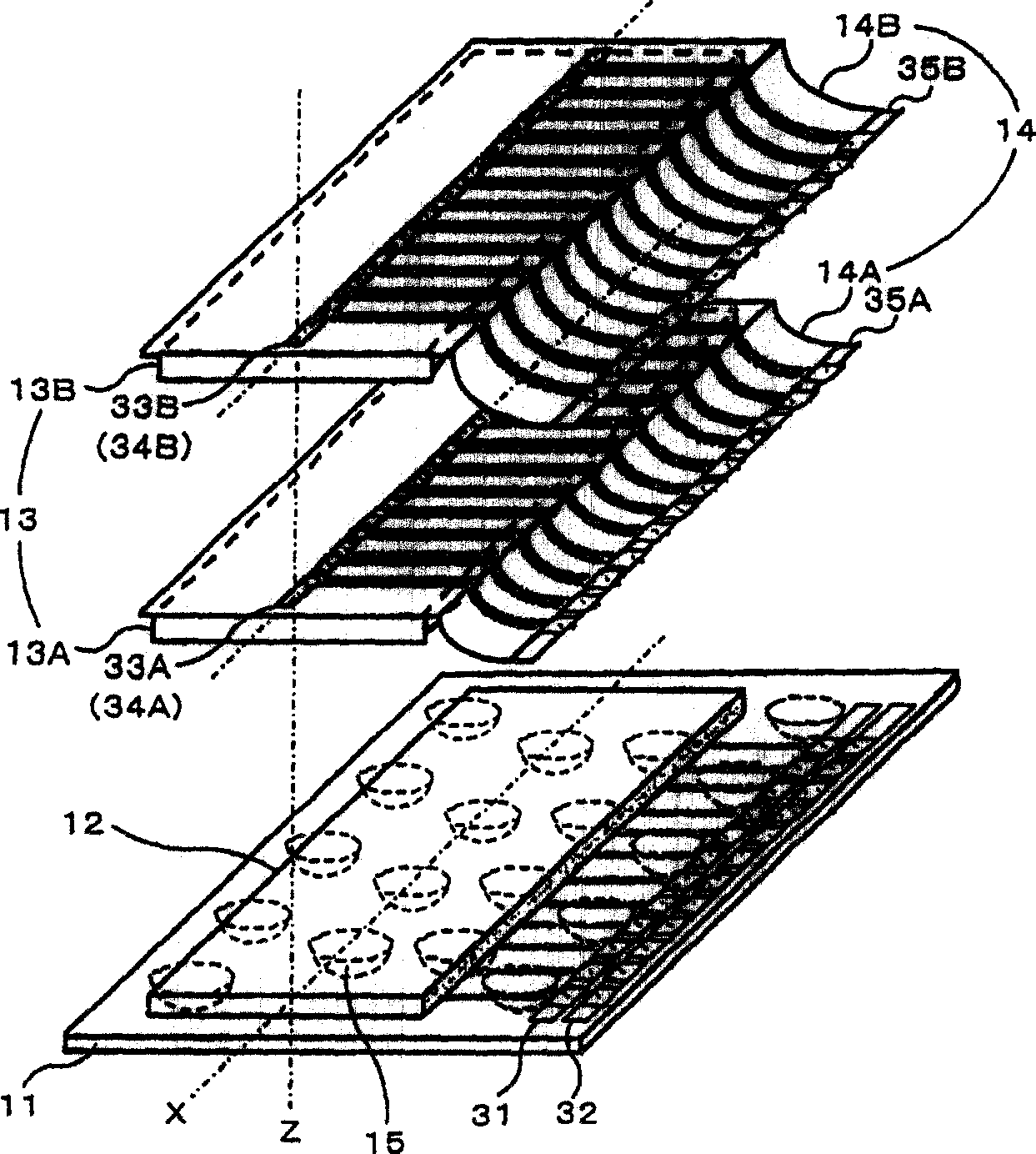

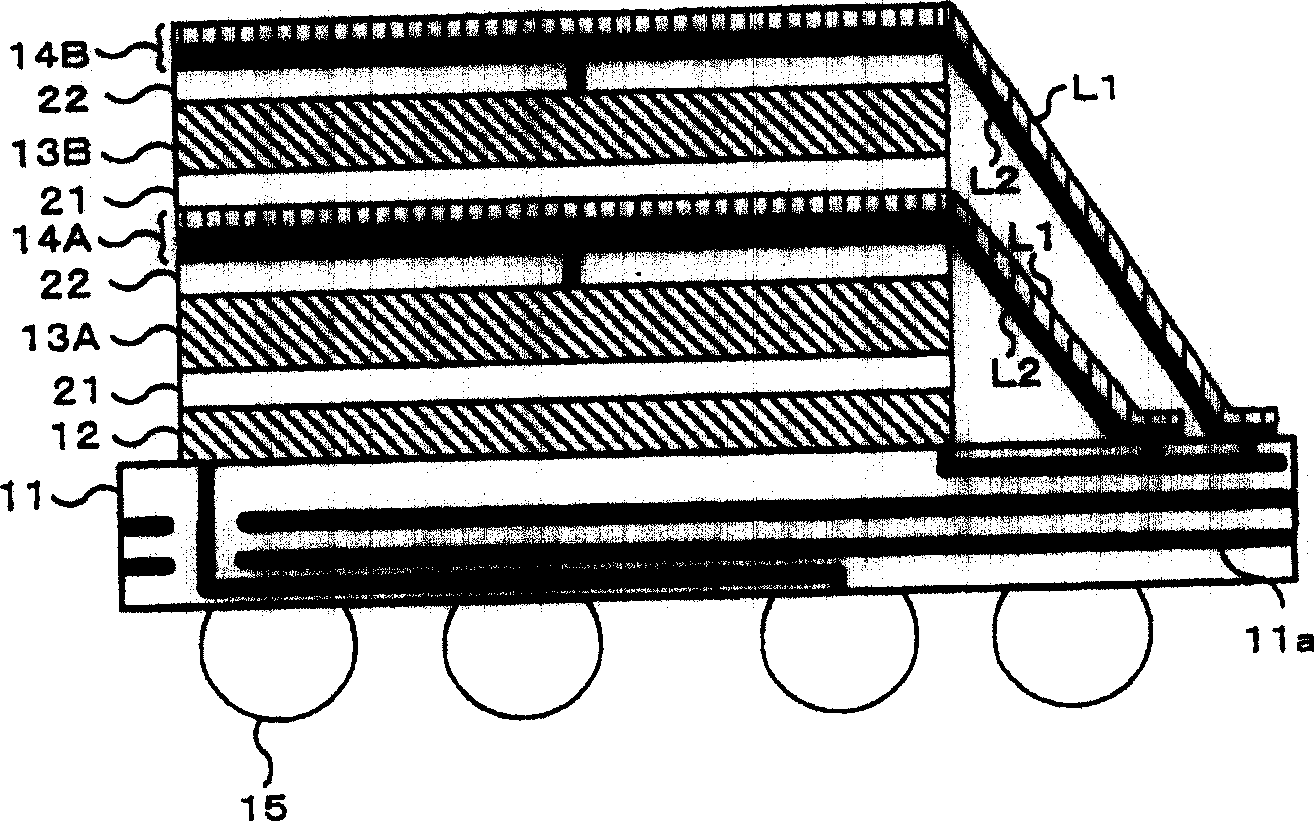

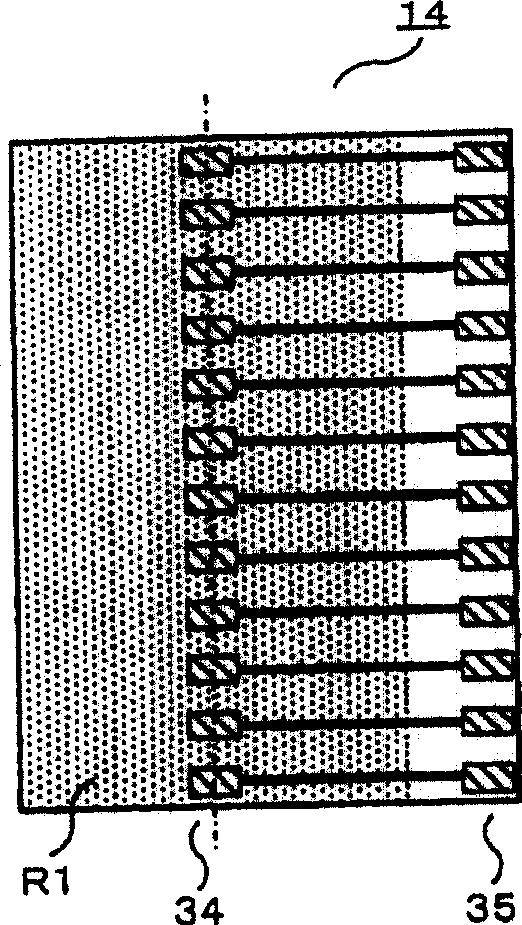

[0041]Embodiments of the present invention will be described below with reference to the drawings. In this embodiment, as an example of a stacked semiconductor device to which the present invention is applied, an embodiment in which a stacked memory is formed by stacking a plurality of DRAM chips will be described. Here, two examples in which the number of stacked DRAM chips are different for the stacked memory of this embodiment will be described. First, as a first embodiment, the basic structure of a stacked memory formed by stacking two DRAM chips will be described. As a diagram illustrating the structure of the stacked memory of the first embodiment, figure 1 is its exploded perspective view, and figure 2 is its cross-sectional structure diagram.

[0042] Such as figure 1 and figure 2 As shown, the stacked memory of the first embodiment has a structure in which three semiconductor chips are stacked on a base substrate 11 . The stacked three semiconductor chips incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More