Laminated semiconductor device

A semiconductor and stacked technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of inability to expand the size of semiconductor chips and decrease wiring efficiency, and achieve improved wiring efficiency and space utilization efficiency. Effect of Improving Noise Resistance Characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

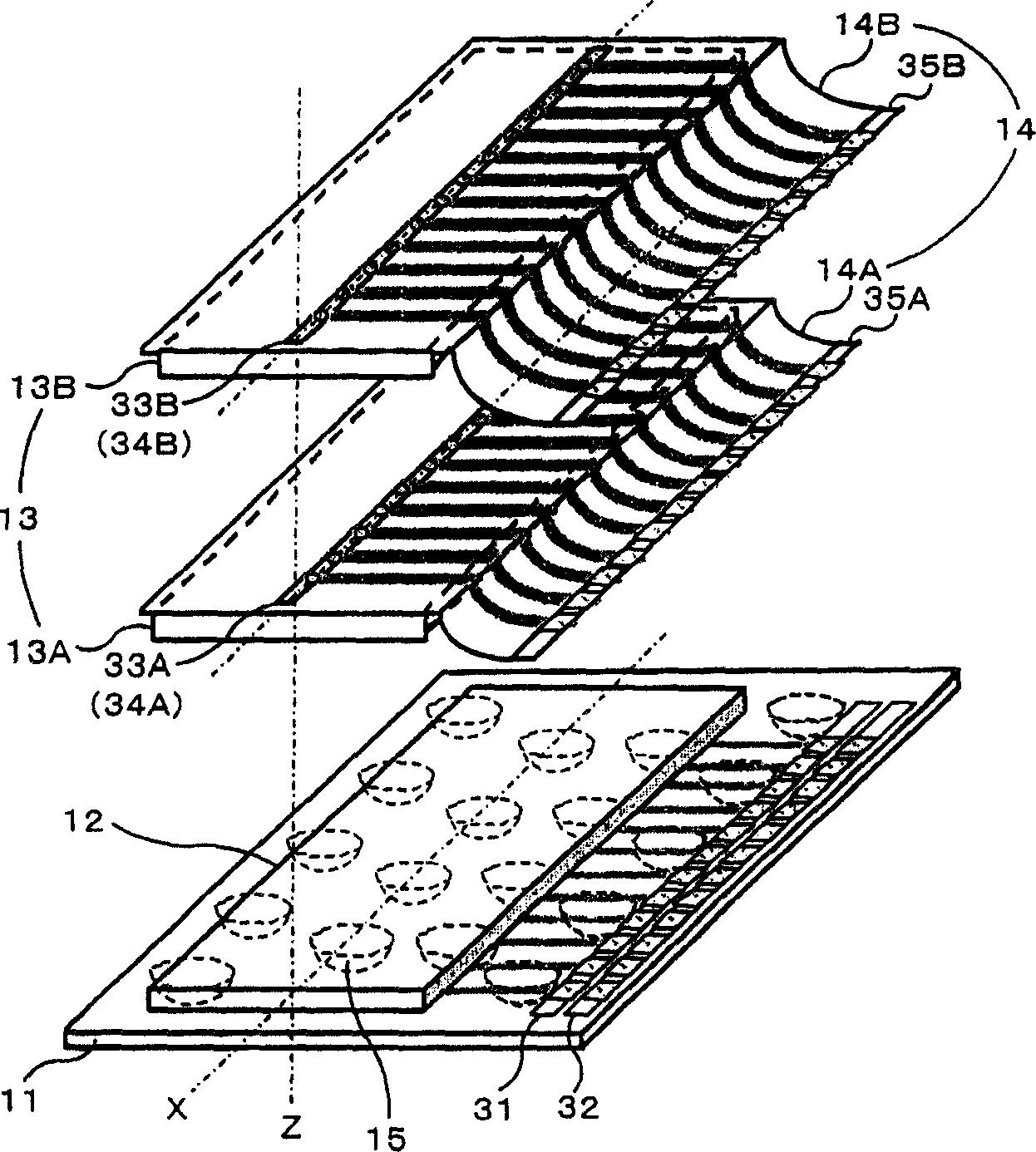

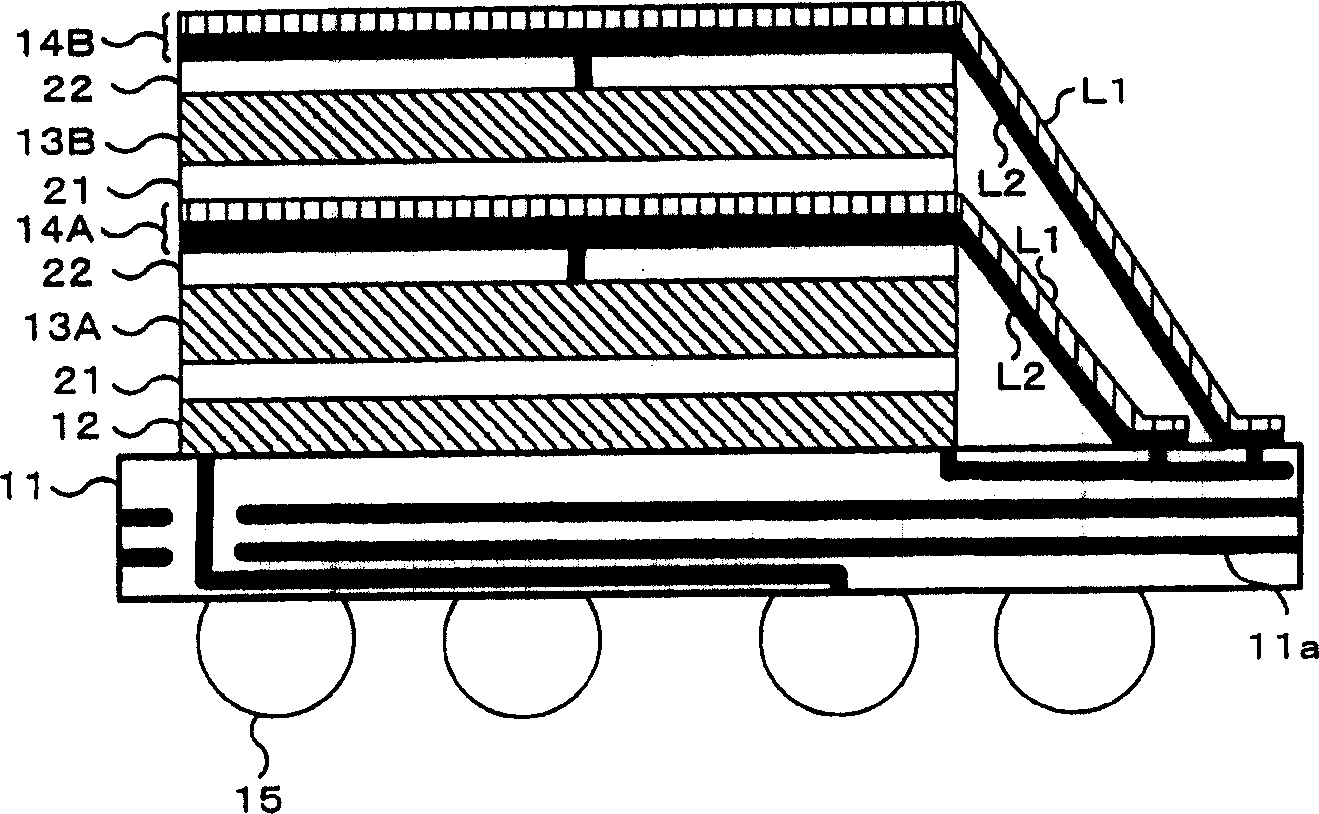

[0042]Embodiments of the present invention will be described below with reference to the drawings. In this embodiment, as an example of a stacked semiconductor device to which the present invention is applied, an embodiment in which a stacked memory is formed by stacking a plurality of DRAM chips will be described. Here, two examples in which the number of stacked DRAM chips are different for the stacked memory of this embodiment will be described. First, as a first embodiment, the basic structure of a stacked memory formed by stacking two DRAM chips will be described. As a diagram illustrating the structure of the stacked memory of the first embodiment, figure 1 is its exploded perspective view, and figure 2 is its cross-sectional structure diagram.

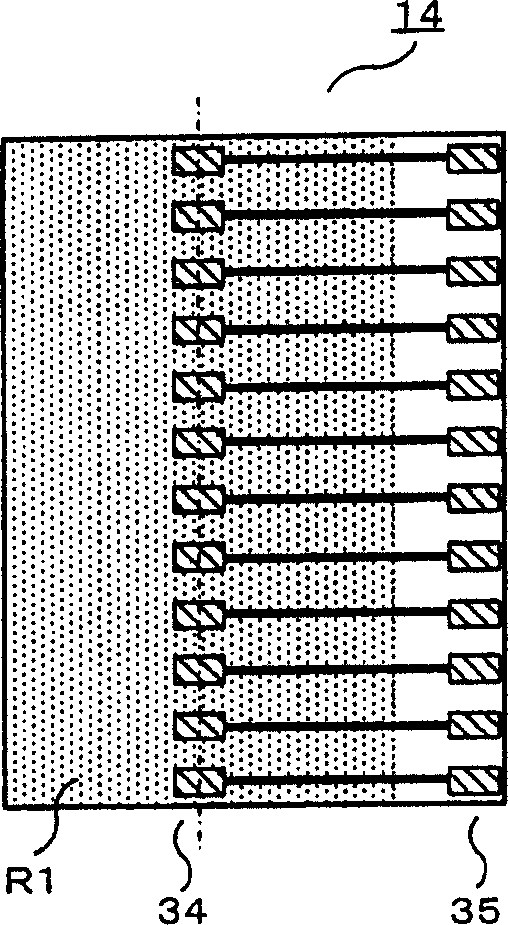

[0043] Such as figure 1 and figure 2 As shown, the stacked memory of the first embodiment has a structure in which three semiconductor chips are stacked on a base substrate 11 . The stacked three semiconductor chips incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More