Data clock recovery circuit

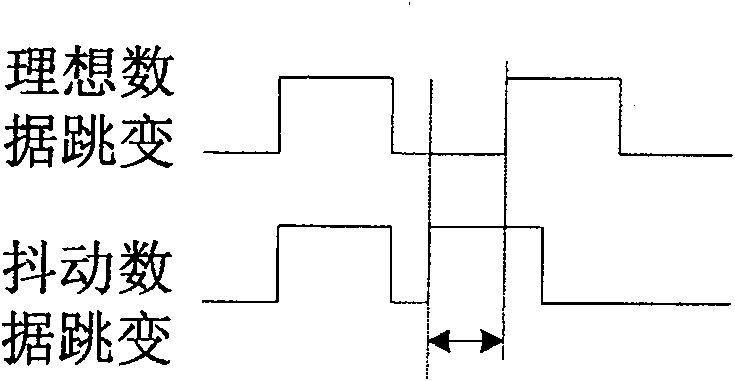

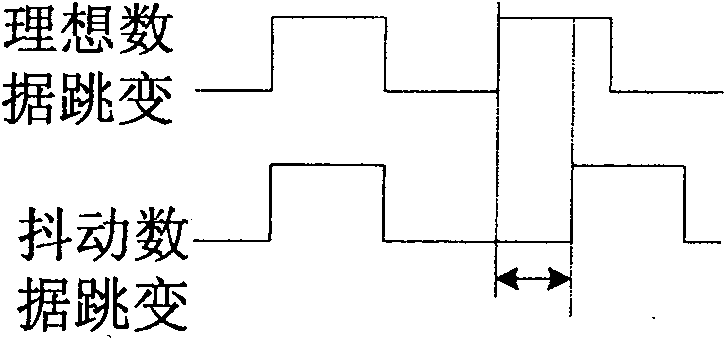

A technology for recovering circuits and data clocks, applied in electrical components, digital transmission systems, transmission systems, etc., can solve the problems of slow phase-locked loop tracking, poor input jitter tolerance, and high reliability, and achieve fast phase-locked tracking speed, Improve the input jitter tolerance and improve the effect of anti-jitter ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Various preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

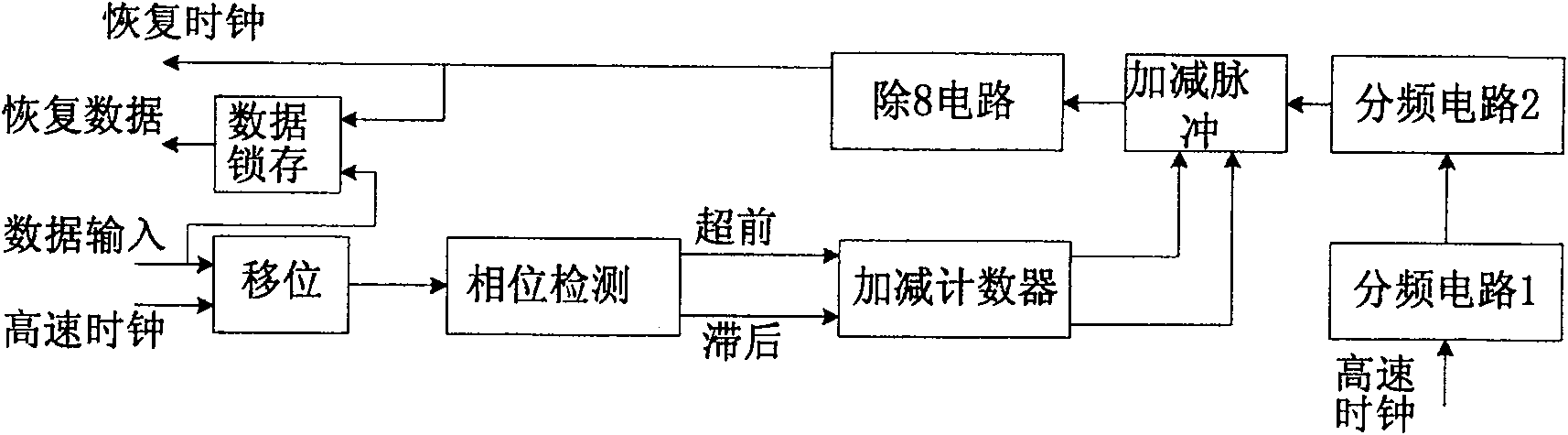

[0021] The data clock recovery circuit of the present invention, such as Figure 4 As shown, it includes: pulse width / edge detection unit A / B, pulse stretching unit A / B, clock phase-locked tracking unit, clock filtering unit, data delay line unit A / B, and data sampling latch unit A / B . The circuit of the present invention has a path for receiving positive polarity data and a path for receiving negative polarity data, and the processing methods of the two are consistent, where A / B represents different paths, not part numbers.

[0022] The received positive polarity data is input to the pulse width / edge detection unit A, and the data edge pulse signal detected by the high-speed clock is output to the pulse stretching unit A. According to the pulse edge signal sent by the previous stage, the pulse stretching unit A stretches it to half...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More