Base semiconductor chip, semiconductor integrated circuit device, and semiconductor integrated circuit device manufacturing method

A technology of integrated circuit and manufacturing method, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of inseparable interconnection test function blocks and difficult identification of test function blocks, etc., to prevent Increase in inventory, prevent increase in power consumption, and shorten the period of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

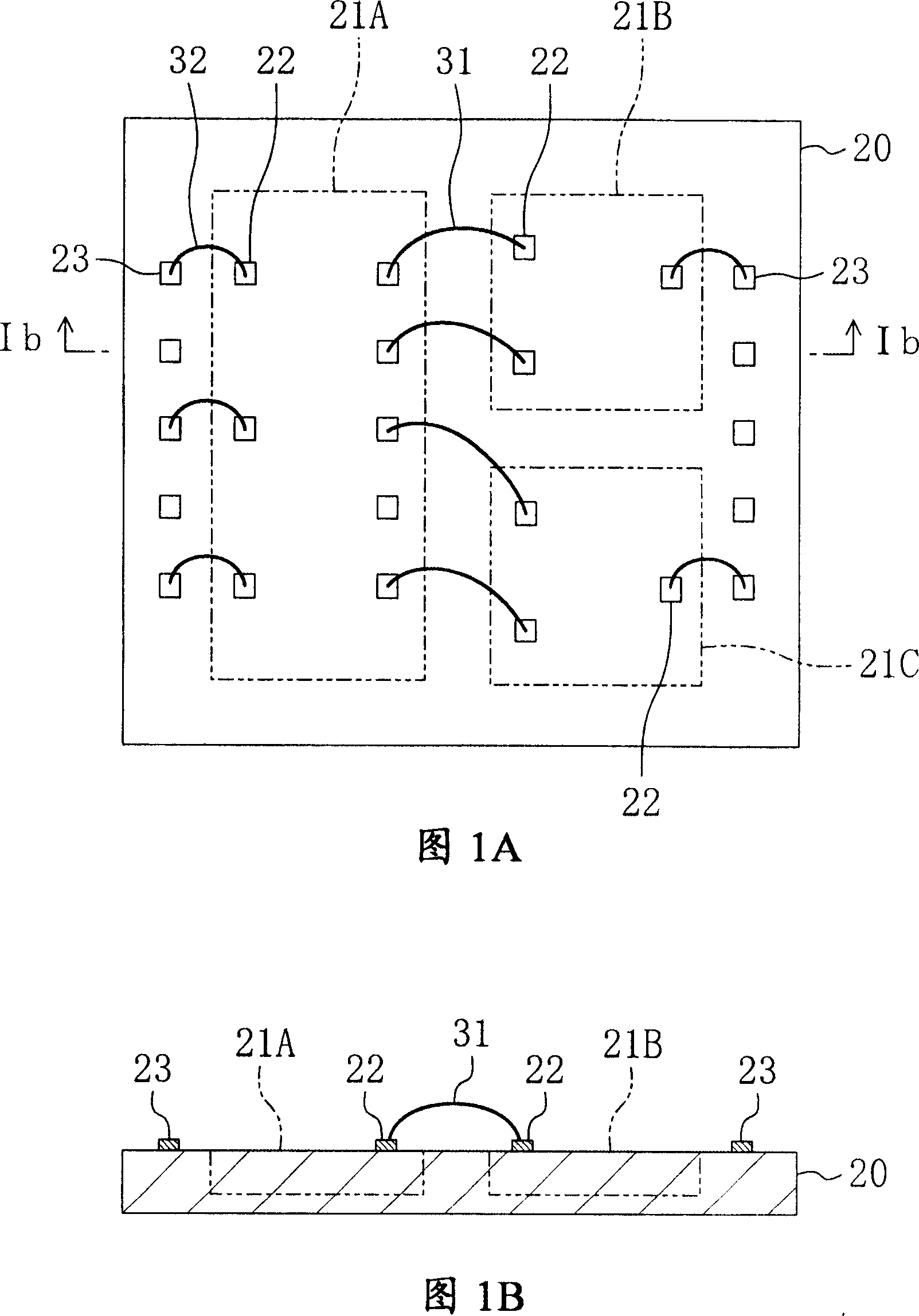

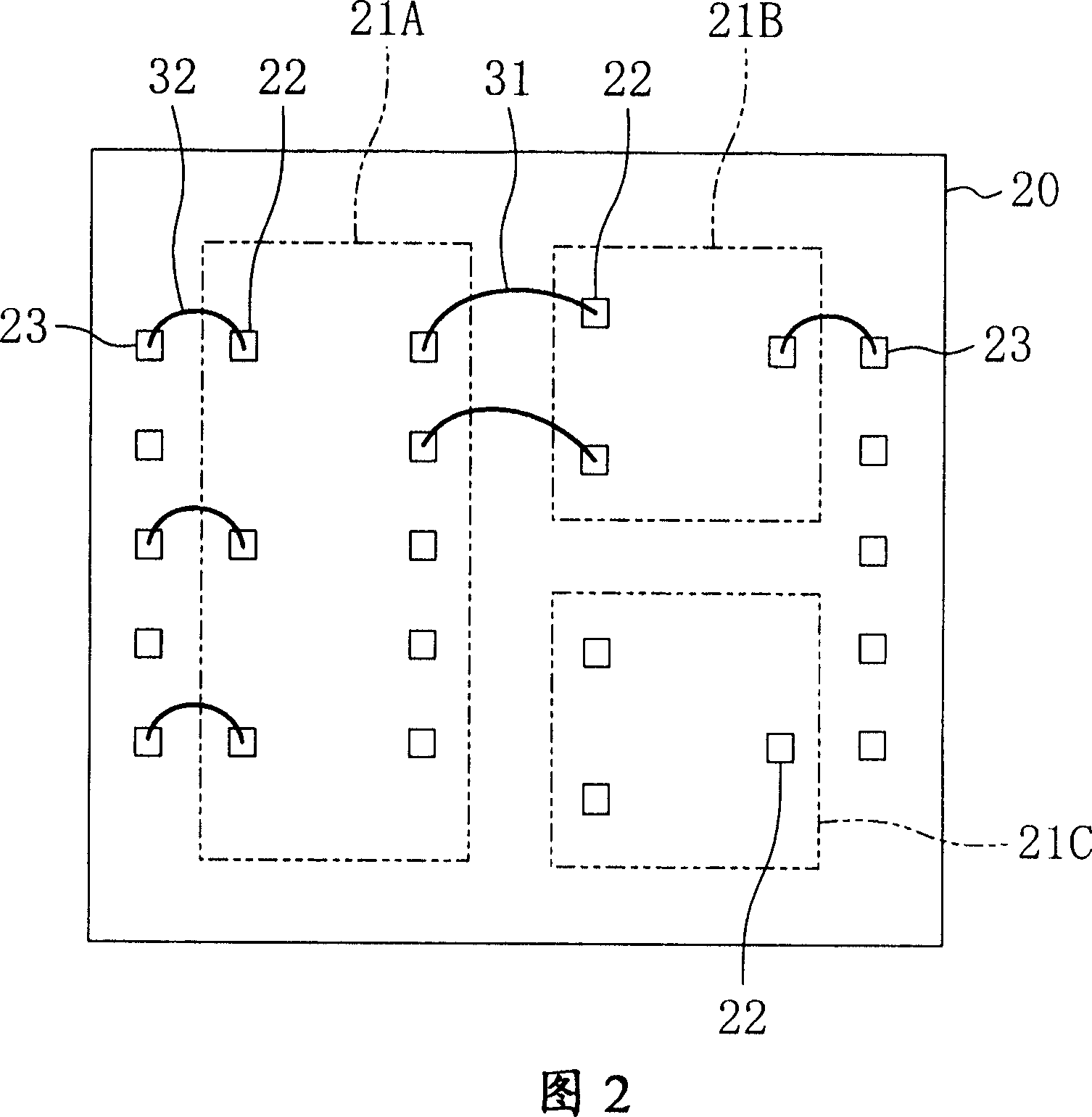

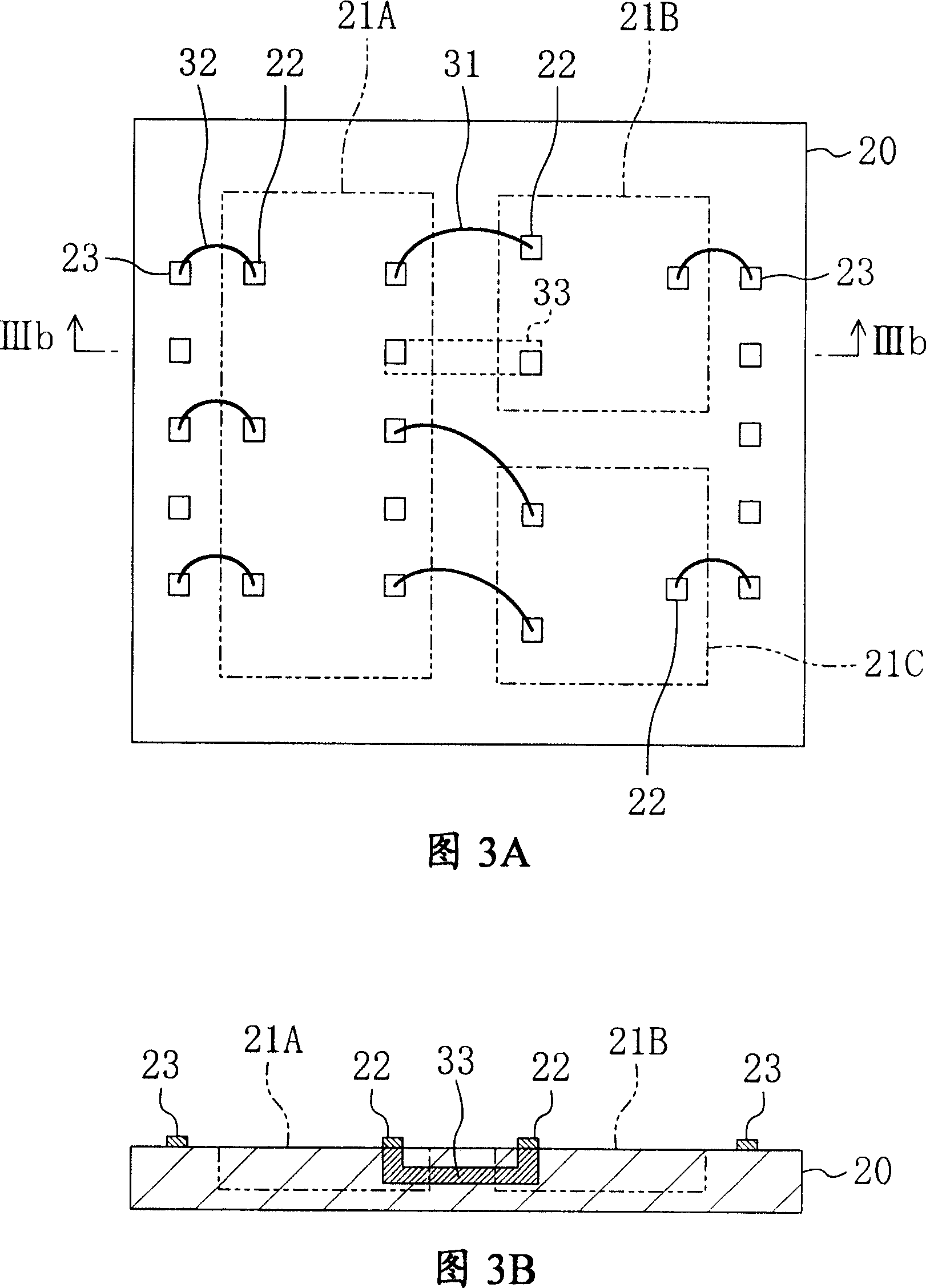

[0054] Embodiment 1 of the present invention will be described with reference to the drawings. 1 shows a main part of a semiconductor integrated circuit device (LSI circuit) according to Embodiment 1, wherein FIG. 1A is a plan view, and FIG. 1B is a cross-sectional view taken along line Ib-Ib in FIG. 1A.

[0055] As shown in FIG. 1, the LSI circuit of the present embodiment includes: a basic semiconductor chip 20 as a semiconductor substrate in which a plurality of functional blocks as a semiconductor integrated circuit are formed; and interconnections for interconnecting the functional blocks. Even 31. In FIG. 1 , three functional blocks of a first functional block 21A, a second functional block 21B, and a third functional block 21C are provided as an example. Each functional block may be any functional block such as a microprocessor, memory or the like.

[0056] These functional blocks are formed independently of each other in a predetermined region of the base semiconduct...

Embodiment 2

[0073] Embodiment 2 of the present invention will be described below with reference to the drawings. FIG. 10 shows a basic semiconductor chip 40 according to Embodiment 2. As shown in FIG. In Embodiment 2, a portion including necessary functional blocks is cut out from a base semiconductor chip to form an LSI circuit including necessary functions.

[0074] As shown in FIG. 10, the basic semiconductor chip 40 is composed of a plurality of functional blocks formed in a semiconductor substrate. For example, the basic semiconductor chip 40 shown in FIG. 10 includes six functional blocks: a first functional block 21A, a second functional block 21B, a third functional block 21C, a fourth functional block 21D, a fifth functional block 21E, and a sixth functional block. Function block 21F.

[0075] Although not shown, similarly to FIG. 1 , a plurality of functional block pads 22 are formed along the periphery of the functional block. Therefore, each region forming a functional bloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More