External memory controller timing configuration device and method

An external memory, timing configuration technology, applied in the field of electronics, can solve the problem of incomplete effective control of write enable signal or output enable signal, single control of write enable signal or output enable signal, operation timing that does not meet timing requirements, etc. problems, to avoid incomplete effective control, flexible configuration, and flexible generation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

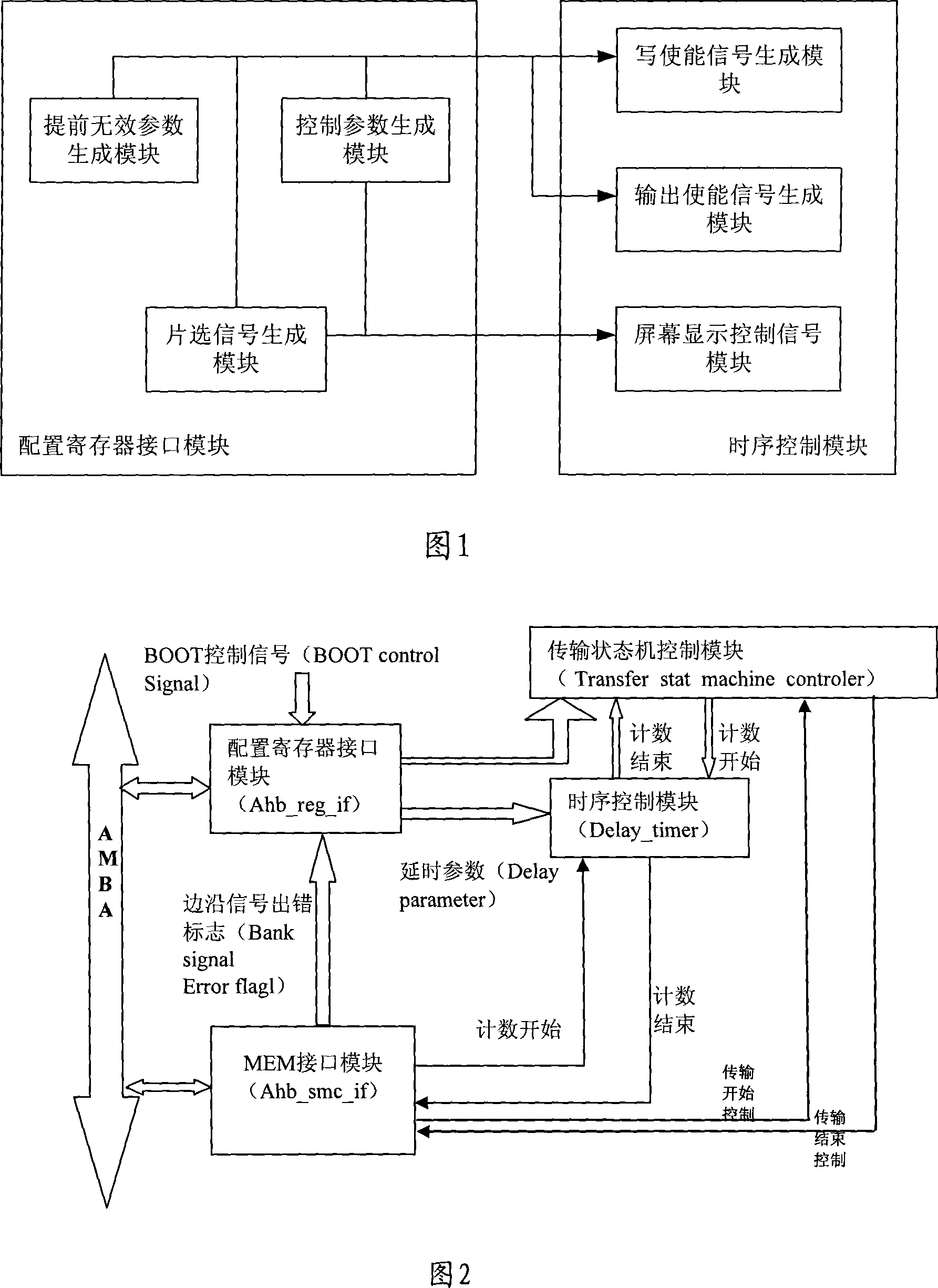

[0024] An embodiment of the present invention provides a device for timing configuration of an external memory controller, and its structural diagram is shown in FIG. 1 . FIG. 1 is a schematic structural diagram of a device for configuring timing of an external memory controller provided by an embodiment of the present invention, including Configuration register interface module and timing control module;

[0025] The configuration register interface module is used to configure the early invalid parameters and control parameters for generating the control signal and the CS signal according to the parameters of the current memory;

[0026] The timing control module is configured to generate a control signal based on the CS signal according to the received early invalidation parameter and control parameter of the control signal; the control signal includes a write enable signal and / or an output enable signal.

[0027] The configuration register interface module includes an early...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More