Lateral double-diffused mosfet (LDMOS) transistor and a method of fabricating the same

A technology of transistors and oxide layers, applied in semiconductor/solid-state device manufacturing, transistors, semiconductor devices, etc., can solve problems such as incompatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

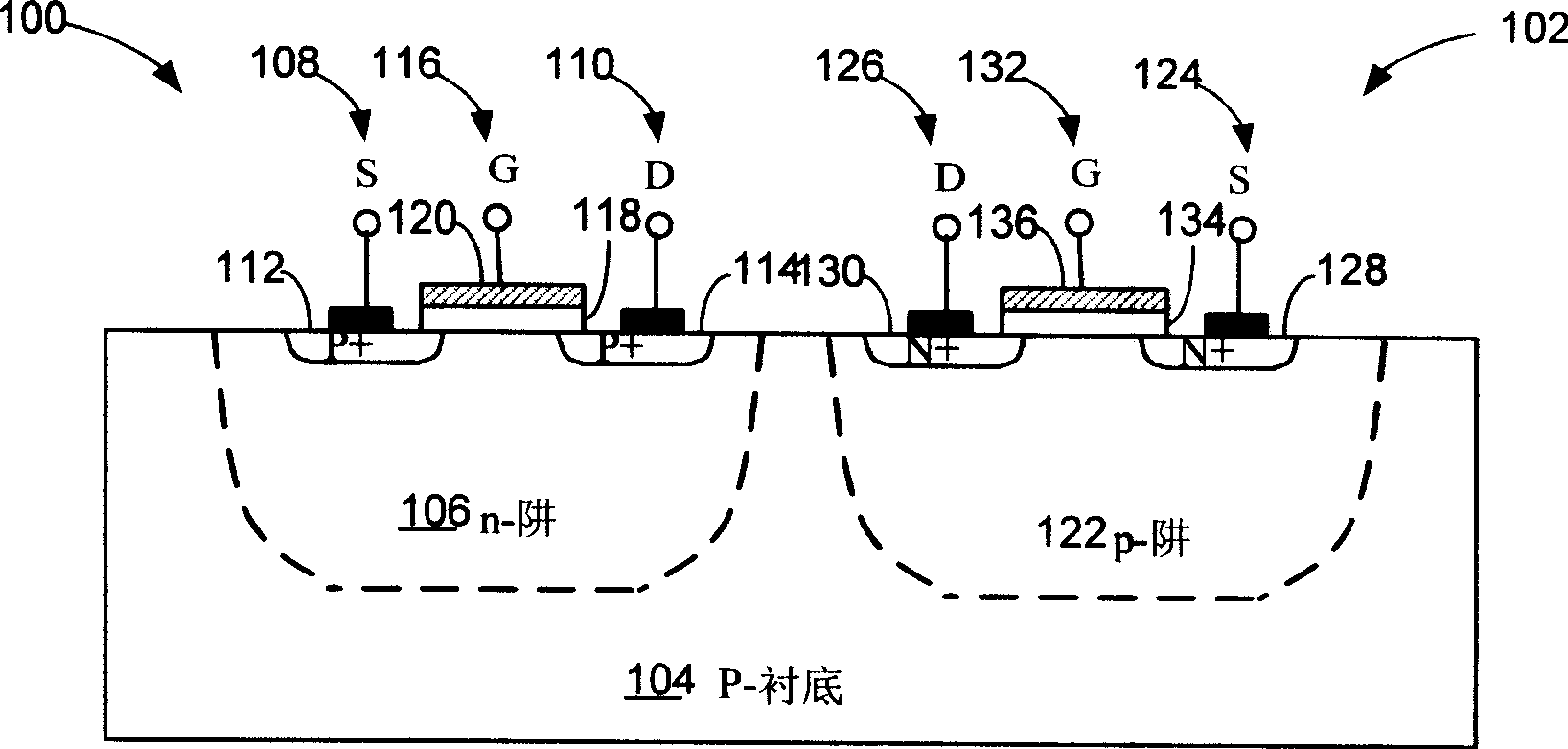

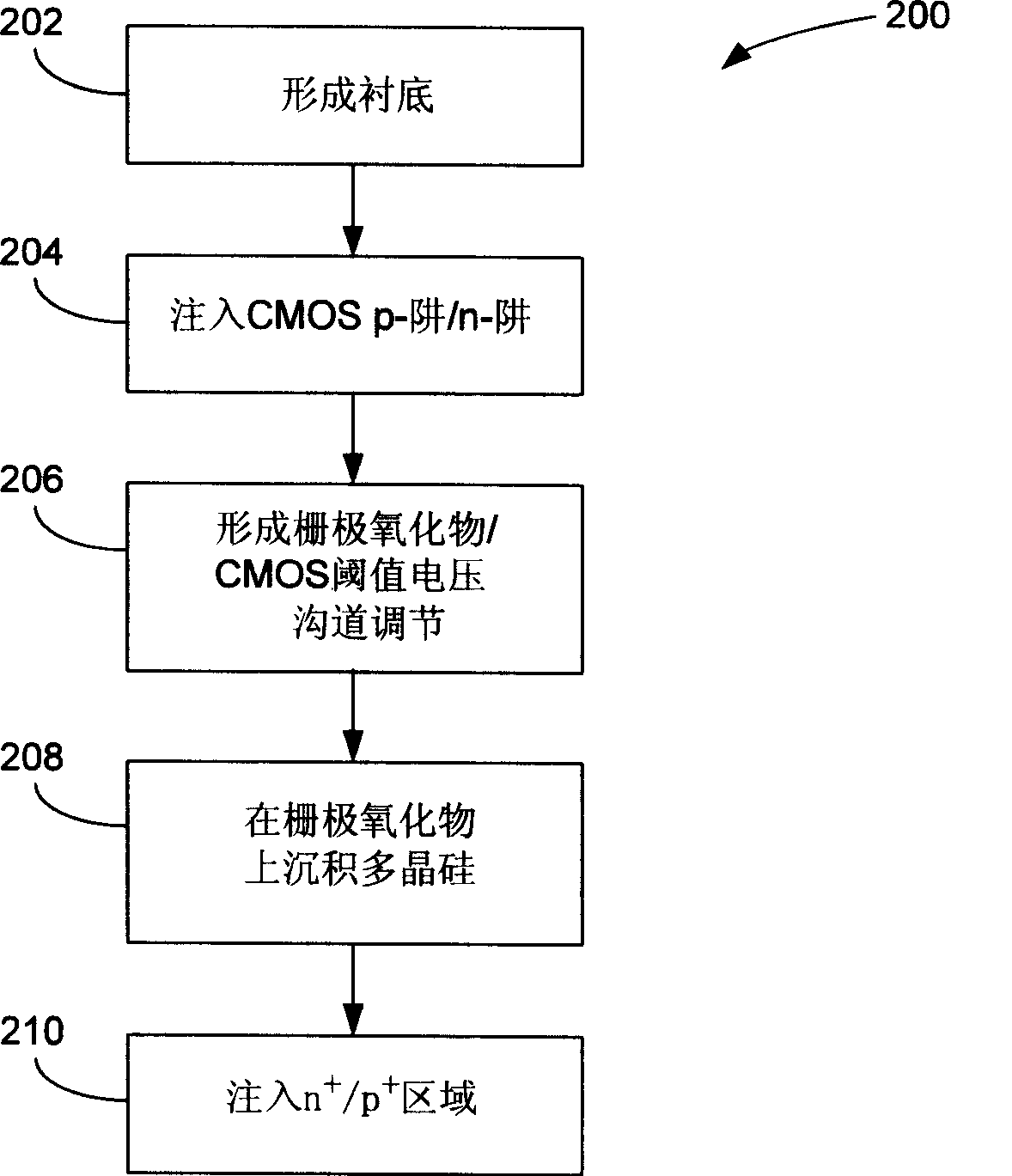

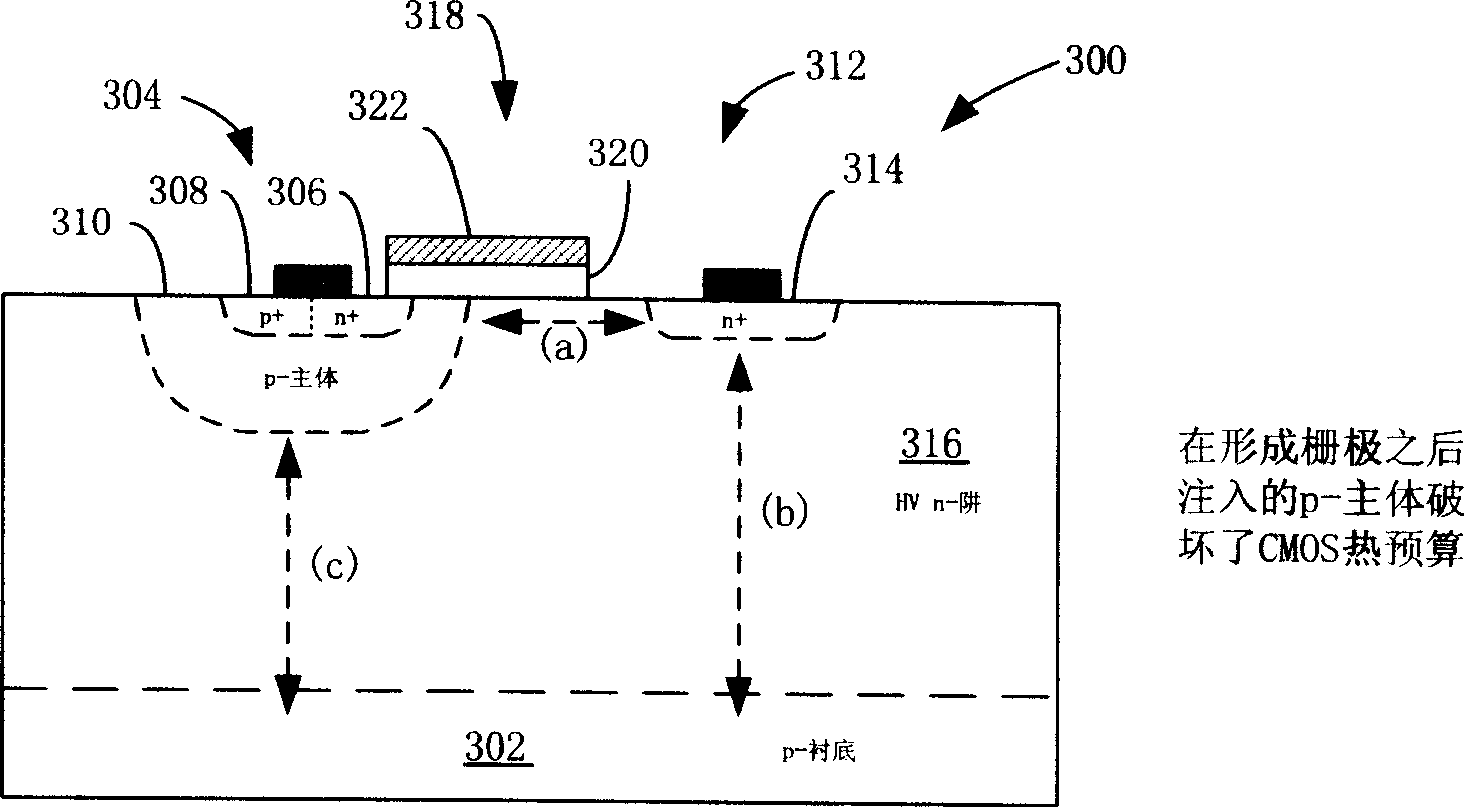

[0045] Figure 4 Shown is a block diagram of a switching regulator including LDMOS transistors according to one embodiment. Conventional LDMOS transistors typically achieve optimized device performance through complex processes such as BiCMOS processes or BCD processes that include one or more process steps that are incompatible with sub-micron processes for mass-produced digital sub-micron CMOS transistors . According to one aspect, there is provided an LDMOS transistor fabricated by a process fully integrated into a typical sub-micron CMOS process.

[0046] refer to Figure 4 , the exemplary switching regulator 400 is connected to a first high DC input voltage source 402 such as a battery through an input terminal 404 . The switching regulator 400 is also connected to a load 406 such as an integrated circuit through an output terminal 408 . The switching regulator 400 acts as a direct current to direct current (DC-to-DC) converter between an input terminal 404 and an out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More