Random access memory having test circuit

A technology for testing circuits and memory, applied in static memory, instruments, etc., can solve problems such as low data volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

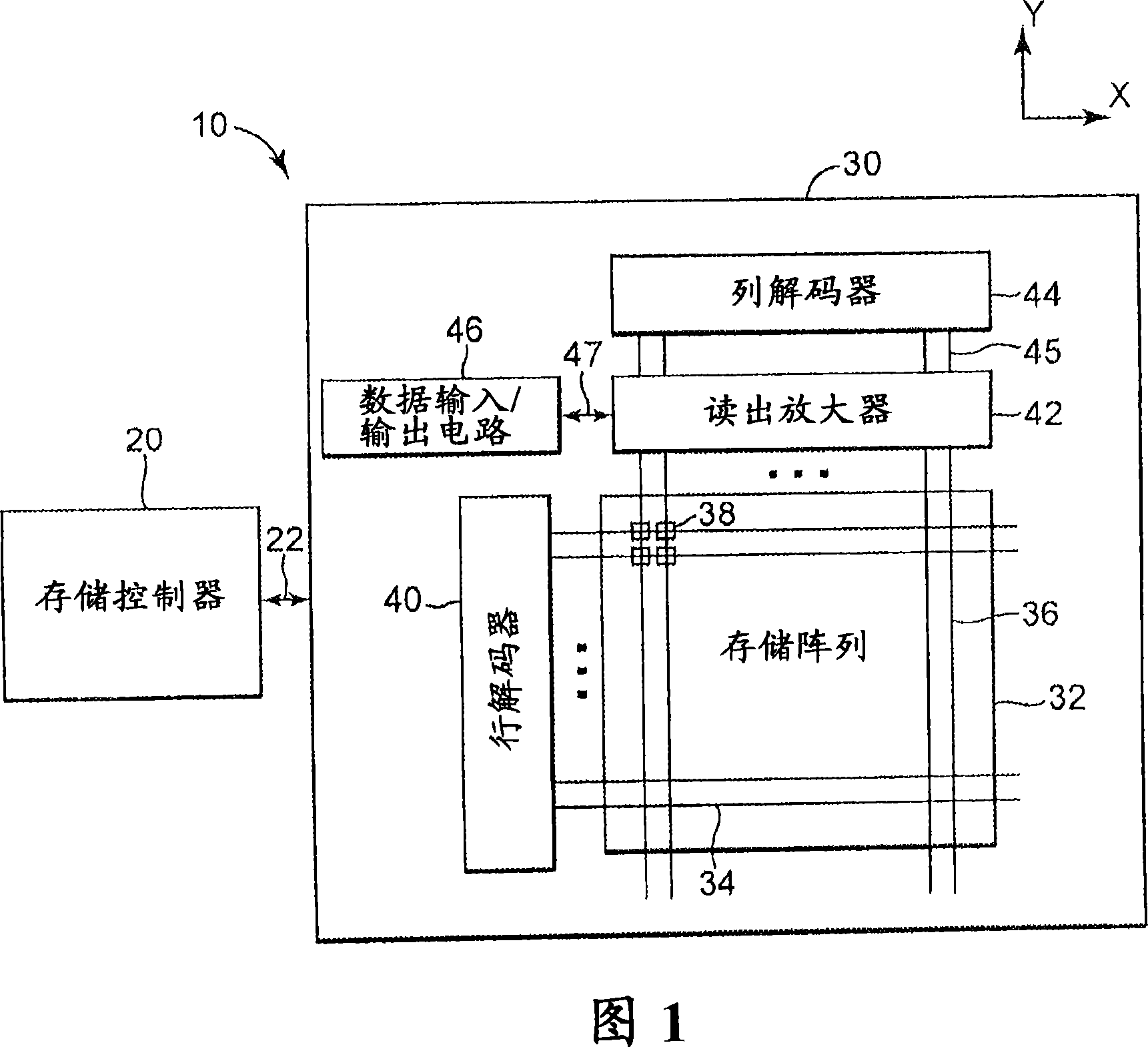

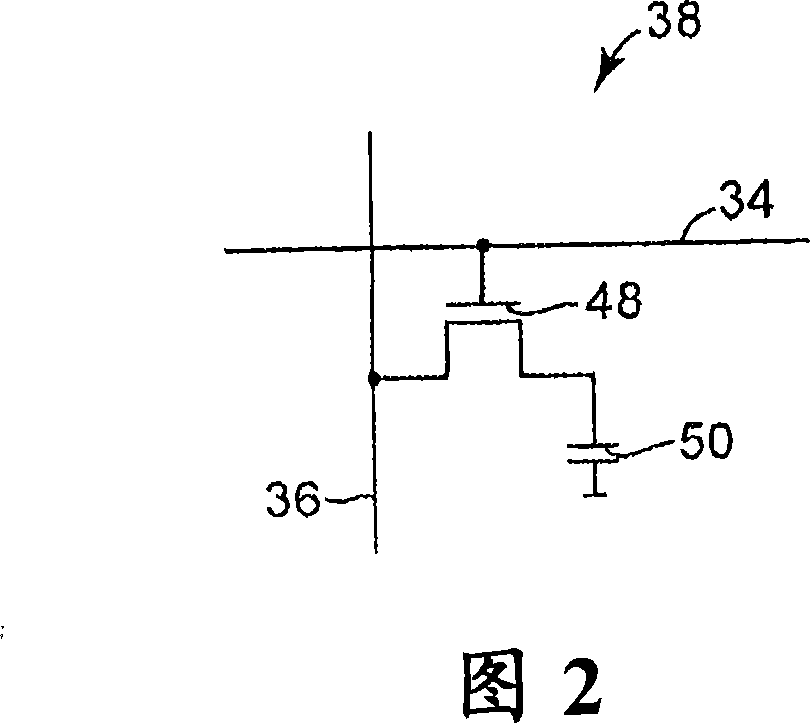

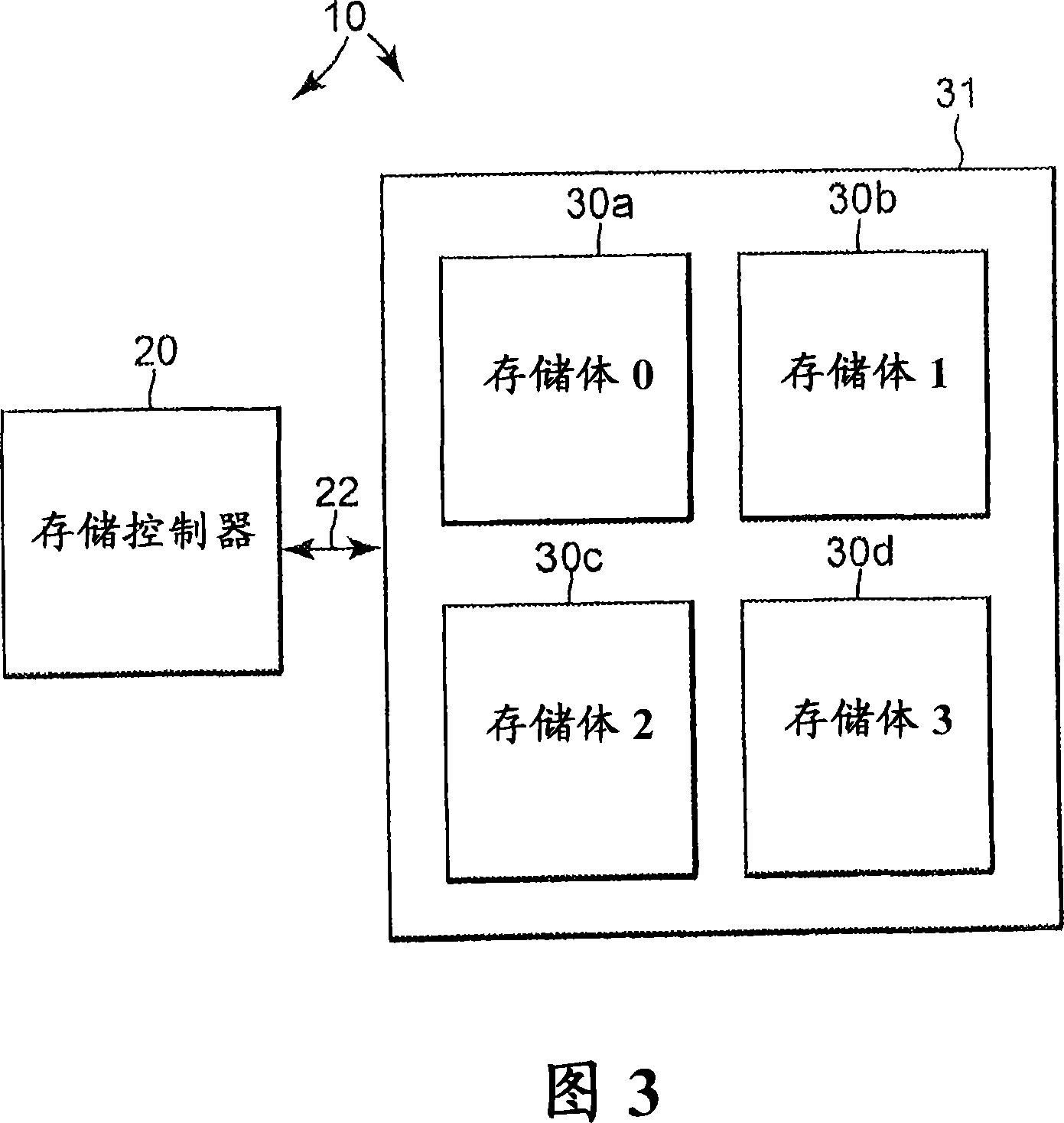

[0011] FIG. 1 is a block diagram illustrating an embodiment of a memory 10 . In this embodiment, memory 10 is a random access memory such as dynamic random access memory (DRAM), synchronous dynamic random access memory (SDRAM), double data rate synchronous dynamic random access memory (DDR SDRAM), dual data rate rate two synchronous dynamic random access memory (DDR2SDRAM), pseudo static random access memory (PSRAM), magnetic random access memory (MRAM), or flash memory. The memory 10 includes a memory controller 20 and at least one memory bank 30 . The memory bank 30 includes a memory cell array 32 , a row decoder 40 , a column decoder 44 , a sense amplifier 42 and a data input / output circuit 46 . Memory controller 20 is electrically connected to memory bank 30 by communication link 22 .

[0012] The memory 10 includes a normal operation mode and a backend test mode. The memory 10 is configured to perform back-end testing in a back-end test mode that tests the memory 10 af...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap