Semiconductor memory, controller and method for operating semiconductor memory

一种存储器、半导体的技术,应用在静态存储器、数字存储器信息、信息存储等方向

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

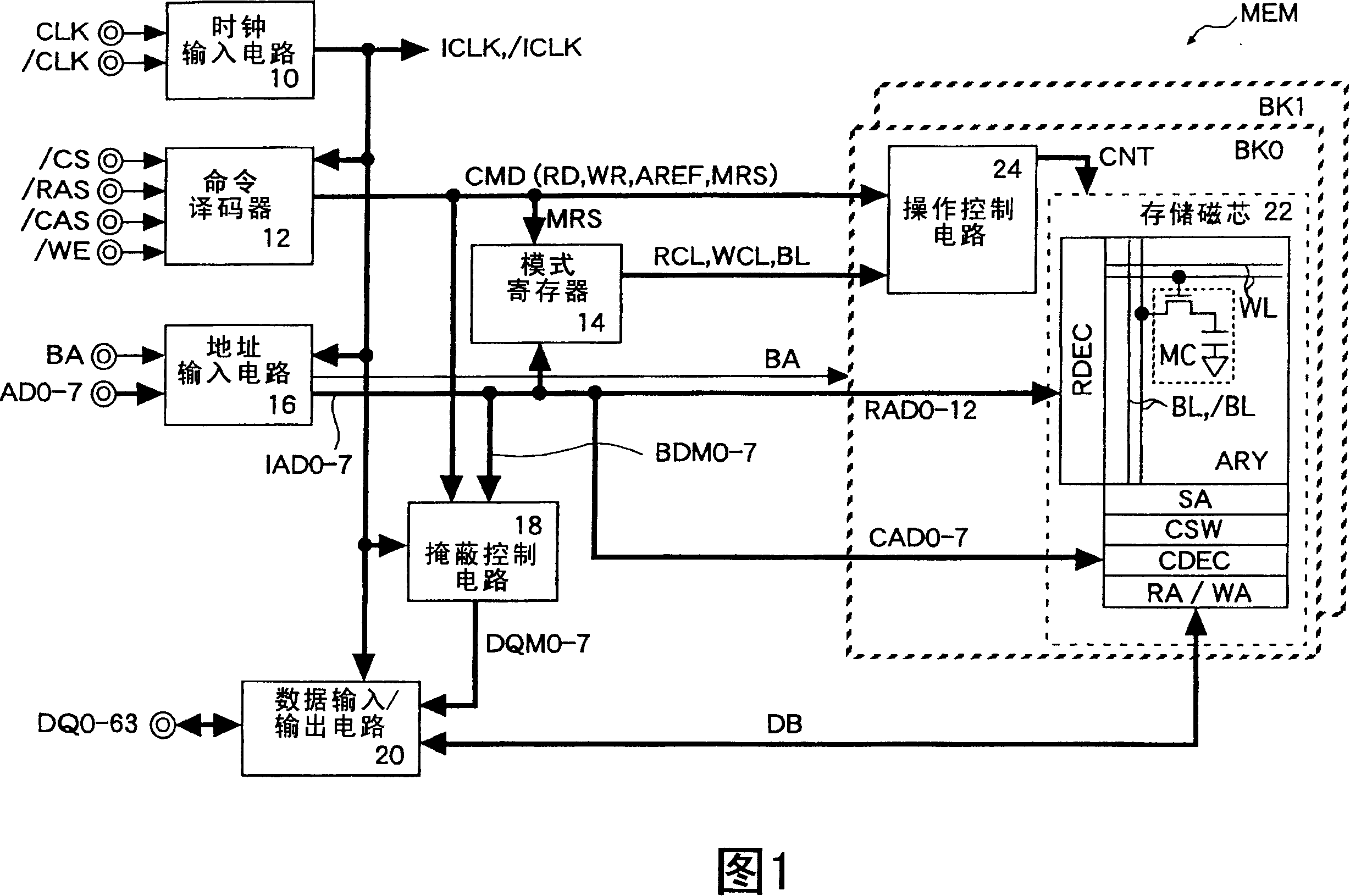

[0022] Embodiments of the present invention will be described below with reference to the drawings. A signal line shown as a thick line in the figure is composed of a plurality of lines. Also, some blocks to which thick lines are connected are constituted by a plurality of circuits. The same symbol as the signal name is used for the signal line that carries that signal. Signals beginning with " / " indicate negative logic. Double circles in the figure indicate external terminals.

[0023] FIG. 1 is a block diagram showing a first embodiment of the present invention. The semiconductor memory MEM is, for example, a clock synchronous type FCRAM (Fast Cycle RAM) that operates in synchronization with an external clock CLK. FCRAM is a pseudo-SRAM having a memory cell of DRAM and an interface of SDRAM. The memory MEM includes a clock input circuit 10, a command decoder 12, a mode register 14, an address input circuit 16, a mask control circuit 18, a data input / output circuit 20, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More