Film transistor array substrates and its producing method, repairing method

A technology of thin film transistors and array substrates, applied in the fields of thin film transistor array substrates and its manufacture and repair, to achieve the effect of convenient and simple repair, without affecting the aperture ratio, and increasing the effect of existing processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

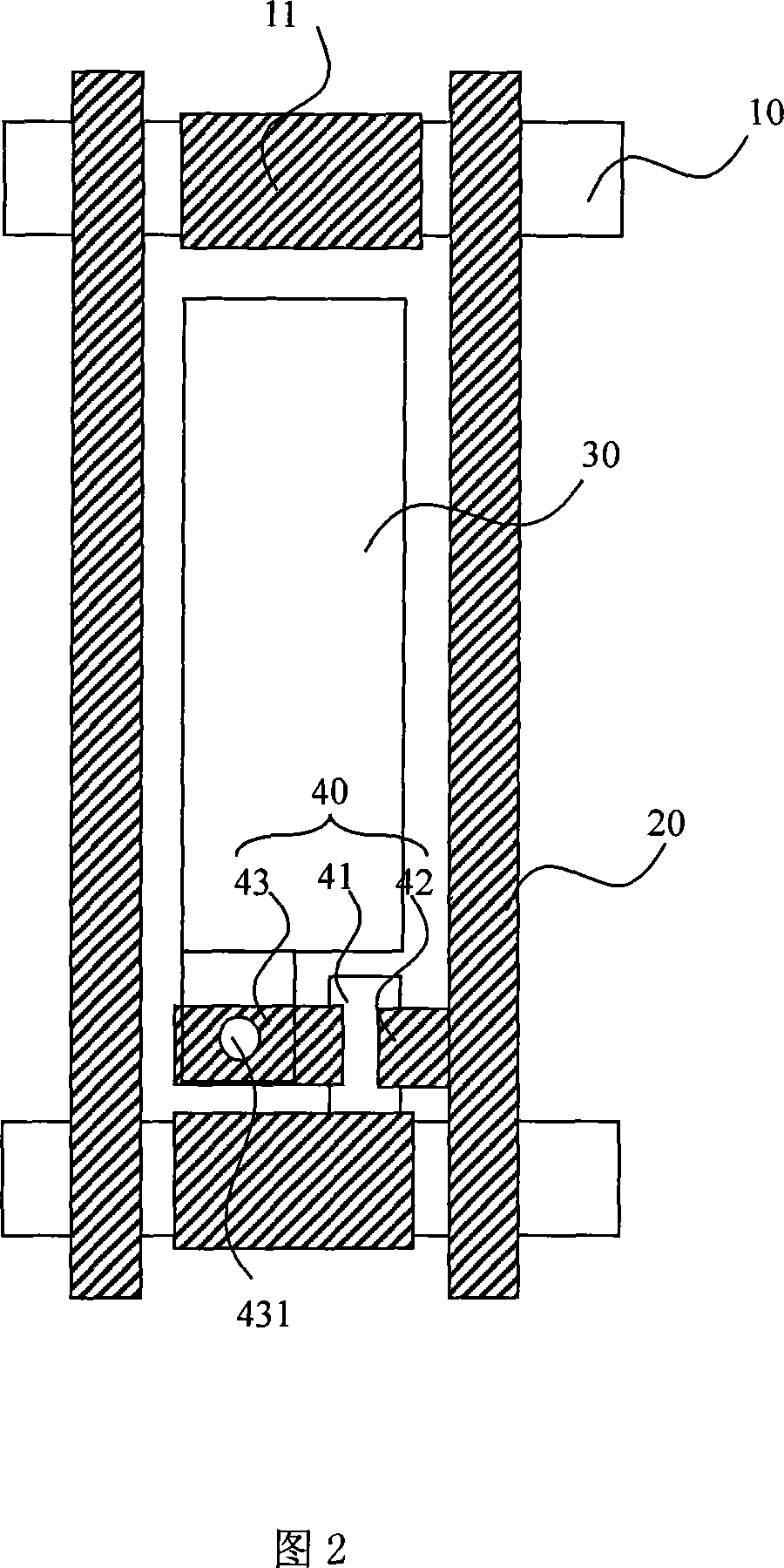

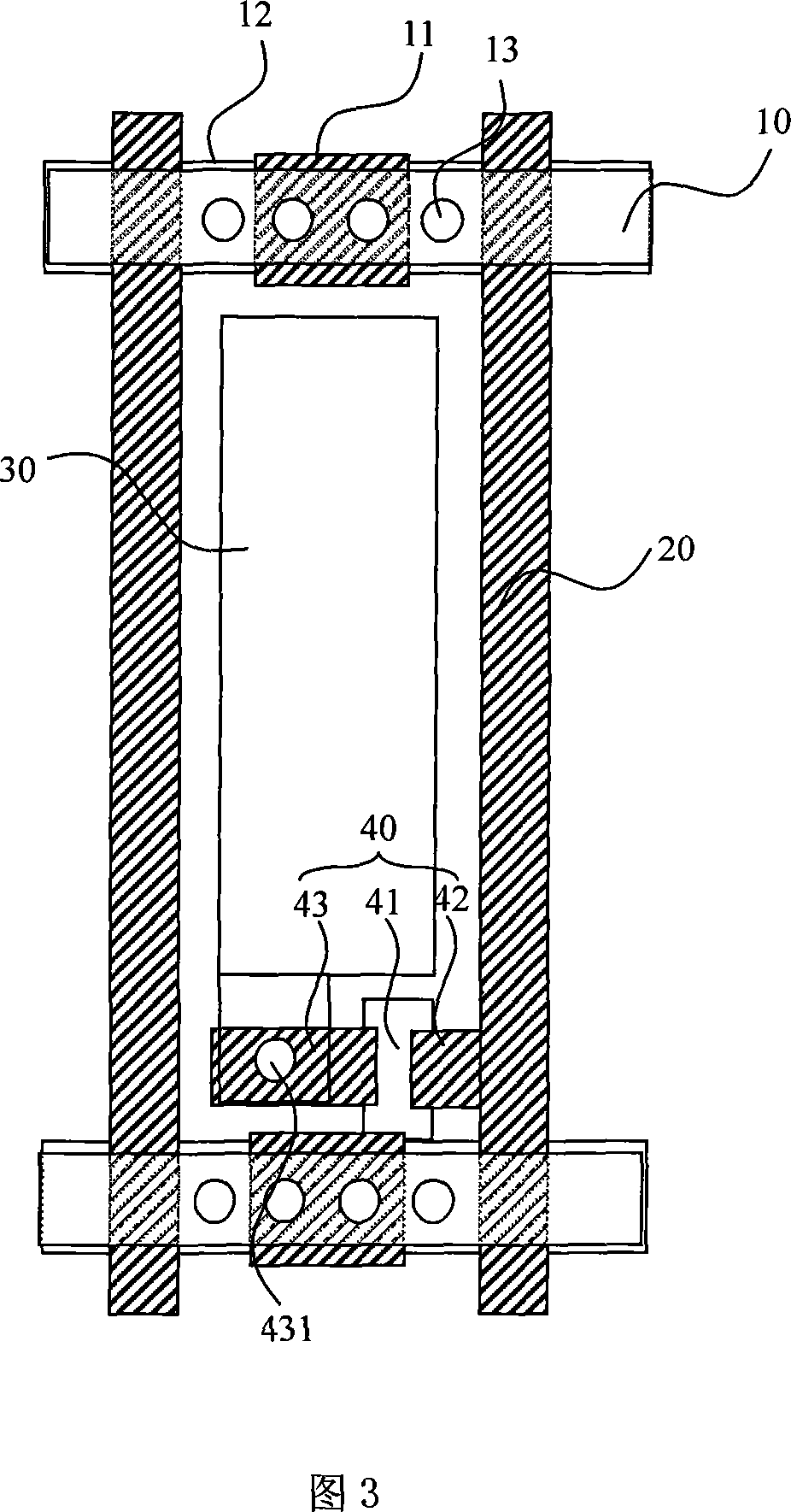

[0029] 2 and 3 are schematic structural views of a thin film transistor array substrate according to Embodiment 1 of the present invention.

[0030] Referring to FIG. 2, the thin film transistor array substrate includes a plurality of gate scanning lines 10 extending along a first direction; a plurality of data lines 20 extending along a second direction, and the intersection of the gate scanning lines 10 and the data lines 20 forms a pixel area; A thin film transistor 40 and a pixel electrode 30 are arranged in the area, and a metal pattern 11 is formed on the gate scanning line 10. The thin film transistor 40 is composed of a gate 41, a source 42 and a drain 43. The gate 41 is electrically connected to the gate scanning line 10. connection, the drain 43 is electrically connected to the data line 20, the source 42 is connected to the pixel electrode 30 through the contact hole 41, the gate 41 and the gate scan line 10 are formed on the first metal layer (M1), the source 42, th...

Embodiment 2

[0039] FIG. 4 is a schematic structural diagram of a thin film transistor array substrate according to Embodiment 2 of the present invention.

[0040] Referring to FIG. 4 , the difference from the structure of the thin film transistor array substrate provided in Embodiment 1 is that a metal pattern 21 is formed under the data line 20 in this embodiment, and the metal pattern 21 is formed on the same layer as the gate scanning line 10 . The material of the metal pattern 21 is the same as that of the gate scan line 10 . In the process of manufacturing the array substrate, when patterning the first metal layer, the metal pattern 21 corresponding to the data line 20 is reserved, and the metal pattern 21 is compatible with other metal patterns of the same layer such as the gate 41 and the gate scanning line 10. separated from each other.

[0041] When an open circuit occurs on the data line 20, laser welding can be performed on both sides of the broken line from the back of the a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More