Network-on-chip digital router and its parallel data transmission method

A network-on-chip and router technology, applied in the field of network-on-chip digital routers and their parallel data transmission, can solve problems such as the inability to fully utilize the functional advantages of the system chip, increase the consumption of chip area, and intensify the competition of bus resources, so as to solve the problem of resource occupation and The problem of data congestion, solving the problem of increased competition, and reducing the effect of data congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

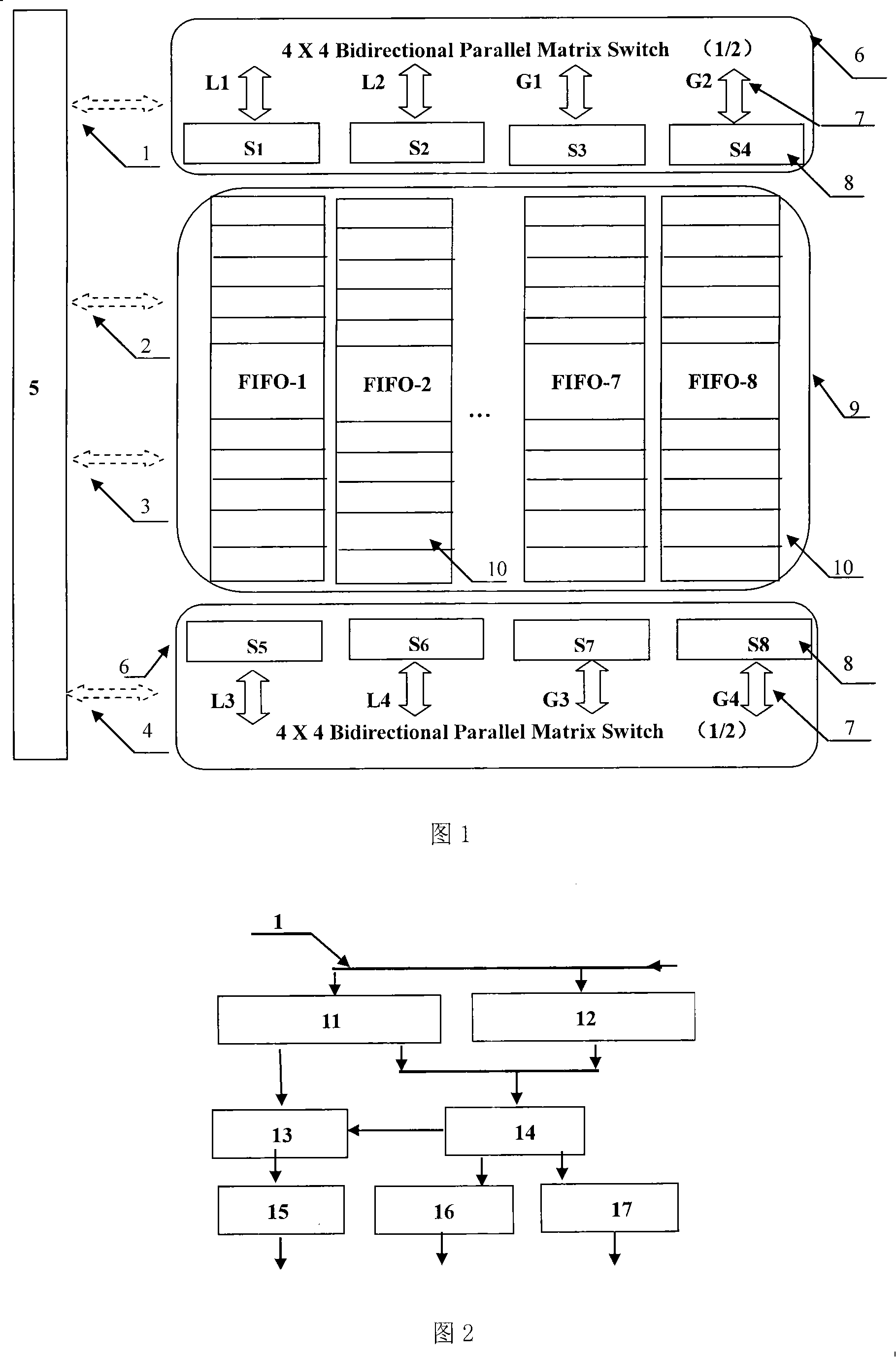

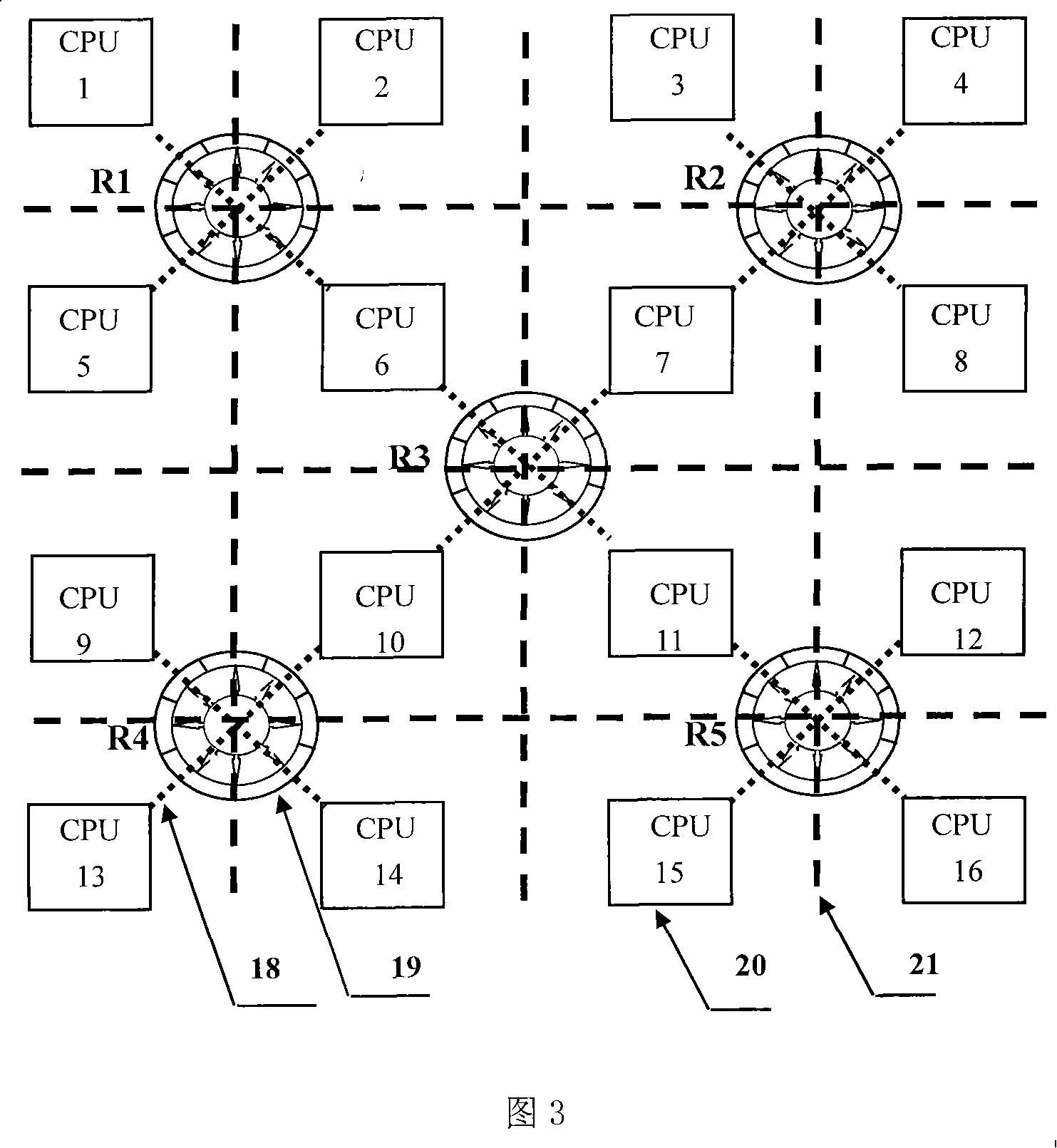

[0035] The embodiment of router of the present invention is shown in Fig. 1-3, and it is on the integrated circuit chip by FIFO shift buffer memory 10, two groups of synchronous matrix switch arrays 8 on both sides of FIFO shift buffer memory 10, The routing decision module 5 and the parallel network interface 7 are collected, and the parallel network interface 7 input ports are connected with the synchronous matrix switch array 8; the output interface of the synchronous matrix switch array 8 on one side of the memory and the first-in-first-out wave shift buffer memory ( FIFO) 10 input interface is connected, and the output interface of FIFO shift buffer memory 10 is connected with synchronous matrix switch array on the other side, is connected to parallel network interface 7 by synchronous matrix switch array; Routing decision module 5 comprises data stream header register 11 And status flag register 12, its interface contains command output interface, the input interface of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More