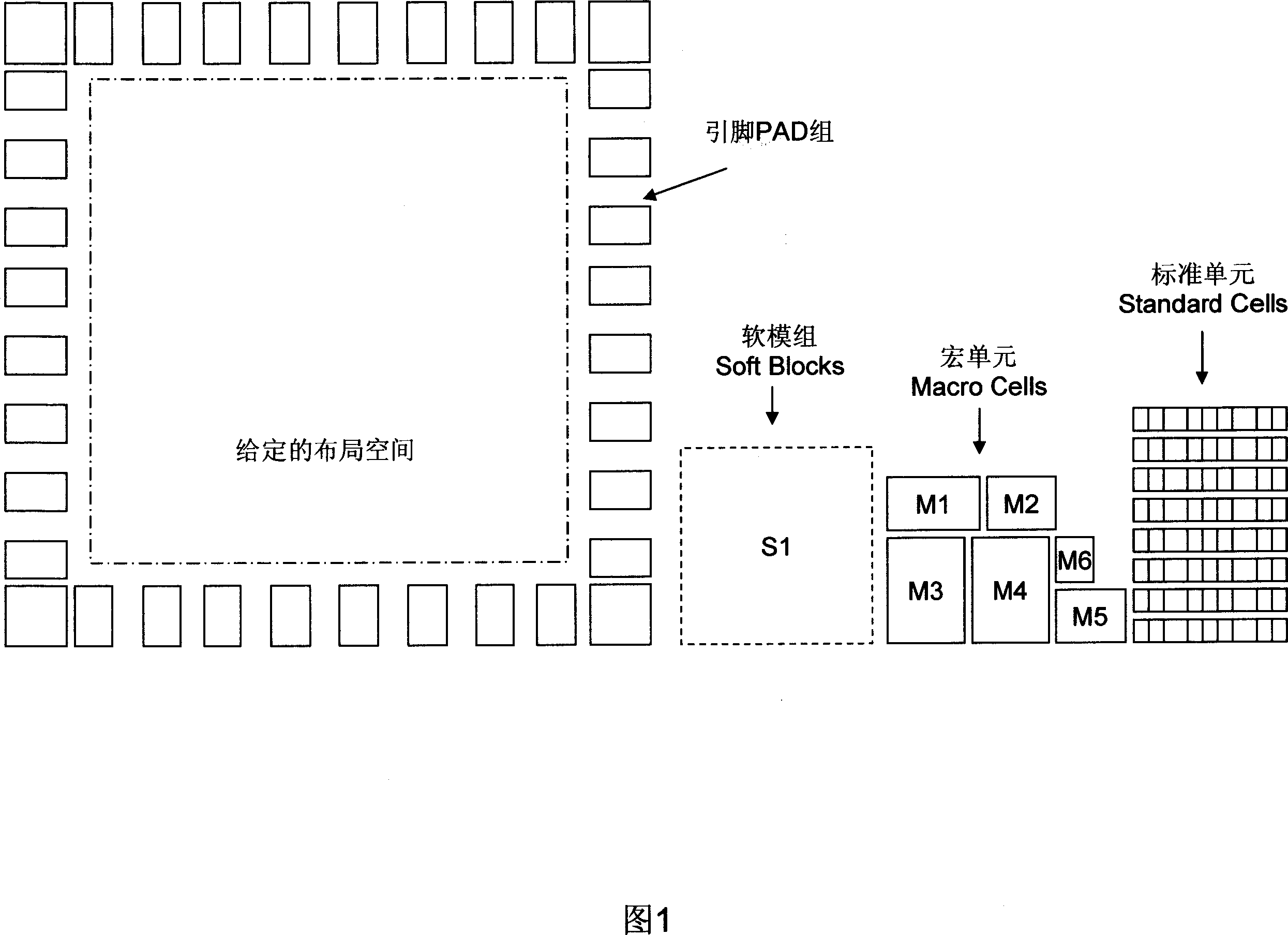

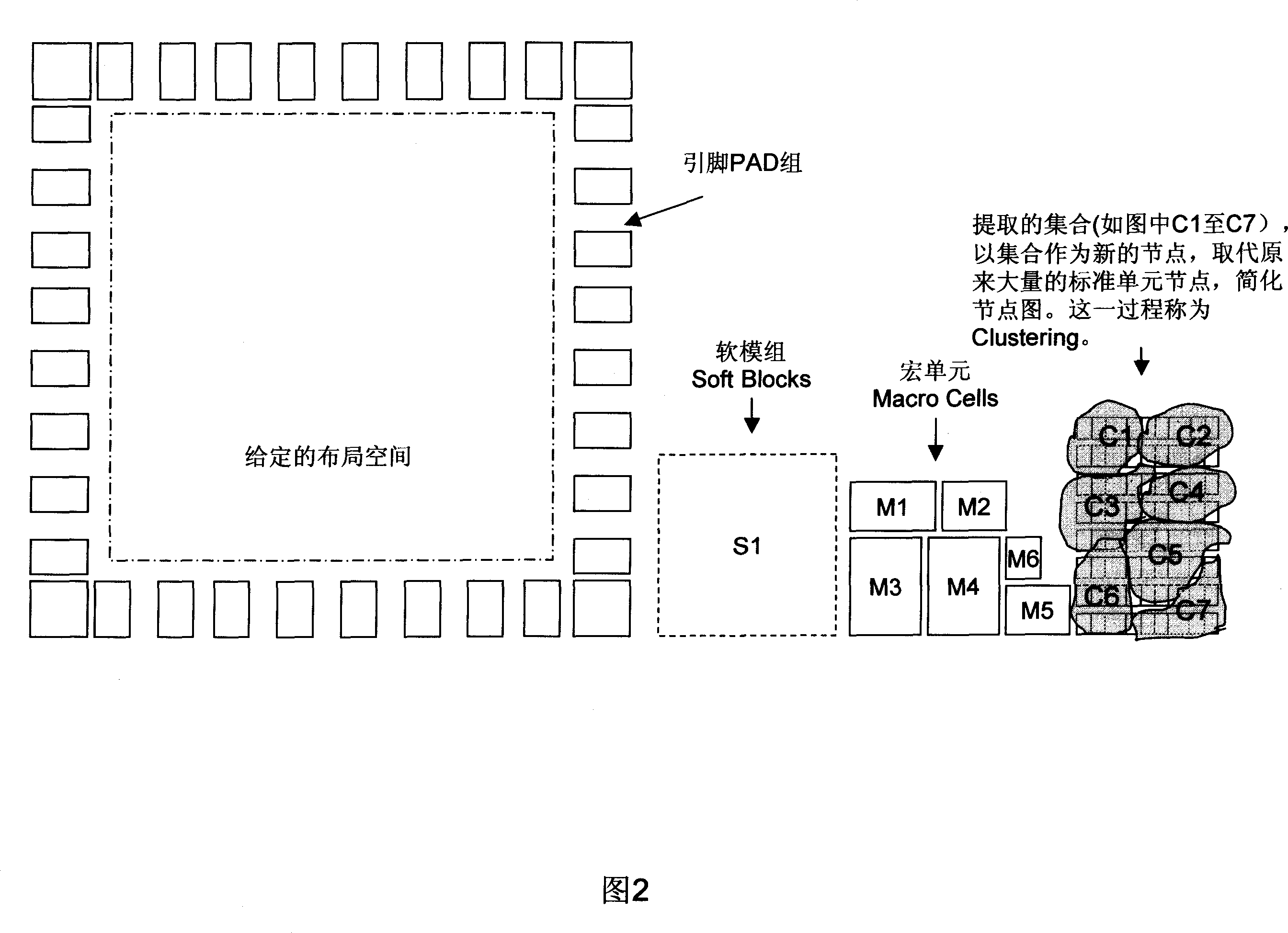

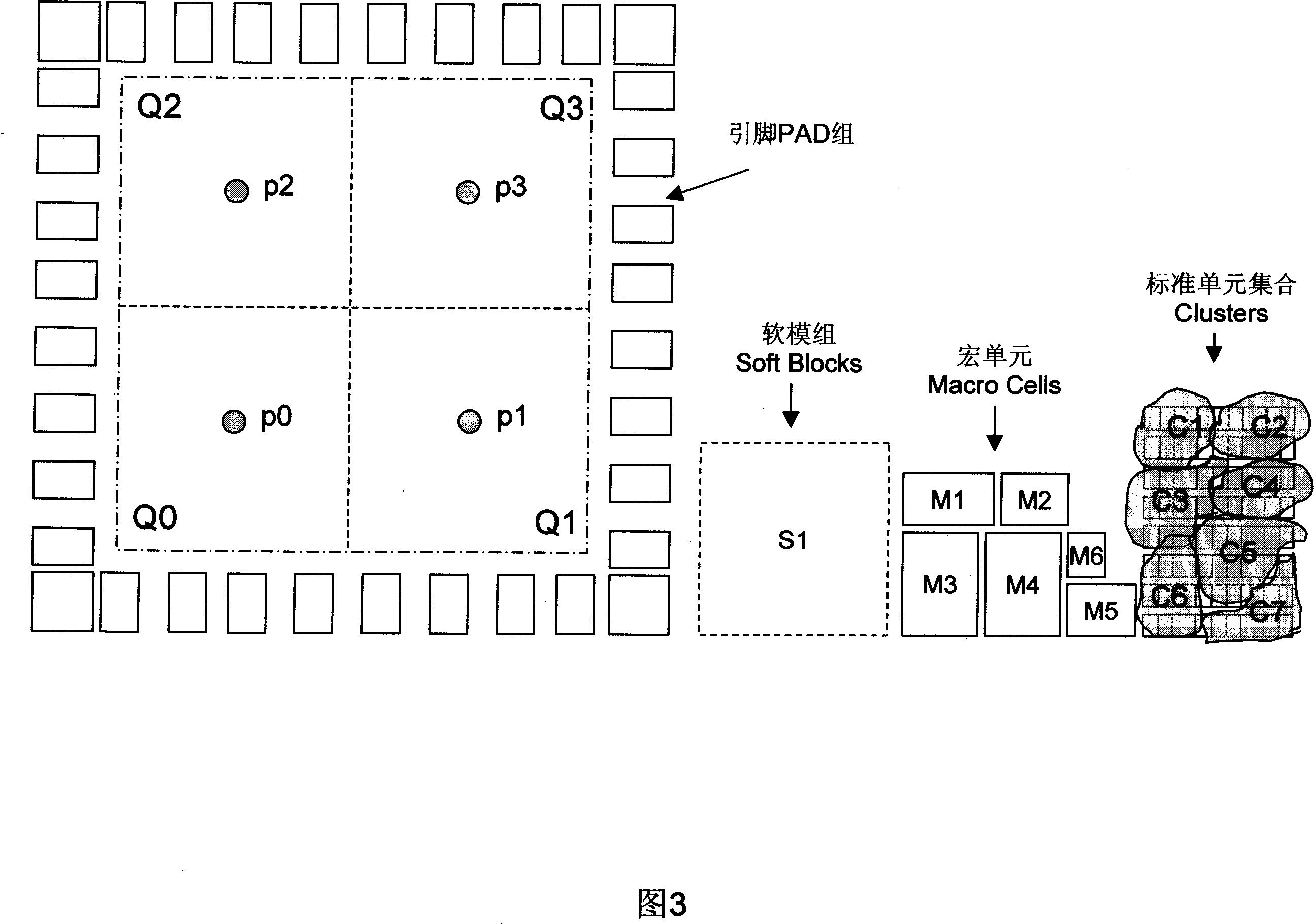

Module group, macrocell, standard unit synchronous layout convergence method and system for SoC integrated circuit automatic layout design

A standard cell, automatic layout technology, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as the insufficiency of algorithms and computing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0099] (1) Choose a computer with a memory of 512MB, a hard disk of 80GB, and an operating system of Linux Fedora 6.0;

[0100] (2) start the layout system of the present invention;

[0101] (3) Open an integrated circuit database in the layout system;

[0102](4) Start the "global layout" command, and the global layout will start running;

[0103] (5) After the layout process ends, a set of global layout diagrams will be generated;

[0104] (6) Select a global layout diagram to generate corresponding standard cell slots;

[0105] (7) Start the "Standard Cell Layout" command, and the layout of the standard cell will start;

[0106] (8) Waiting for the completion of the standard cell layout process, the complete layout process is completed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More