Method for dynamic reducing CPU power consumption

A power consumption and dynamic technology, applied in the field of CPU, can solve the problems of reducing the service life of equipment, reducing the reliability and service life of CPU, and increasing the maintenance cost of equipment providers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

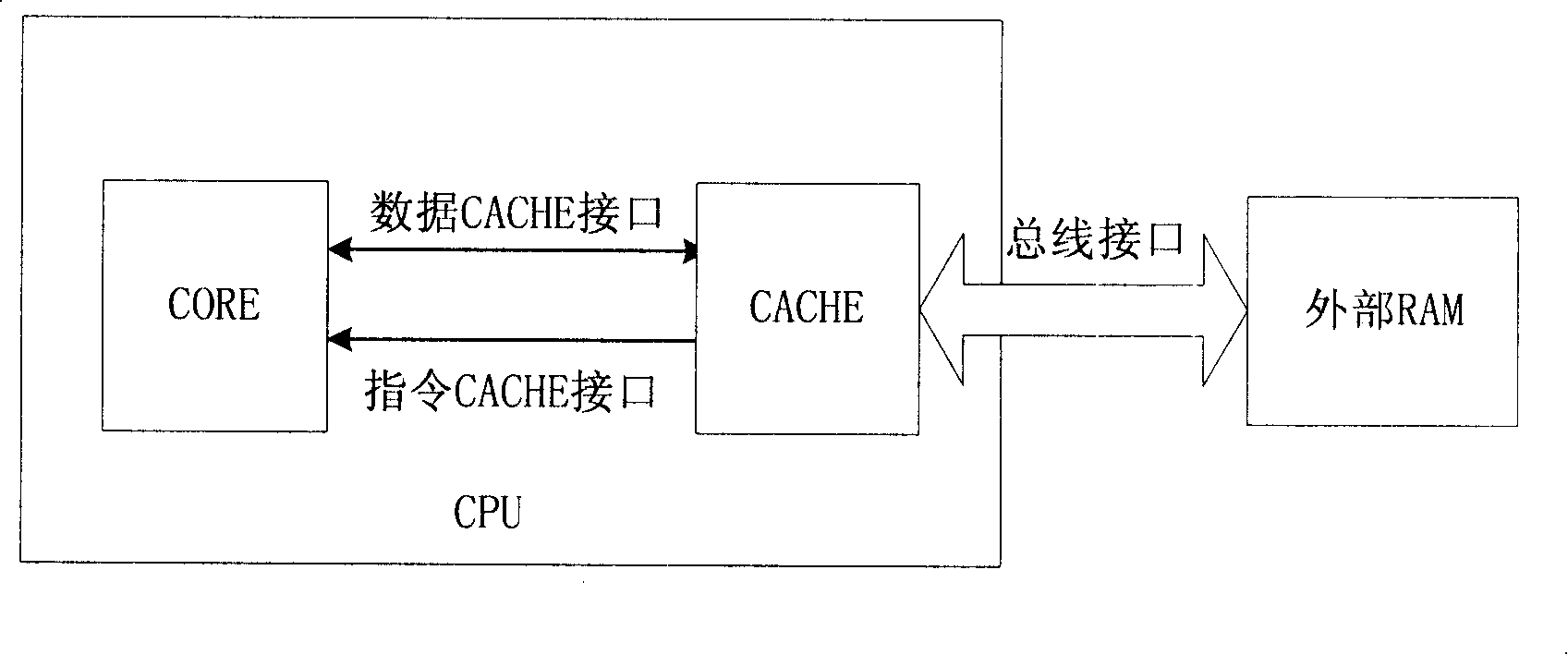

[0026] Such as figure 1 Shown is the simplest architecture diagram of the embedded CPU system in the field of mobile communication. The embedded CPU system in the field of mobile communication includes at least the processor core, cache and RAM, among which the cache is The high-speed cache of the interface between the processor core and peripherals. RAM is a volatile memory used to store program instructions or data in the CPU system.

[0027] The interface between the processor core and Cache is a high-speed interface. The processor core and Cache have interfaces with external RAM, but they are both lower-speed interfaces. The low-speed interface between the processor core and external RAM is formed. It is: when the Cache is closed, it is equivalent to a channel, which directly connects the processor core and the external RAM; when the Cache is open, it is a high-speed cache, which reads instructions or data from the external RAM and caches it in the Cache. For direct access by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More