Patents

Literature

57 results about "CPU power dissipation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Central processing unit power dissipation or CPU power dissipation is the process in which central processing units (CPUs) consume electrical energy, and dissipate this energy in the form of heat due to the resistance in the electronic circuits.

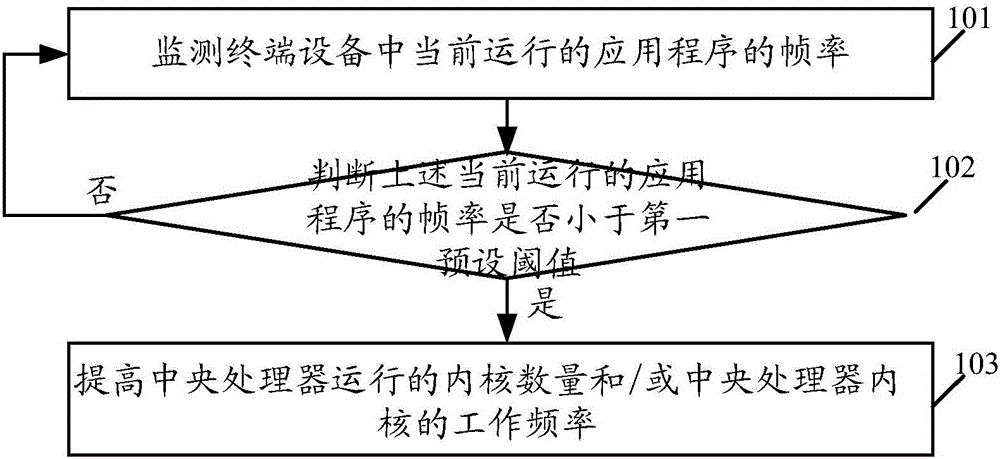

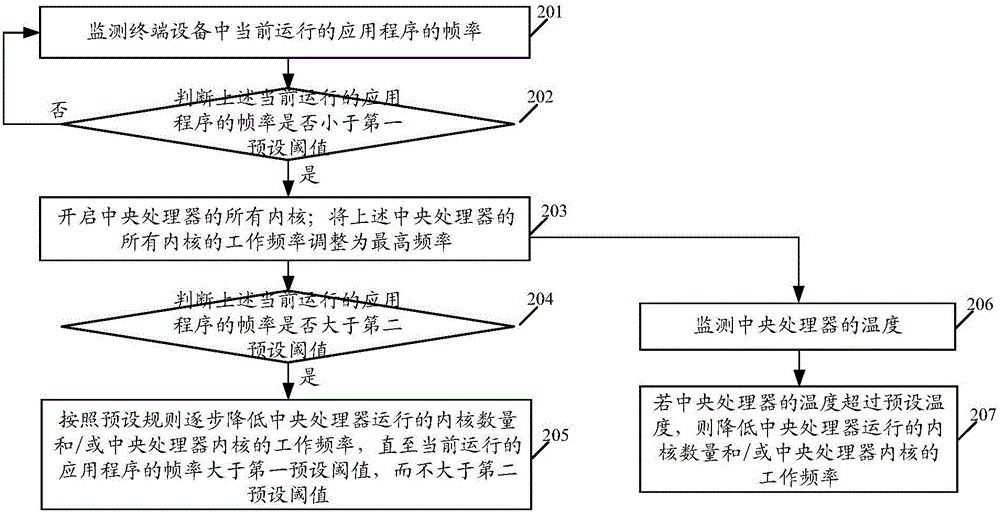

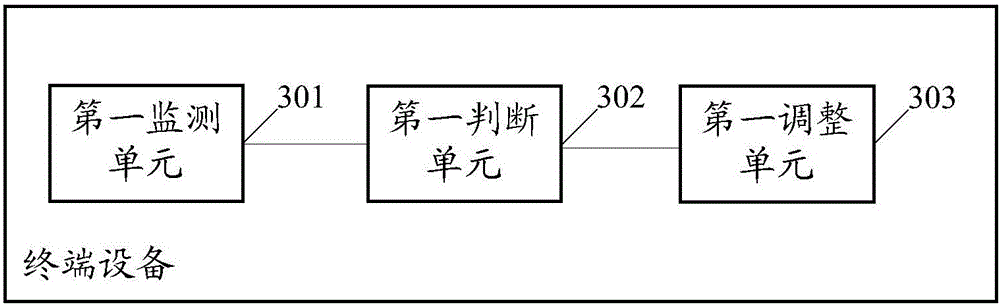

Control method for central processing unit and terminal equipment

ActiveCN106020990AIncrease the number of coresIncrease working frequencyResource allocationEnergy efficient computingTerminal equipmentCPU power dissipation

The embodiment of the invention discloses a control method for a central processing unit and terminal equipment, which are applied to the technical field of mobile communications. The method in the embodiment of the invention comprises the following steps of monitoring the frame rate of a currently-running application program in the terminal equipment; judging whether the frame rate of the currently-running application program is smaller than a first preset threshold or not; if the frame rate of the currently-running application program is smaller than the first preset threshold, improving the number of running kernels of the central processing unit and / or the working frequency of the kernels of the central processing unit. According to the embodiment of the invention, the power consumption of a CPU (Central Processing Unit) and the limitation of performance optimization are reduced.

Owner:YULONG COMPUTER TELECOMM SCI (SHENZHEN) CO LTD

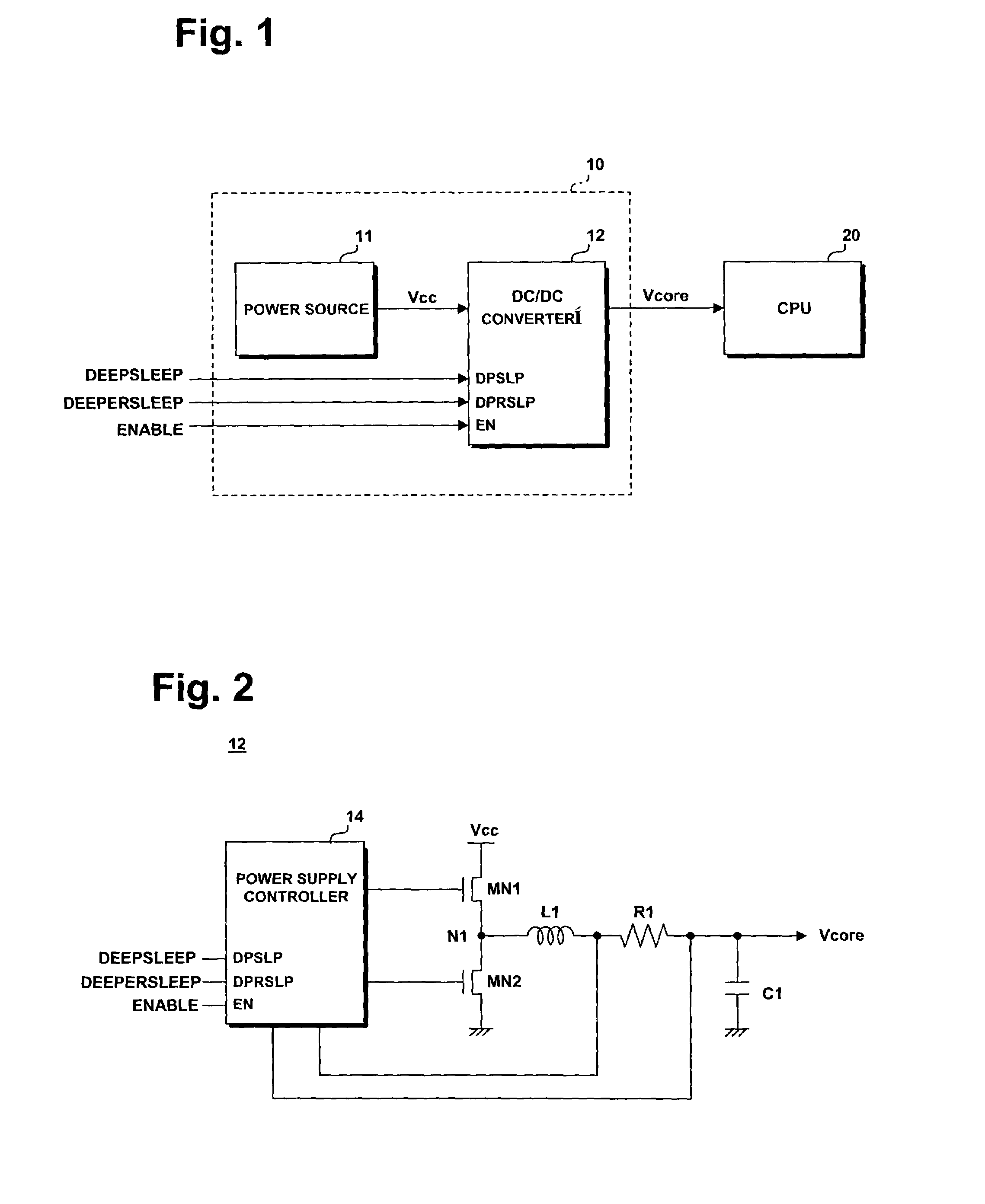

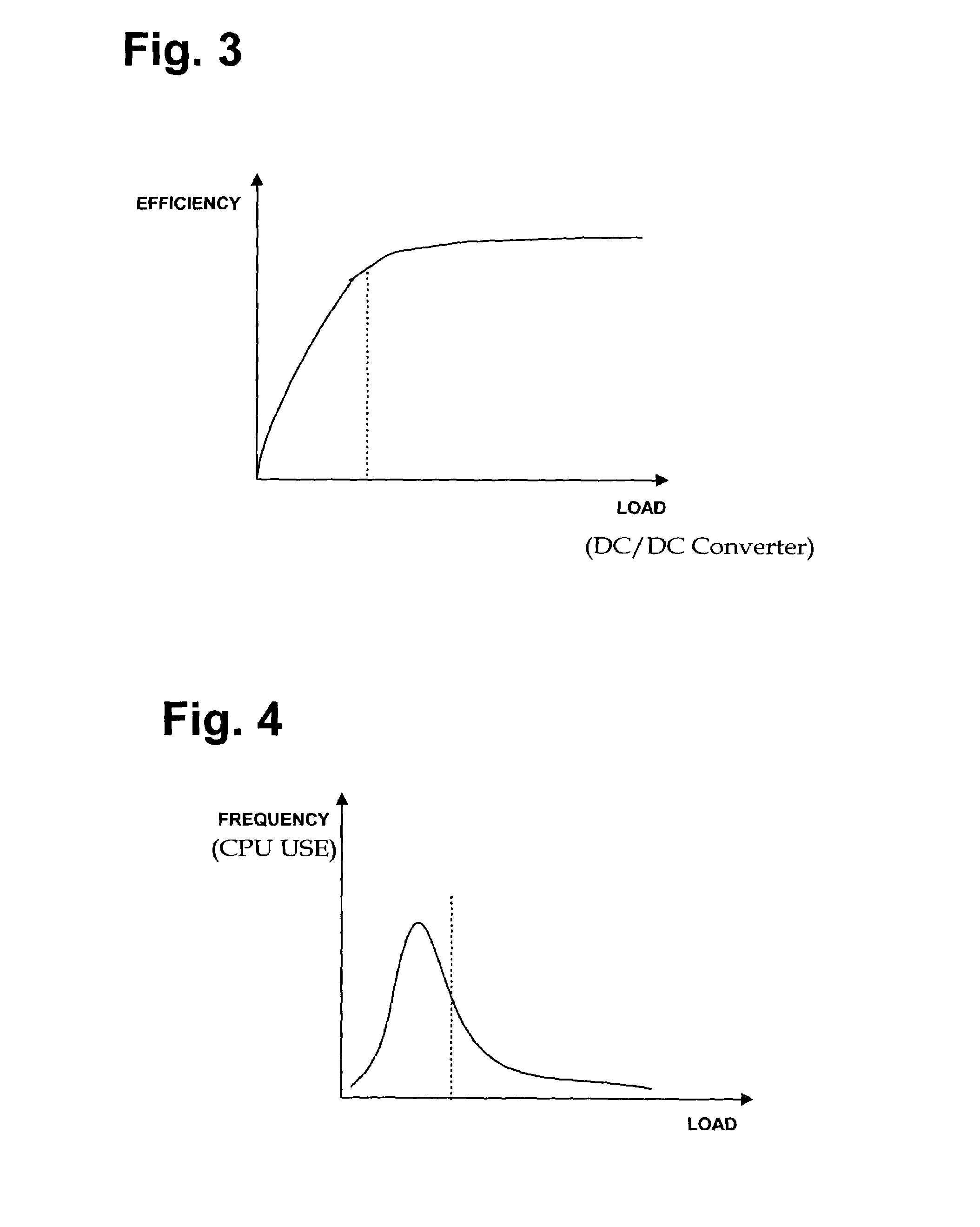

Power supply for central processing unit

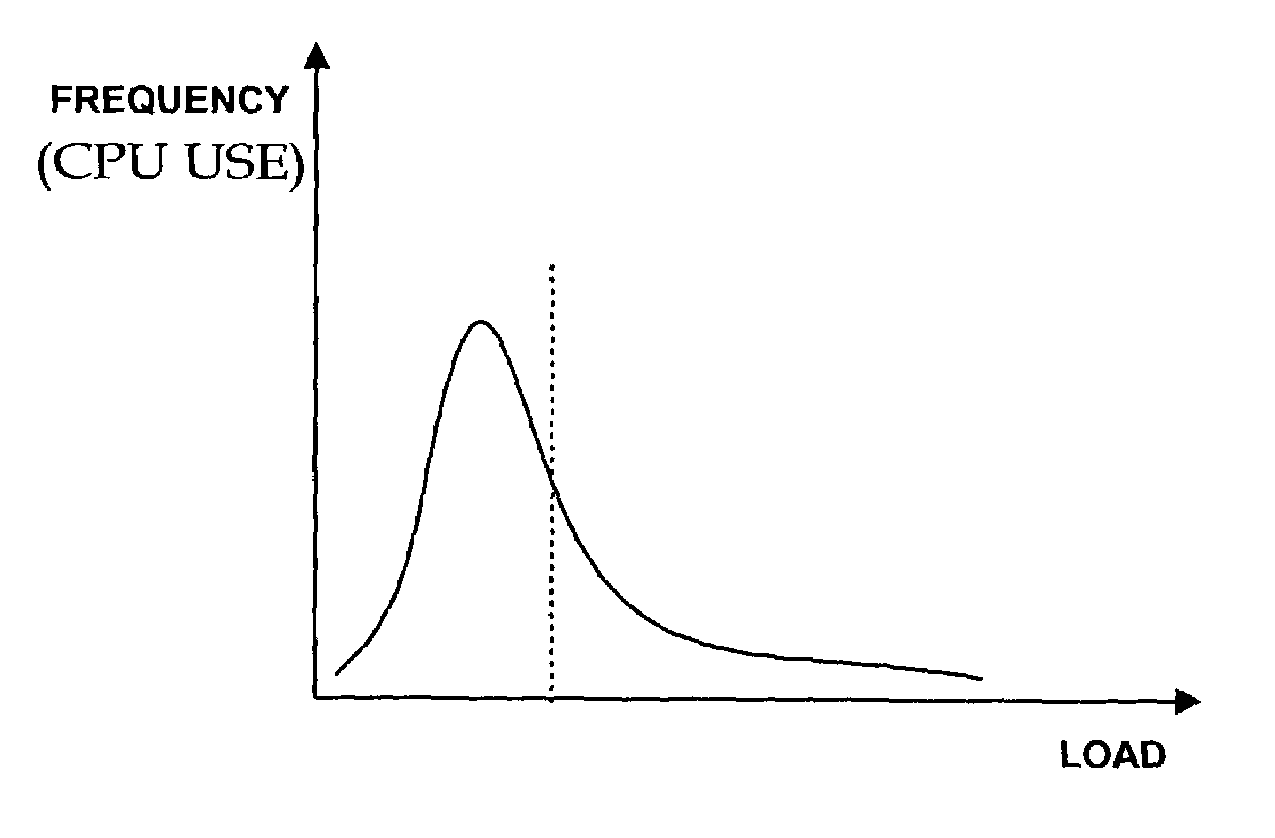

ActiveUS7203847B2Improve power efficiencyReduces and prevents efficiencyVolume/mass flow measurementPower supply for data processingLow activityLow load

A power supply and method for a central processing unit (CPU). The power can include a first power supply circuit such as a DC / DC converter for supplying a voltage of a first level to the CPU when the CPU is in a high activity mode, and a second power supply circuit such as an LDO regulator circuit for supplying a voltage of a second level lower than the first level to the CPU when the CPU is in a low activity mode. The second power supply circuit is preferably efficient when the CPU is in a low load or low activity mode. In such a power supply, when the CPU is in the low activity mode, the LDO regulator circuit is operated to reduce or prevent the efficiency from being degraded, reduce a CPU power consumption and extend a CPU battery lifetime.

Owner:LG ELECTRONICS INC

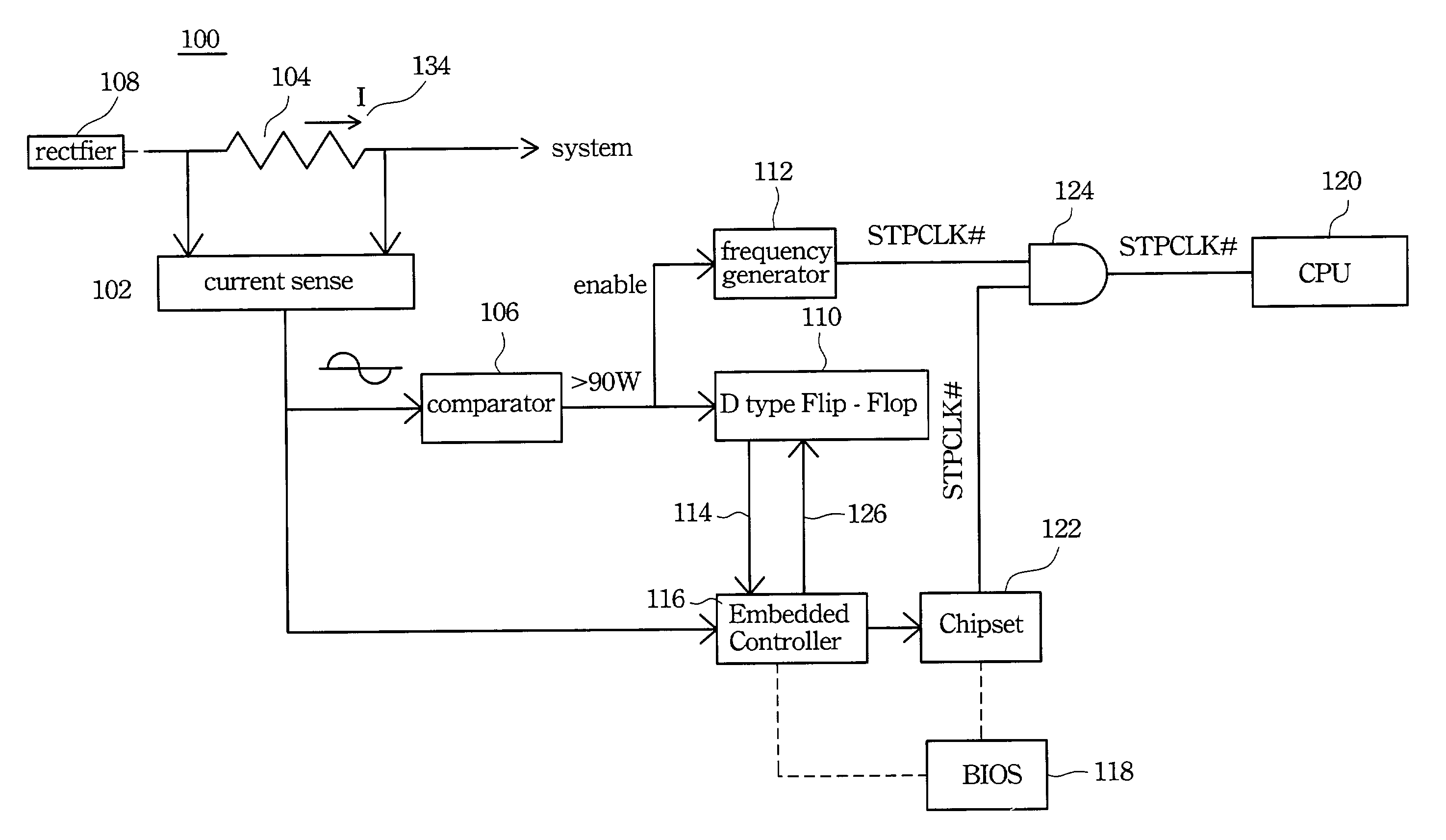

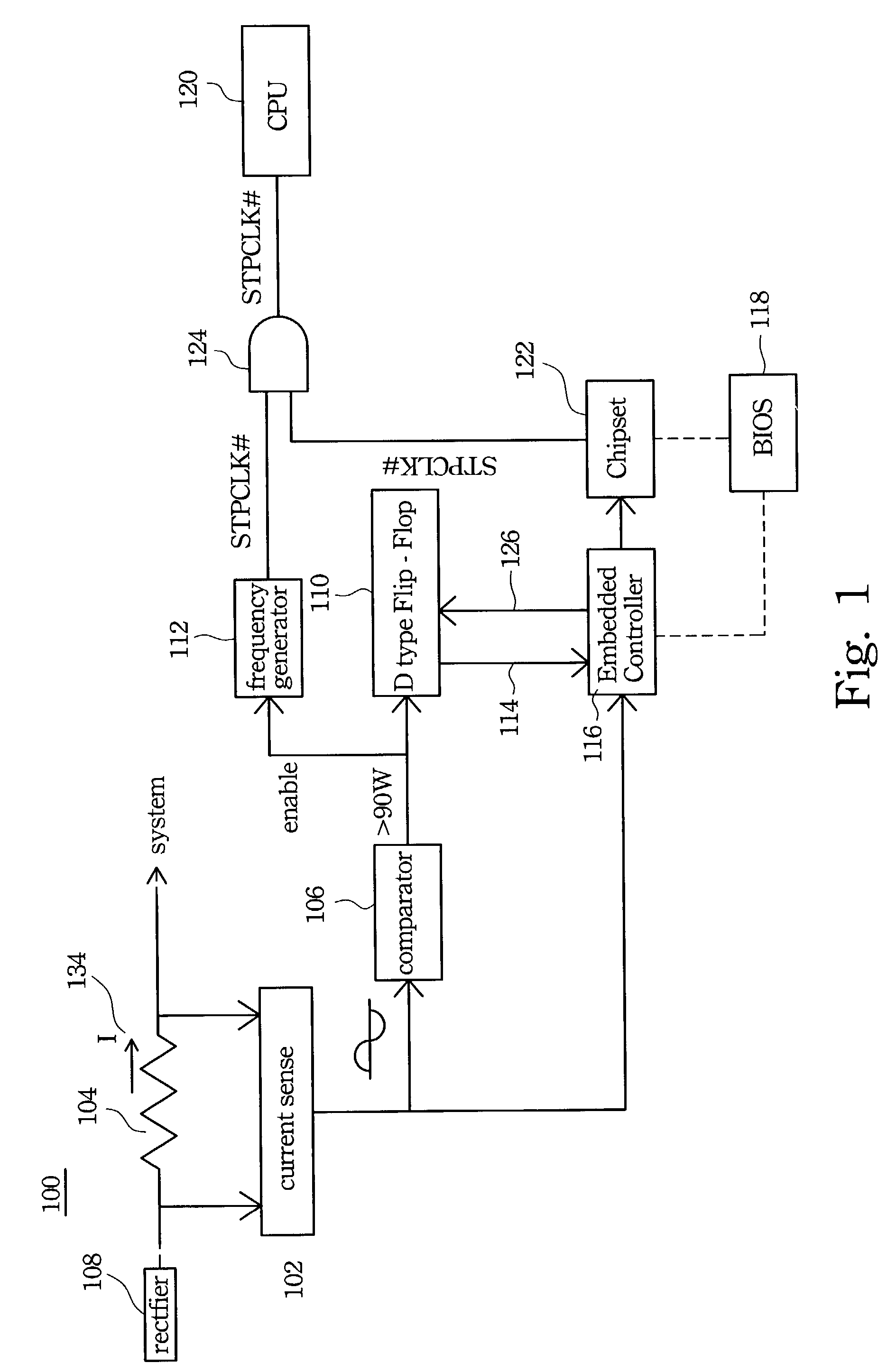

Apparatus for dynamically adjusting CPU power consumption

ActiveUS7010704B2Avoids sudden shut downIncrease loadEnergy efficient ICTVolume/mass flow measurementAsynchronous operationComputerized system

An apparatus for dynamically adjusting power consumption of a CPU in a computer system is described. A current flowing through the limiting resistor is detected and whether or not this current is larger than a predetermined current is determined. A warning signal is issued when the current is larger than this predetermined signal. The warning signal triggers the software framework and the hardware framework of the apparatus to issue an asynchronous operation frequency reduction instruction to the CPU of the computer system.

Owner:QUANTA COMPUTER INC

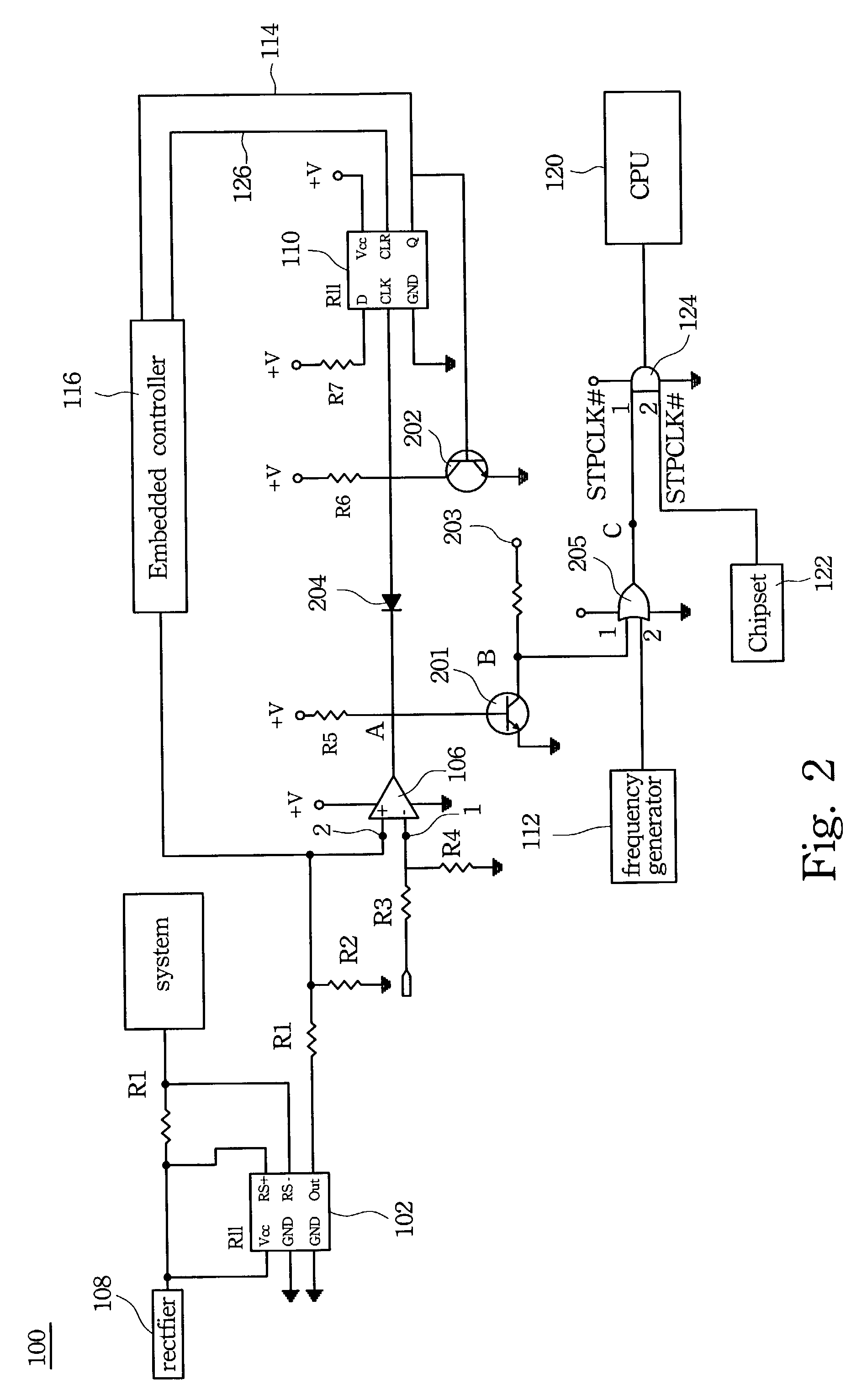

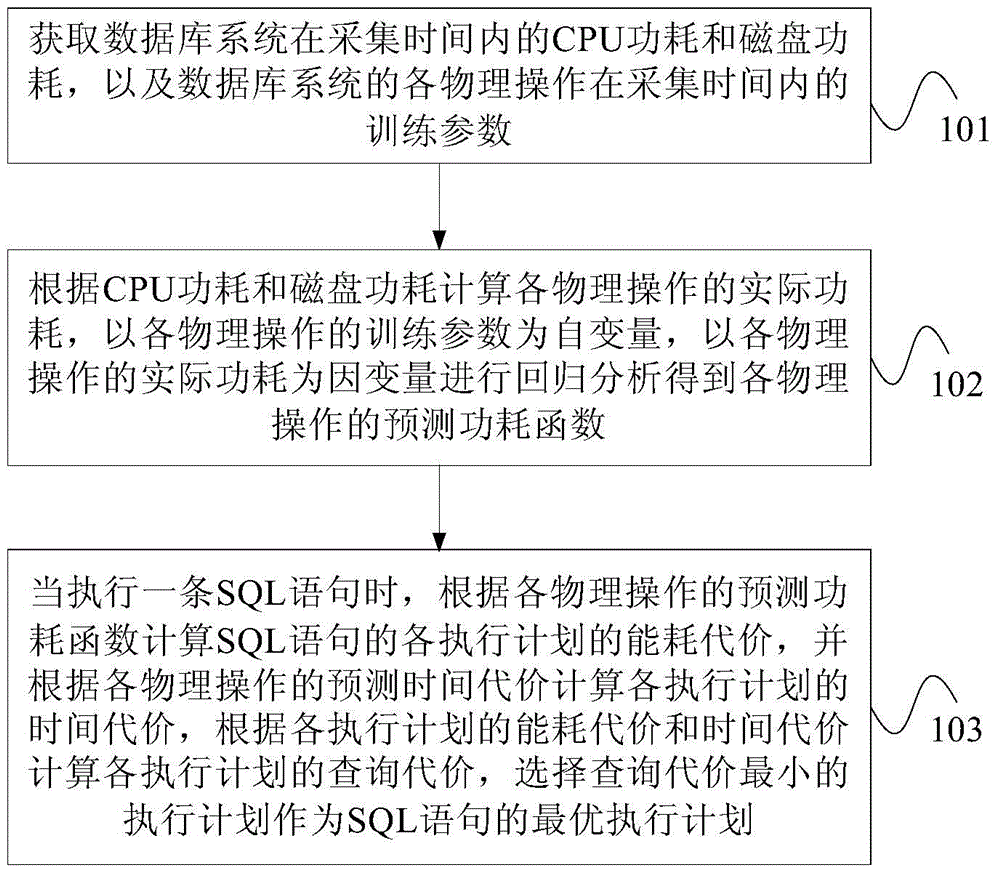

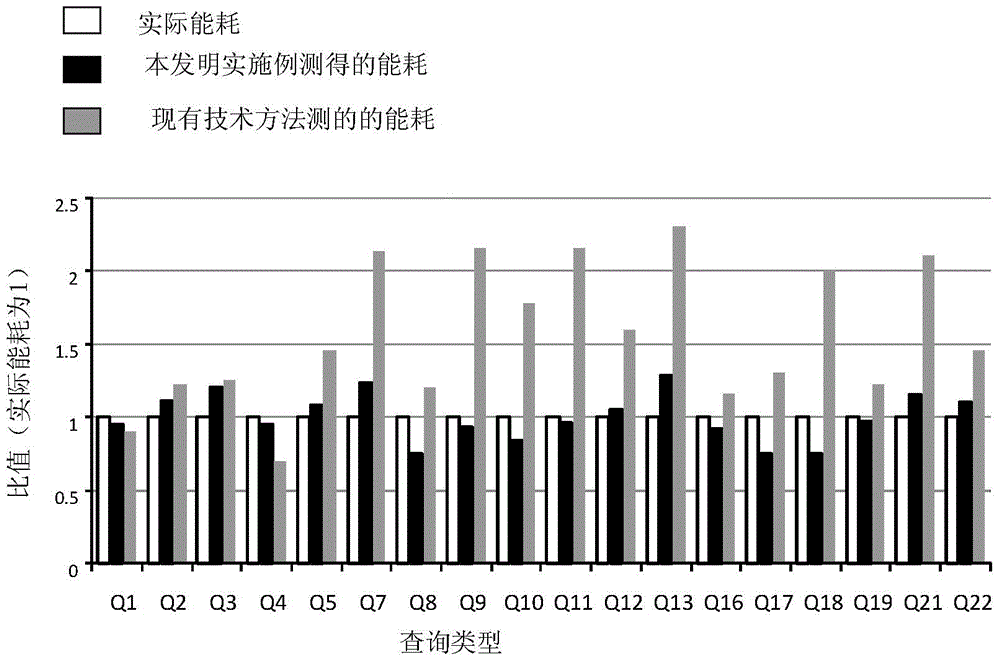

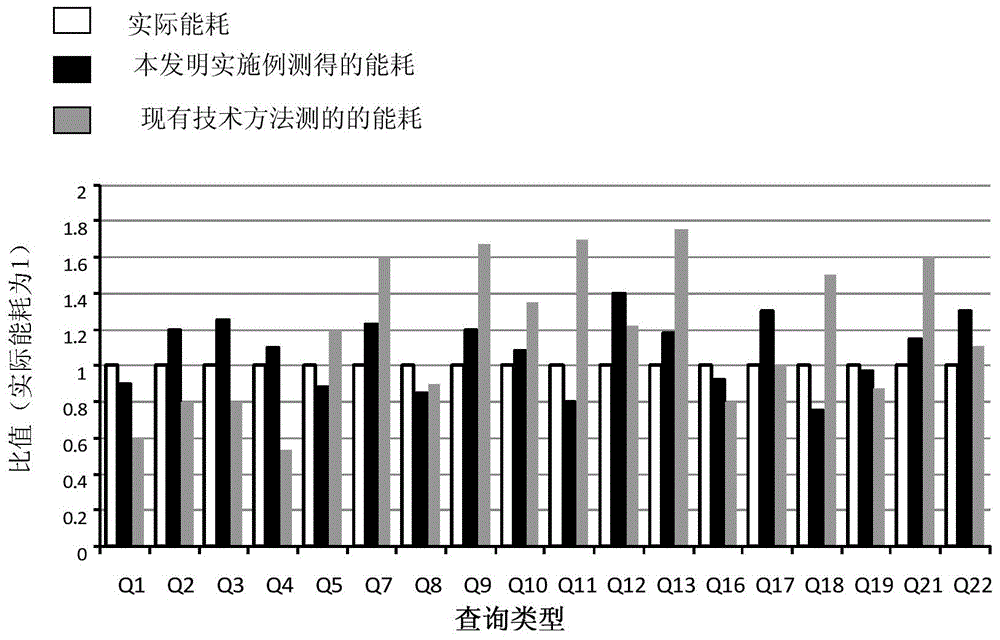

Database system query method, server and energy consumption test system

InactiveCN105243068AFlexible adjustment of energy consumptionPredict power consumption function accuratelyEnergy efficient computingSpecial data processing applicationsExecution planRegression analysis

Embodiments of the invention provide a database system query method, a server and an energy consumption test system. The method comprises: obtaining CPU power consumption and disk power consumption of a database system within an acquisition time and a training parameter of each physical operation of the database system within the acquisition time; according to the CPU power consumption and the disk power consumption, calculating actual power consumption of each physical operation, and performing regression analysis by taking the training parameter of each physical operation as an independent variable and the actual power consumption of each physical operation as a dependent variable to obtain a power consumption prediction function of each physical operation; and calculating the energy consumption cost of each execution plan of an SQL statement according to the power consumption prediction function of each physical operation. According to the method, the power consumption prediction function of each physical operation is obtained with the regression analysis method, so that the power consumption prediction function of each physical operation is more accurate. In addition, an adjustment factor is introduced to adjust the energy consumption cost and the time cost of a database, so that the energy consumption of the database system can be flexibly adjusted.

Owner:HUAWEI TECH CO LTD +1

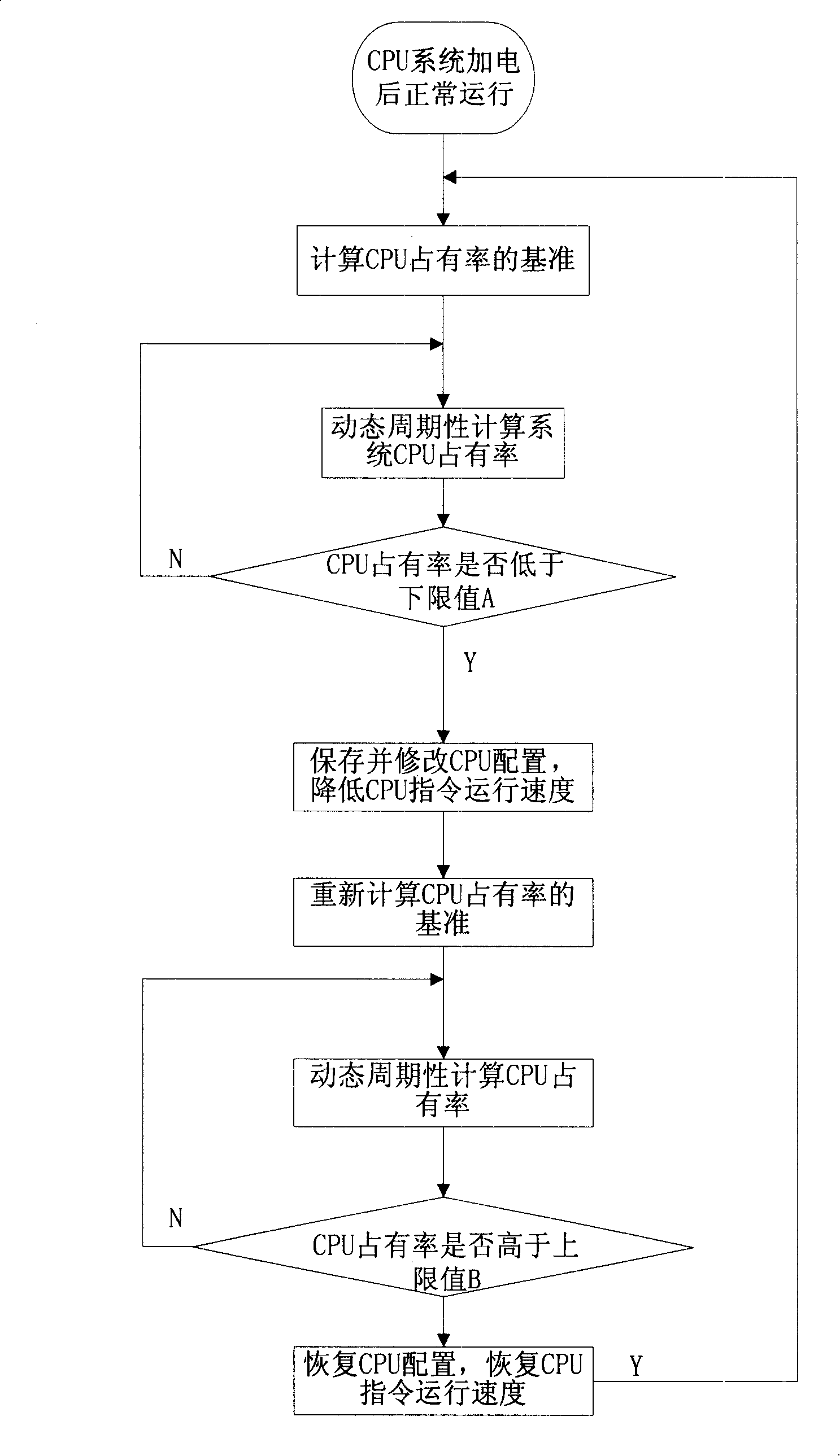

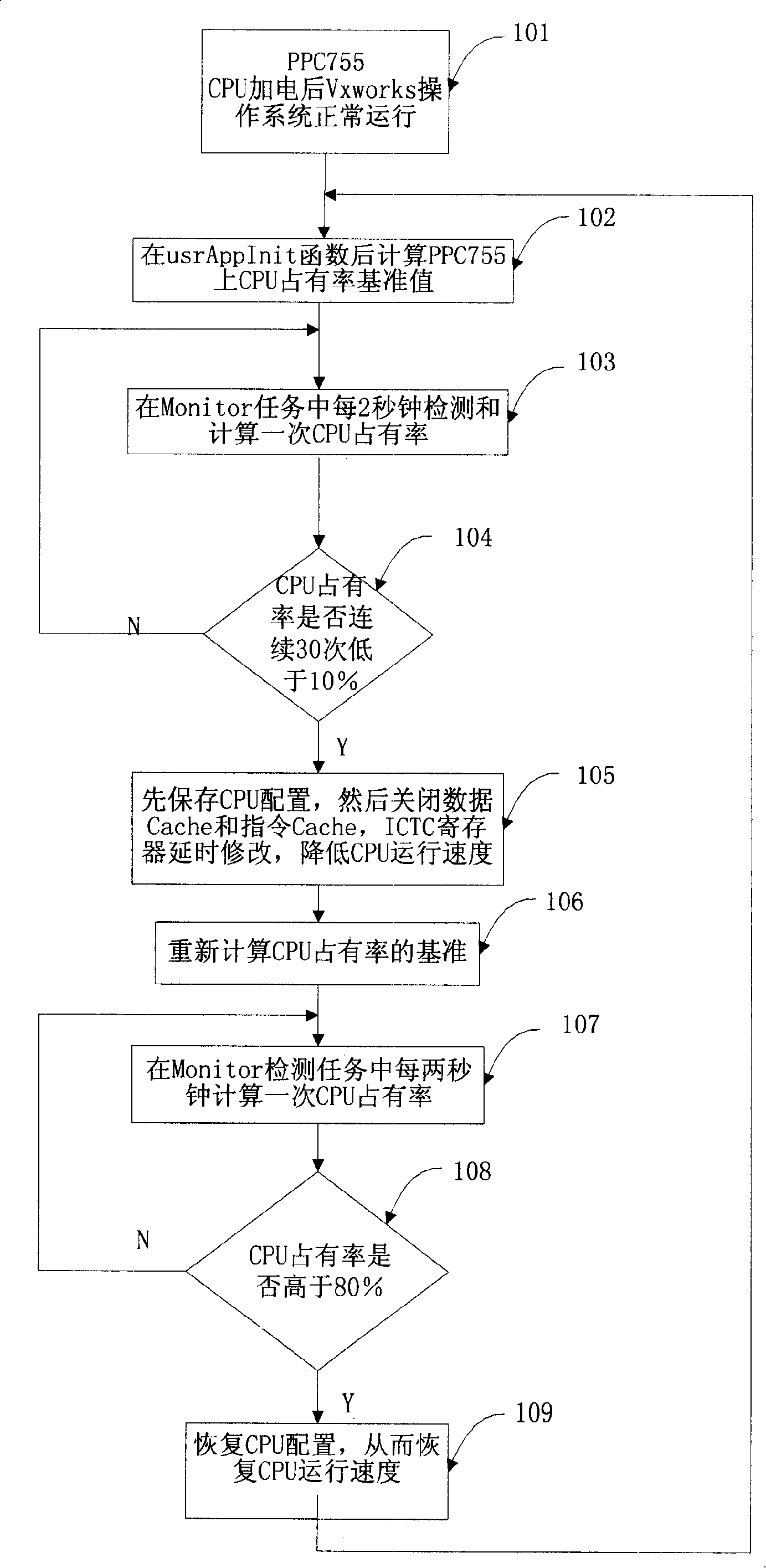

Method for dynamic reducing CPU power consumption

ActiveCN101162405ASlow downReduce heat dissipationPower supply for data processingLower limitSingle plate

The invention discloses a method for dynamically reducing the CPU power consumption; the method is invented aiming at resolving the problem existing in prior art that the CPU power consumption can not be adjusted based on the service processing capacity. The method for dynamically reducing the CPU power consumption can dynamically adjust the directive operation speed of the CPU according to the CPU occupancy. When the CPU works, if the CPU occupancy is lower than the set lower limit value, the directive operation speed of the CPU is lowered; if the CPU occupancy is higher than the set upper limit value, the directive operation speed of the CPU is increased; wherein the adjustment on the directive operation speed is realized by opening or closing the data cache interface and the directive cache interface and changing the transmission delay. The invention is mainly applied to the CPU design of the embedded system, particularly the CPU design of the base station veneer in the communication field.

Owner:ZTE CORP

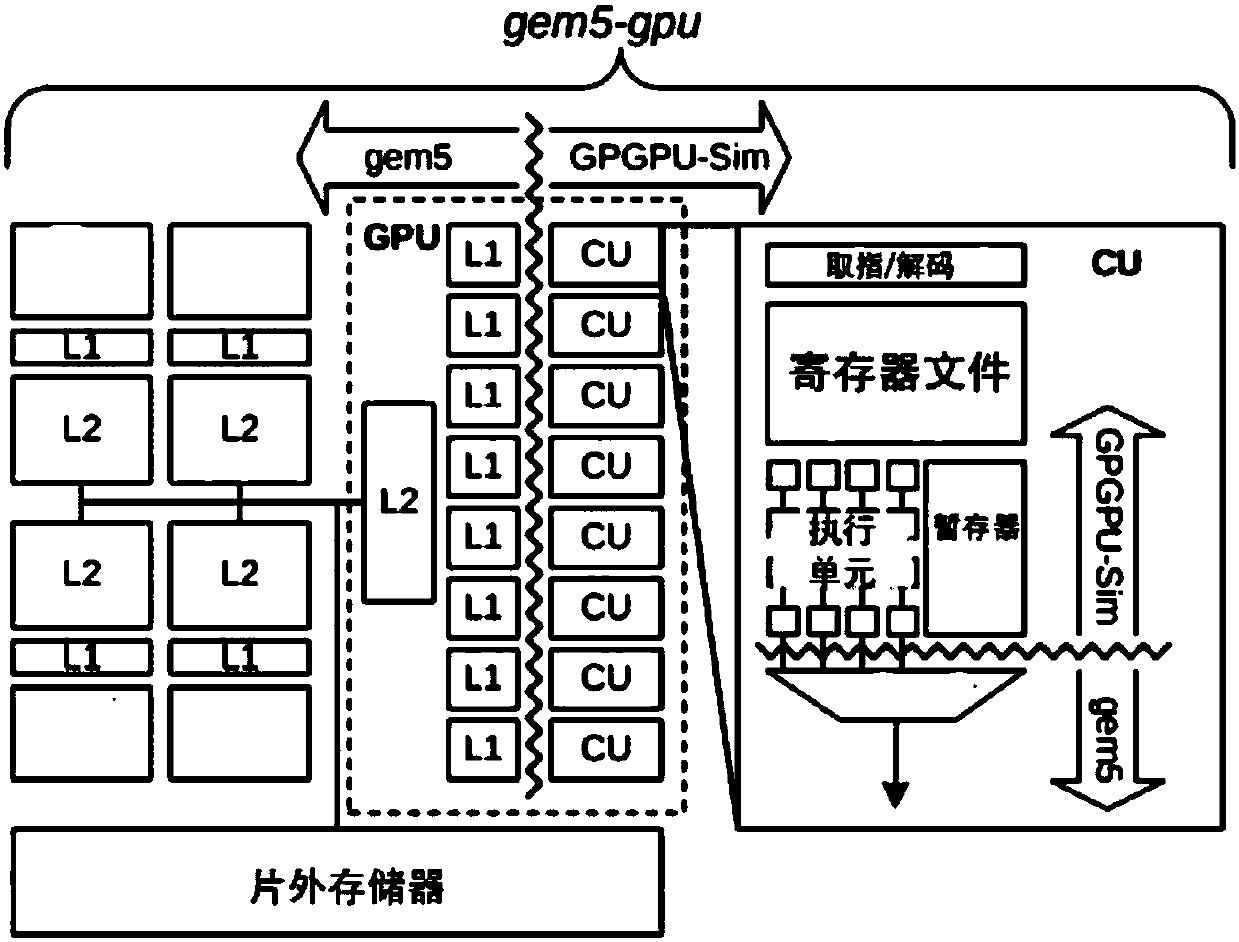

Heterogeneous multi-kernel power capping method through coordination of DVFS and task mapping

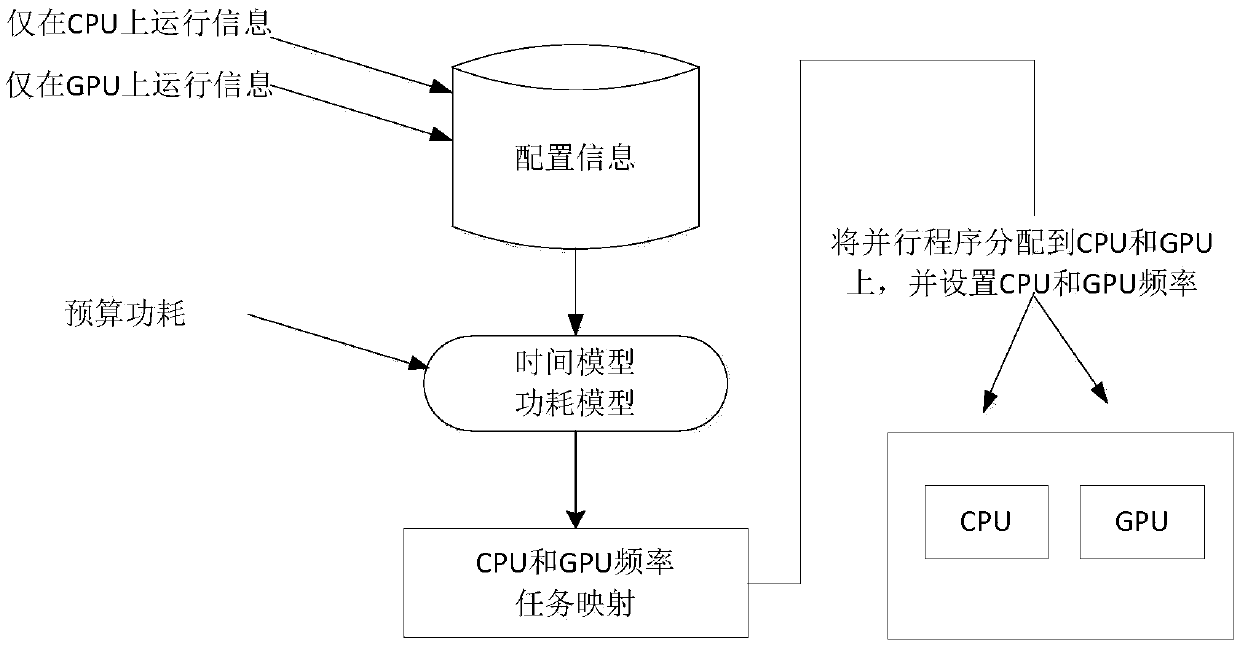

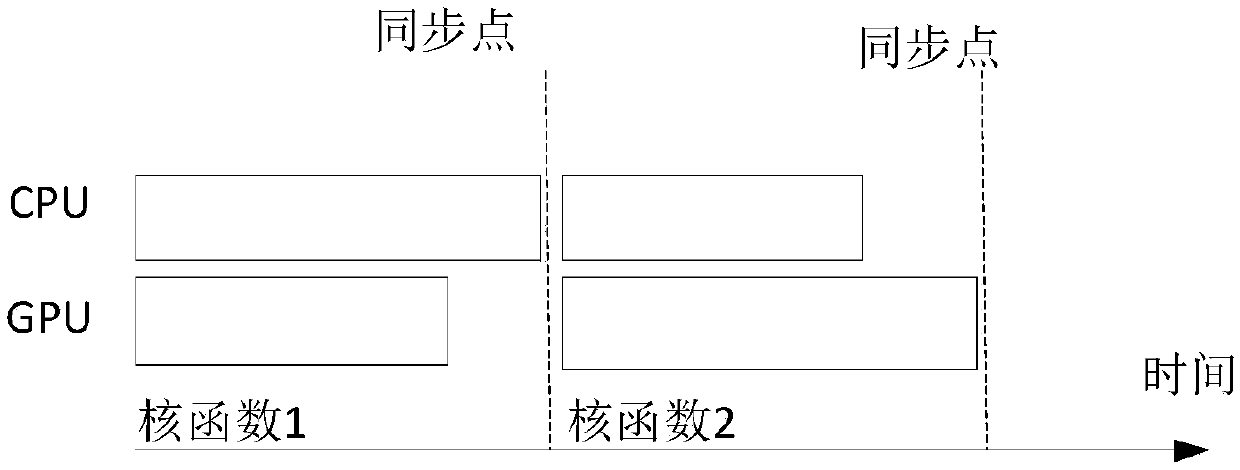

InactiveCN107861606AGuaranteed performanceTake advantage of computing powerPower supply for data processingGreedy algorithmParallel computing

The invention discloses a heterogeneous multi-kernel power capping method through coordination of DVFS and task mapping. The method comprises the steps that firstly, computational node power consumption, CPU power consumption and GPU power consumption scripts can be measured after program execution is completed for a heterogeneous system, then, selected parallel test benchmark programs are modified for obtaining the execution time of different kernel functions; different frequencies are set for a CPU and a GPU, application programs are operated only on the CPU and the GPU, detailed operation information is obtained and comprises the total execution time, the execution time of each kernel function, computational node power consumption, CPU power consumption and GPU power consumption; on thebasis of the operation information, a predicted model is designed and includes a predicted execution time model and a power consumption model; finally, on the basis of the predicted model, system power consumption and execution time under different CPU frequencies, GPU frequencies and task distribution schemes are obtained to be filled in a configuration table, and according to an improved greedyalgorithm, the best configuration scheme is found. By adopting the heterogeneous multi-kernel power capping method, the system power consumption budget is limited while the system performance can beimproved.

Owner:BEIJING UNIV OF TECH

Clustering-based energy-saving scheduling method in cluster environment

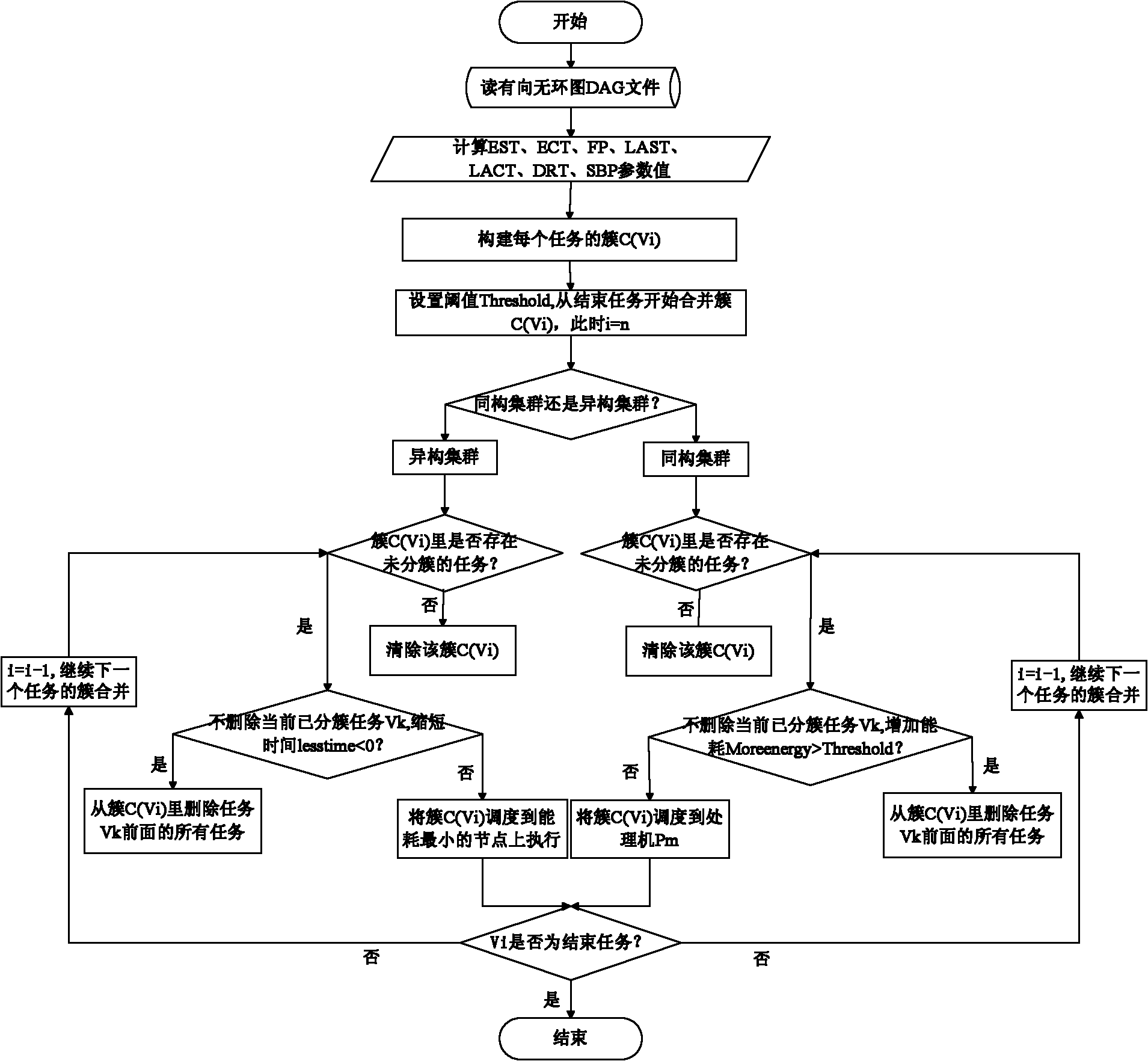

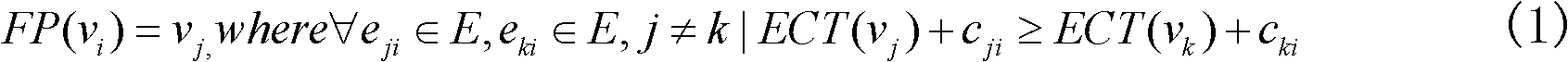

InactiveCN102231122AGuaranteed performanceReduce energy consumptionEnergy efficient ICTResource allocationParallel computingMerger process

The invention discloses a clustering-based energy-saving scheduling method in a cluster environment, which comprises the following steps of: reading a directed acyclic graph (DAG) file of a parallel task, constructing a cluster corresponding to each task, merging clusters, and mapping the clusters to complete scheduling from the clusters to a processor. A threshold is set according to performance and energy consumption emphasis degree of a cluster system and characteristics of central processing unit (CPU) power consumption and network power consumption in the system, the increased computing energy consumption and reduced communication energy consumption of a current non-clustered task are weighed in the process of merging the clusters, and whether to delete the clustered task is determined so as to control the system performance, the CPU energy consumption and network communication energy consumption. The requirements on performance and energy consumption of the cluster system are comprehensively considered, the performance, the CPU energy consumption and the network communication energy consumption are balanced by a cluster scheduling method, the total energy consumption of the system is reduced on the premise of guaranteeing the system performance, and the method is suitable for scheduling the parallel task based on energy optimization in the cluster system environment.

Owner:WUHAN UNIV OF TECH

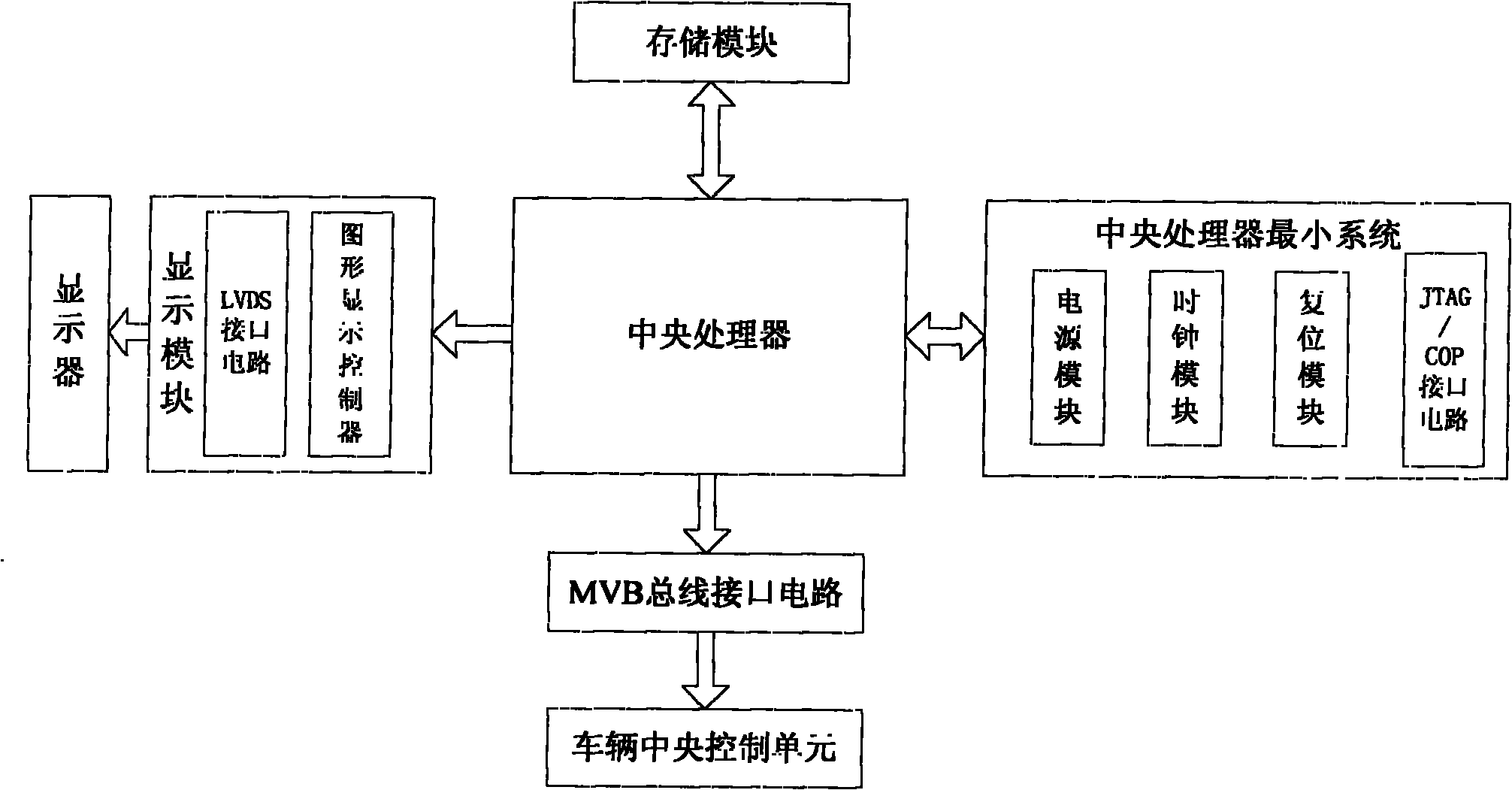

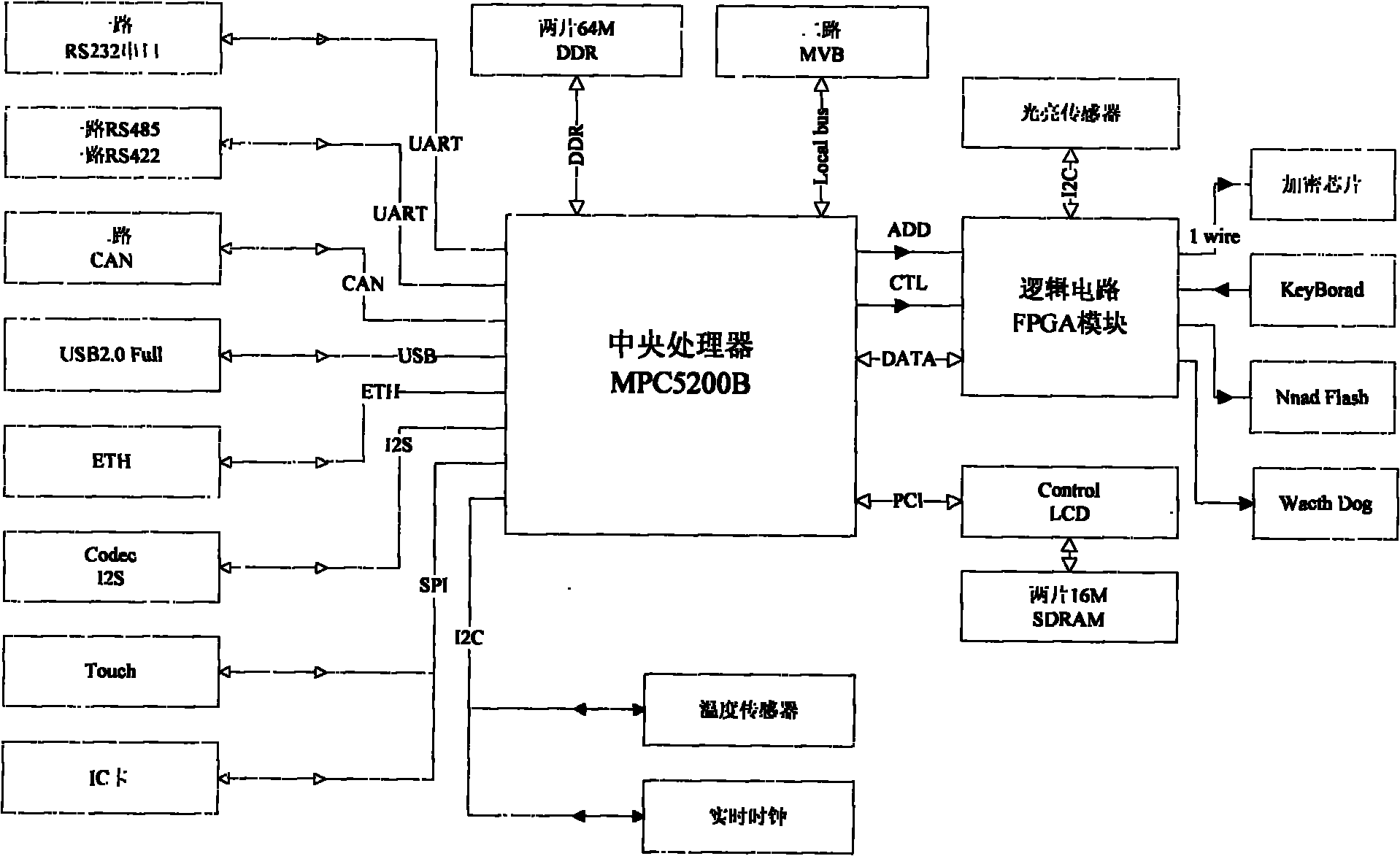

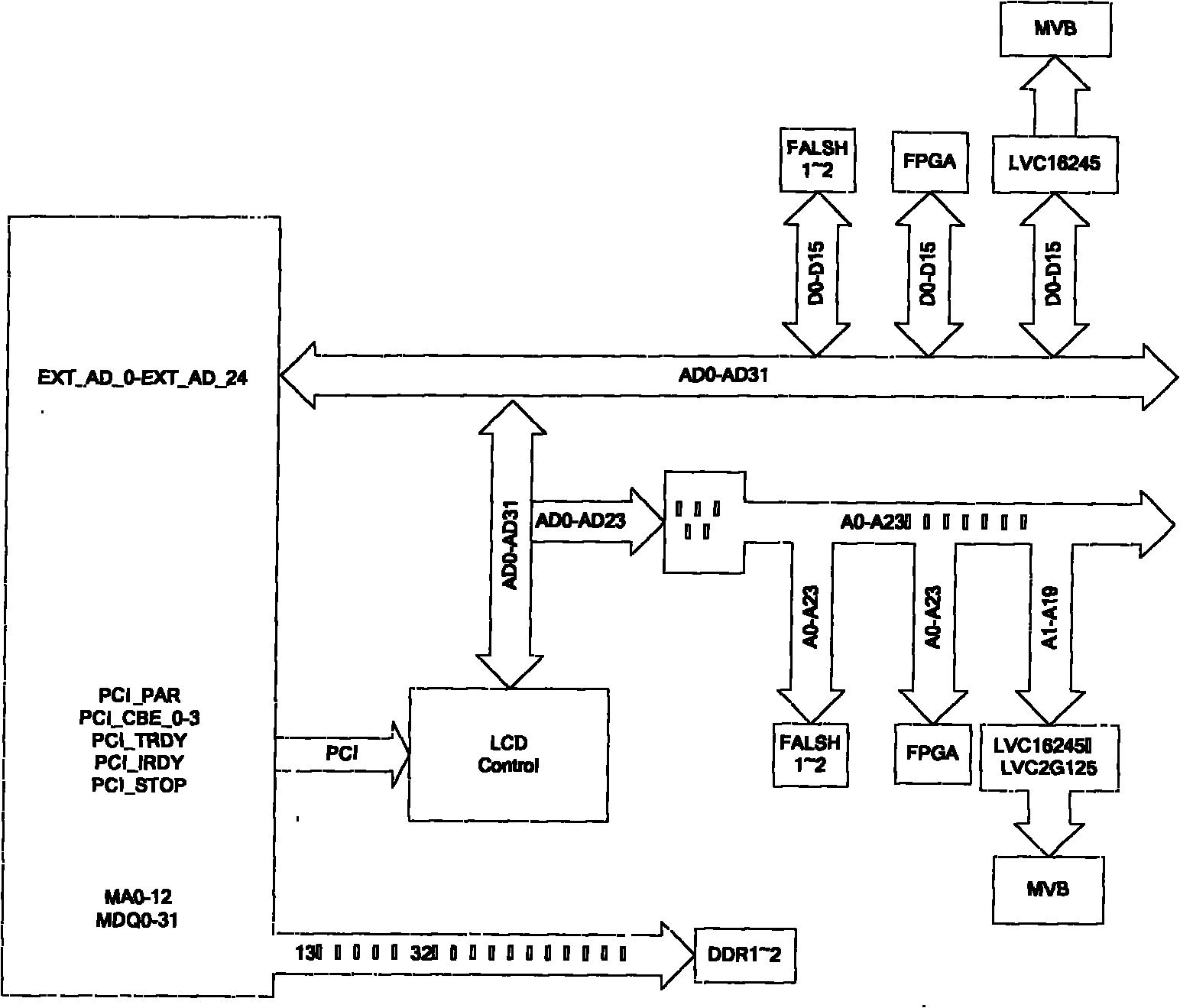

Man-machine interaction unit device

InactiveCN101853051AImprove stabilityReduce power consumptionDigital data processing detailsDisplay deviceJoint Test Action Group

The invention discloses a man-machine interaction unit device, which comprises a central processing unit, a central processing unit minimum system module, a storage module, a display module and an MVB bus interface circuit, wherein the central processing unit minimum system module comprises a power module, a clock module, a reset module and a JTAG / COP interface circuit; the central processing unit is connected with the storage module and the central processing unit minimum system module; the central processing unit expands the MVB bus interface circuit through an external bus and communicates with a vehicle central control unit through an MVB bus; the display module comprises a graphics display controller; and the central processing unit is connected with a display through the graphics display controller, and is an industrial processor of Freescale Company. Through the device, CPU power consumption and system heating are effectively reduced, the stability of the man-machine interaction unit device is improved, the CPU computing power is greatly improved, and the product life cycle is prolonged.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

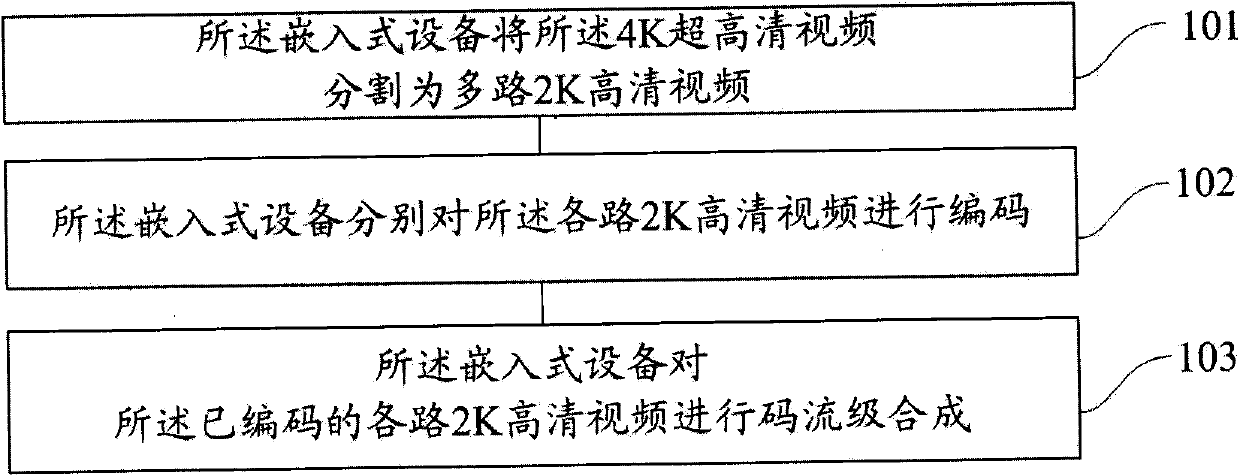

Coding method and coding system for embedded device-oriented 4K ultra-high-definition video

InactiveCN104219527AReduce power consumptionEasy to deal withDigital video signal modificationCPU power dissipationHigh-definition video

The embodiment of the invention provides a coding method and a coding system for an embedded device-oriented 4K ultra-high-definition video. The method comprises the following steps that: an embedded device segments the 4K ultra-high-definition video into a plurality of paths of 2K high-definition videos; the embedded device codes each path of the 2K high-definition videos; the embedded device carries out code stream-level synthesis on each of the coded 2K high-definition videos. The coding method and the coding system provided by the embodiment of the invention are used for lowering cost and CPU power consumption, and have the characteristics of real-time performance, stability and the like.

Owner:广州盈可视电子科技有限公司

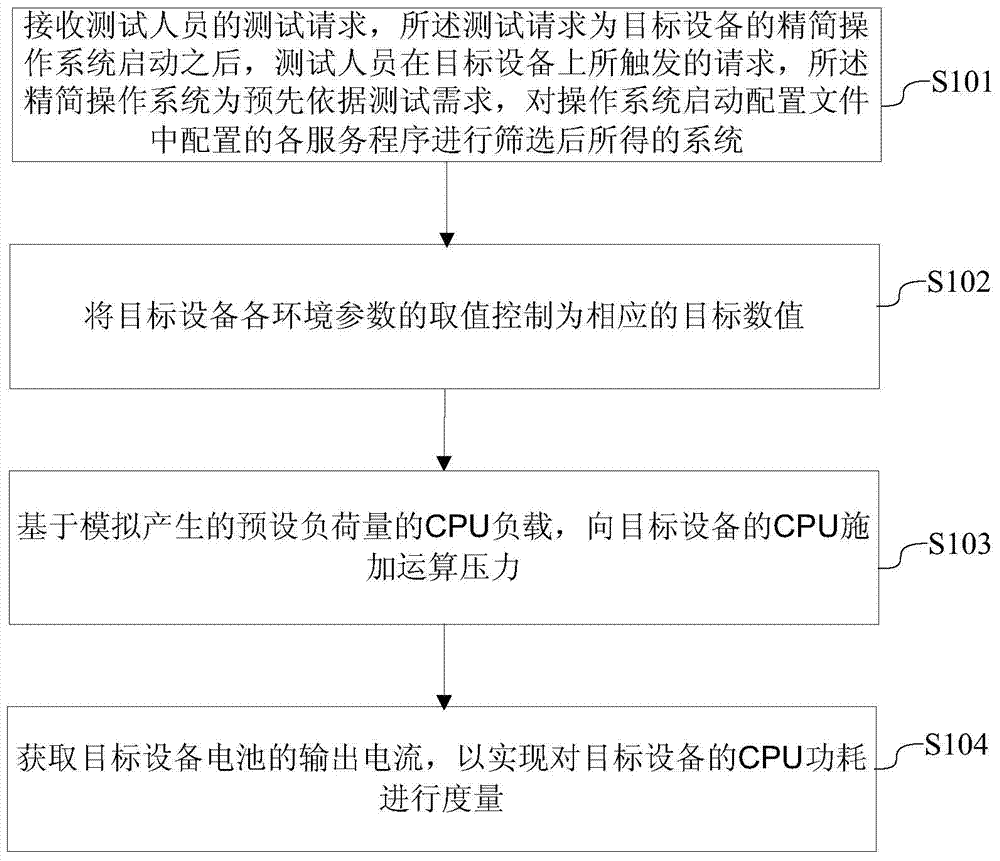

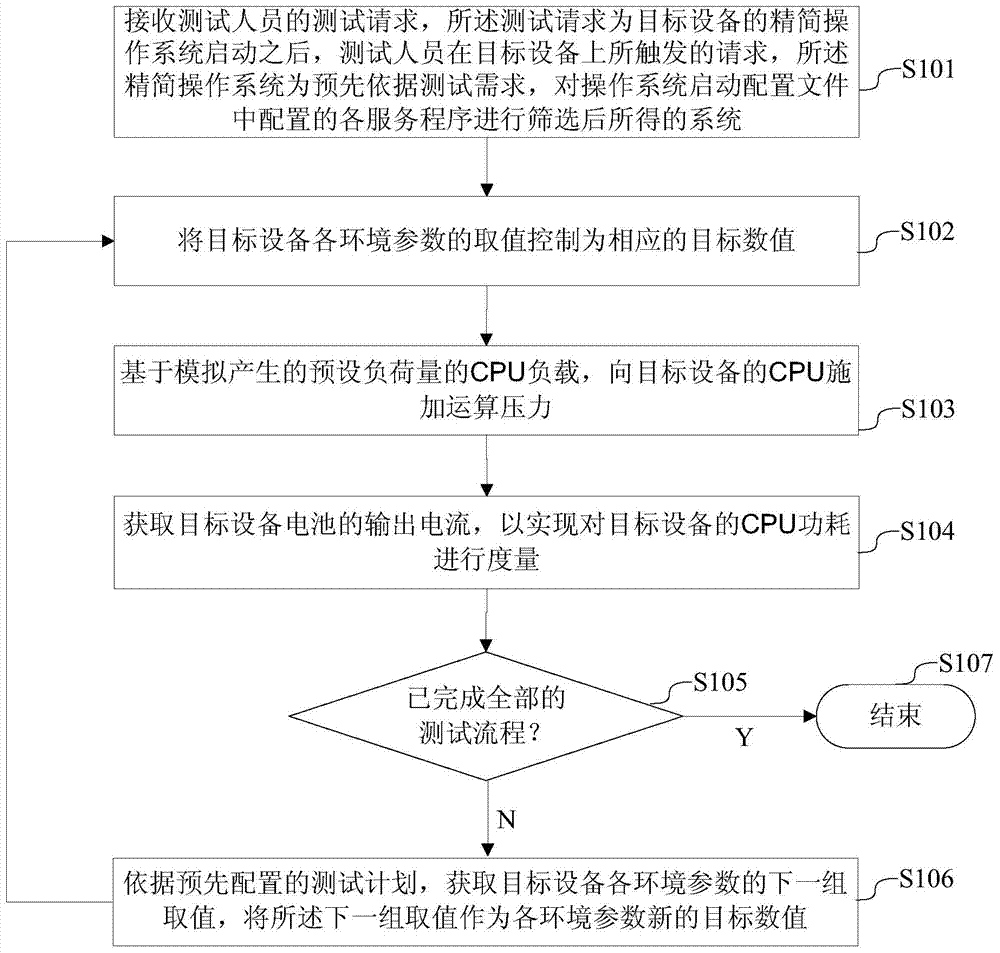

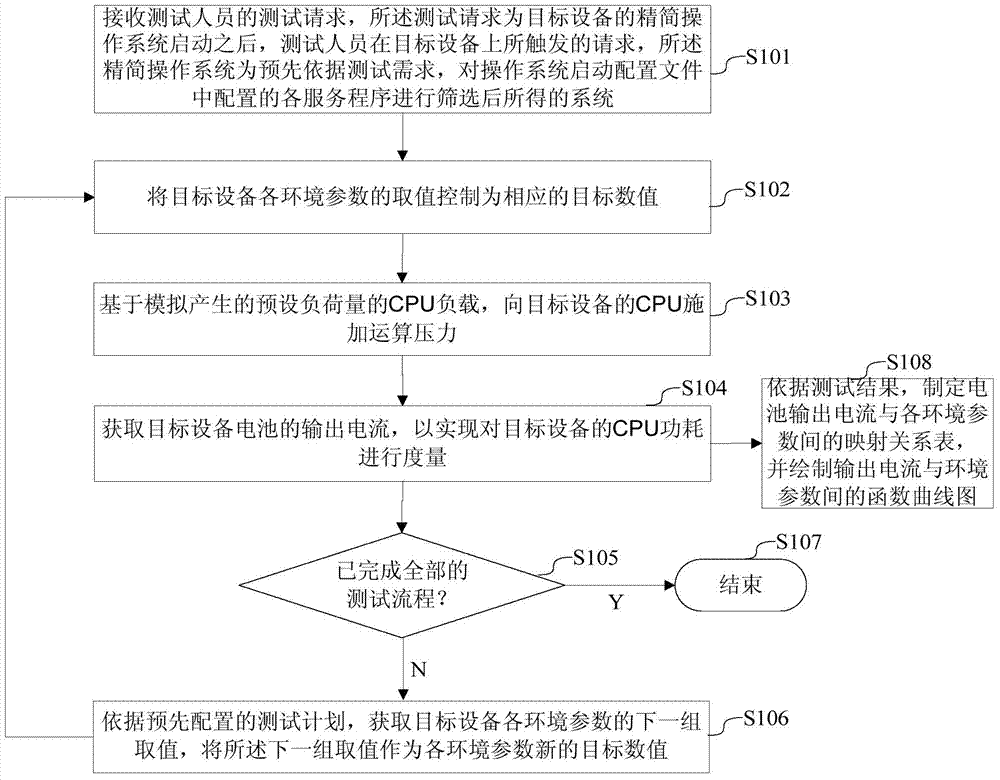

CPU power consumption test method and CPU power consumption test system

ActiveCN104502690AAchieve streamliningReduce adverse effectsElectric devicesElectric power measurementTest requirementsCPU power dissipation

The invention discloses a CPU power consumption test method and a CPU power consumption test system. According to the CPU power consumption test method and the CPU power consumption test system, service programs configured in an operating system booting configuration file are screened in advance according to test requirements, unnecessary service programs for a test process are eliminated, and an operating system is simplified; when a CPU (central processing unit) power consumption test for a target device is performed on the basis of the simplified operating system, environmental parameters of the target device are controlled according to preset corresponding target numerical values, CPU load is generated through simulation, operation pressure is applied to a CPU of the target device, output current of a battery of the target device is acquired on that basis, and CPU power consumption measurement of the target device is realized; therefore, the CPU load is generated through simplification of the operating system and simulation, negative influences of the system and application programs on test results are reduced, and accurate data support is provided for system power consumption optimization.

Owner:THUNDERSOFT

CPU (central processing unit) power consumption based fan control method

InactiveCN106292963AQuick responseDissipate in timePower supply for data processingEnergy efficient computingAir volumeBaseboard

The invention discloses a CPU (central processing unit) power consumption based fan control method. The method includes: at a research and development stage, testing required fan duty ratios of a CPU under different operation power consumptions, and writing a corresponding relation between the power consumptions and the fan duty ratios into a BMC (baseboard management controller); in a server operation process, allowing the BMC to acquire CPU power consumption values in real time and output corresponding PWM (pulse width modulation) to adjust the rotating speed of a fan, so that air volume required for CPU heat dissipation is guaranteed. Compared with the prior art, the CPU power consumption based fan control method has advantages that the rotating speed of the fan can be regulated according to actual heat dissipation of the CPU, response speed of the fan is increased, timeliness in dissipation of heat generated by the CPU is guaranteed, the CPU is guaranteed against overheat under all operating conditions, and system power consumption is reduced effectively.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

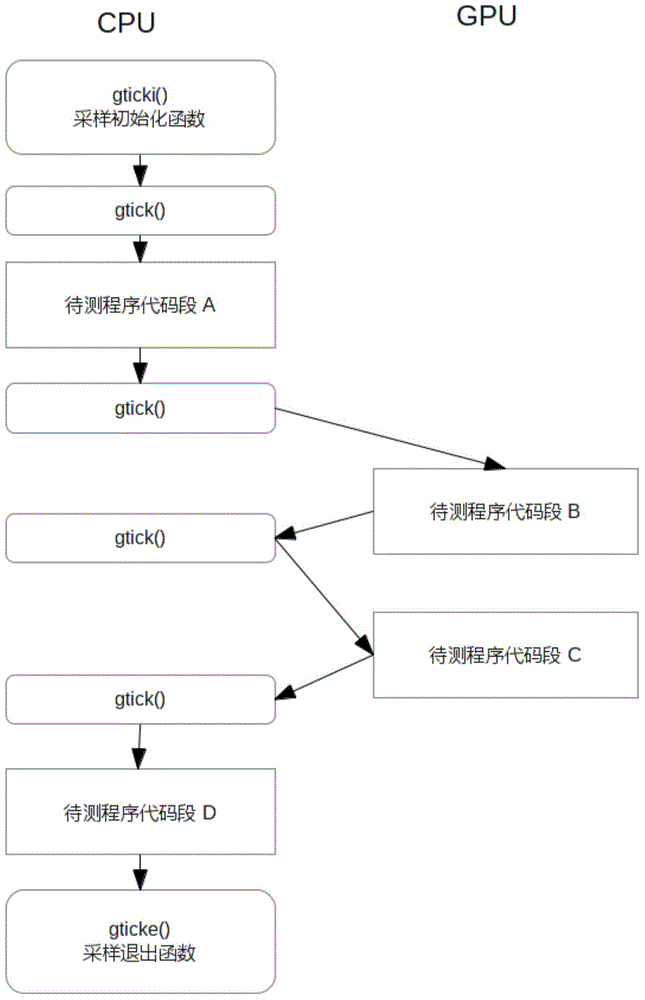

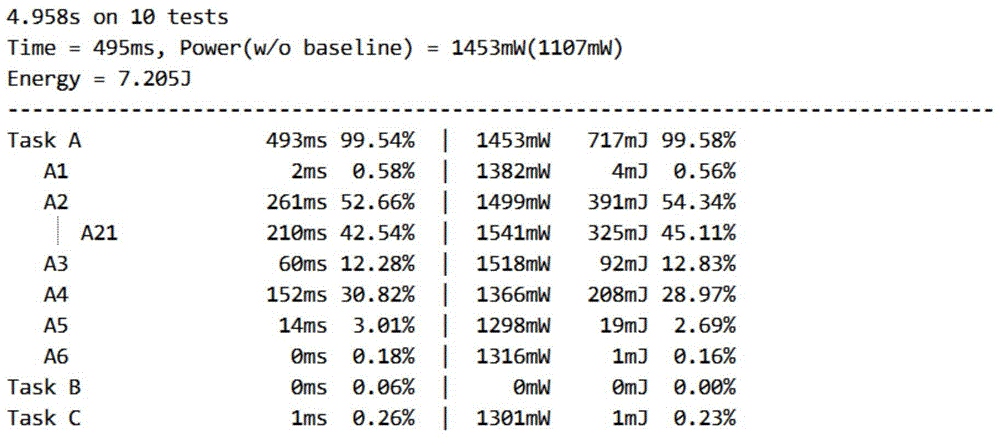

Method for measuring power consumption of CPU (Central Processing Unit) and GPU (Graphics Processing Unit) software on mobile processor

ActiveCN104461849ASolve power consumptionReduce power consumptionHardware monitoringEnergy efficient computingSoftware developmentCPU power dissipation

The invention discloses a method for measuring power consumption of CPU (Central Processing Unit) and GPU (Graphics Processing Unit) software on a mobile processor. The method comprises the following steps: establishing a CPU power consumption model; modifying a program to be measured and recompiling; setting a platform to be measured; and operating the program to be measured and carrying out data processing. The method for measuring power consumption of a CPU and a GPU on the mobile processor, which is disclosed by the invention, effectively solves the problem that currently, a software developer difficultly and simultaneously acquires power consumption of the CPU and the GPU in the program executing process on a mobile processor of a mobile intelligent terminal. Any additional measurement tool is not required, the platform to be measured also does not need to be disassembled, power consumption of the CPU and the GPU on the mobile processor in the program executing process can be directly and accurately acquired on the mobile intelligent terminal and the developer of applications can be helped to design applications and games, which have low power consumption, for the intelligent terminal.

Owner:RES INST OF SOUTHEAST UNIV IN SUZHOU

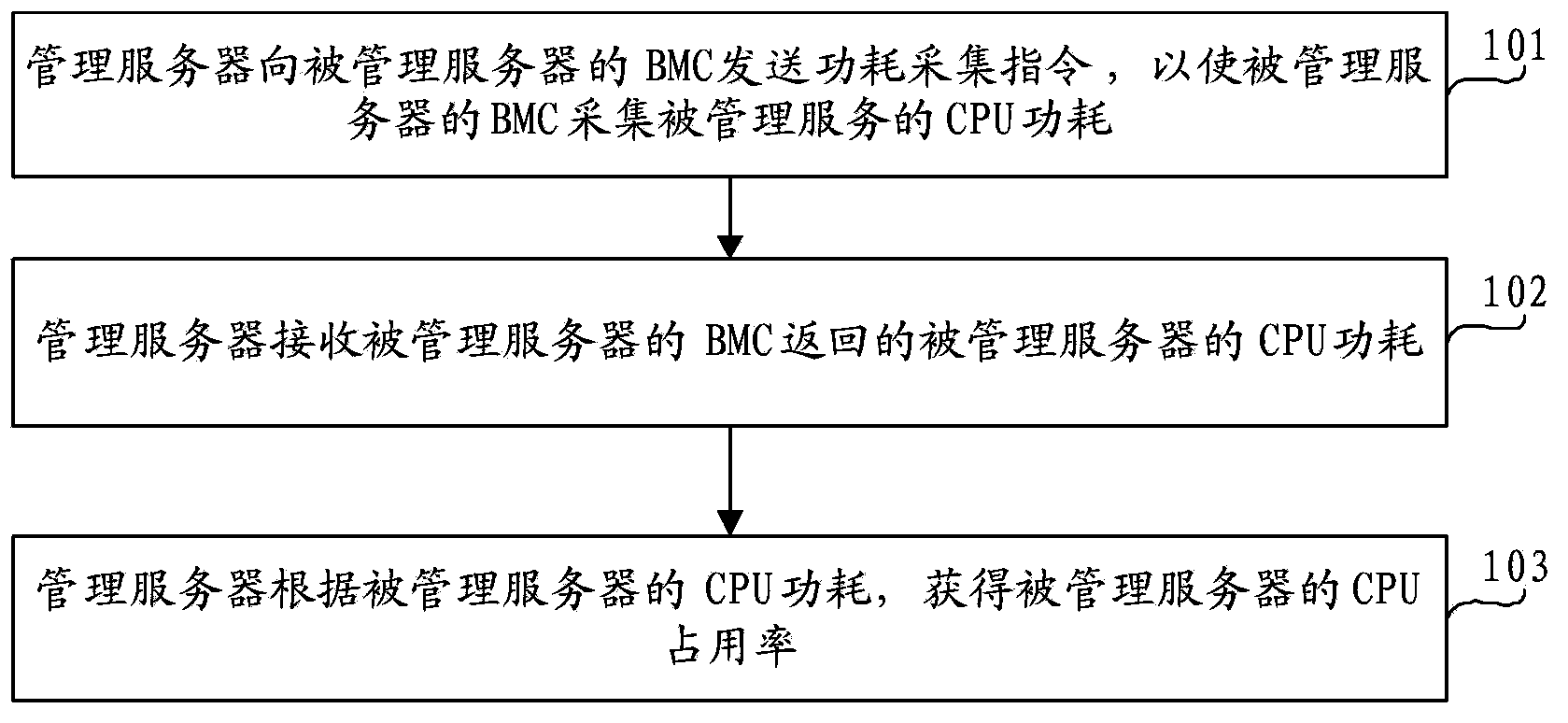

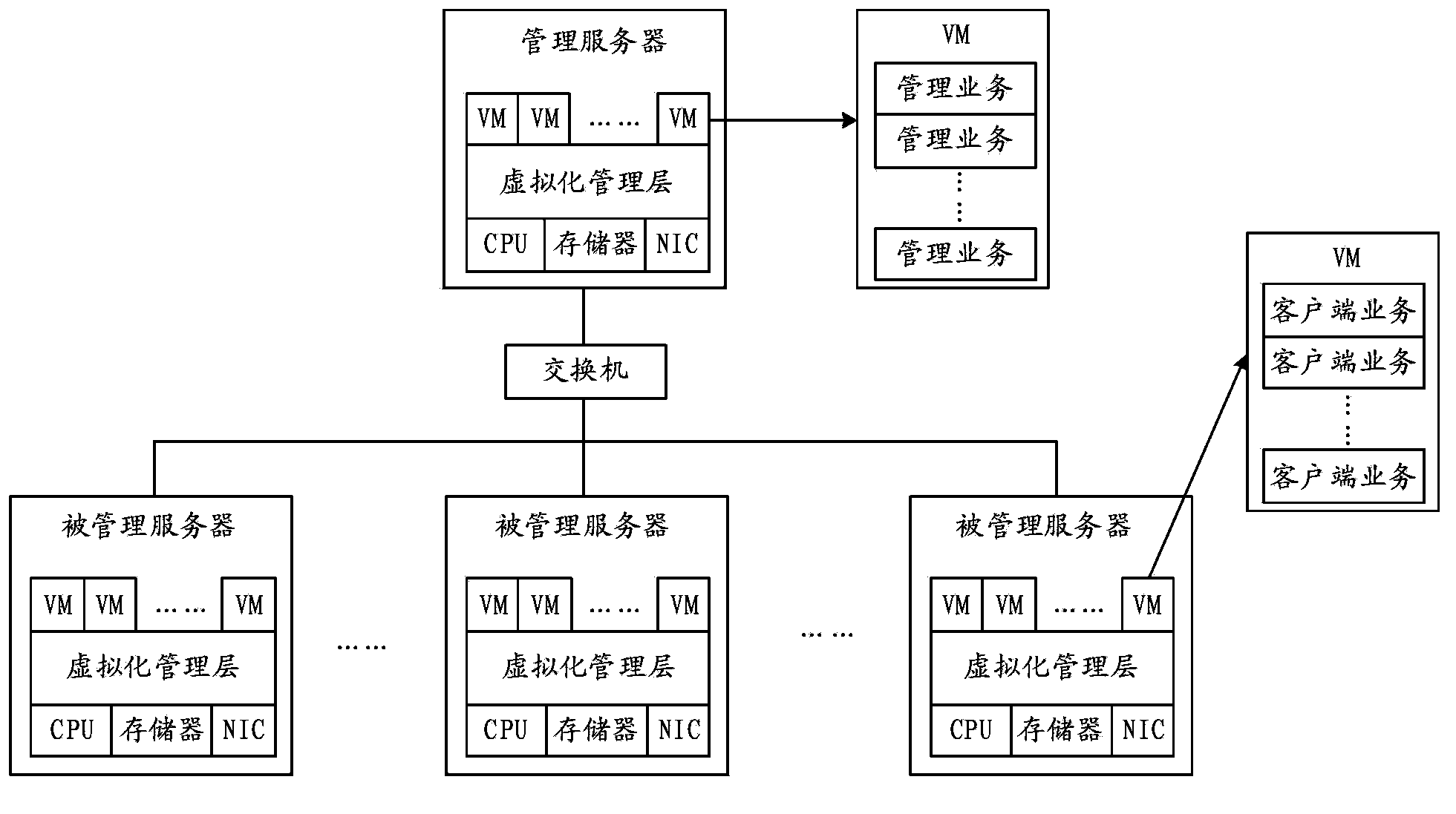

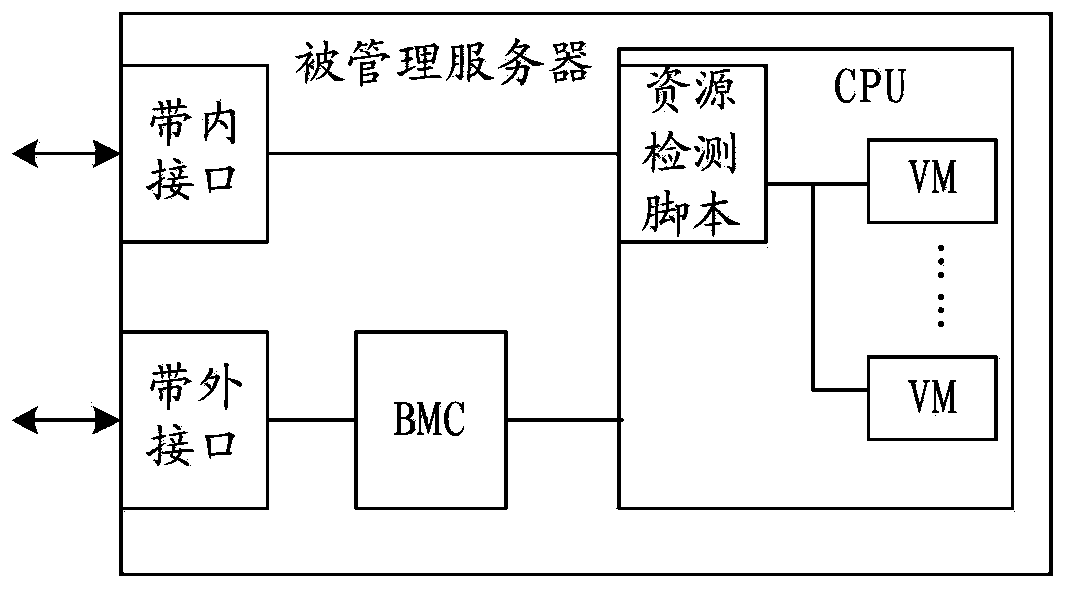

Resource occupation rate acquiring method, providing method, system and server thereof

ActiveCN103856337AImplement out-of-band managementImprove business performanceData switching networksOn boardCPU power dissipation

This invention provides a resource occupation rate acquiring method, a providing method, a system and a server thereof. The resource occupation rate acquiring method comprises that: a management server transmits a power consumption collection order to an on-board management center (BMC) of a managed server in order to make the on-board management center (BMC) of the managed server collect the CPU power consumption of the managed server; the management server receives the CPU power consumption of the managed server which is returned by the on-board management center (BMC) of the managed server; and the management server acquires the CPU occupation rate of the managed server according to the CPU power consumption of the managed server. By adopting the scheme of the invention, the CPU resource consumed by acquiring the CPU occupation rate can be reduced, and thus the business performance of the server is improved.

Owner:HUAWEI TECH CO LTD

Method for reducing system energy consumption

InactiveCN101957654AReduce energy consumptionSave electricityPower supply for data processingLow loadCore component

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

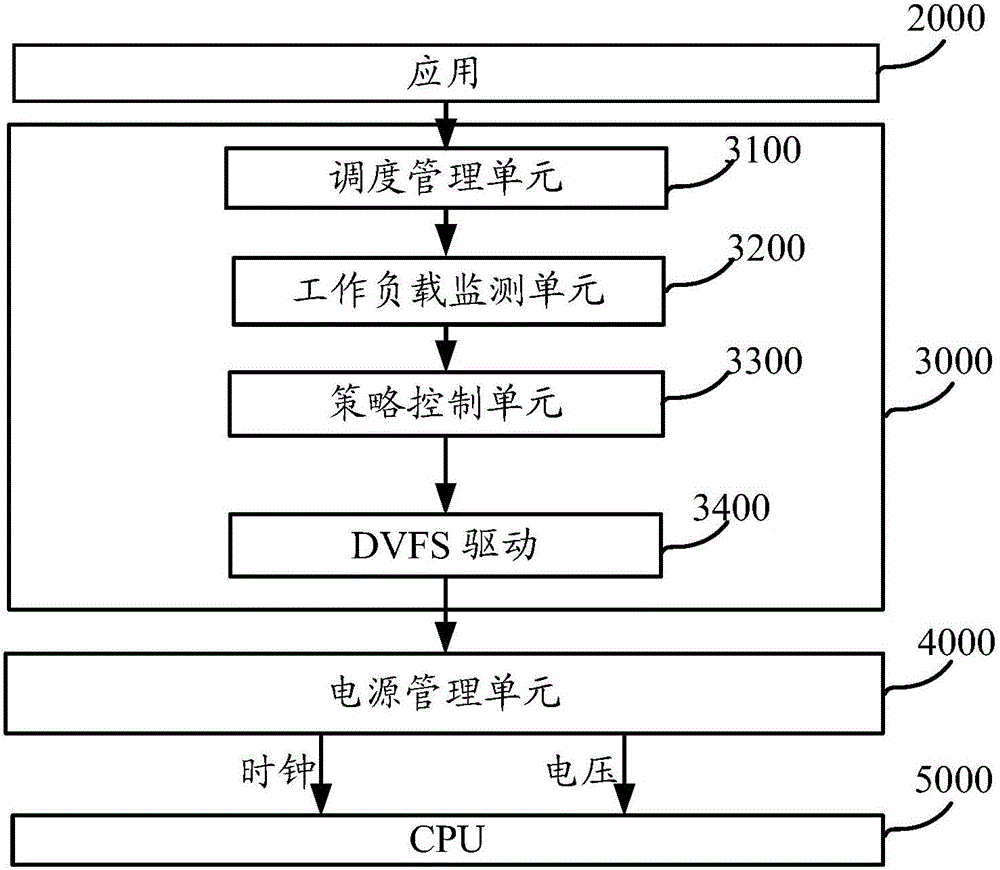

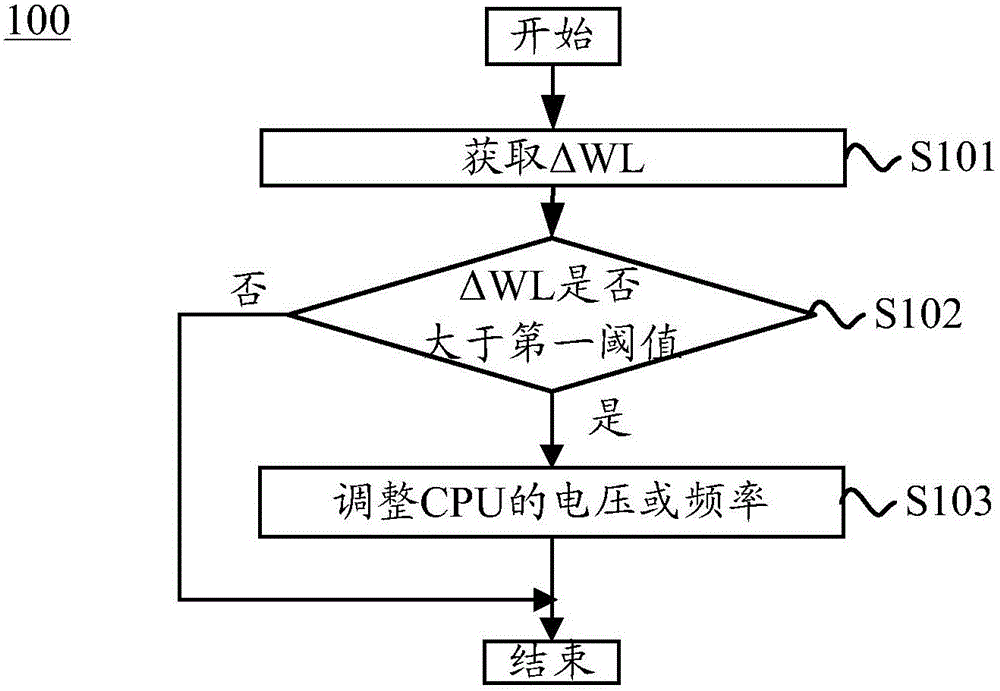

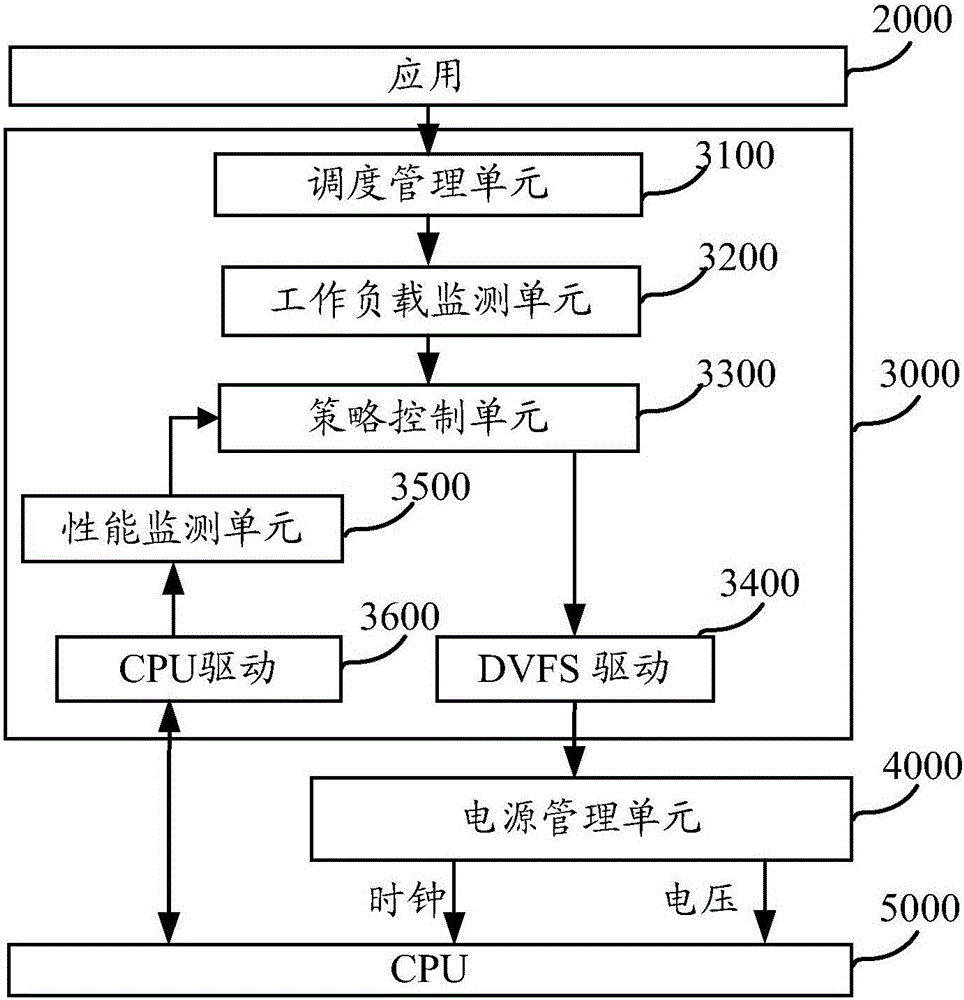

Dynamic voltage and frequency scaling system and method

ActiveCN105677000AEasy to controlGuaranteed performanceHardware monitoringPower supply for data processingArithmetic logic unitEngineering

Embodiments of the invention provide a dynamic voltage and frequency scaling (DVFS) system and method. The system comprises a performance monitoring unit and a policy control unit. The performance monitoring unit is used for determining a current first core blockage (CB) coefficient of a central processing unit (CPU) and determining a first variable quantity according to the first CB coefficient, wherein the first CB coefficient represents the performance bottleneck of current processing capability of an arithmetic logic unit (ALU) in the CPU. The policy control unit is used for scaling a working frequency and a working voltage of the CPU according to the first variable quantity determined by the performance monitoring unit. According to the embodiments of the invention, the CPU is subjected to DVFS according to the variable quantity of the CB coefficient, so that the DVFS process can be controlled more finely, caused unnecessary scaling is avoided, and the fine management on the power consumption of the CPU is realized on the basis of ensuring the system performance of the CPU.

Owner:HUAWEI TECH CO LTD

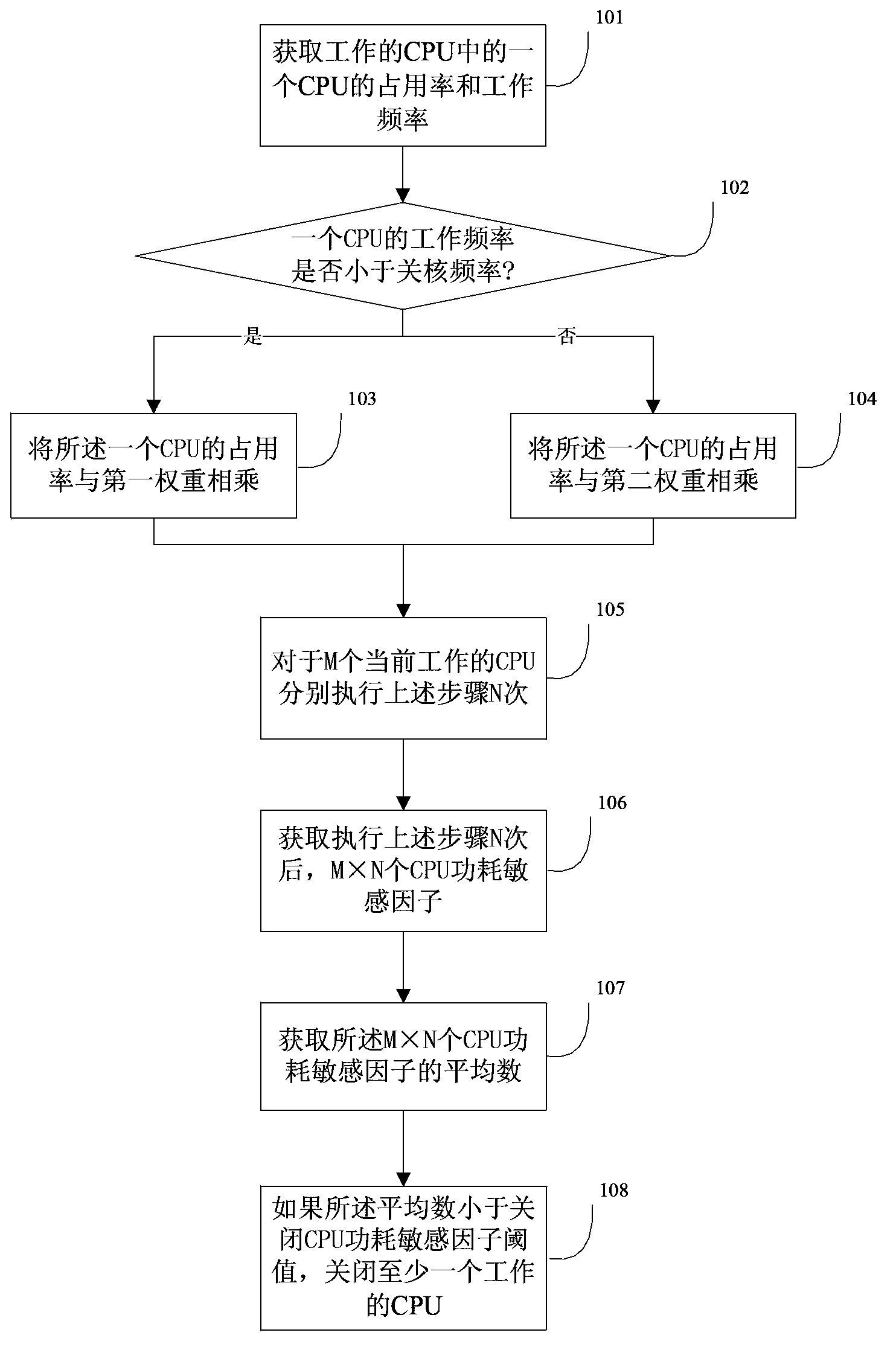

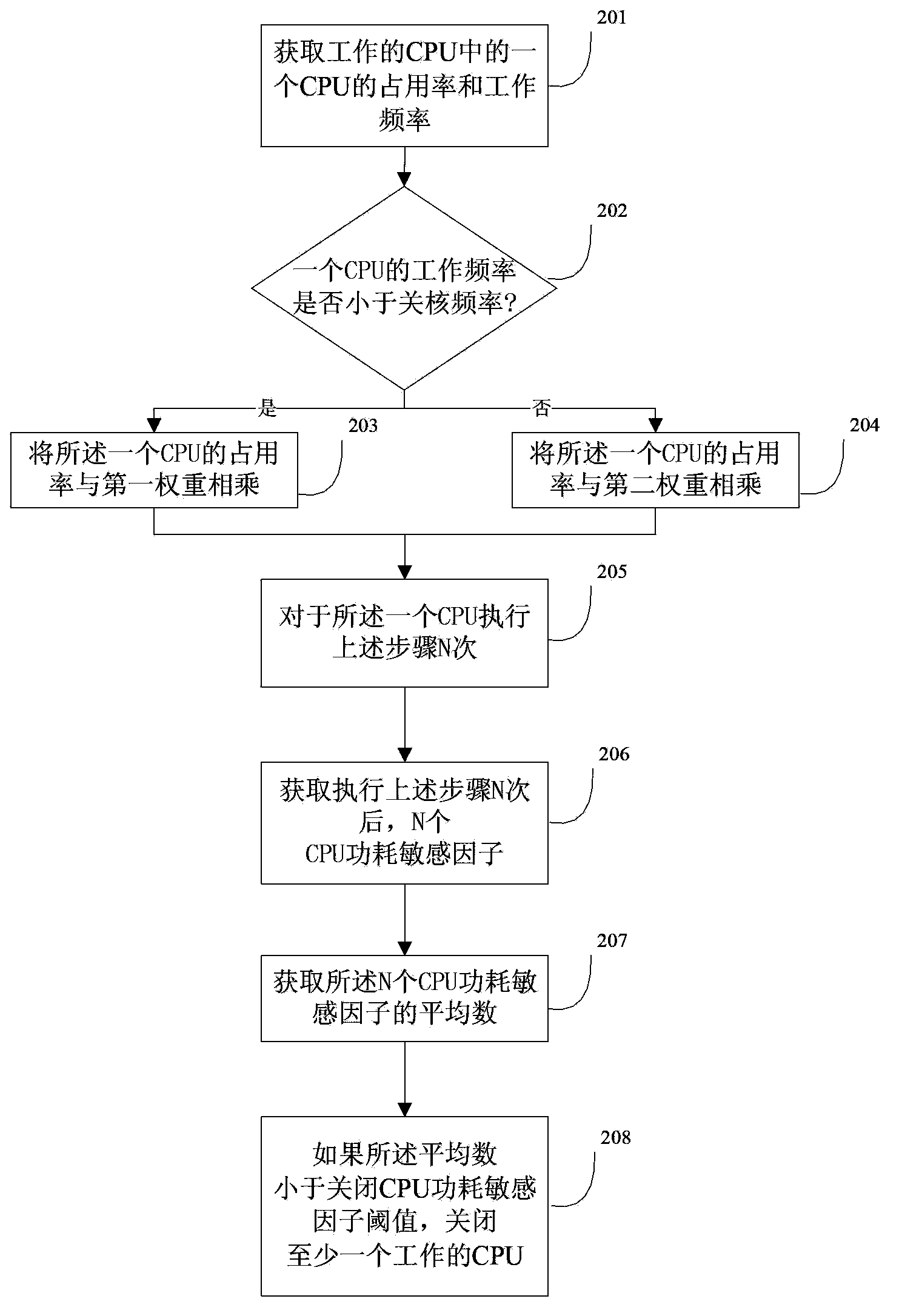

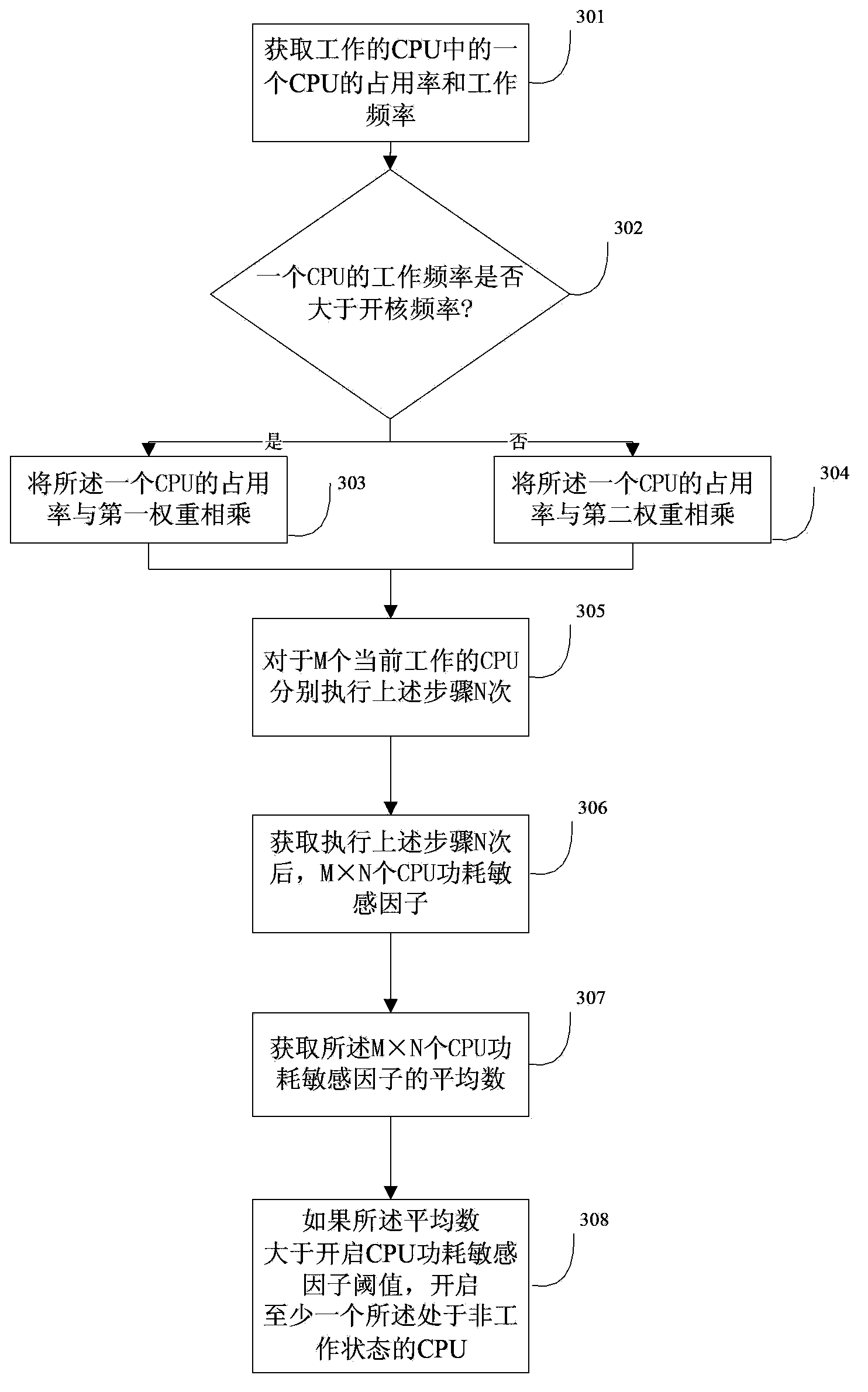

Method and apparatus for controlling CPU

ActiveCN103415824AReduce consumptionPower supply for data processingEnergy efficient computingOccupancy rateCPU power dissipation

The invention discloses a method for controlling CPUs, comprising: obtaining the occupancy rate and work frequency of one of the CPUs in work, wherein the number of CPUs in work is M; when the work frequency of the CPU is lower than an off-core frequency, obtaining a CPU power consumption sensitive factor corresponding to the CPU by multiplying the occupancy rate of the CPU and a first weight; when the work frequency of the CPU is not lower than the off-core frequency, obtaining the CPU power consumption sensitive factor corresponding to the CPU by multiplying the occupancy rate of the CPU and a second weight; executing the steps for N times to the M CPUs repeatedly, wherein N is an integral not less than 1; obtaining M*N CPU power consumption sensitive factors and an even number; and powering off at least one CPU in work if the even number is smaller than the power-off CPU power consumption sensitive factor.

Owner:HUAWEI DEVICE CO LTD

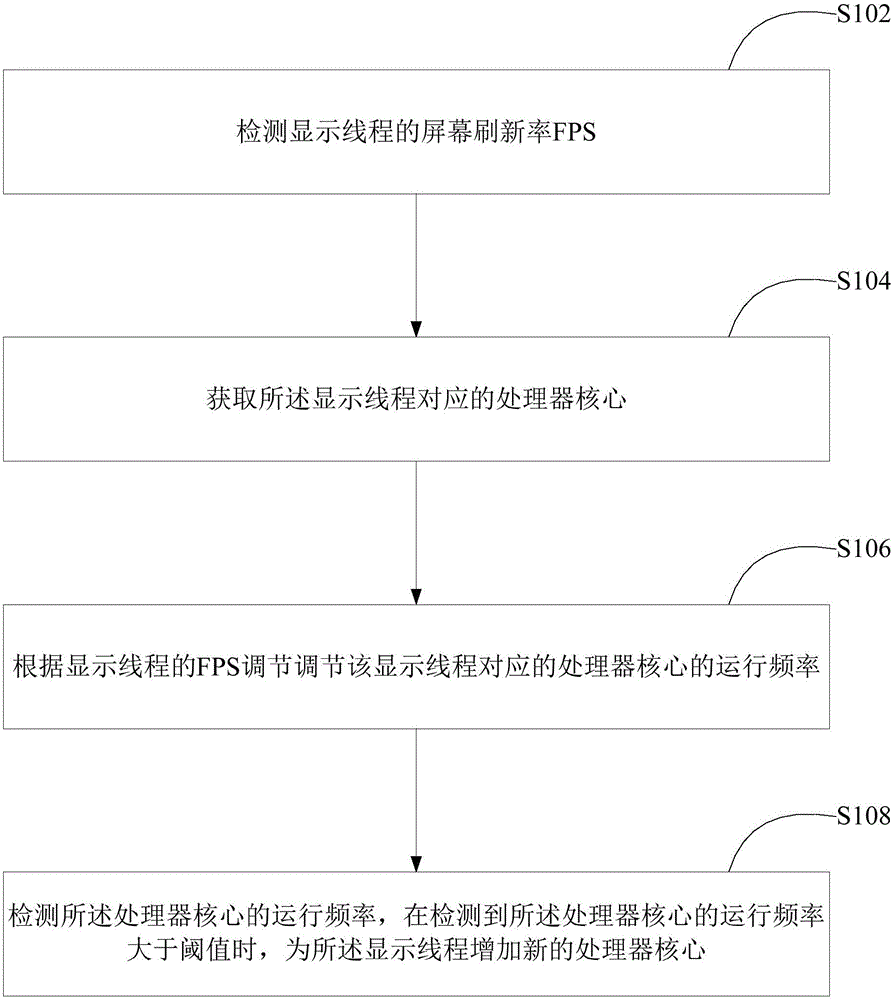

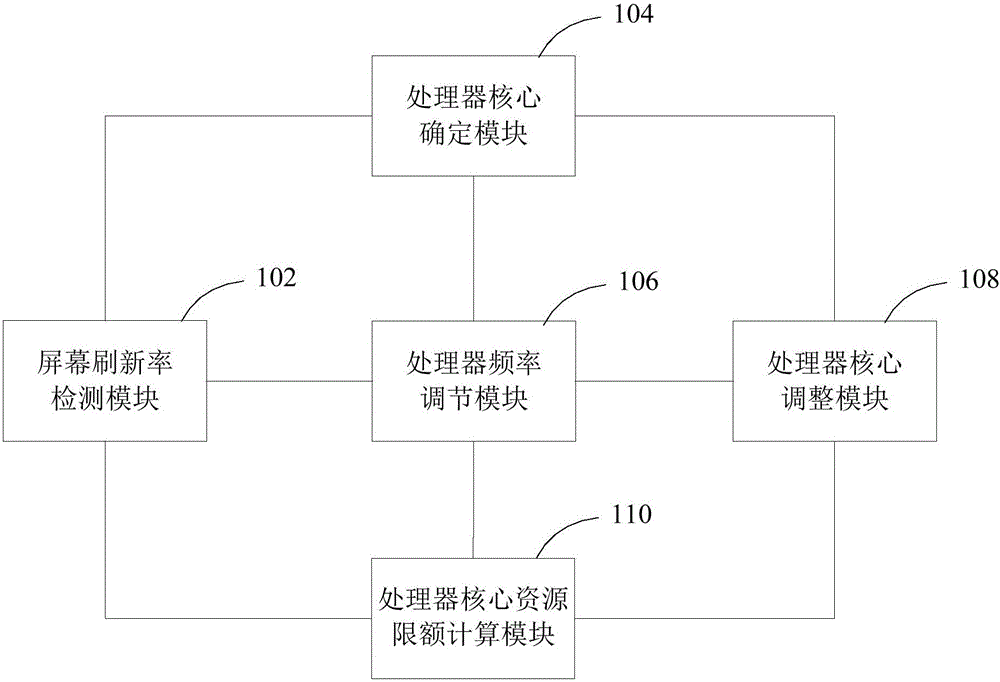

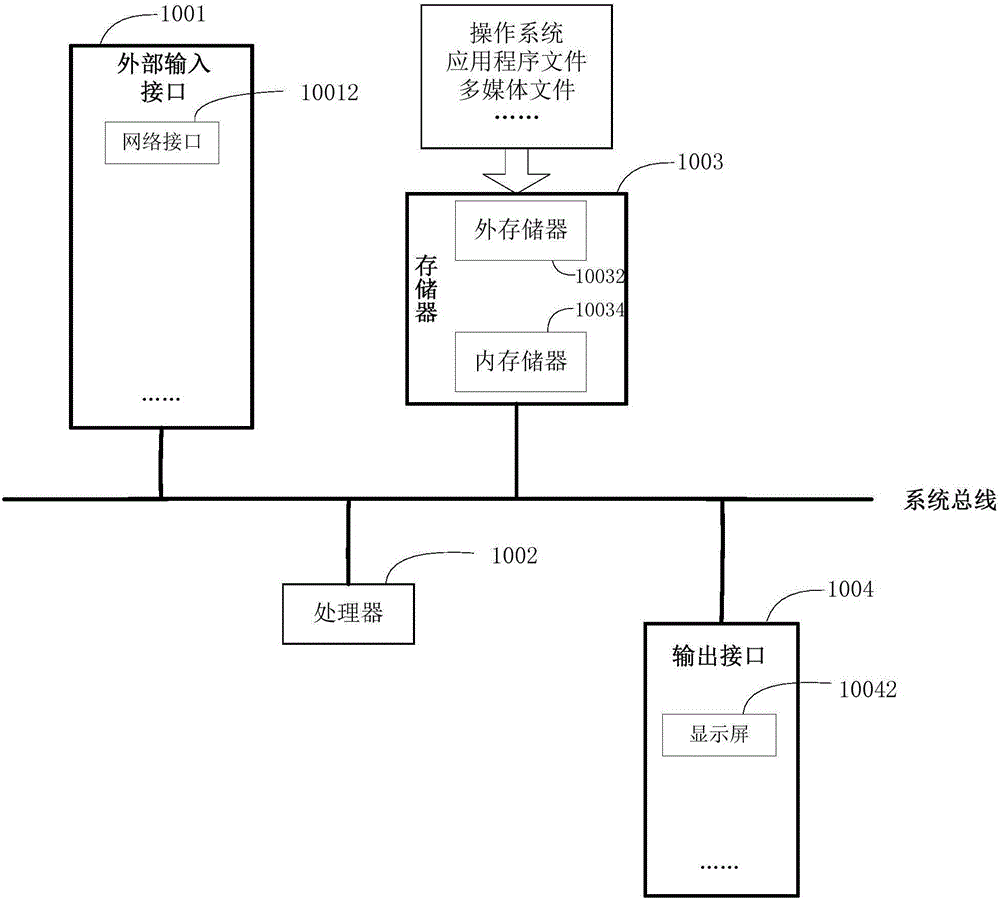

Method and apparatus for controlling CPU power consumption

ActiveCN106095052AGuaranteed performanceReduce power consumptionPower supply for data processingCPU power dissipationEmbedded system

Embodiments of the invention disclose a method for controlling CPU power consumption. The method comprises: detecting a screen refresh rate FPS of a display thread; acquiring a processor core corresponding to the display thread; adjusting a running frequency of the processor core corresponding to the display thread according to the FPS of the display thread; and detecting the running frequency of the processor core, and when it is detected that the running frequency of the processor core is greater than a threshold value, adding a new processor core to the display thread. In addition, embodiments of the invention further disclose an apparatus for controlling the CPU power consumption. By virtue of the method and apparatus disclosed by the embodiments of the invention, terminal power consumption can be reduced.

Owner:SHANGHAI JINSHENG COMM TECH CO LTD

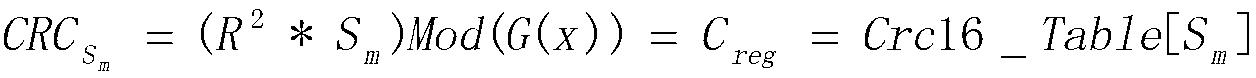

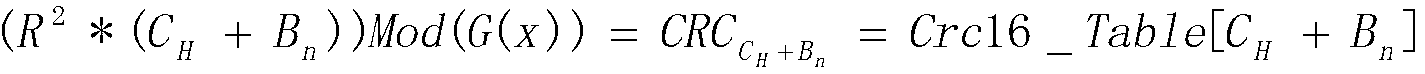

Cyclic redundancy check algorithm of non-integral byte data

The invention discloses a cyclic redundancy check algorithm of non-integral byte data. The cyclic redundancy check algorithm of the non-integral byte data comprises obtaining a CRC16 value of a fist byte S0 through directly looking up a table of Crcl6-Table [S0]; performing exclusive or on Bn and a n bits higher CH of the CRC16 value a last byte and performing the exclusive or result as a subscript to be looked up the table to obtain Crcl6-Table [(CH+Bn)]; and performing exclusive or on a n bits left shifted (16-n) bits and the table looked up value Crcl6-Table [(CH+Bn)]. The value relationship of n is that n is equal to 8 when an integral byte CRC 16 is calculated and the n is the actual bite when the CRC 16 which not satisfies a bite. The cyclic redundancy check algorithm of the non-integral byte data has the advantages of being applicable to a situation that input information which is a non-integral byte cannot be calculated according to the bites, greatly improving the calculation efficiency, reducing the calculation time, releasing a large number of CPU (Central Processing Unit) resources and reducing power consumption of the CPU.

Owner:CHENGDU GUOXING COMM

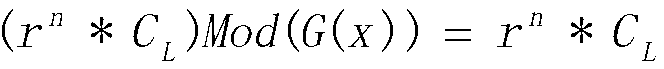

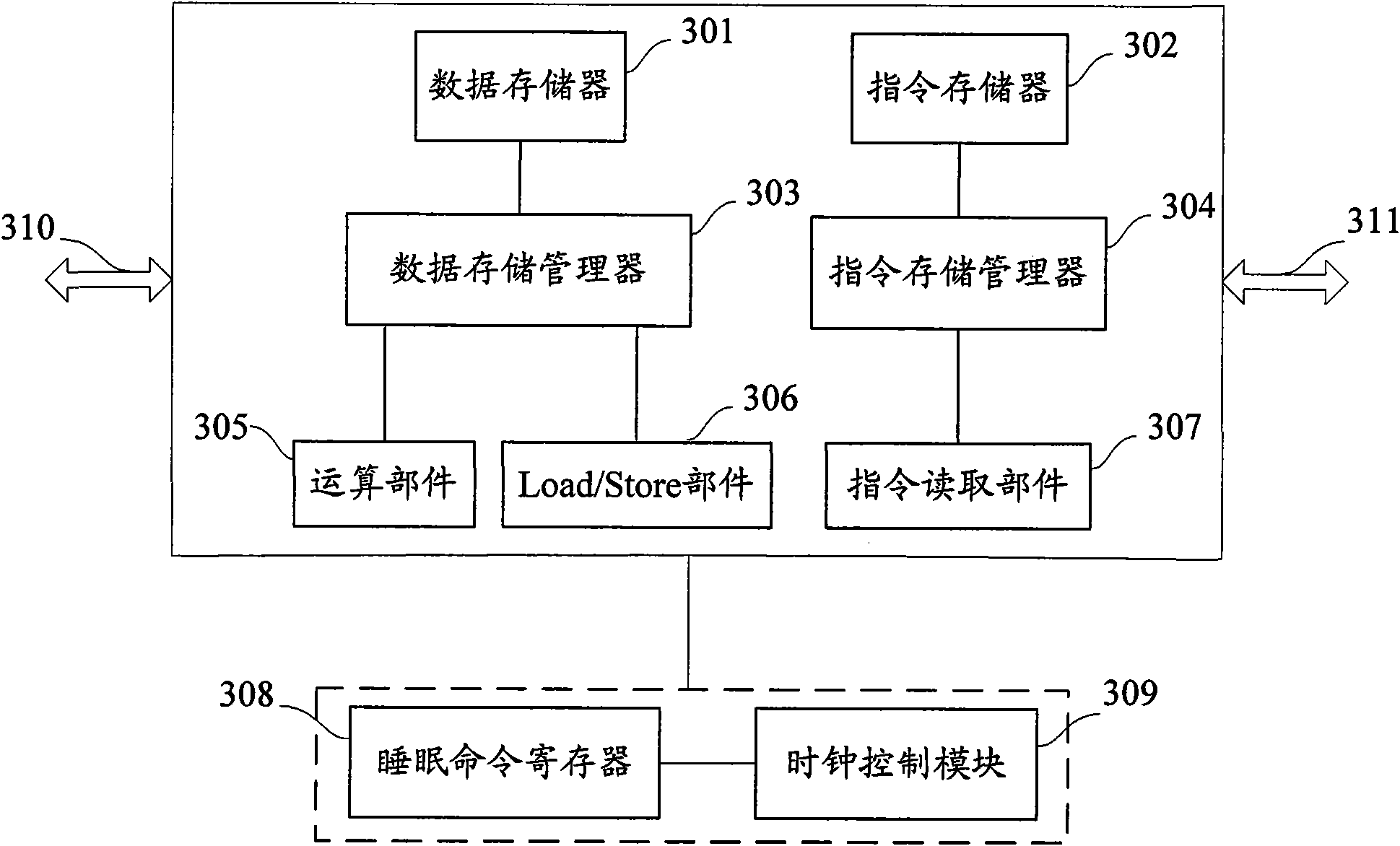

Method for reducing CPU power consumption and CPU

InactiveCN101581963AReduce power consumptionReduce dynamic power consumptionPower supply for data processingLogical operationsCPU power dissipation

The invention discloses a CPU, comprising the following components: a transmission component for transmitting data or instructions between the CPU and peripheral equipment or in the CPU; and an operation and instruction logical component for finishing the non-transmission operation of various arithmetic and logical operations. The CPU further comprises a sleep order register for generating sleep trigger signals in a preset clock period when the transmitter starts working; and a clock control module for closing the clocks of the operation and instruction logical component according to the sleeptrigger signal. The invention can reduce dynamic power consumption of CPU modules not making contribution to transmission work of CPU device, thereby reducing the power consumption of the whole CPU device.

Owner:北京红旗胜利科技发展有限责任公司

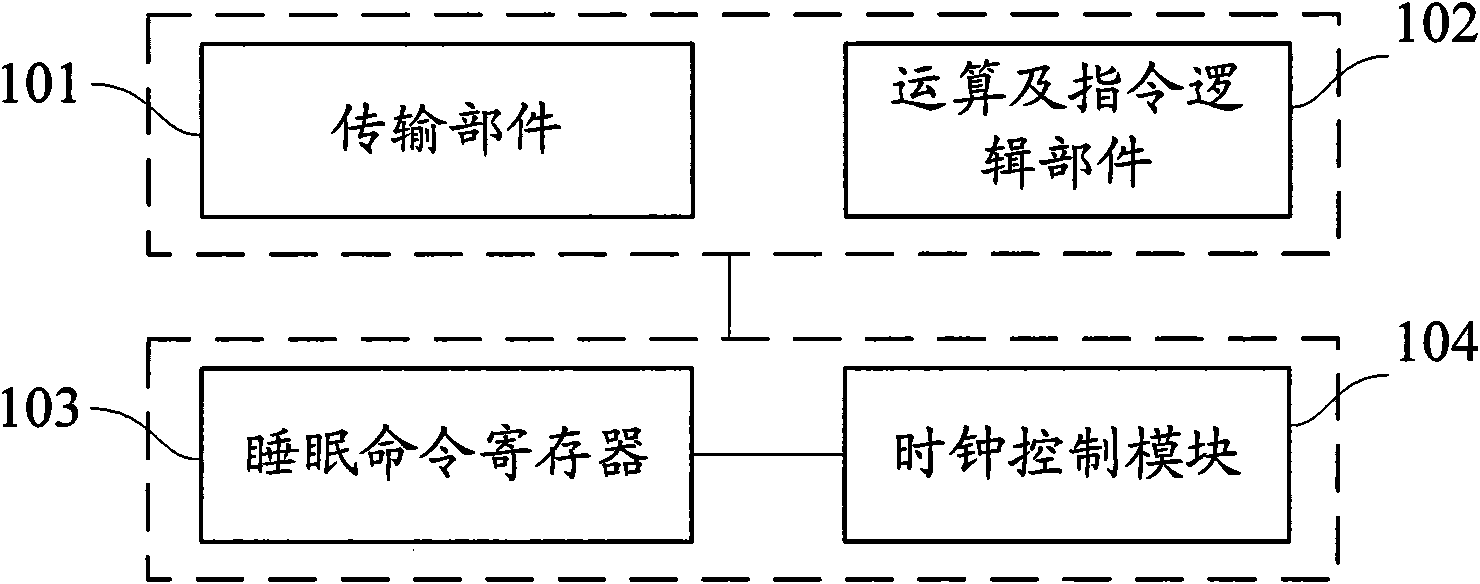

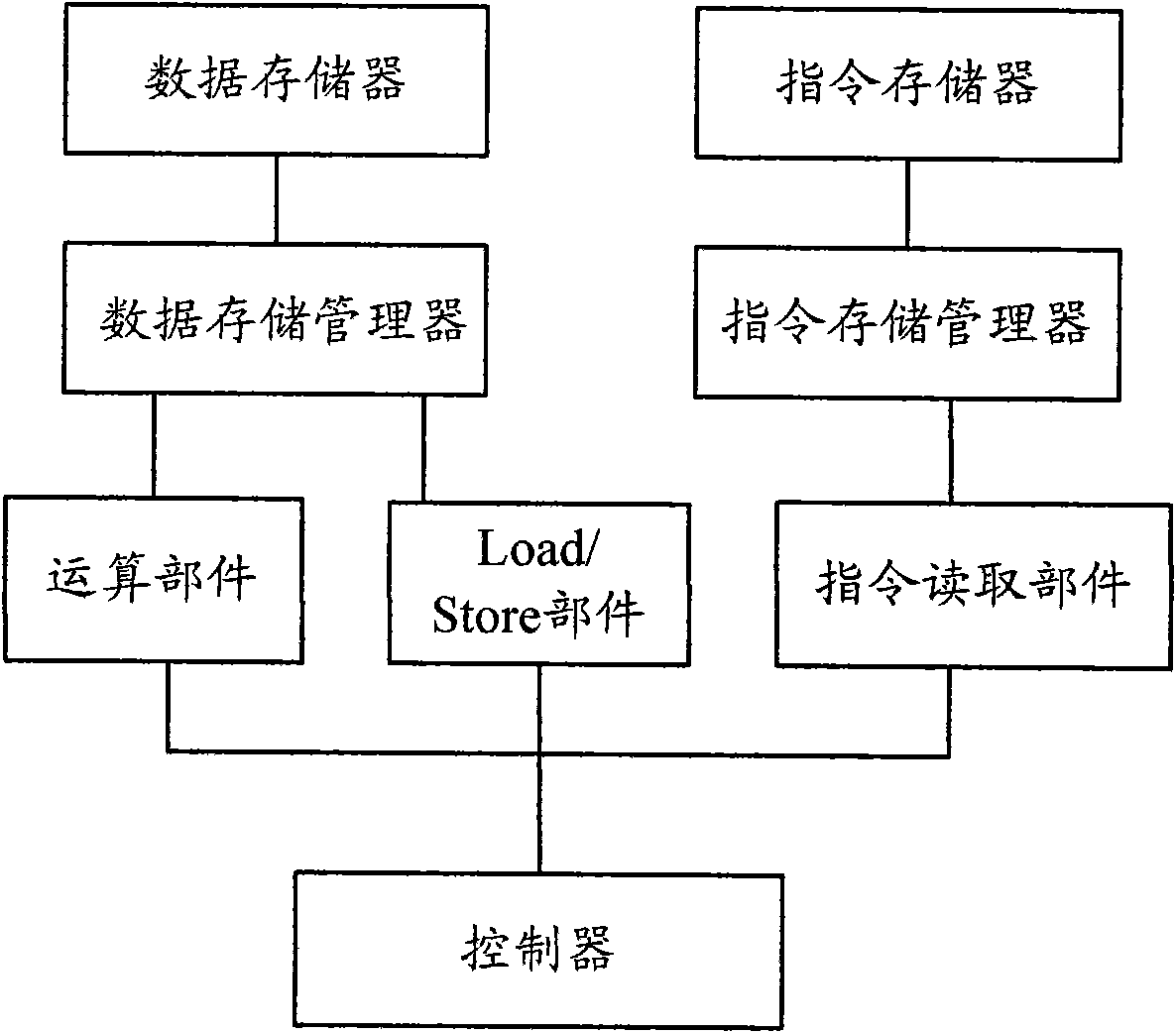

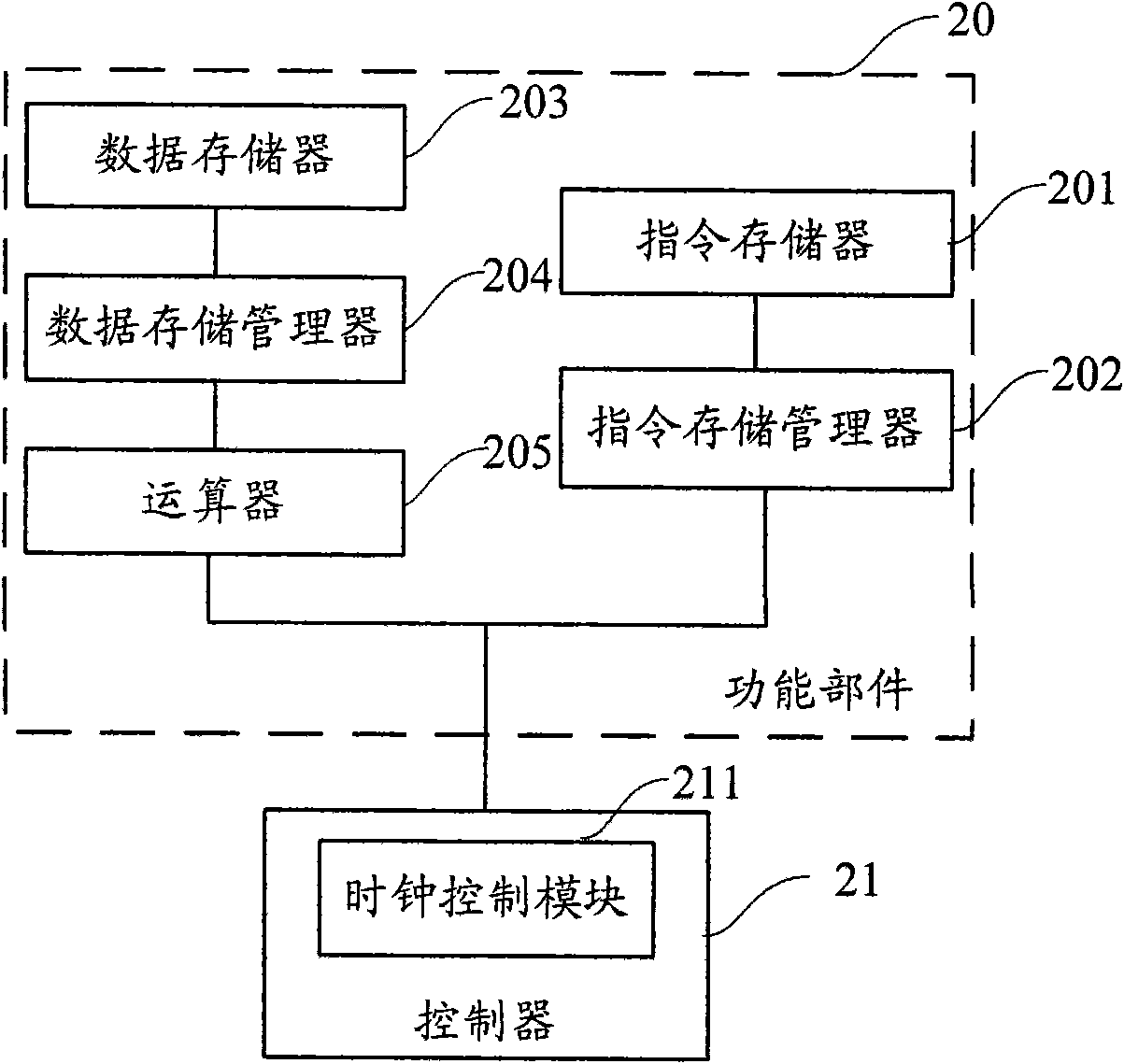

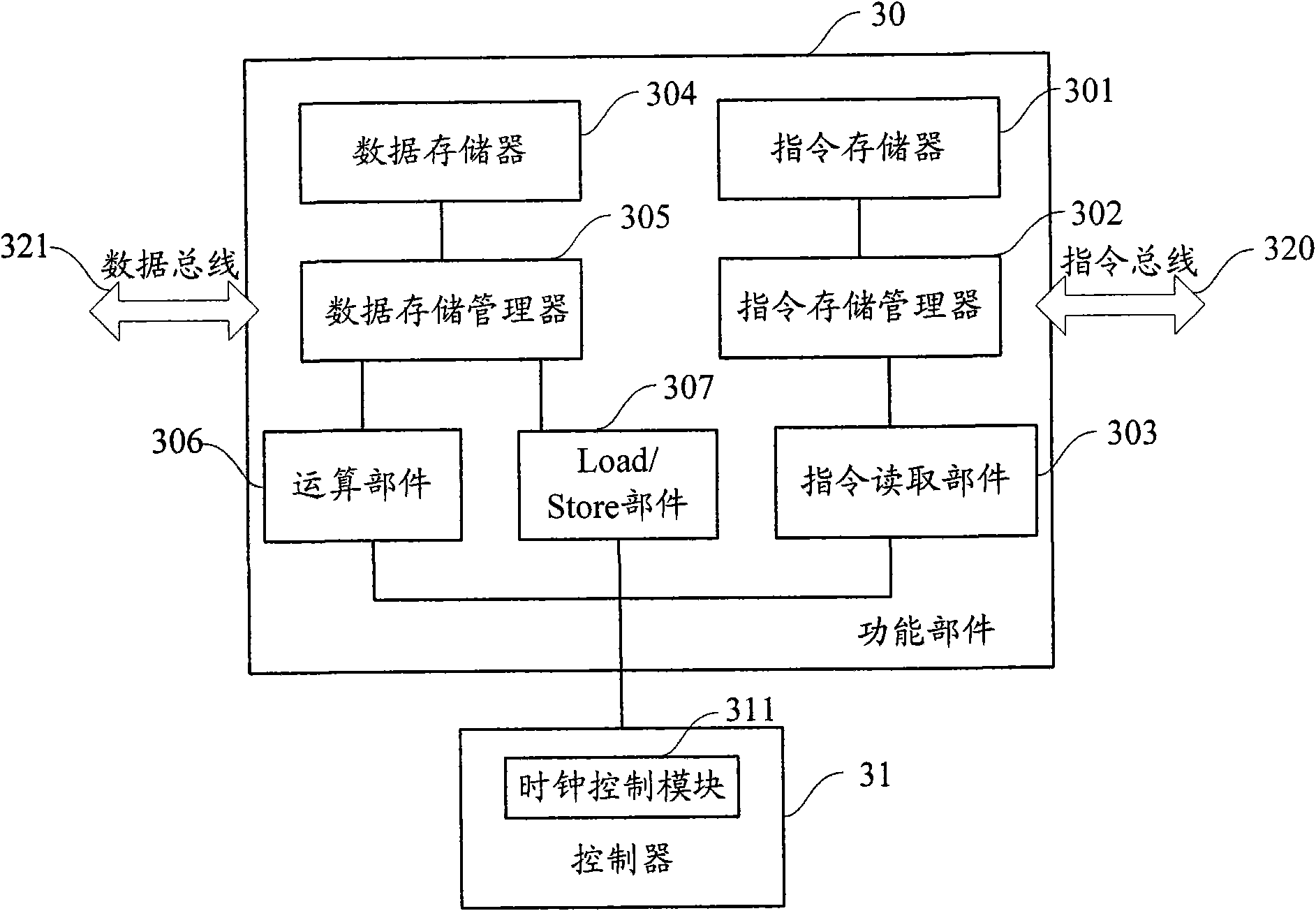

CPU and method for reducing CPU power consumption

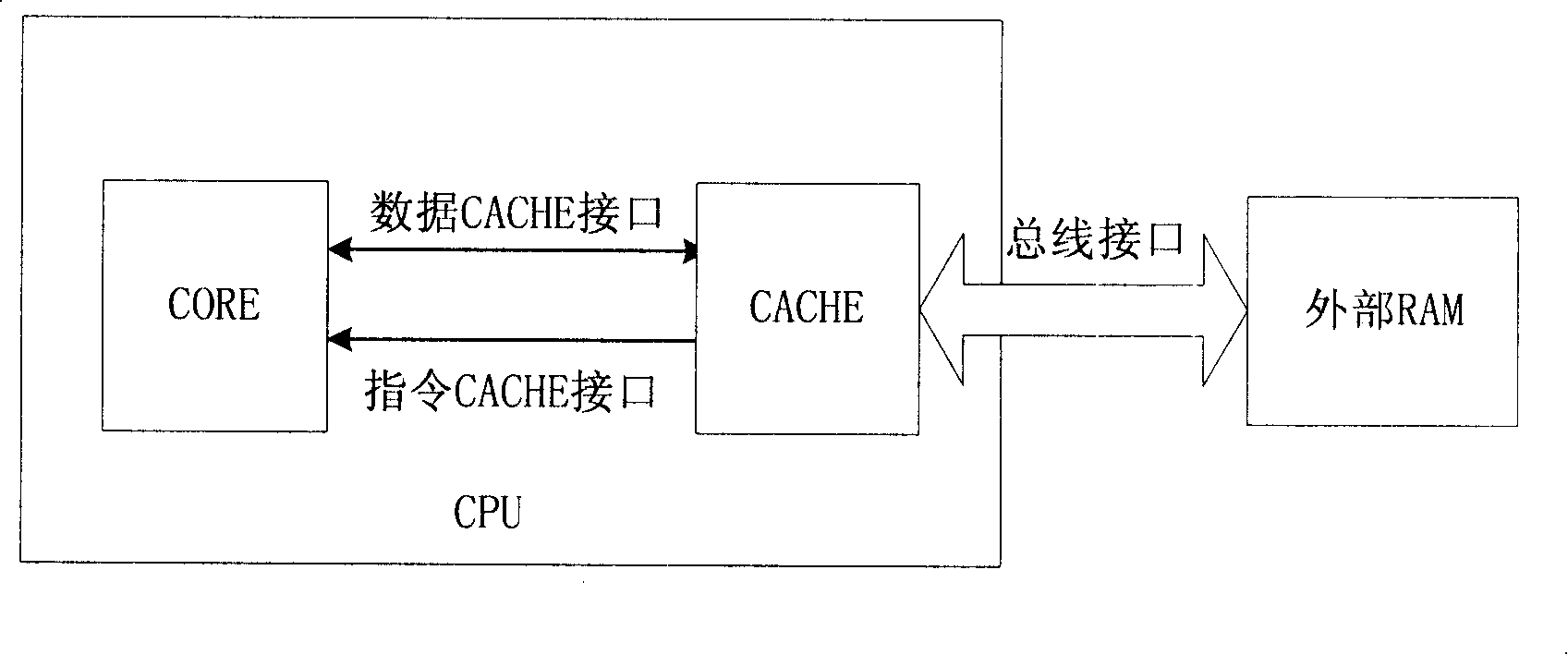

InactiveCN101581961AReduce power consumptionConcurrent instruction executionPower supply for data processingInstruction memoryCycle control

The invention provides a CPU and a method for reducing CPU power consumption. The CPU comprises functional units and a controller; the functional units comprise an instruction storage for storing instruction, an instruction storage manager for managing the access request which directs to the instruction storage, a data storage for storing data, a data storage manager for managing the access request which directs to the instruction storage and an arithmetic unit for accomplishing arithmetic and logic operations; the controller is used for controlling and coordinating the running of each functional unit, also comprises a clock control module located in the controller for judging whether the access request aiming at a certain functional unit exists in the current clock cycle; if the access request exists, the clock of the functional unit is controlled to be started in the current clock cycle; otherwise, the clock of the functional unit is controlled to be closed in the current clock cycle. By controlling the clock to be started or closed, the invention removes the power consumption of functional units in idle state, thus reducing the power consumption of the whole CPU.

Owner:北京红旗胜利科技发展有限责任公司

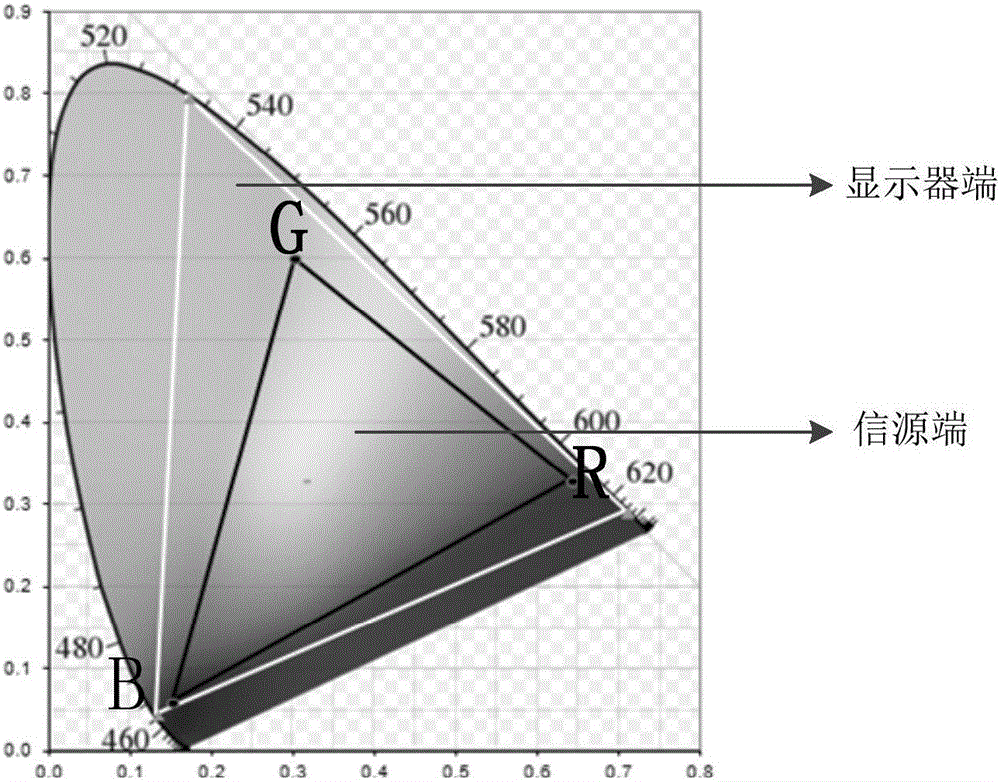

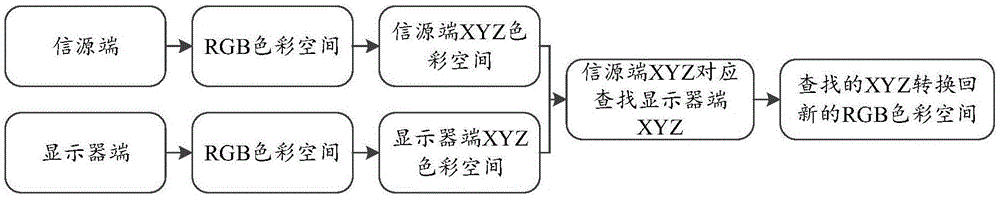

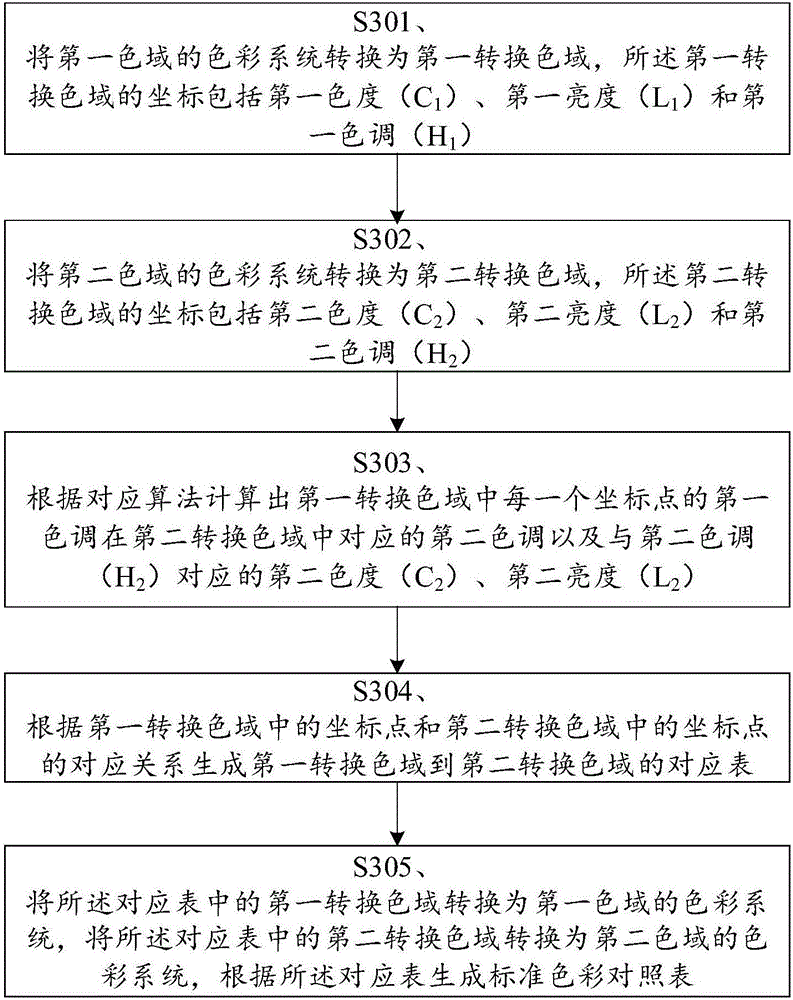

Color gamut keeping system and method

ActiveCN106412544AReduce consumptionProcessing speedColor signal processing circuitsGamutDisplay device

The invention provides a color gamut keeping system and method. When an image is transmitted to a second color gamut from a first color gamut, the color gamut can be kept by generating a standard color comparison table of an image color in the first color gamut and an image color in the second color gamut. The system comprises a first conversion module used for converting a color system of the first color gamut into a first conversion color gamut; a second conversion module used for converting a color system of the second color gamut into a second conversion color gamut; a coordinate point correspondence module used for calculating coordinate point of each coordinate point in the first conversion color gamut correspondingly in the second conversion color gamut according to a corresponding algorithm; a corresponding table generation module used for generating a corresponding table from the first conversion color gamut to the second conversion color gamut; and a standard color comparison table generation module used for generating a standard color comparison table according to the corresponding table. The color gamut keeping system and the color gamut keeping method provided by the invention can maintain the output result of images on different displays, obtain an effect of color gamut keeping, improve the picture processing speed, and reduce the power consumption of a CPU (Central Processing Unit).

Owner:SHENZHEN TCL DIGITAL TECH CO LTD

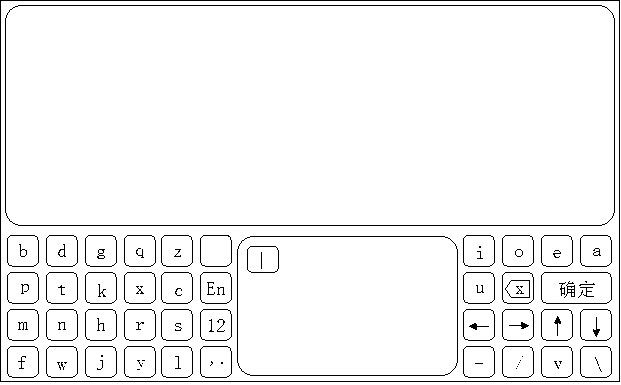

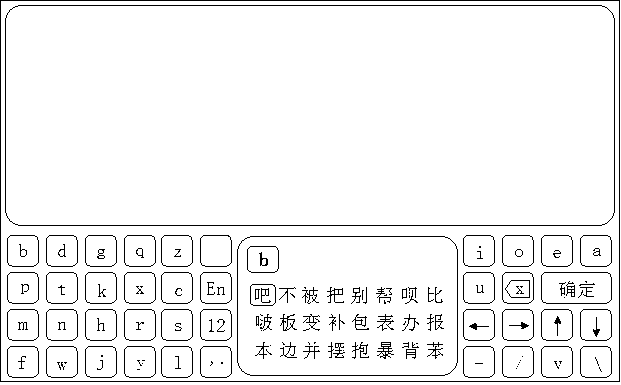

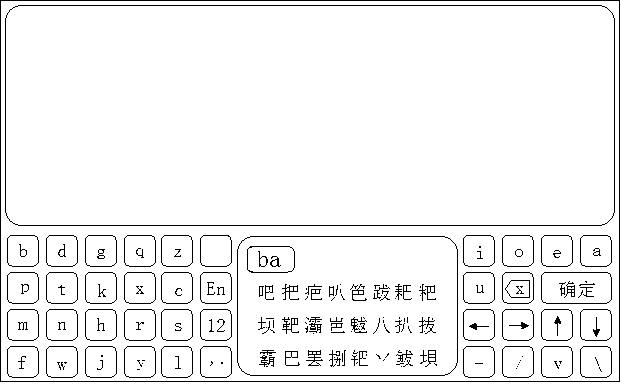

Chinese input method used for touch screen electronic device

InactiveCN103235648AReduce power consumptionEasy to operateInput/output processes for data processingCPU power dissipationHuman–computer interaction

The invention discloses a Chinese input method used for a touch screen electronic device. The Chinese input method comprises the steps of: arranging an initial consonant list and a vowel list of pinyin at two sides of a screen respectively, and setting a character selection auxiliary key region which includes a tone selection key; after inputting an initial consonant by touching, locking vowels which cannot be combined with the initial consonant to form characters by using a special way, and only keeping the vowels which can be combined with the initial consonant to form characters for the subsequent selection; after inputting the vowels by touching, selecting the tones to finish the input; and after selecting a character needing to be input by touching, returning to the initial state. The Chinese input method used for the touch screen electronic device is more convenient and faster to operate as the initial consonants and the vowels are respectively displayed on the left and right sides of the screen and a user can operate with left and right hand at the same time, and reduces CPU (Central Processing Unit) power consumption as a system is unnecessary to wait for the display of the vowel list after the selection of the initial consonants.

Owner:SAMSUNG ELECTRONICS HUIZHOU CO LTD

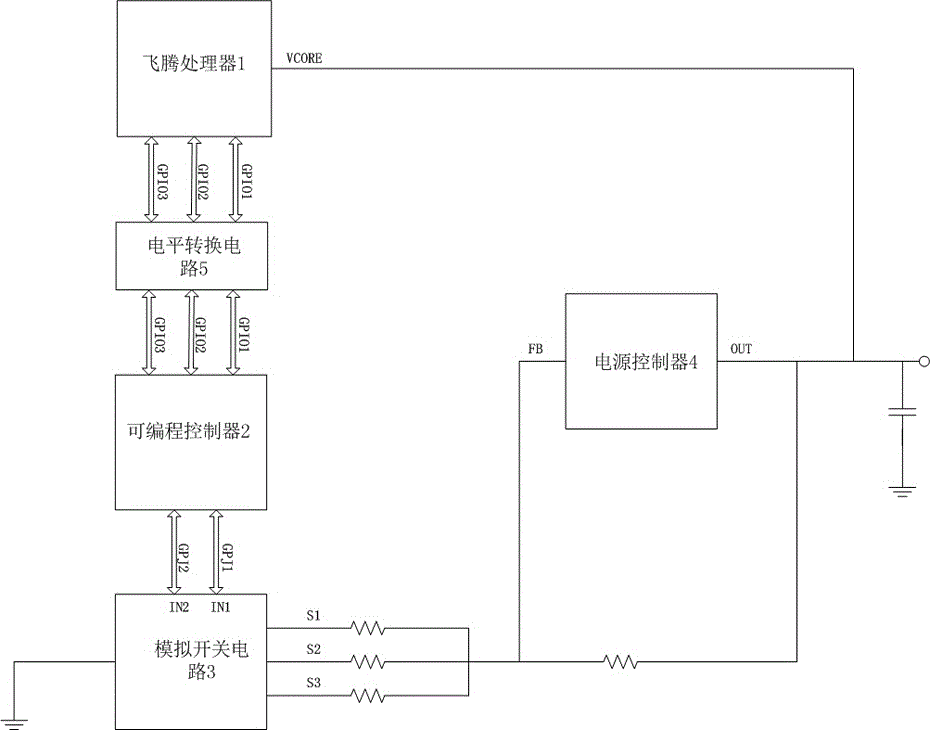

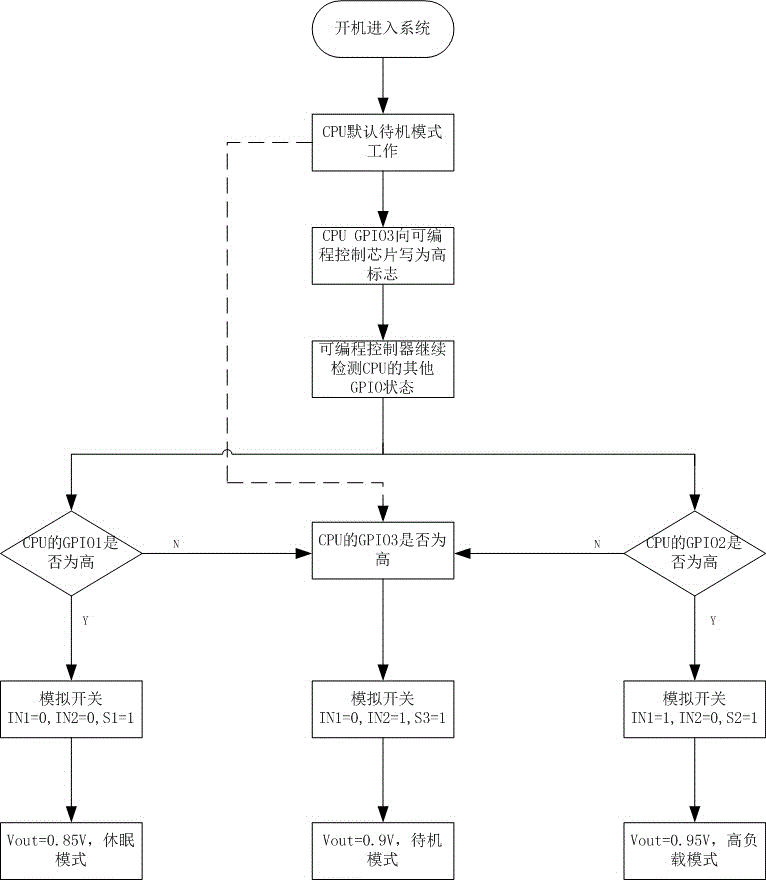

Device and method for controlling CPU power consumption under Feiteng platform

InactiveCN106843453ASimple designLow costPower supply for data processingElectrical resistance and conductancePower controller

The invention discloses a device for controlling the CPU power consumption under a Feiteng platform. The device comprises a Feiteng processor (1) configured with three CPIO interfaces, a programmable controller (2) connected with the Feiteng processor (1) through the three CPIO interfaces, an analog switch circuit (3) including three switch channels in serial connection with resistors and a power supply controller (4), wherein the Feiteng processor (1) sends standby, dormant and high-load states to the programmable controller (2) through the CPIO interfaces, the programmable controller (2) controls on and off of the three switch channels, three feedback voltage divider resistors of the power supply controller (4) correspond to the resistors in serial connection with three switch channels respectively, and the power supply controller (4) correspondingly outputs predetermined voltages according to resistance values. Control of the CPU power consumption is achieved on the Feiteng platform, the hardware circuit design is simple, the BOM cost is low, the software code development amount of the programmable controller is small, and the device is easy to maintain. The invention further provides a CPU power consumption control method.

Owner:湖南长城银河科技有限公司

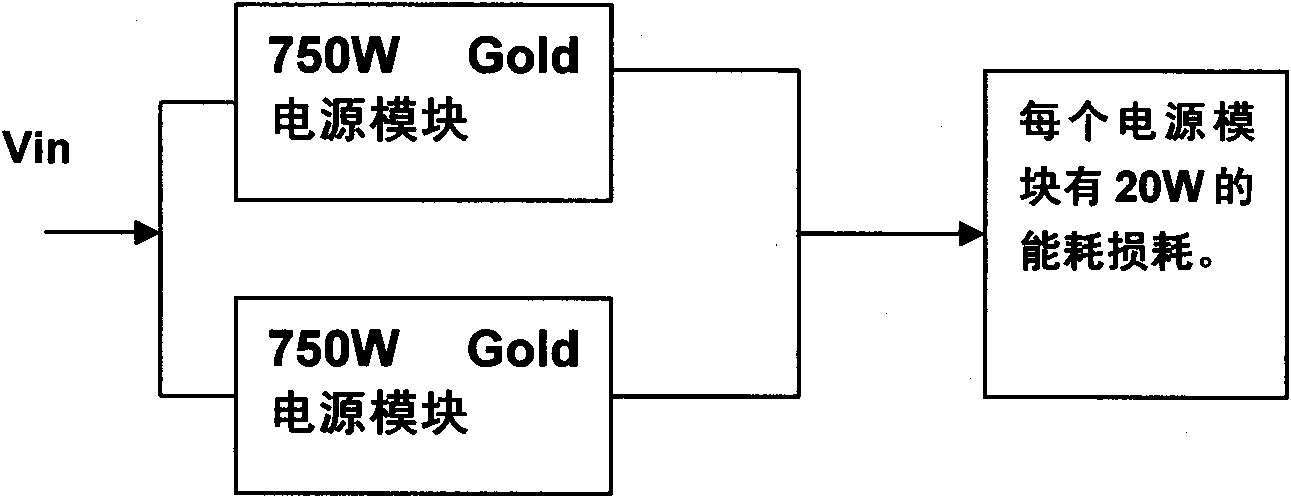

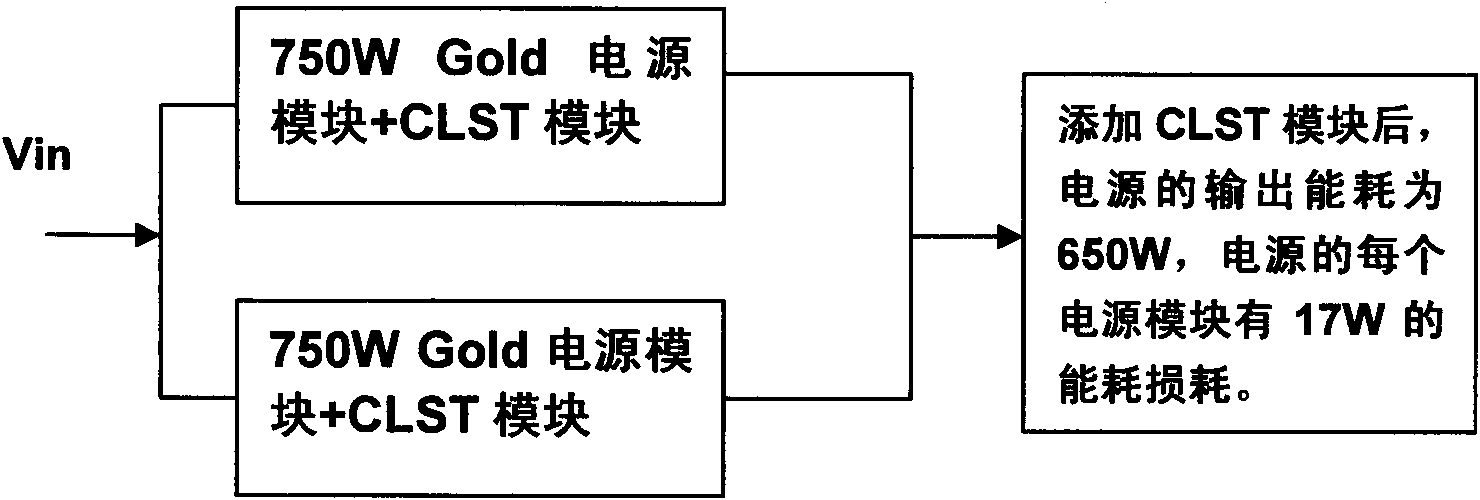

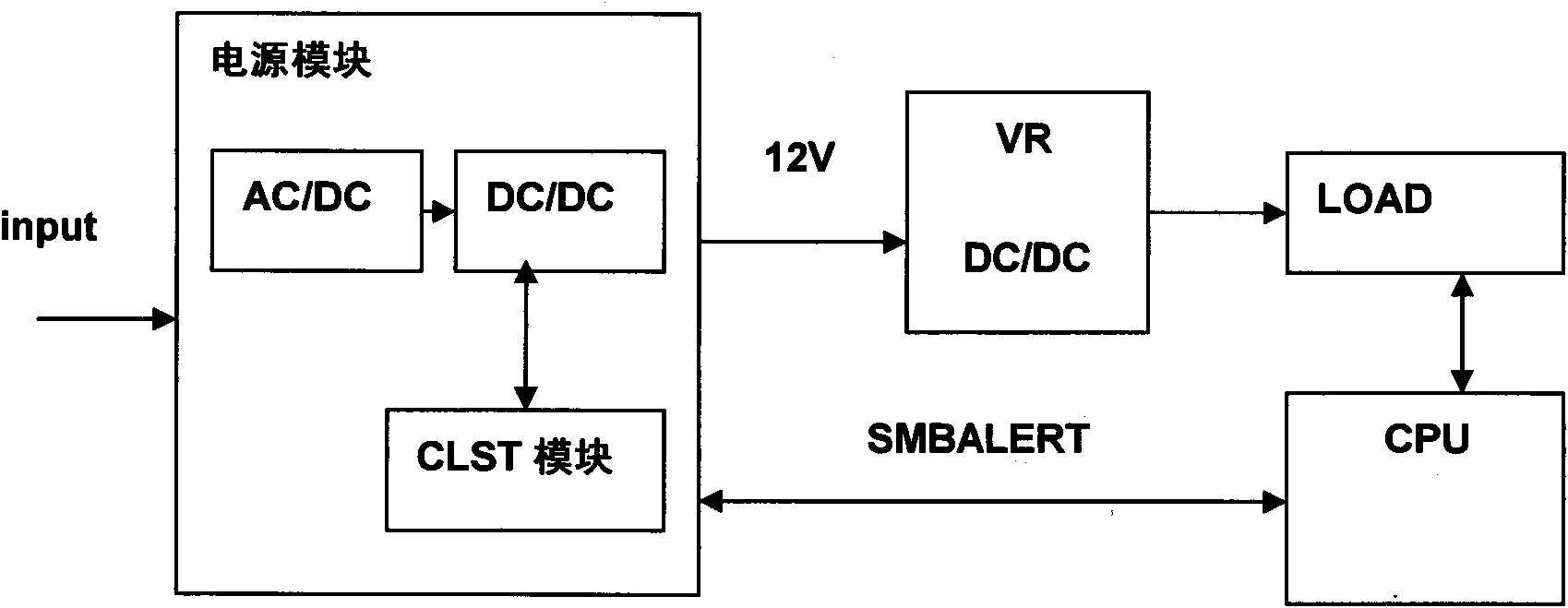

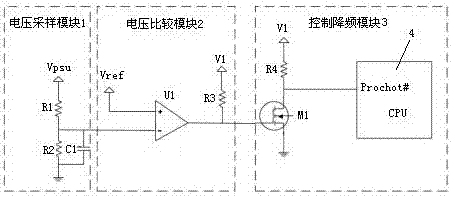

Under voltage protection (UVP) device and protection method of server PSU power supply

InactiveCN107544652AProtect normal operationSolve the problem of a large drop in output voltageVolume/mass flow measurementPower supply for data processingComputer moduleFrequency reduction

The invention discloses an under voltage protection (UVP) device of a server PSU power supply. The device includes the PSU power supply and a server CPU, and further includes: a voltage sampling module, which collects output voltage of the PSU power supply to obtain sampled voltage, and transmits the sampled voltage to a voltage comparison module; the voltage comparison module, which compares thesampled voltage with a preset voltage threshold value, and transmits a comparison result to a frequency-reduction control module; and the frequency-reduction control module, which controls, accordingto the comparison result of the voltage comparison module, whether frequency reduction is carried out on the server CPU. According to the device, a feedback result can be effectively sent to the server CPU in time, frequency reduction of the server CPU can be controlled in time, thus the problem that too much power consumption of the server CPU causes drastic reduction of the output voltage of thePSU power supply is solved, and power-down, restarting or even a crash phenomenon, caused by too low output voltage of the PSU power supply, of a system is avoided.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

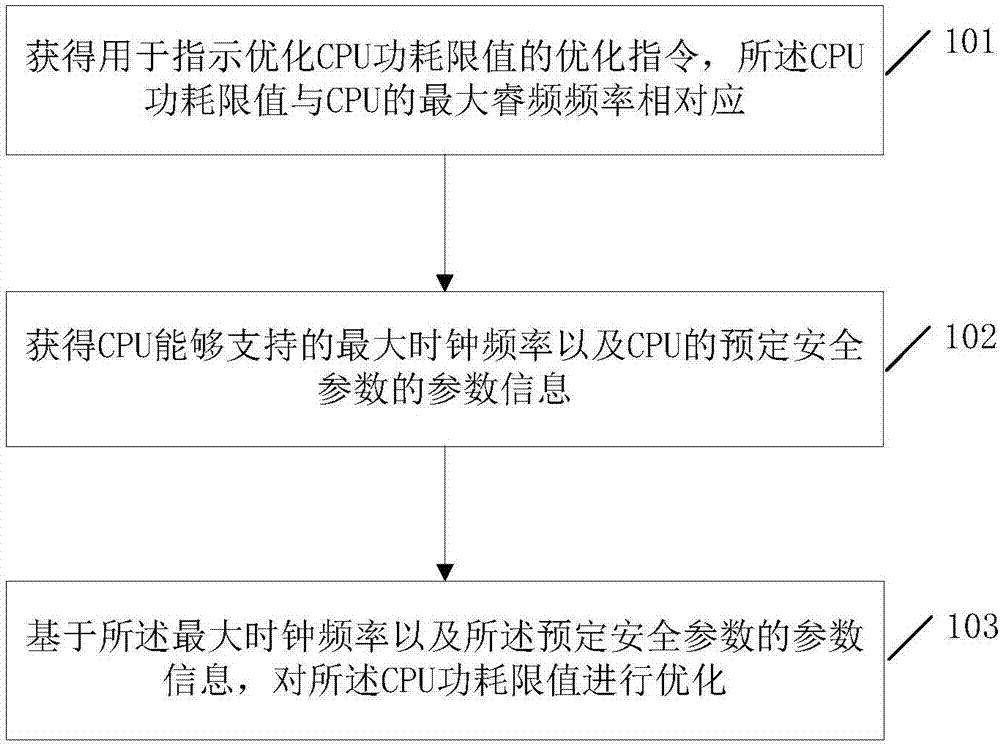

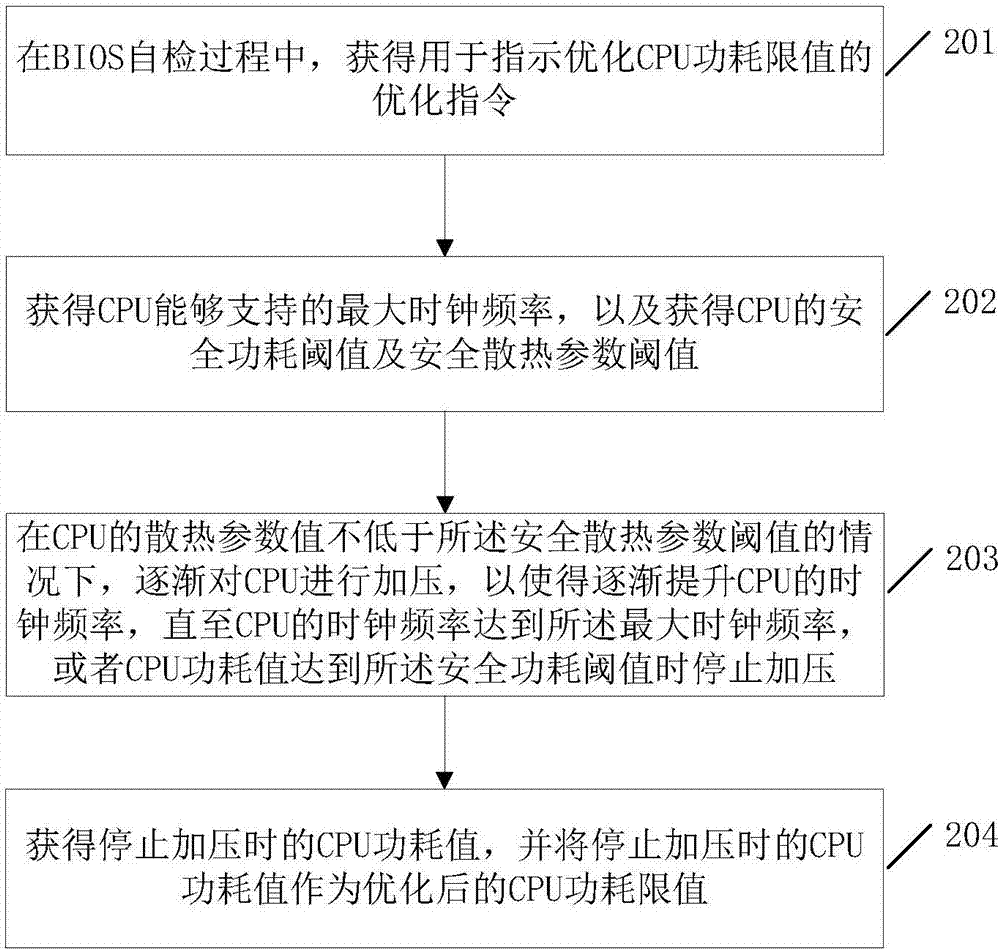

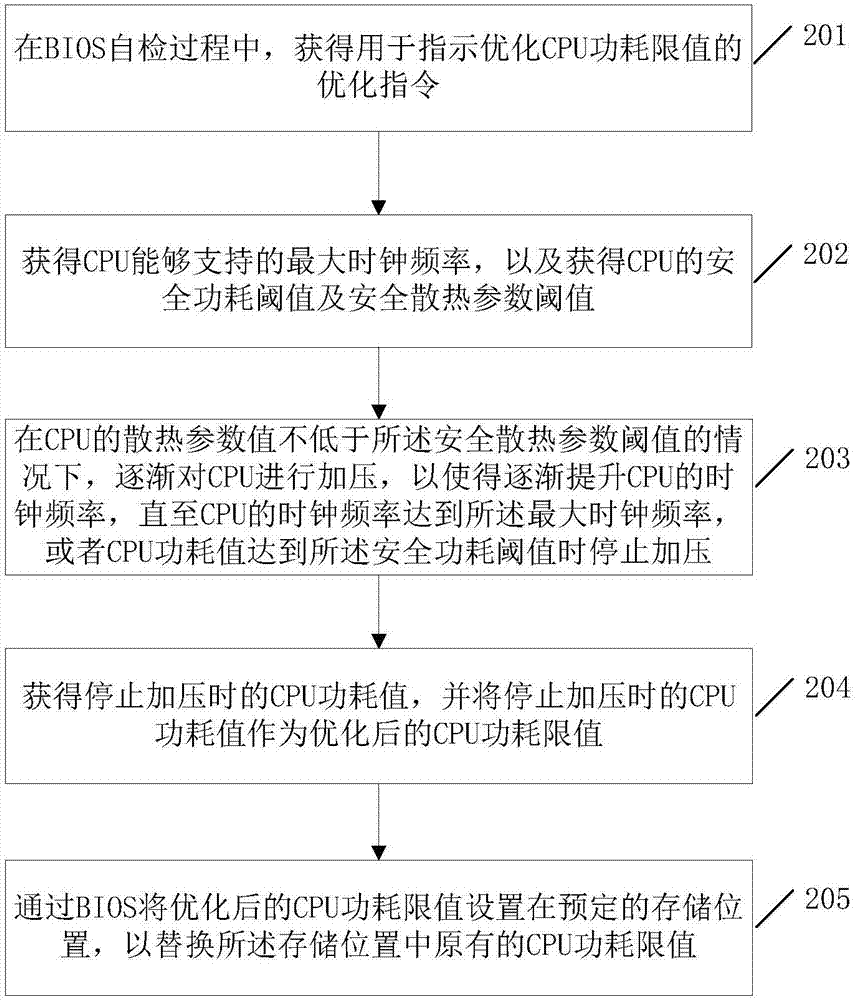

CPU (central processing unit) power consumption limit value optimizing method and electronic device

ActiveCN107992183AEnsure safetyProgram initiation/switchingPower supply for data processingUnsafe conditionClock rate

The invention discloses a CPU power consumption limit value optimizing method and electronic device. The CPU power consumption limit value optimizing method comprises, after an optimizing instructionfor indicating power consumption limit value optimization of a CPU is acquired, acquiring the maximum clock frequency that the CPU can support, and information of default safety parameters of the CPU,and based on the maximum clock frequency and the information of the default safety parameters, optimizing the CPU power consumption limit value corresponding to the maximum turbo frequency of the CPU. Therefore, the CPU power consumption limit value optimizing method is a scheme for automatically optimizing the CPU power consumption limit value corresponding to the maximum turbo frequency of theCPU, compared with manual optimizing manners in the prior art, the automatic scheme can be convenient and fast; due to the fact, during automatic optimization, the information of the default safety parameters of the CPU are taken into consideration, the CPU power consumption limit value optimizing method can effectively prevent the CPU from running under unsafe conditions and further ensure safetyof the CPU.

Owner:LENOVO (BEIJING) CO LTD

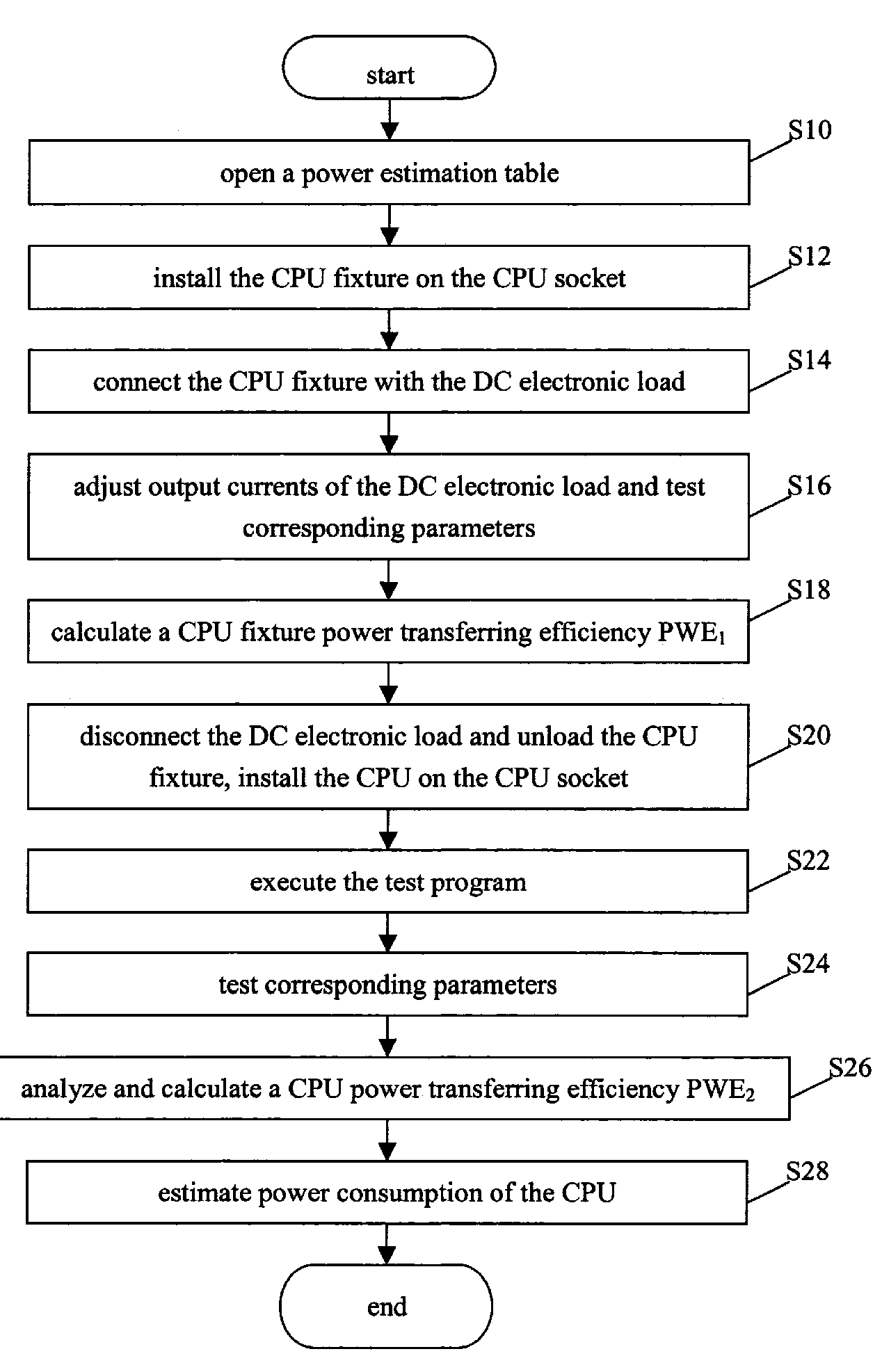

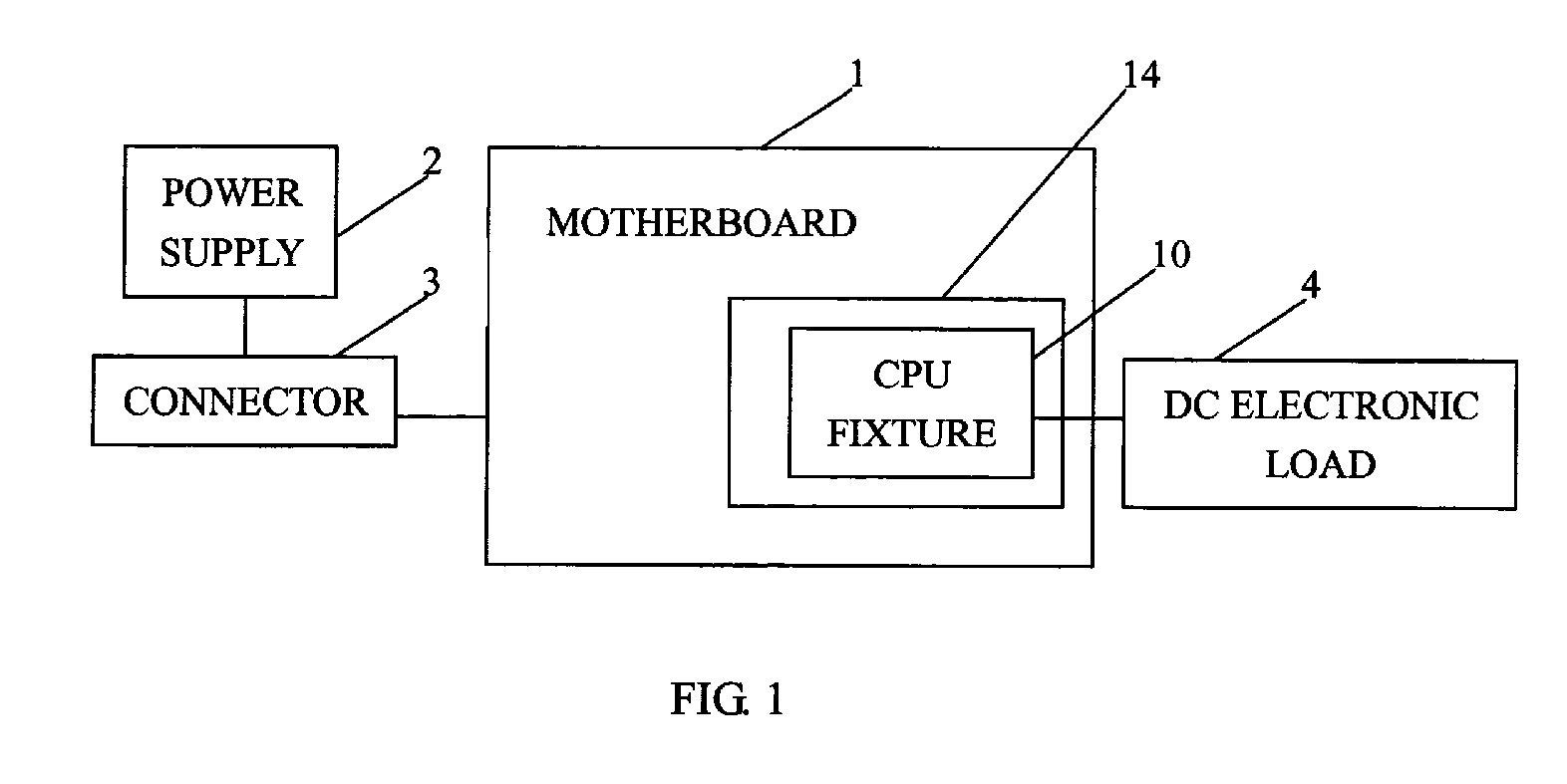

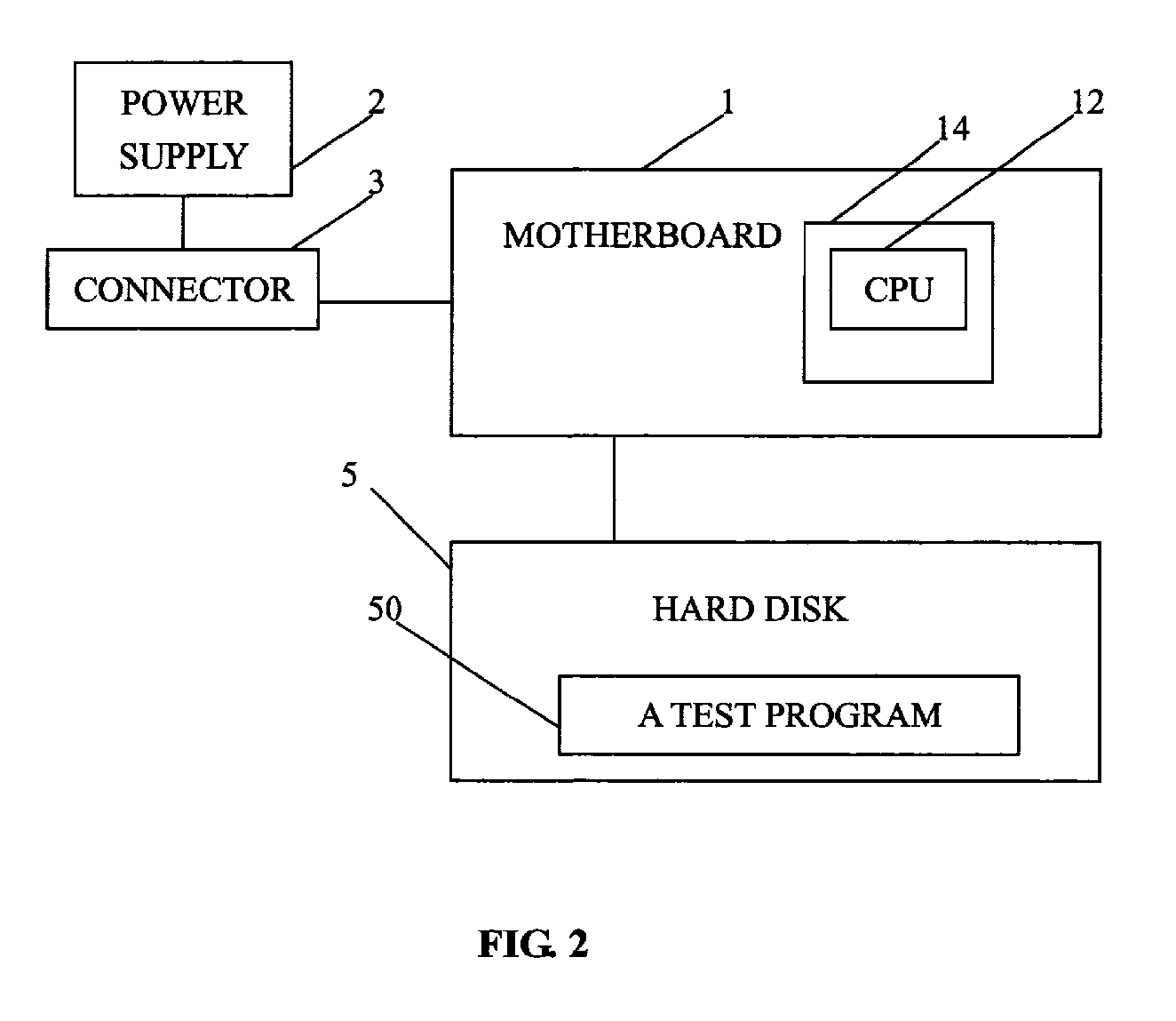

Method for estimating power consumption of a CPU

InactiveUS7424633B2Estimate the power consumption of the CPU more accurately and quicklyShort timeVolume/mass flow measurementHardware monitoringElectric power transmissionEngineering

Owner:HON HAI PRECISION IND CO LTD

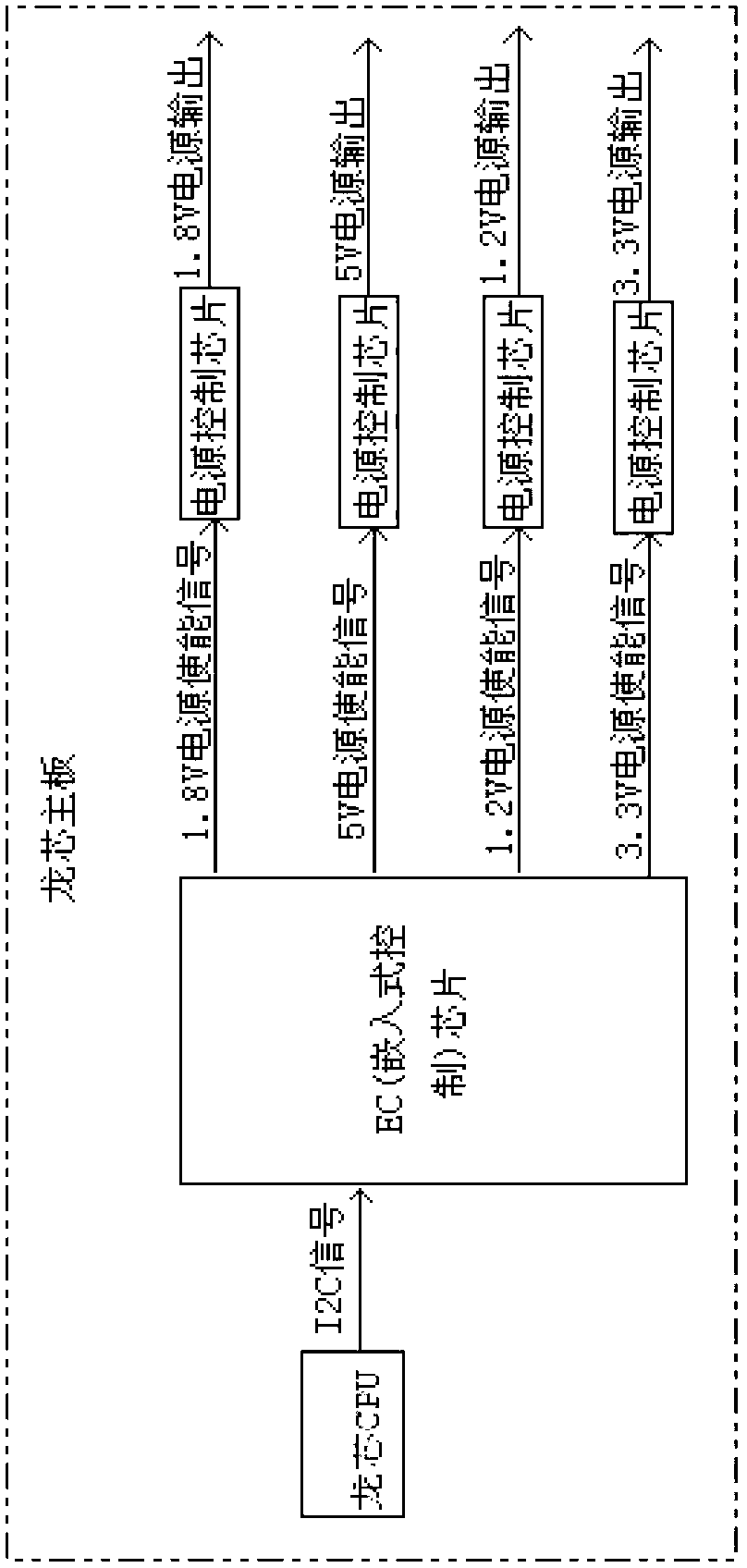

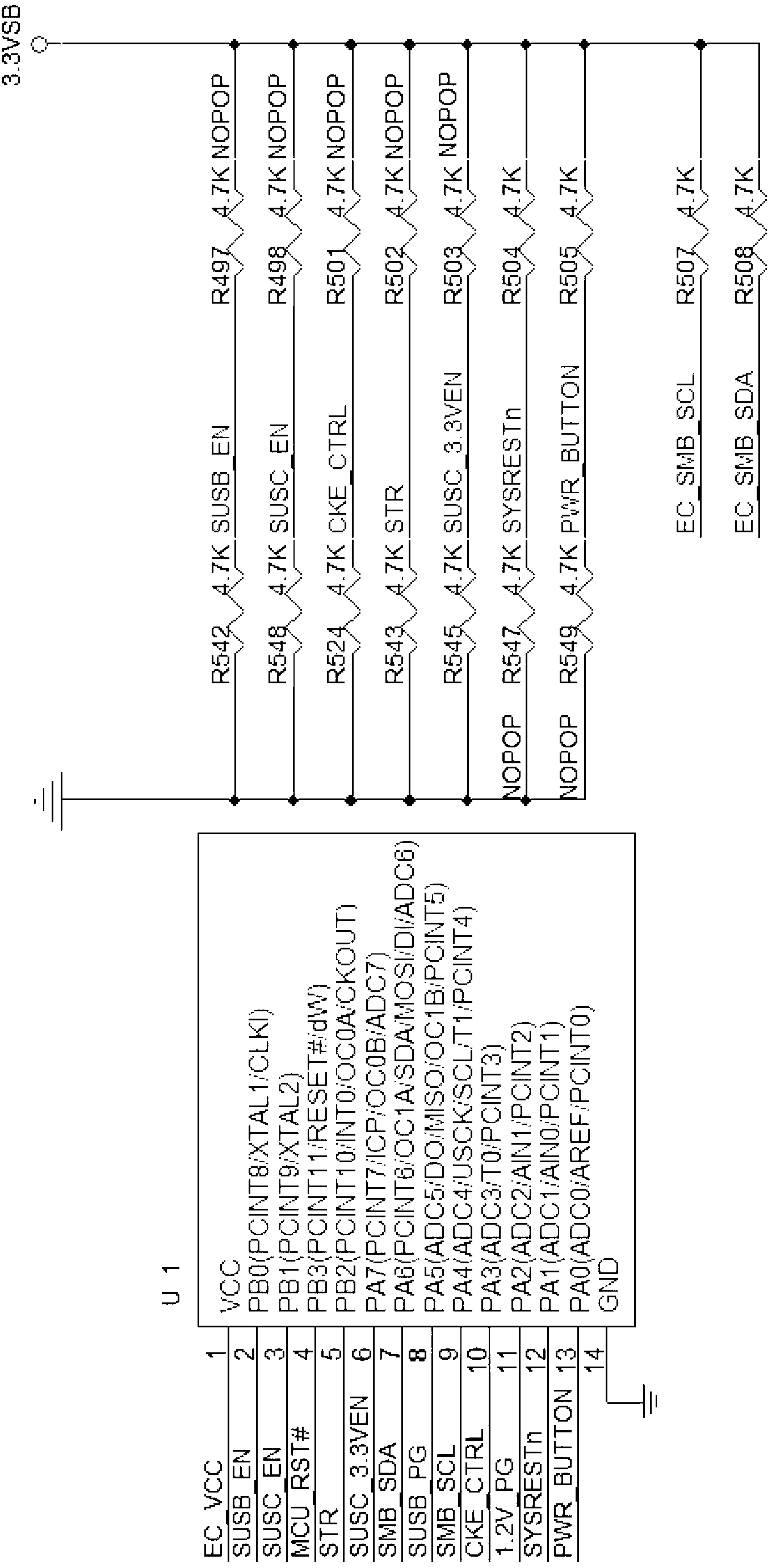

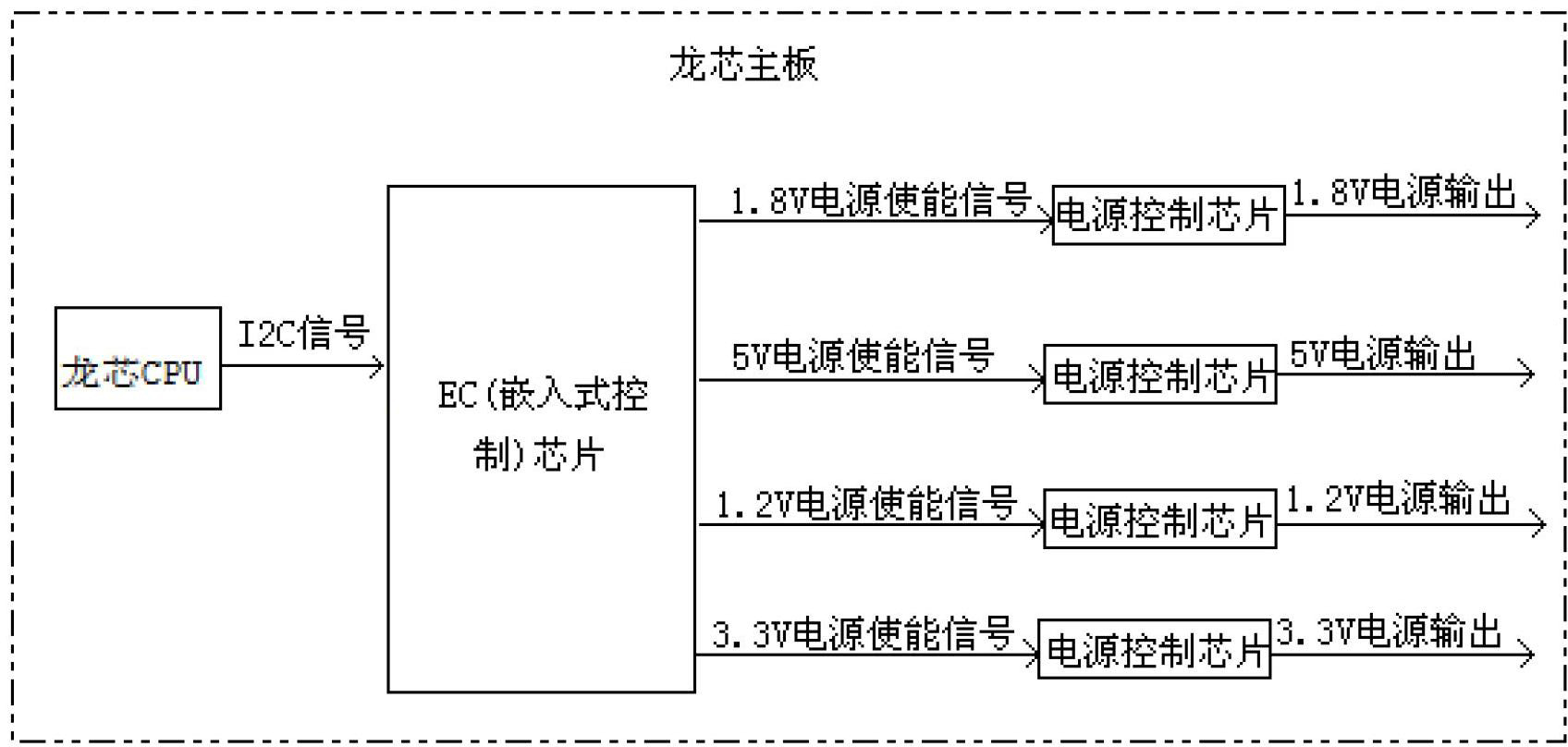

Shutdown and reset system and method of mainboard software

InactiveCN102707781AReduce power consumptionNo SouthbridgeData resettingCPU power dissipationEmbedded system

The invention discloses a shutdown and reset system and a shutdown and reset method of mainboard software. The shutdown and reset system comprises a processer, a single EC (electronic computer) chip and a main power supply control chip on a hardware mainboard, wherein the processor is a processer of a hardware mainboard without a south bridge, the processor sends I2C signals, and outputs the I2C signals to an input end of the EC chip; and an output end of the EC chip is connected with an input end of the power supply control chip. The shutdown and reset method of the mainboard software comprises a shutdown method and a reset method. The integral type and desk type computers can be shut down and reset by adopting the independent EC chip so as to realize a domestic loongson CPU (central processing unit) mainboard without the south bridge and a mainboard of a Super IO (input / output) control chip. The shutdown and reset system has low power consumption. The power consumption of the entire mainboard is less than 30watt, and the CPU power consumption on the mainboard is less than 5watt.

Owner:JIANGSU LEMOTE TECH CORP

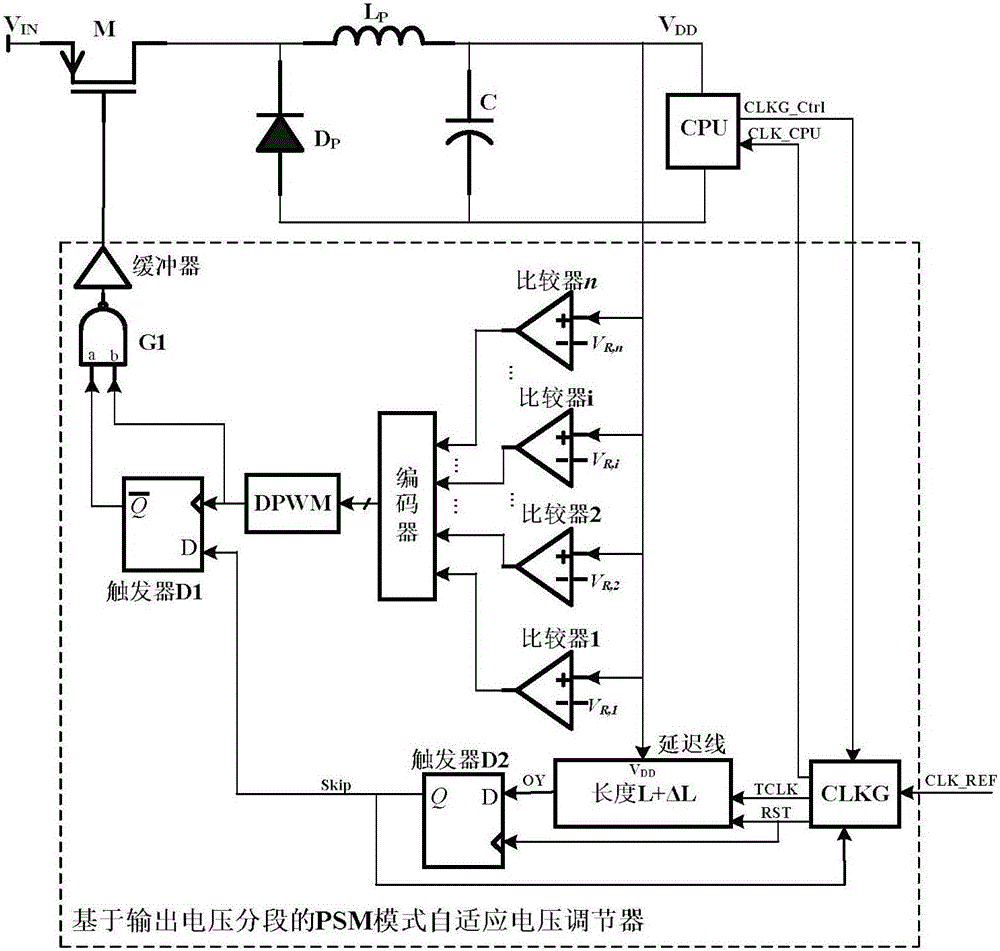

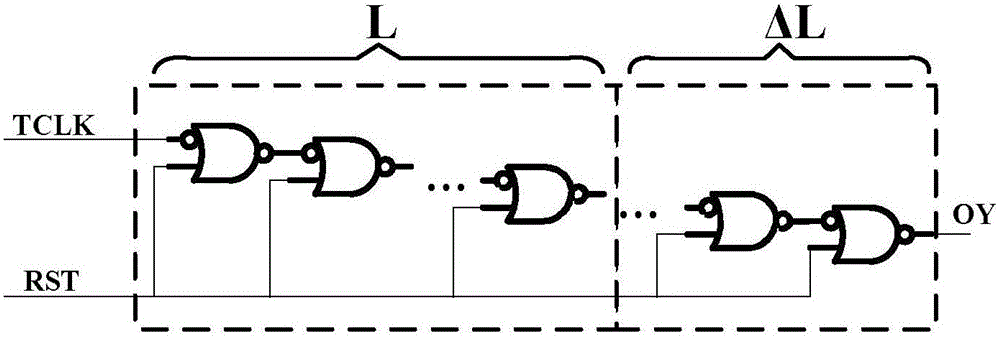

PSM mode adaptive voltage regulator based on output voltage segmentation

ActiveCN105955380AImprove transient response characteristicsReduce lossElectric variable regulationControl signalEngineering

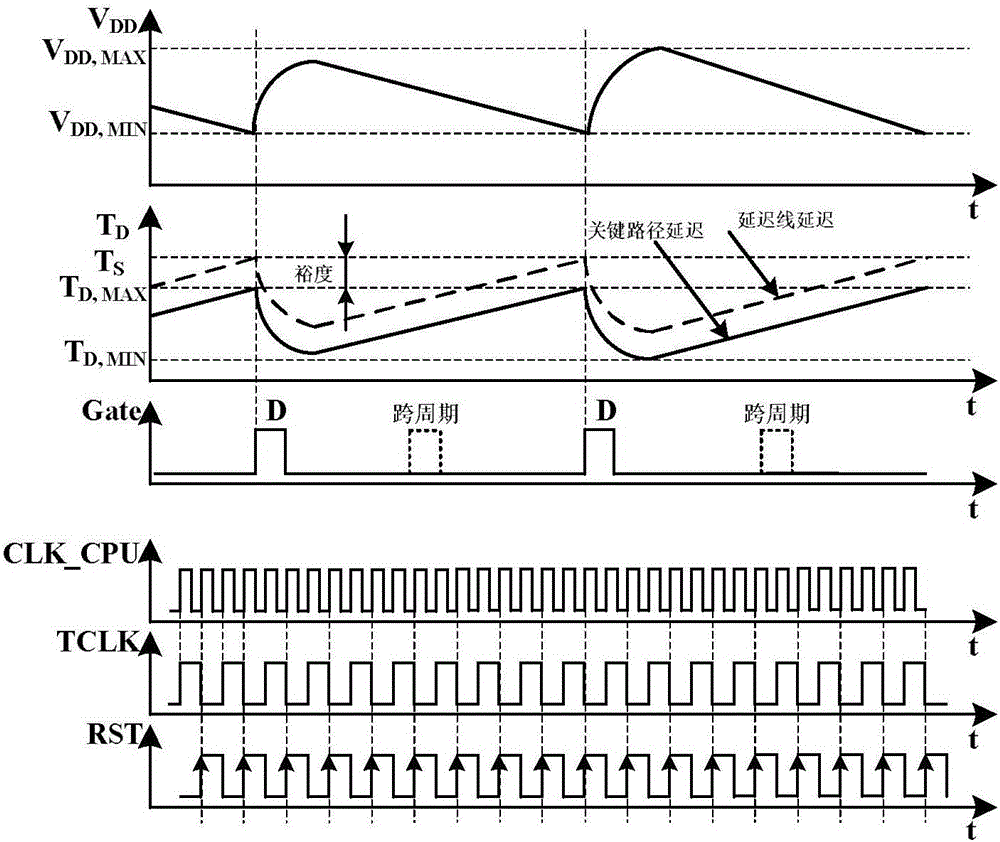

The invention discloses a PSM mode adaptive voltage regulator based on output voltage segmentation, and aims to provide a voltage regulator which is good in transient response characteristics and high in power conversion efficiency under light load and can effectively reduce power consumption of the CPU of a load processor. According to the technical scheme, a clock signal generator generates three clock signals including a load processor clock, a delay line resetting signal and a delay testing signal according to a control signal requested by an external CPU; compared with a rising edge of the delay testing signal, a rising edge of the delay line resetting signal is lagged by a clock period TS of the load processor clock signal; and when a testing signal in the TS is transmitted to a data input end of a trigger D2, the CPU of the load processor judges whether output voltage of a power converter can enable a key path of the CPU to work normally or not according to the transmission condition of the delay testing signal in a delay line, output voltage of the power converter is adjusted according to the detected result, and CPU delay is adaptively adjusted to be L / (L+ deltaL) times of the TS.

Owner:10TH RES INST OF CETC

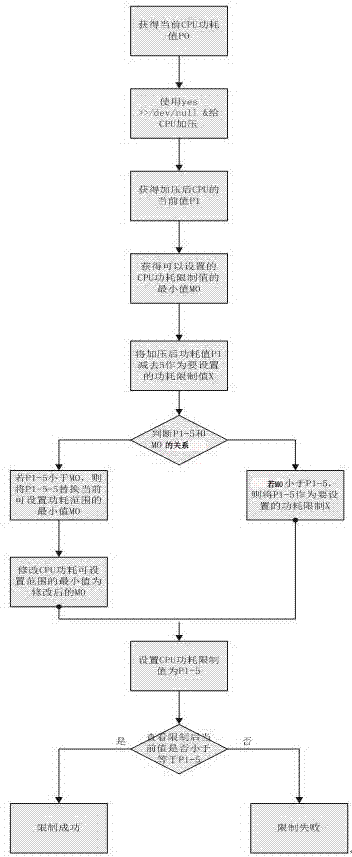

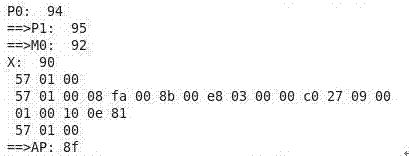

Method for automatically verifying CPU (central processing unit) power consumption limit function

ActiveCN107992388AImplement automated testingShorten test timeFaulty hardware testing methodsFunctional testingTested time

The invention discloses a method for automatically verifying a CPU (central processing unit) power consumption limit function, and relates to the field of server software. The method includes the steps: performing pressuring on a CPU to obtain a power consumption value P1 of the pressured CPU; acquiring a settable minimum value M0 of CPU power consumption limit; subtracting five from the power consumption value P1 of the pressurized CPU to serve as a power consumption limit value X to be set; comparing X and M0, directly setting CPU power consumption limit or amending the settable minimum value to limit CPU power consumption, and viewing whether the CPU power consumption is successfully limited or not after setting to achieve automatically testing of the CPU power consumption limit function. Compared with a traditional manual testing method, the CPU power consumption limit function is automatically tested, the method is simple and easy to use, testing time greatly saved, and working efficiency is improved.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

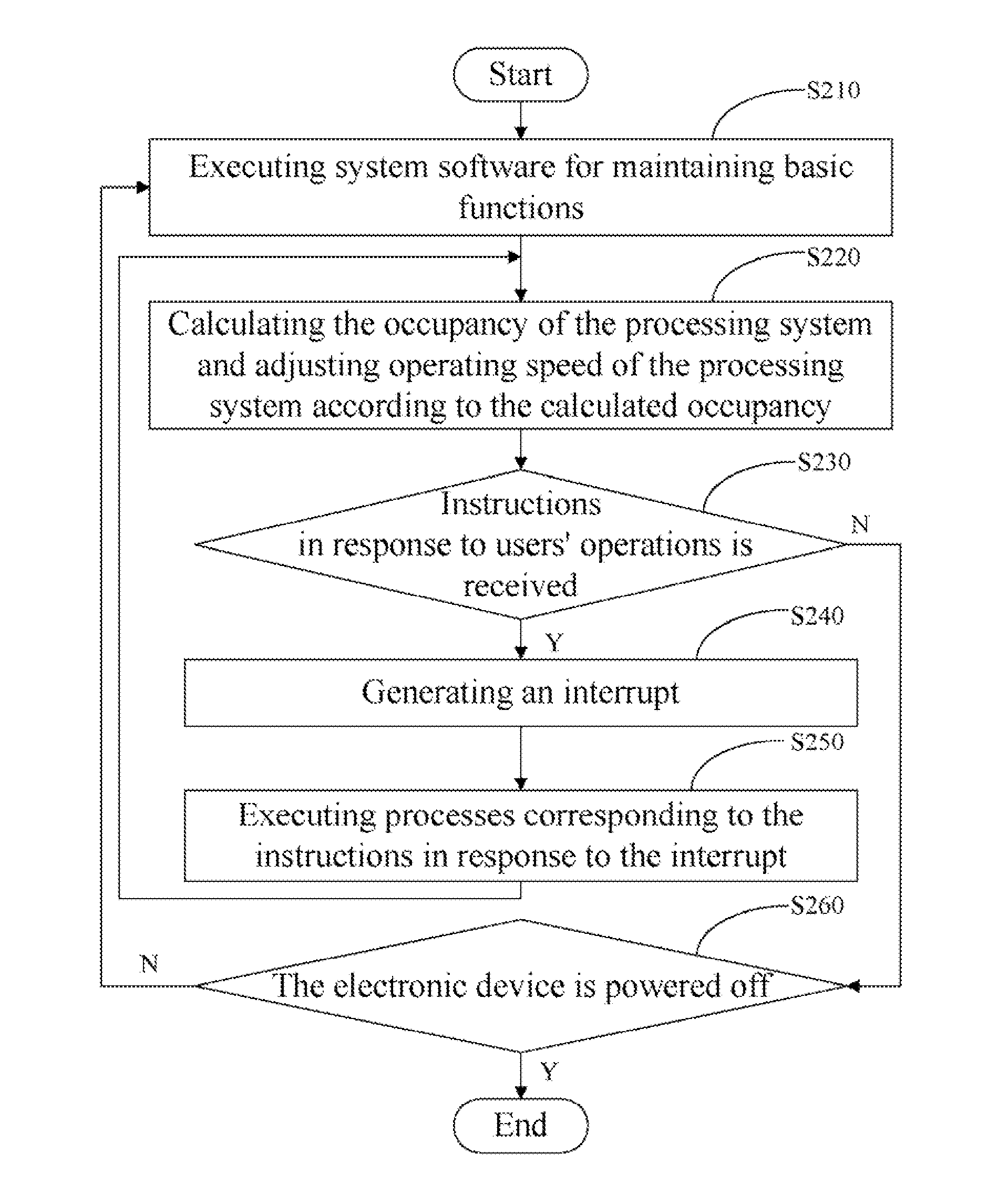

Electronic device and method for reducing CPU power consumption

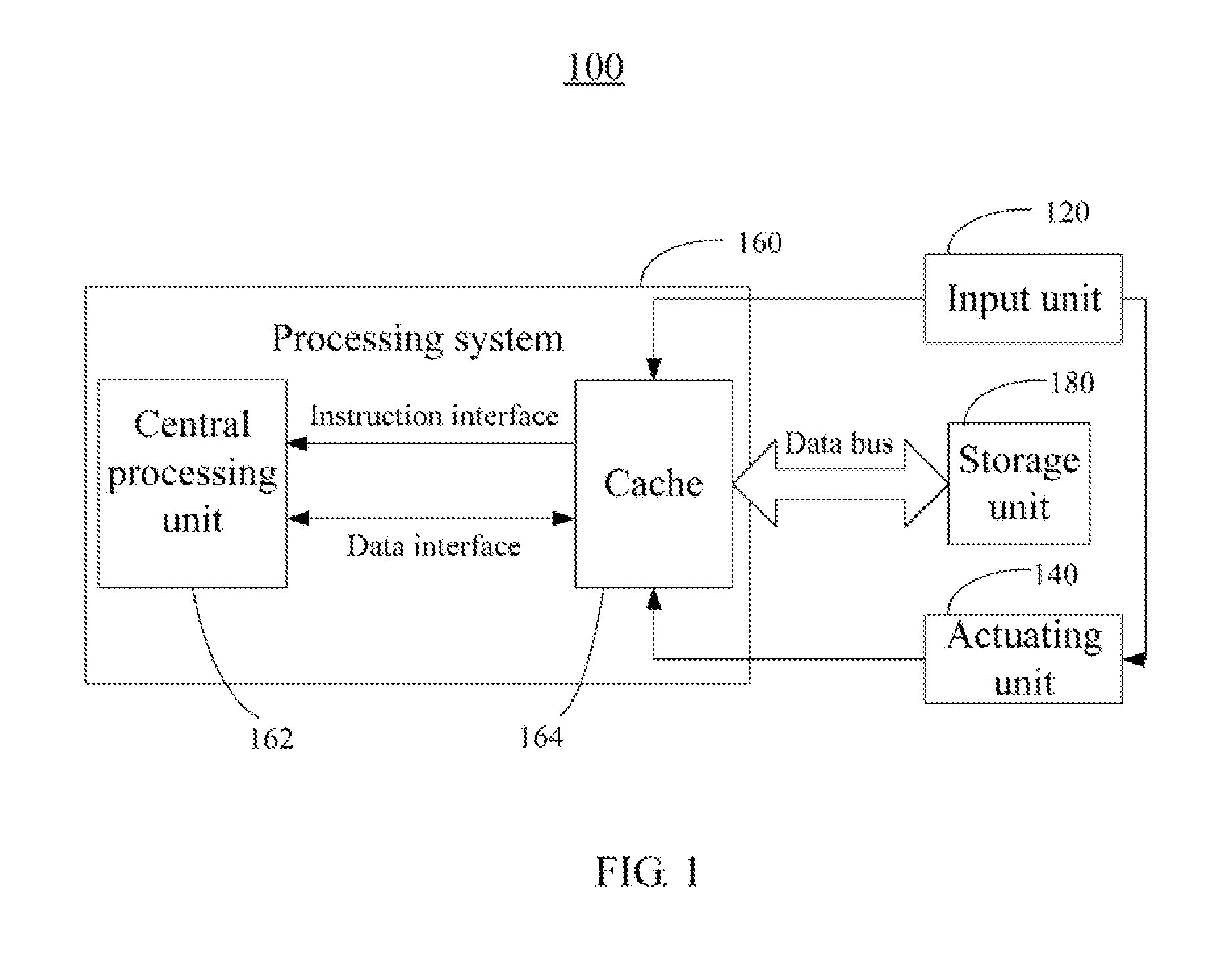

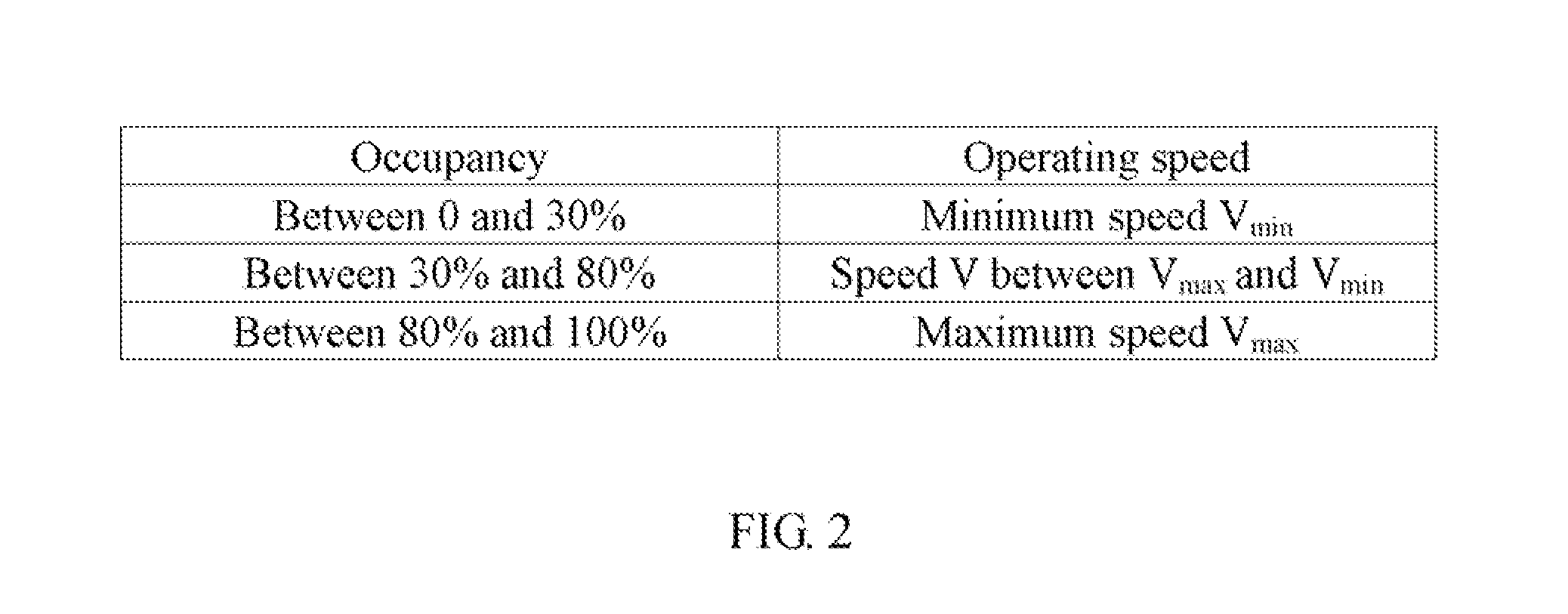

InactiveUS20140157022A1Increased power consumptionWaste of energyPower supply for data processingEnergy efficient computingComputer hardwareCPU power dissipation

An electronic device includes a processing system, a storage unit for storing a table, an input unit for generating instruction in response to the operations of the user, and an actuating unit for generating an interrupt in response to the instructions to request the processing system to execute the instructions to perform desired functions. The table recording a relationship between an occupancy and a desired operating speed of the processing system. When the processing system is requested to execute instructions, the processing system calculates the occupancy and adjusts operating speed according to the calculated occupancy and the table. A method for reducing CPU power consumption is also provided.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1