Chip test method, system and apparatus

A test equipment and chip testing technology, applied in the field of testing, can solve the problems of not being able to modify the test logic, affecting the test speed, increasing the chip area, etc., to achieve the effect of improving the test speed, reducing the area and reducing the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

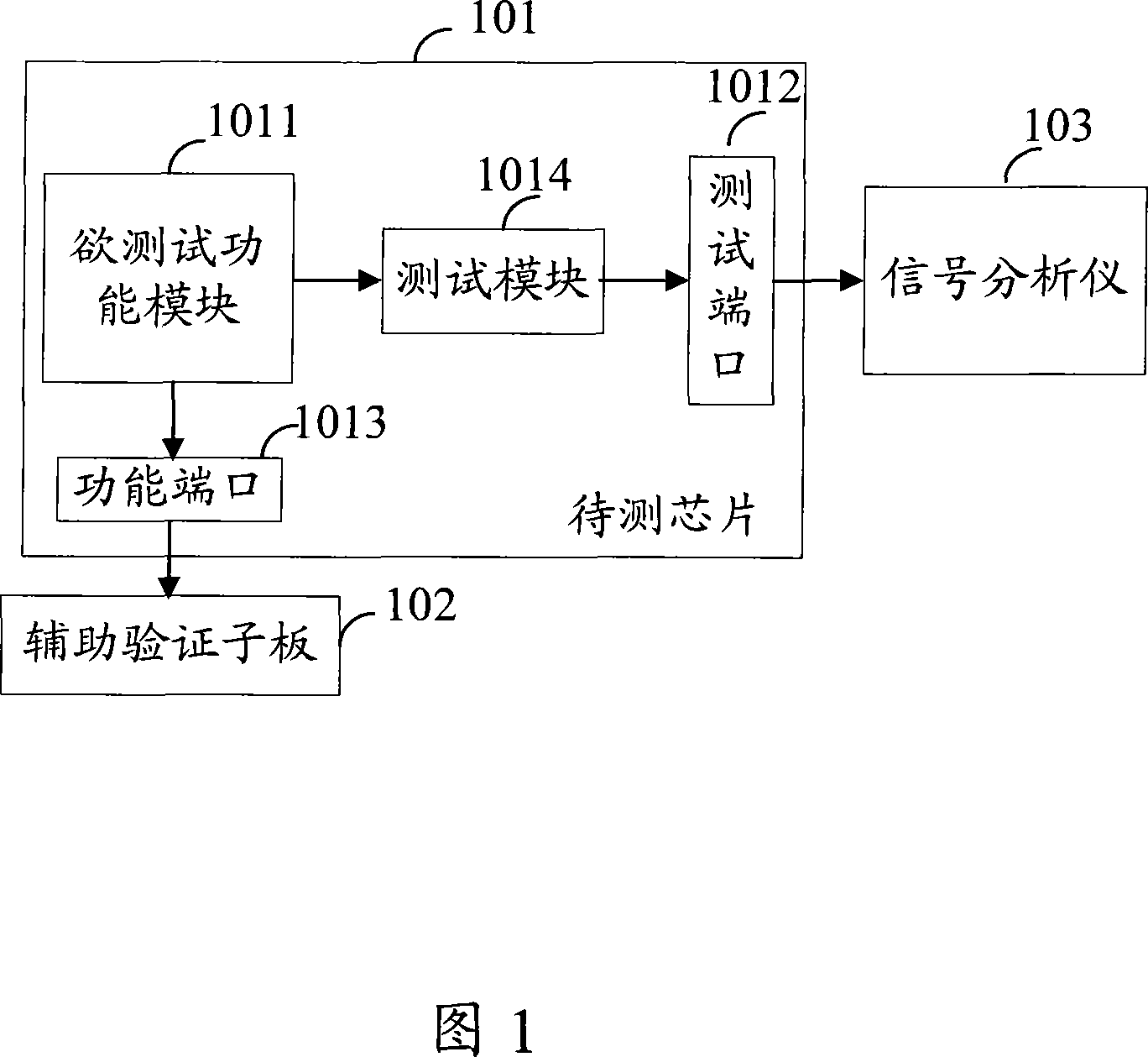

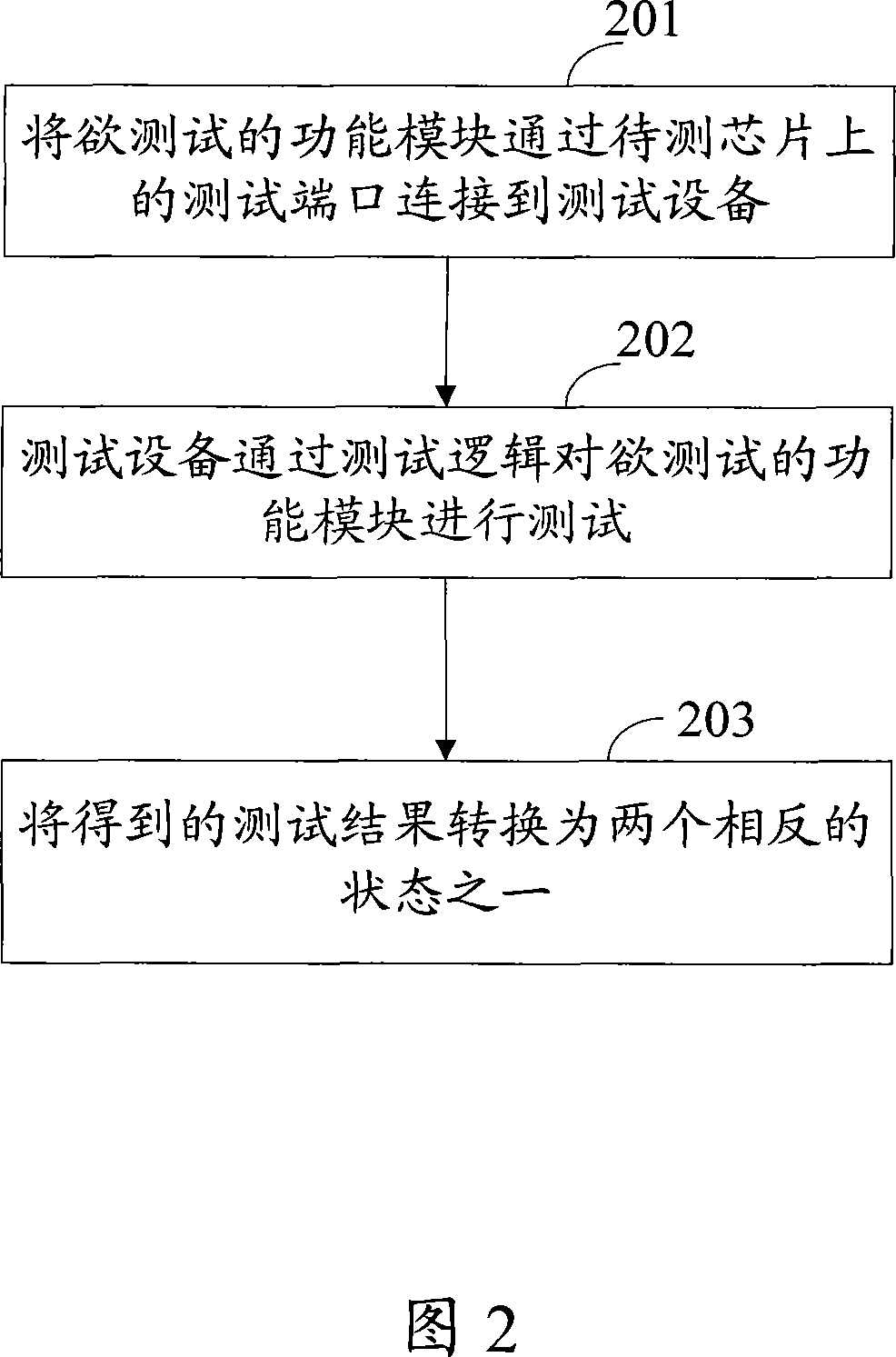

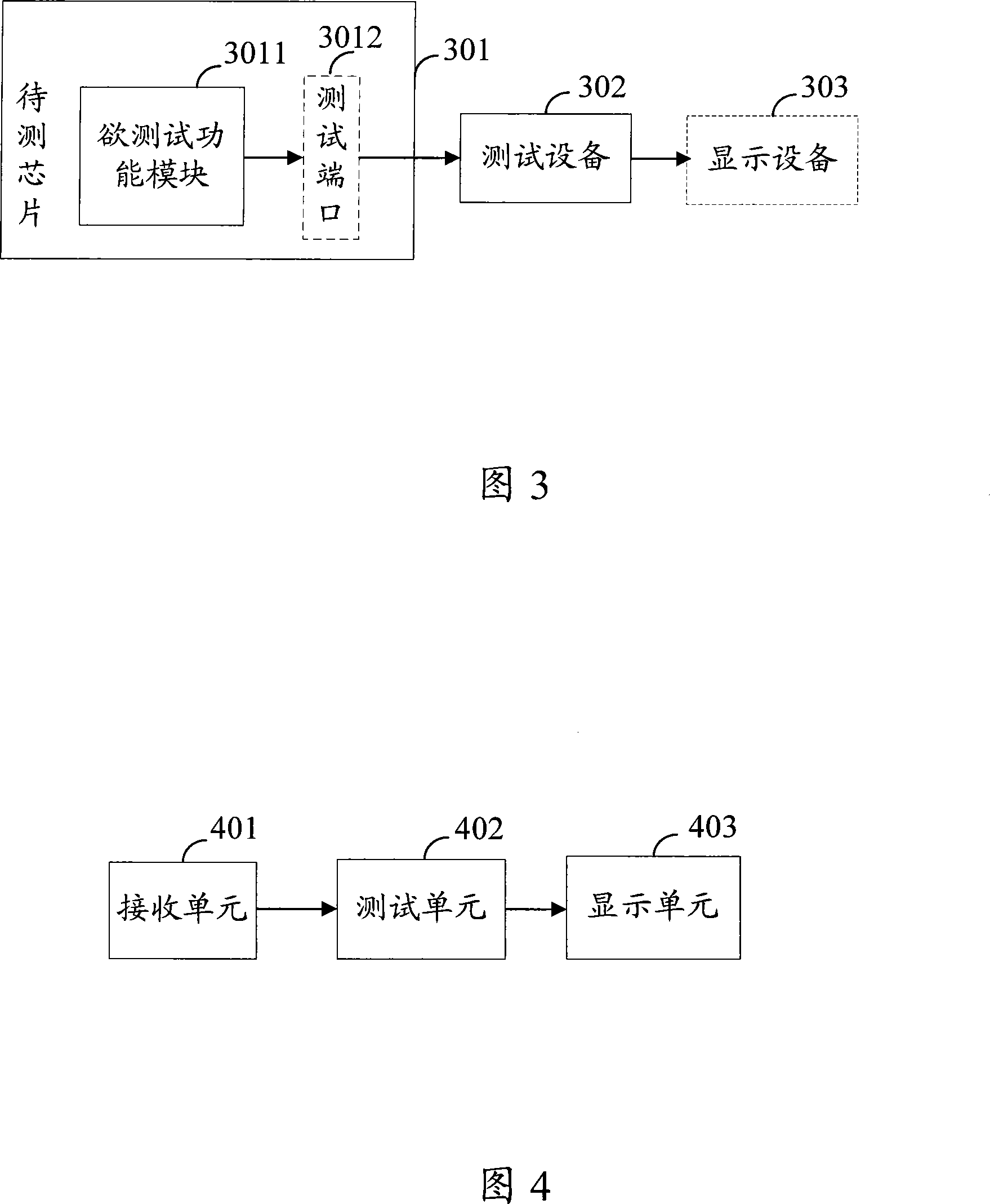

[0043] Different from the prior art, the embodiment of the present invention is to first estimate the errors that may occur in the functional modules to be tested on the chip to be tested; set the test logic for testing the errors, and set the test logic in the in test equipment external to the chip. In this way, the method for testing the chip to be tested in the embodiment of the present invention mainly includes: the test device tests the functional module through the test logic; converts the obtained test result into one of two opposite states, so The two opposite states respectively indicate whether there is an error in the functional module, so that the test logic can be modified according to the new debugging scheme, and the test speed can be imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More