Nand flash memory device with ecc protected reserved area for non volatile storage of redundancy data

A technology for non-volatile storage and non-volatile data, applied in the field of NAND flash memory devices, which can solve problems such as burdensomeness, inability of unit blocks to be electrically isolated from each other, and implementation obstacles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

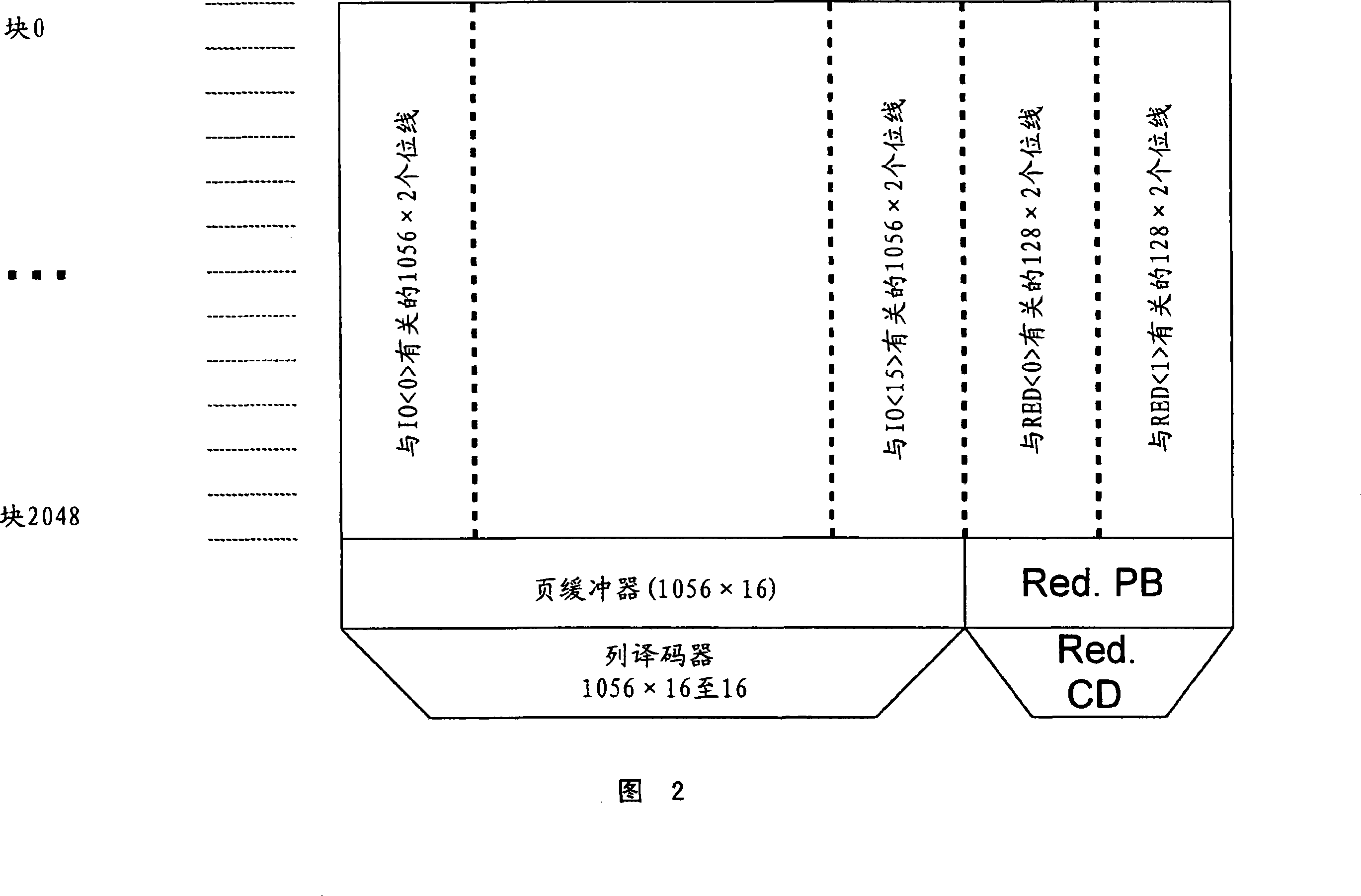

[0028] As represented graphically in FIG. 3, the reserved area RA (identified with dark areas) that will not be addressed by the user of the EWS tested, adjusted, repaired and finalized memory device is the addressable area of the memory cell array , which maintains virtually the same organizational structure as defined graphically in Figure 2.

[0029] In FIG. 3, black dots represent failed cells that cannot be used (as identified during the on-wafer test of the device), while vertical solid lines represent failed bit lines of the array (as also identified during the on-wafer test phase). ).

[0030] The substantially redundant data on the failed array elements identified during the EWS test are written during the EWS phase itself in the reserved area RA of the addressable area of the memory cell array, which is denoted by the dark array area in Figure 3. logo.

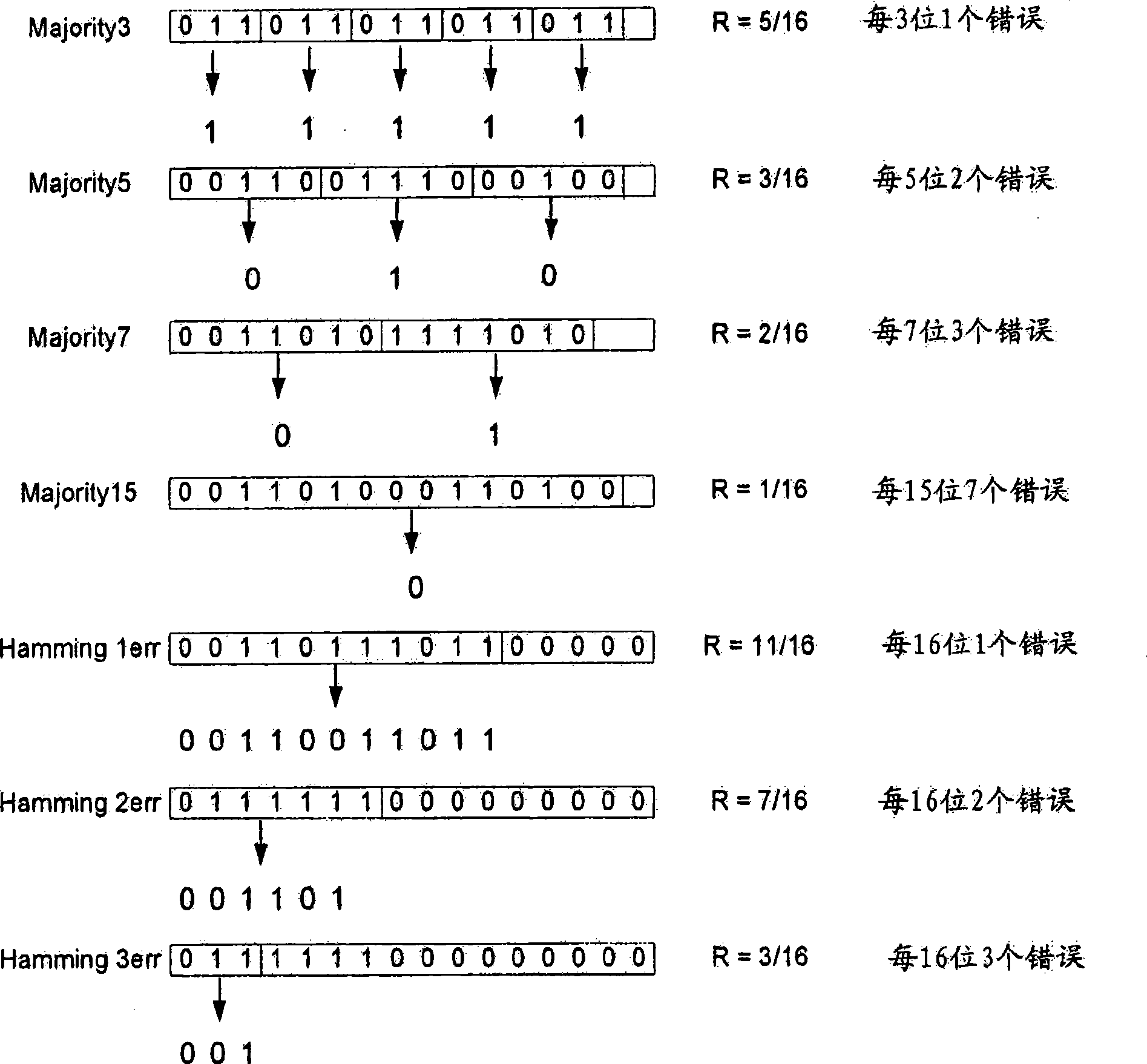

[0031] Writing of substantially redundant data in the reserved area is performed using an ECC data writing t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More