Transport protocols suitable for multiprocessor network on chip

A network-on-chip, transmission protocol technology that is used in transmission systems, error prevention/detection using return channels, electrical components, etc., to solve problems such as the inability of bus structures to effectively support processors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

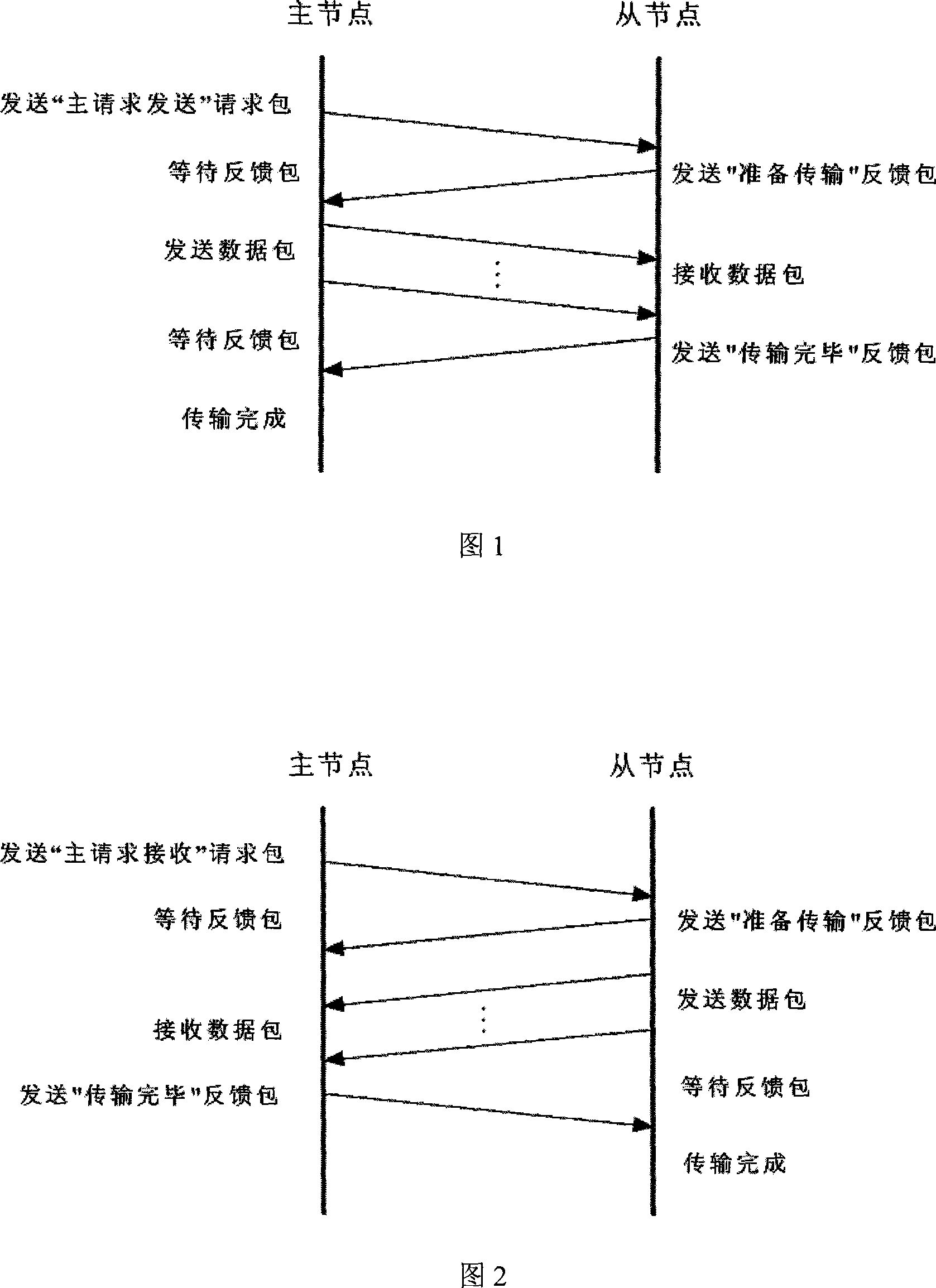

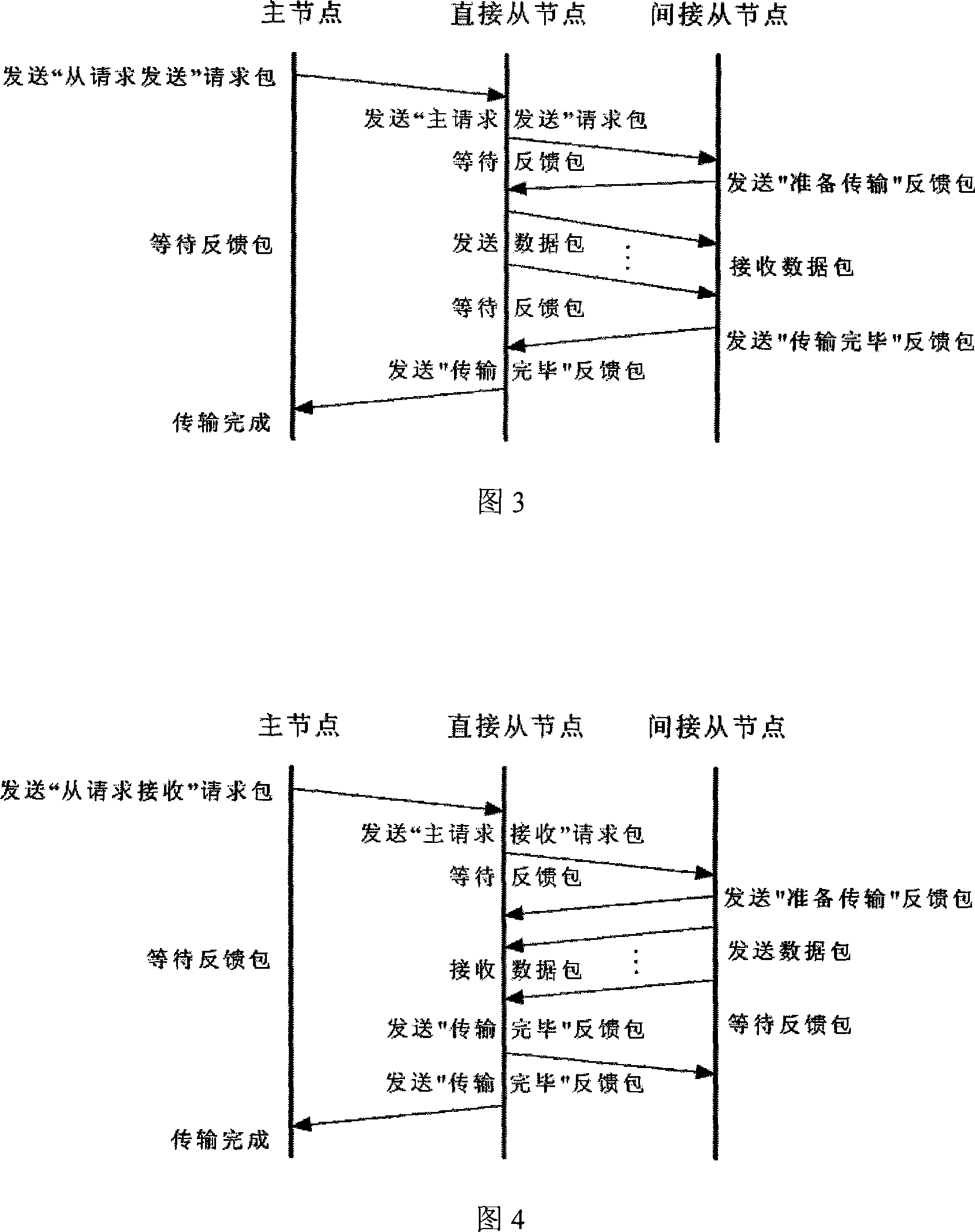

[0072] A specific embodiment of the present invention will be described below in conjunction with the accompanying drawings, but it is not intended to limit the present invention. This implementation example includes four transmission processes: master request sending, master request receiving, slave request sending and slave request receiving.

[0073] In this embodiment, the network on chip includes three nodes, node zero can initiate master request transmission and slave request transmission, node I and node II can respond to master request transmission and slave request transmission, and initiate master request transmission. The data address is 32 bits, and it is a byte address, the data transmission amount is 16 bits, and the node number is 3 bits. Packets in the network-on-chip arrive out of order. The bit width of the packet is 88 bits, including 8 bits of header information and 80 bits of payload.

[0074] The header information includes a 2-bit packet type, a 3-bit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More