Patents

Literature

33 results about "Multiprocessor network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

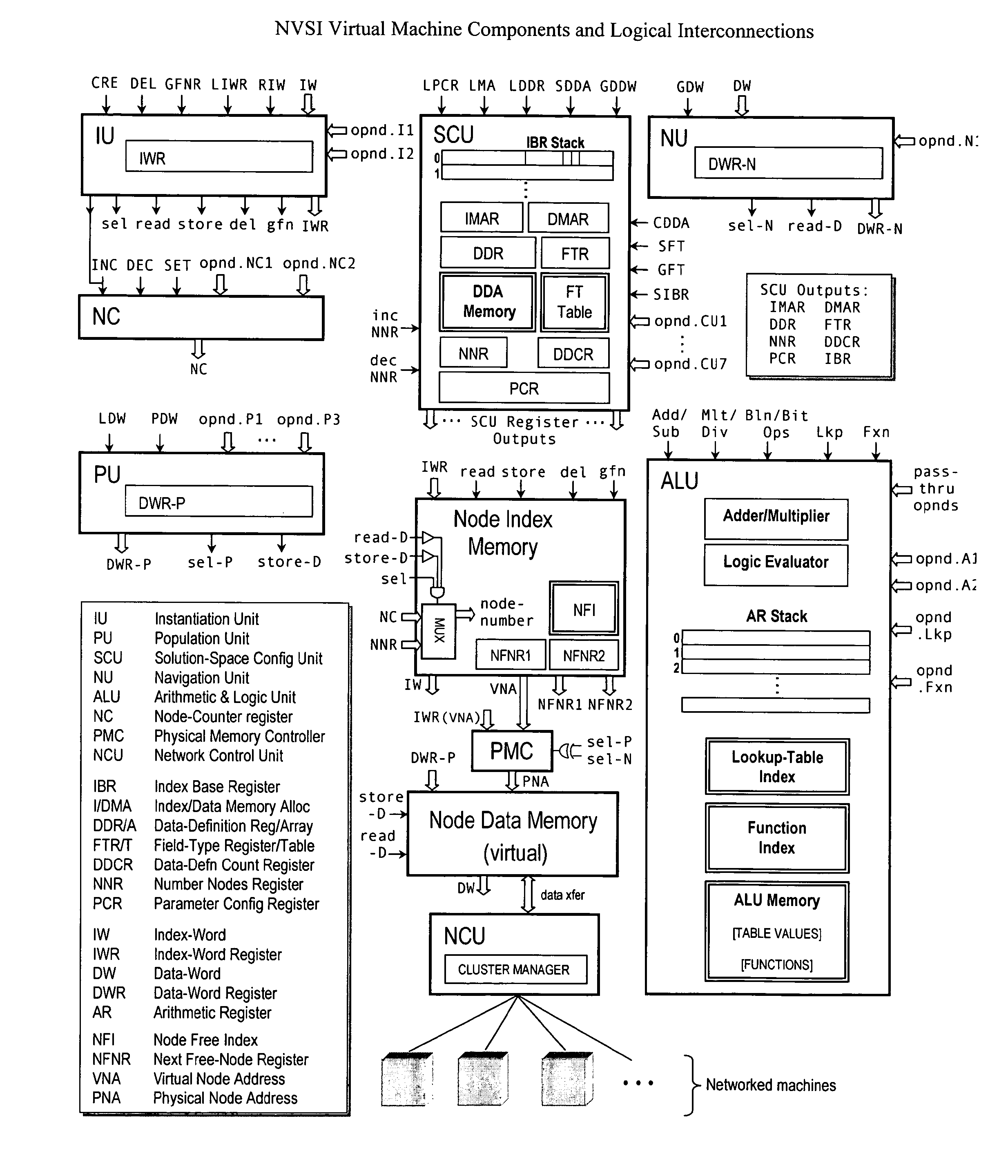

Virtual supercomputer

ActiveUS7774191B2Improve efficiencyFinanceResource allocationInformation processingOperational system

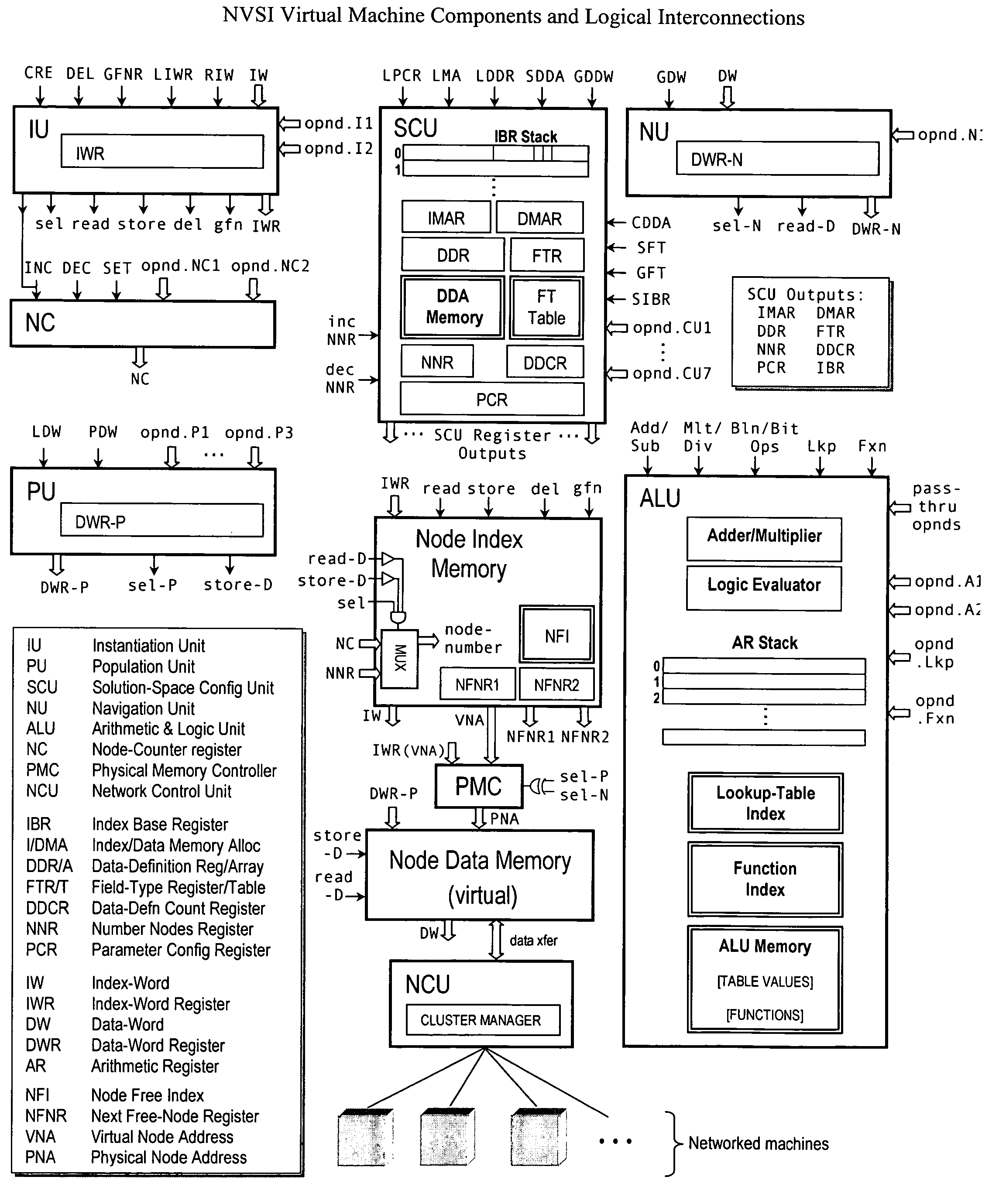

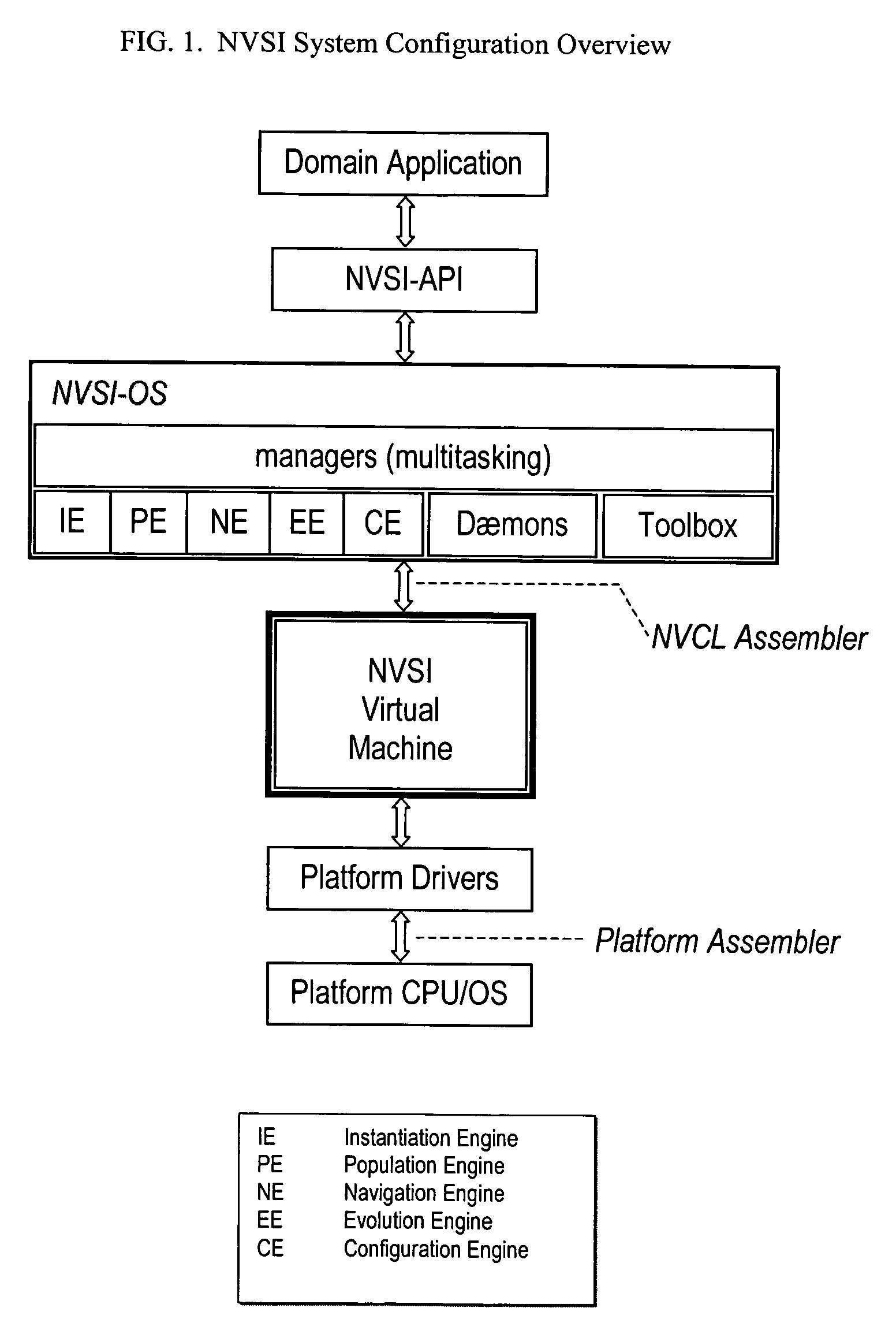

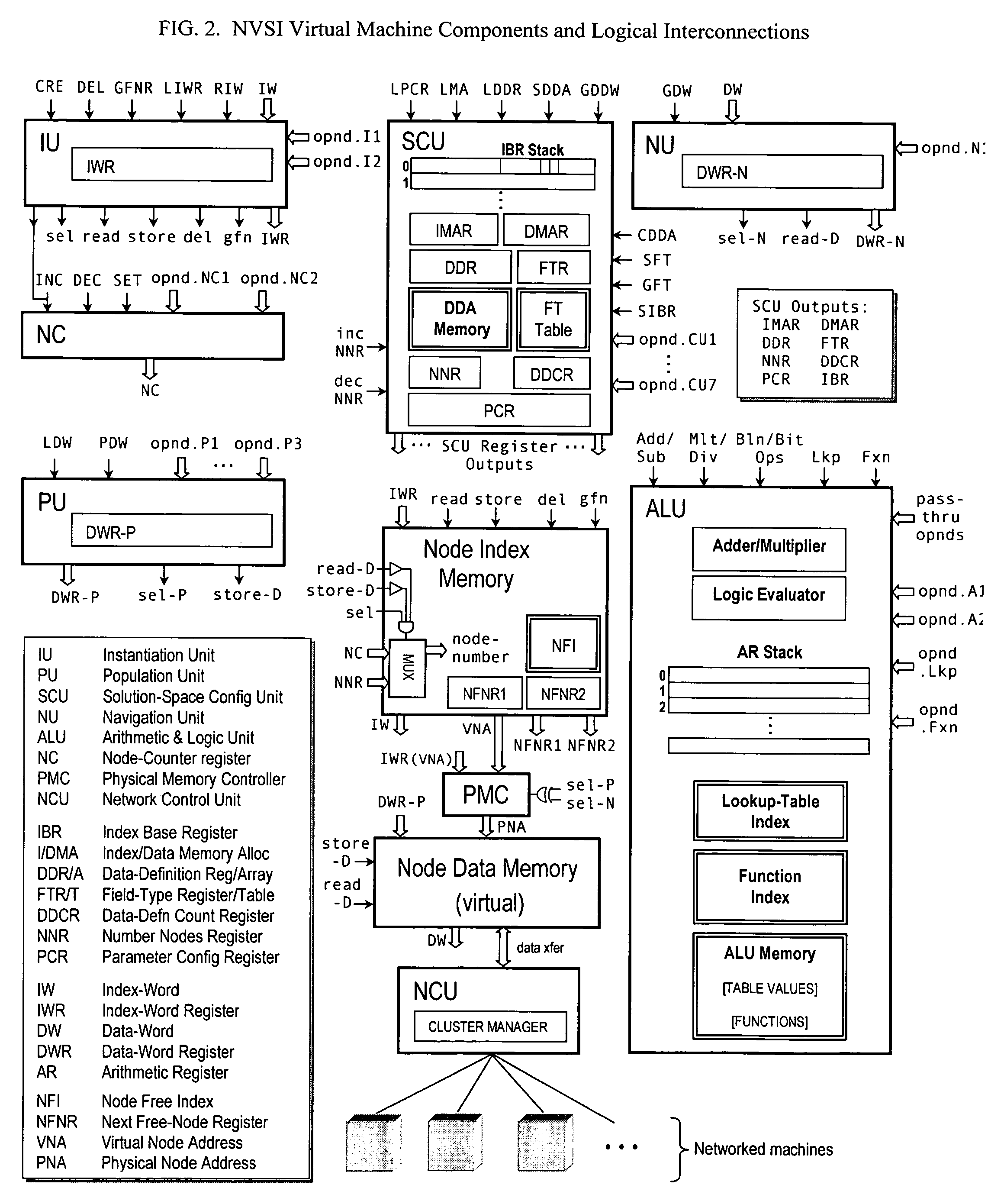

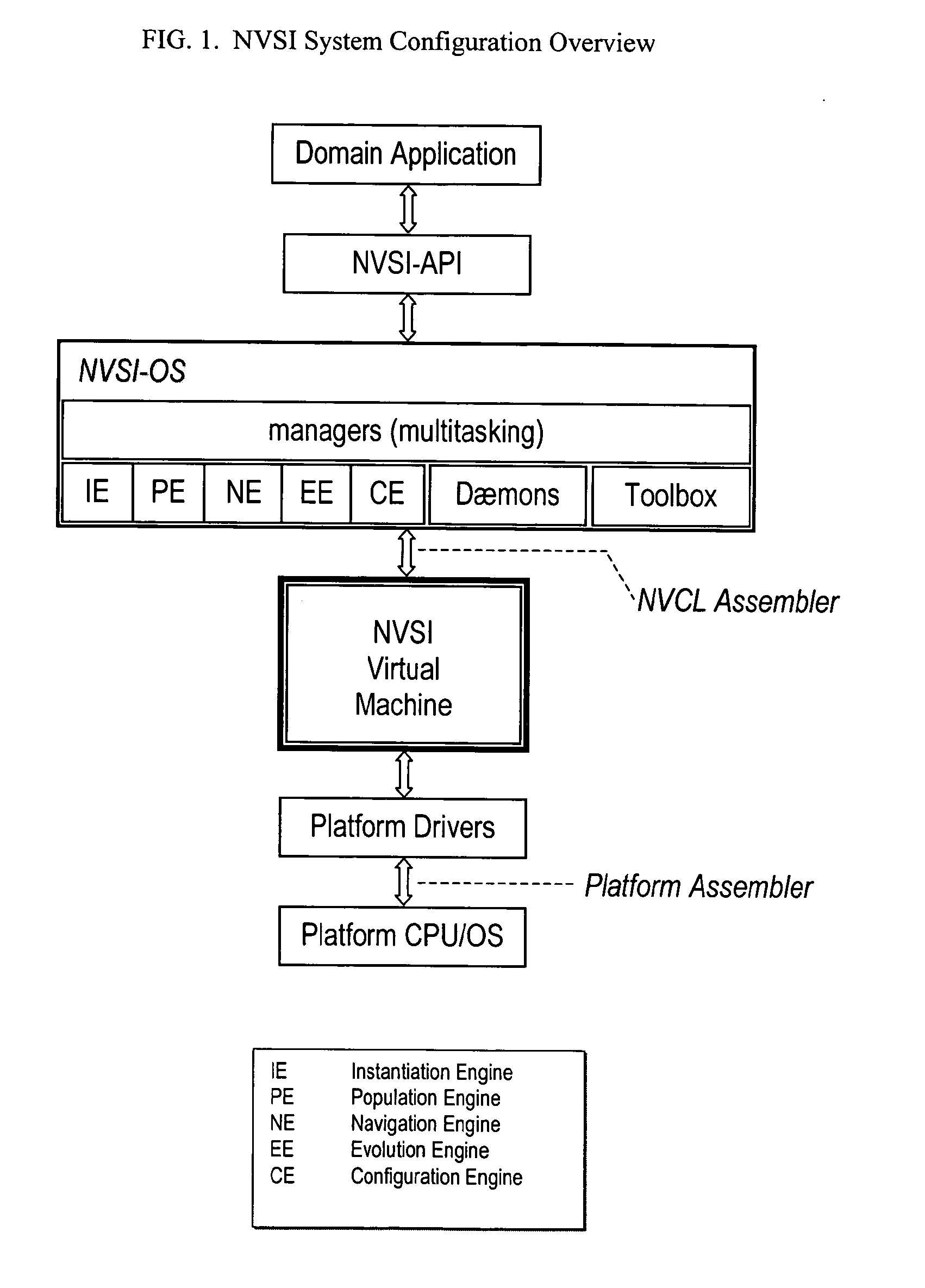

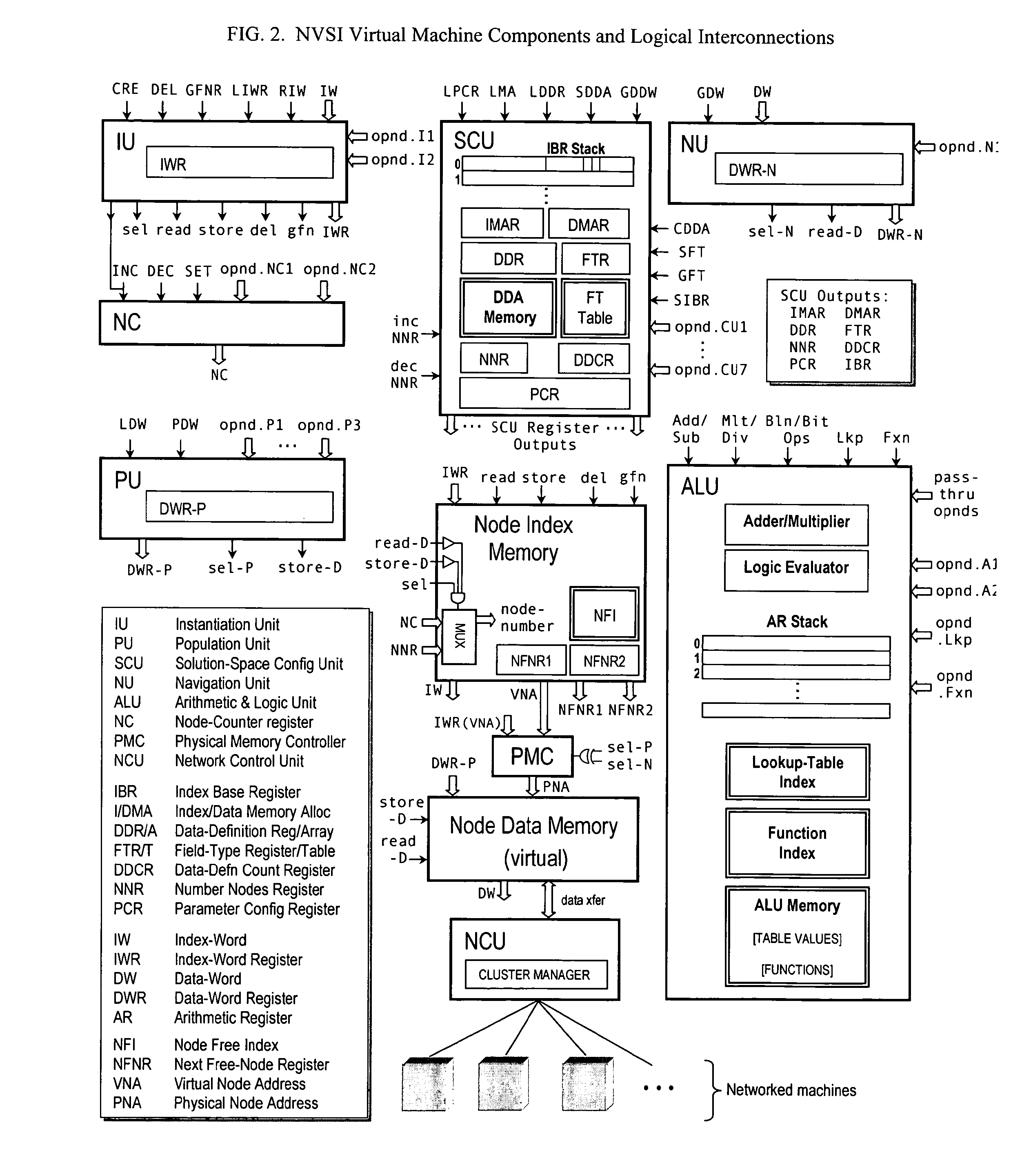

The virtual supercomputer is an apparatus, system and method for generating information processing solutions to complex and / or high-demand / high-performance computing problems, without the need for costly, dedicated hardware supercomputers, and in a manner far more efficient than simple grid or multiprocessor network approaches. The virtual supercomputer consists of a reconfigurable virtual hardware processor, an associated operating system, and a set of operations and procedures that allow the architecture of the system to be easily tailored and adapted to specific problems or classes of problems in a way that such tailored solutions will perform on a variety of hardware architectures, while retaining the benefits of a tailored solution that is designed to exploit the specific and often changing information processing features and demands of the problem at hand.

Owner:VERISCAPE

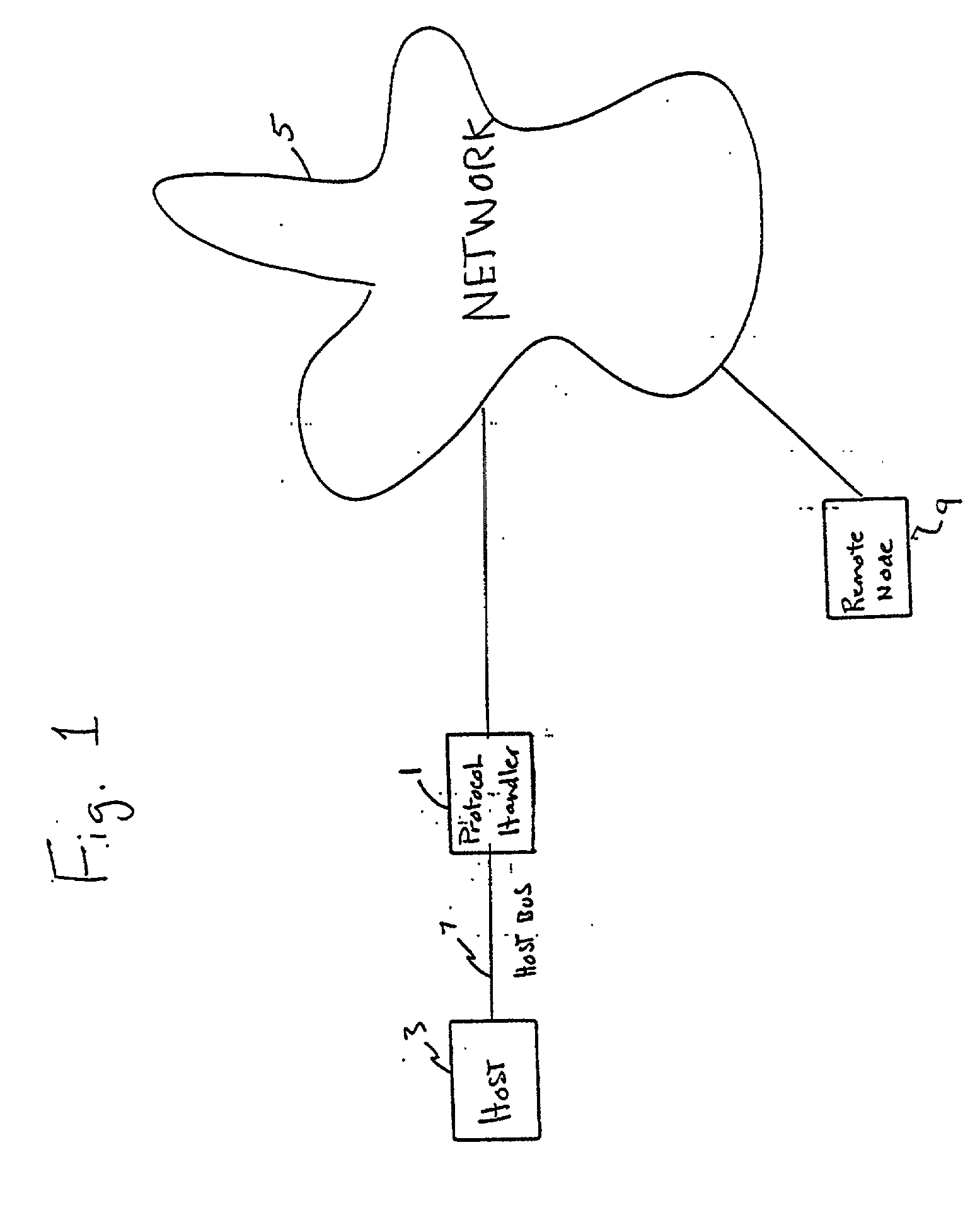

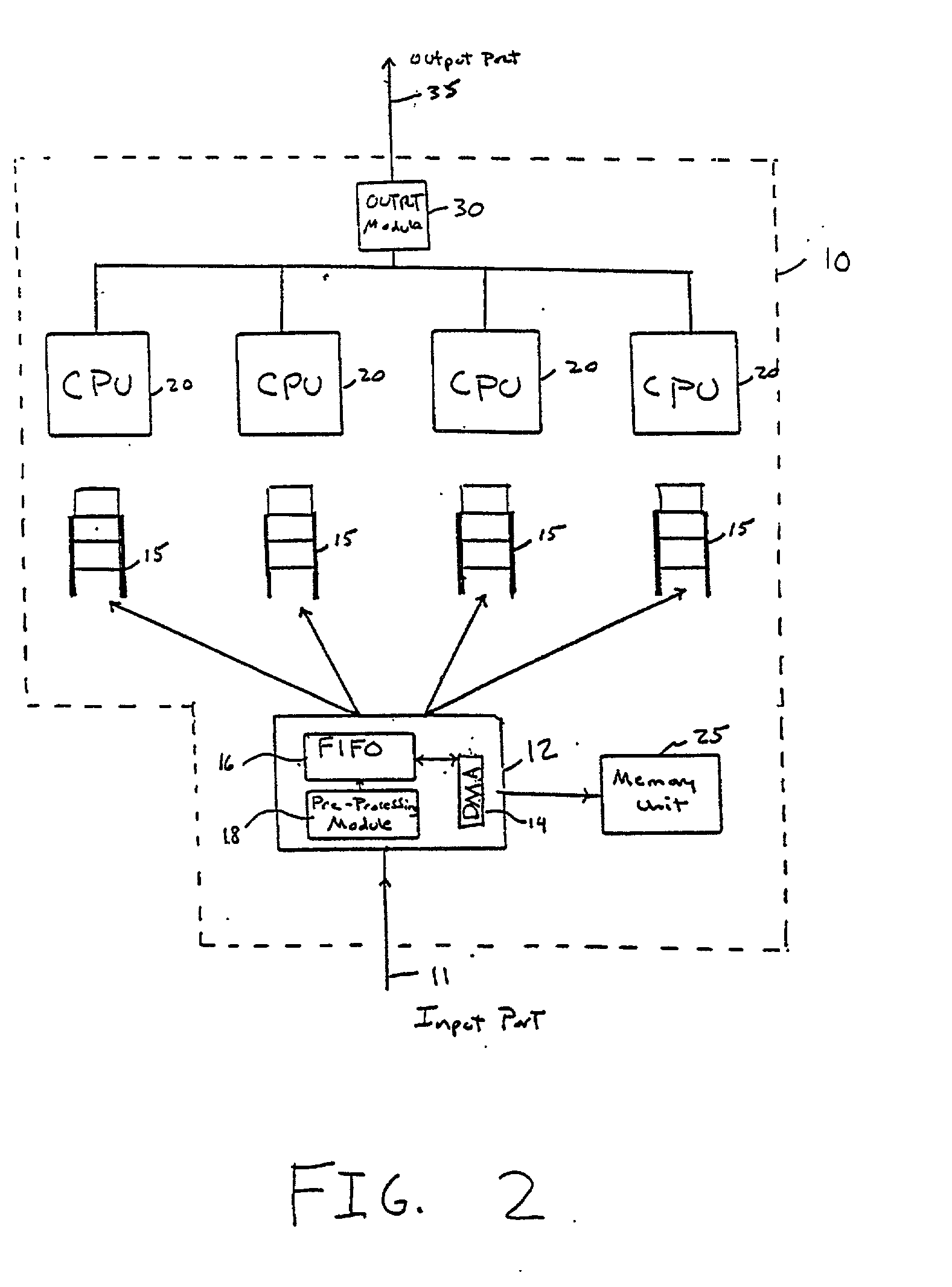

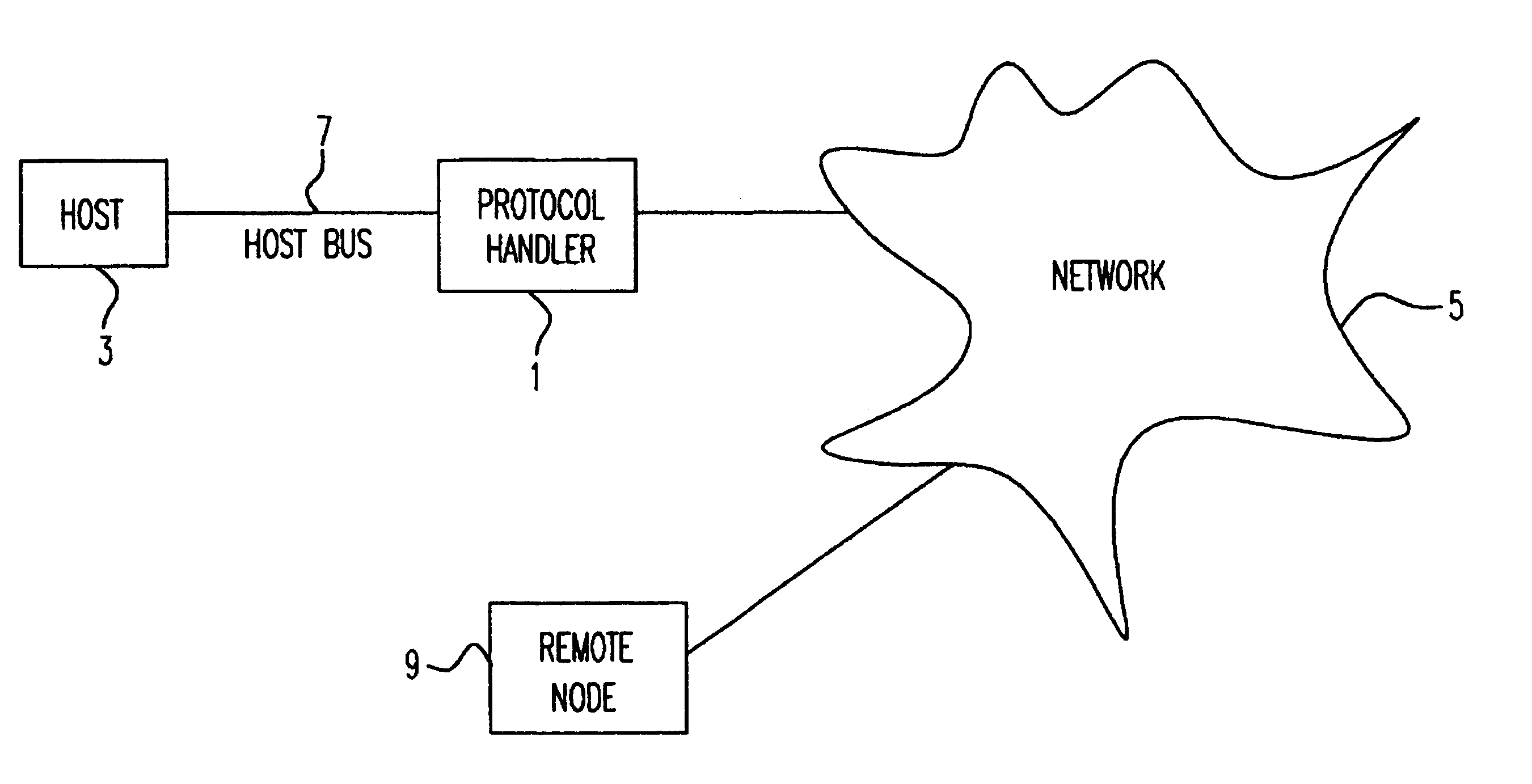

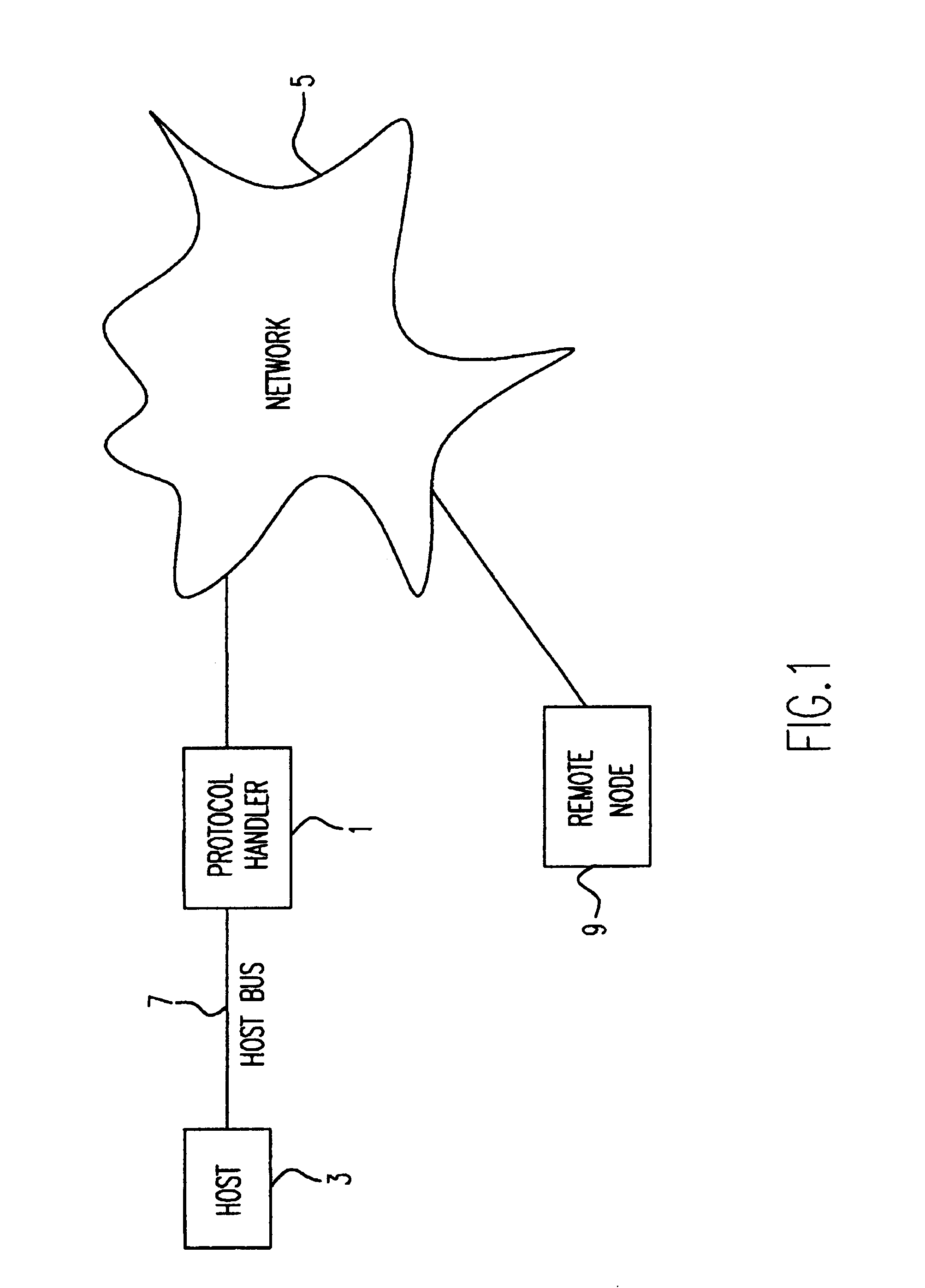

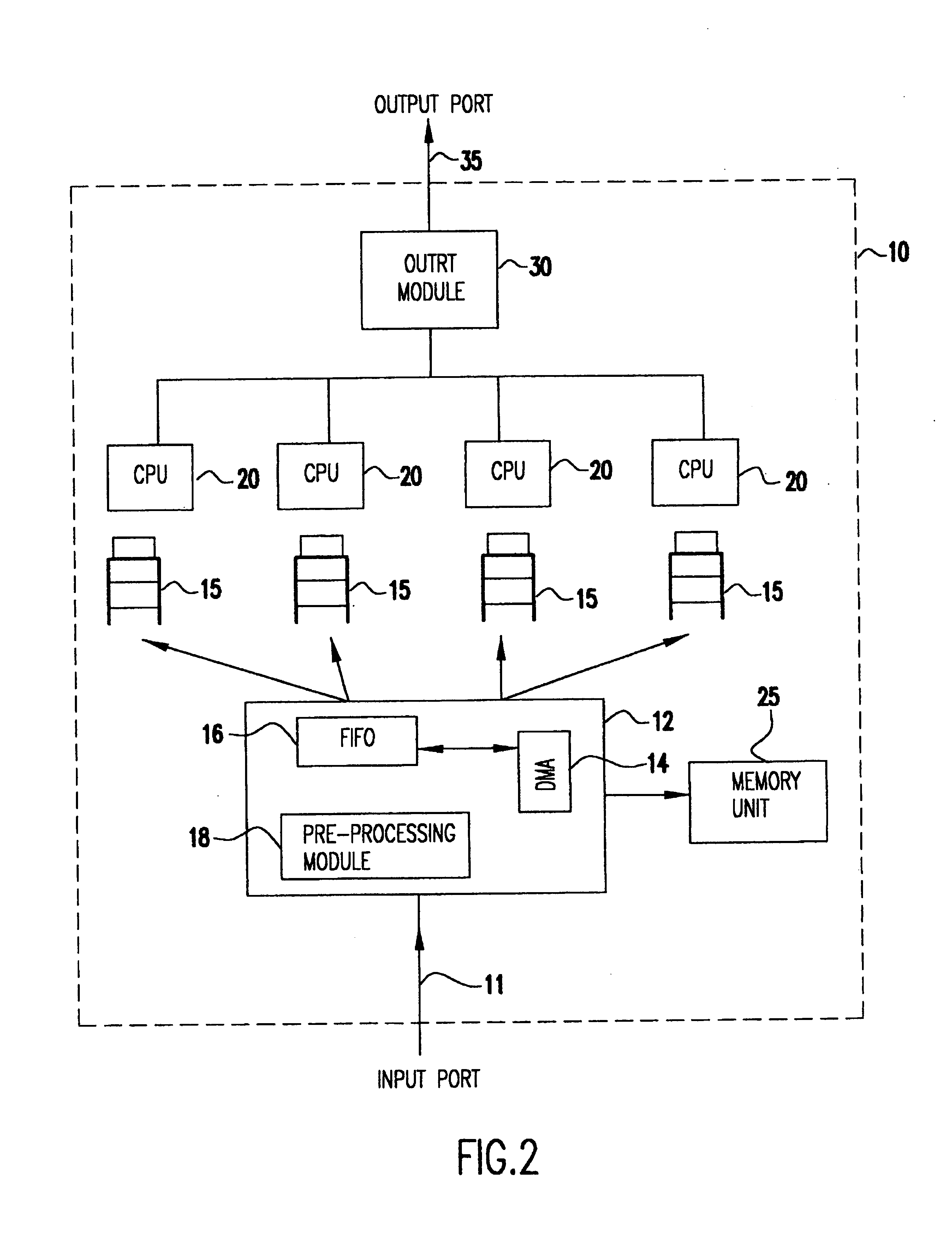

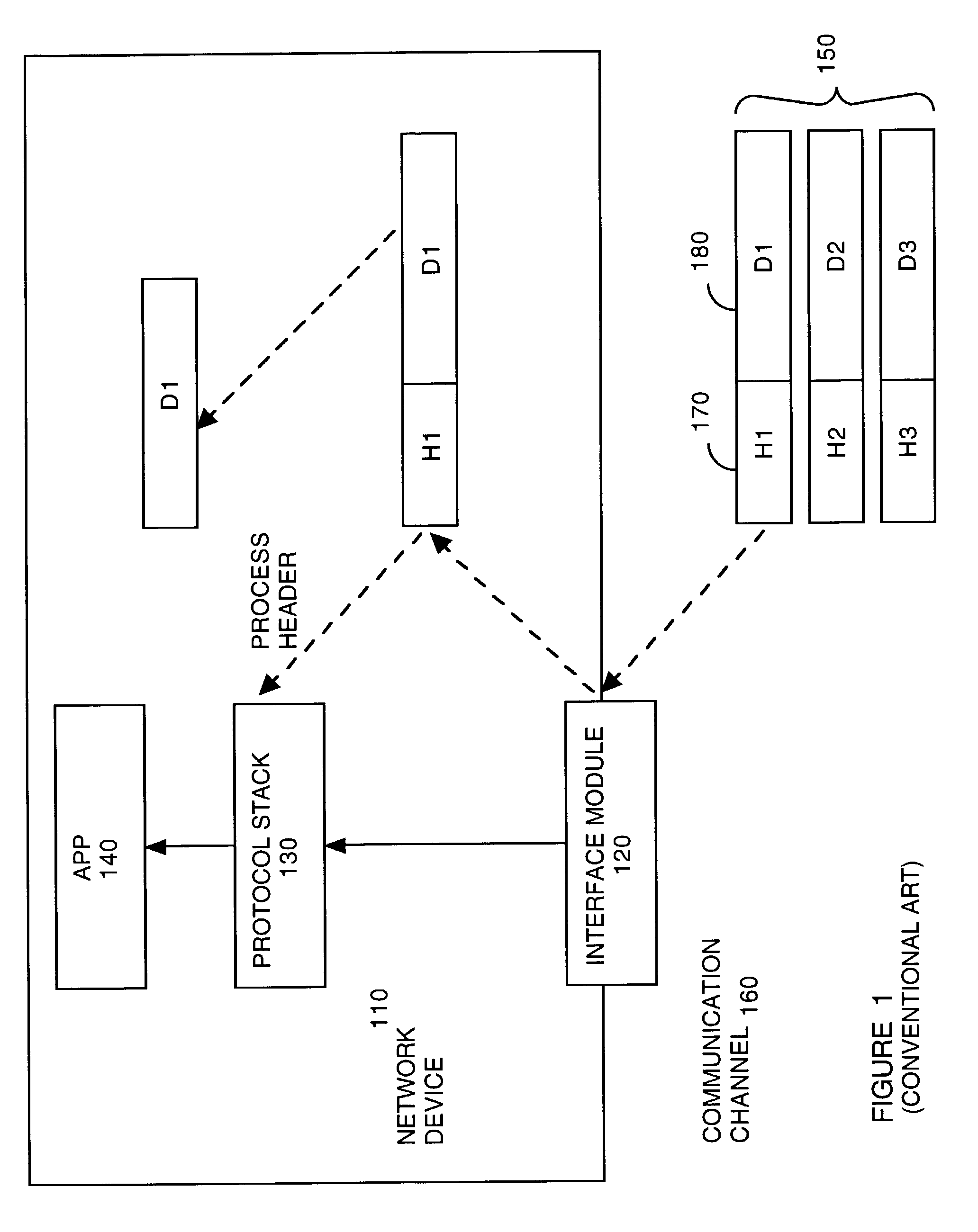

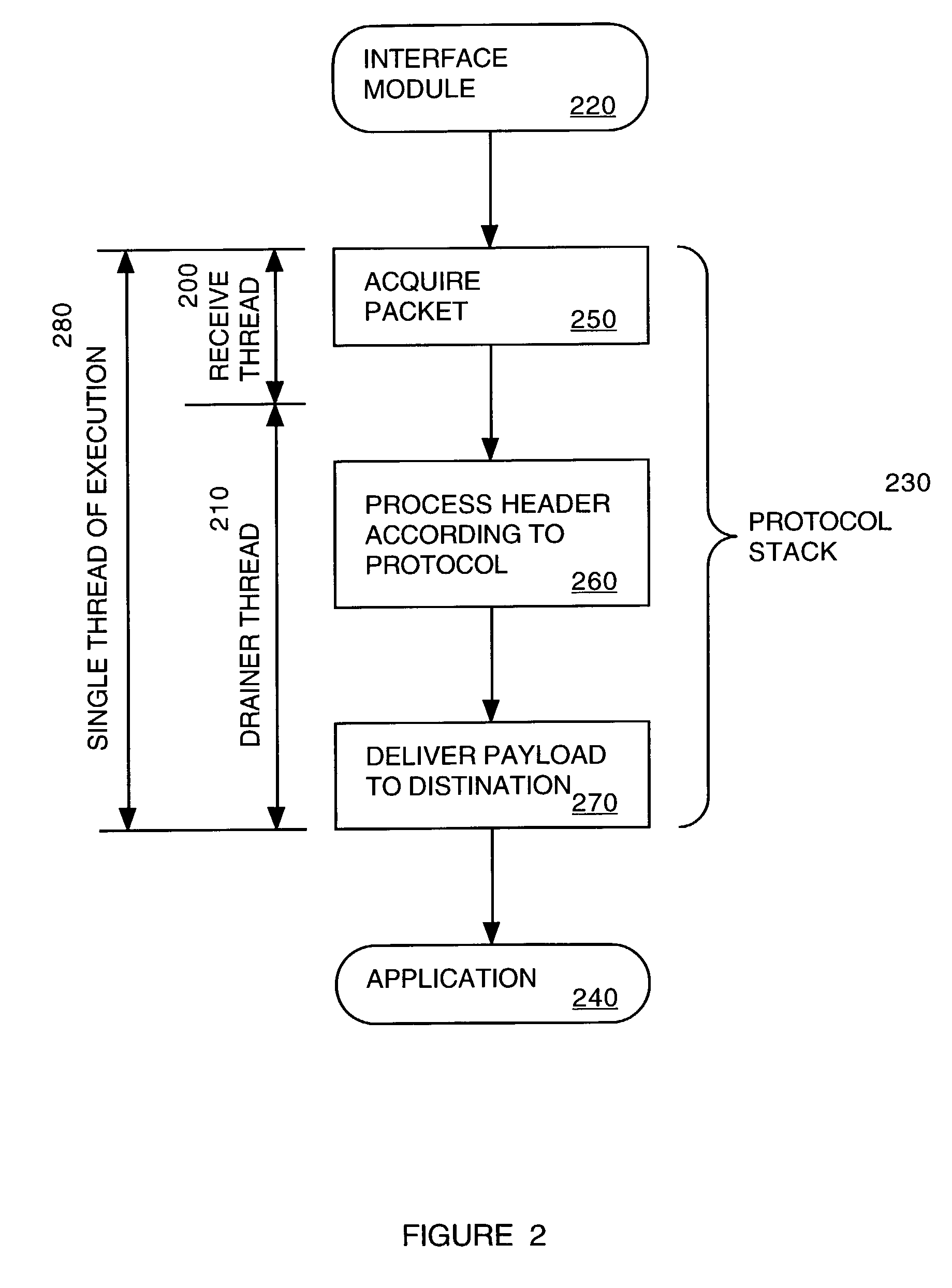

Packet preprocessing interface for multiprocessor network handler

InactiveUS20030067930A1Efficient developmentEvenly distributedData switching by path configurationStore-and-forward switching systemsTraffic capacityHash function

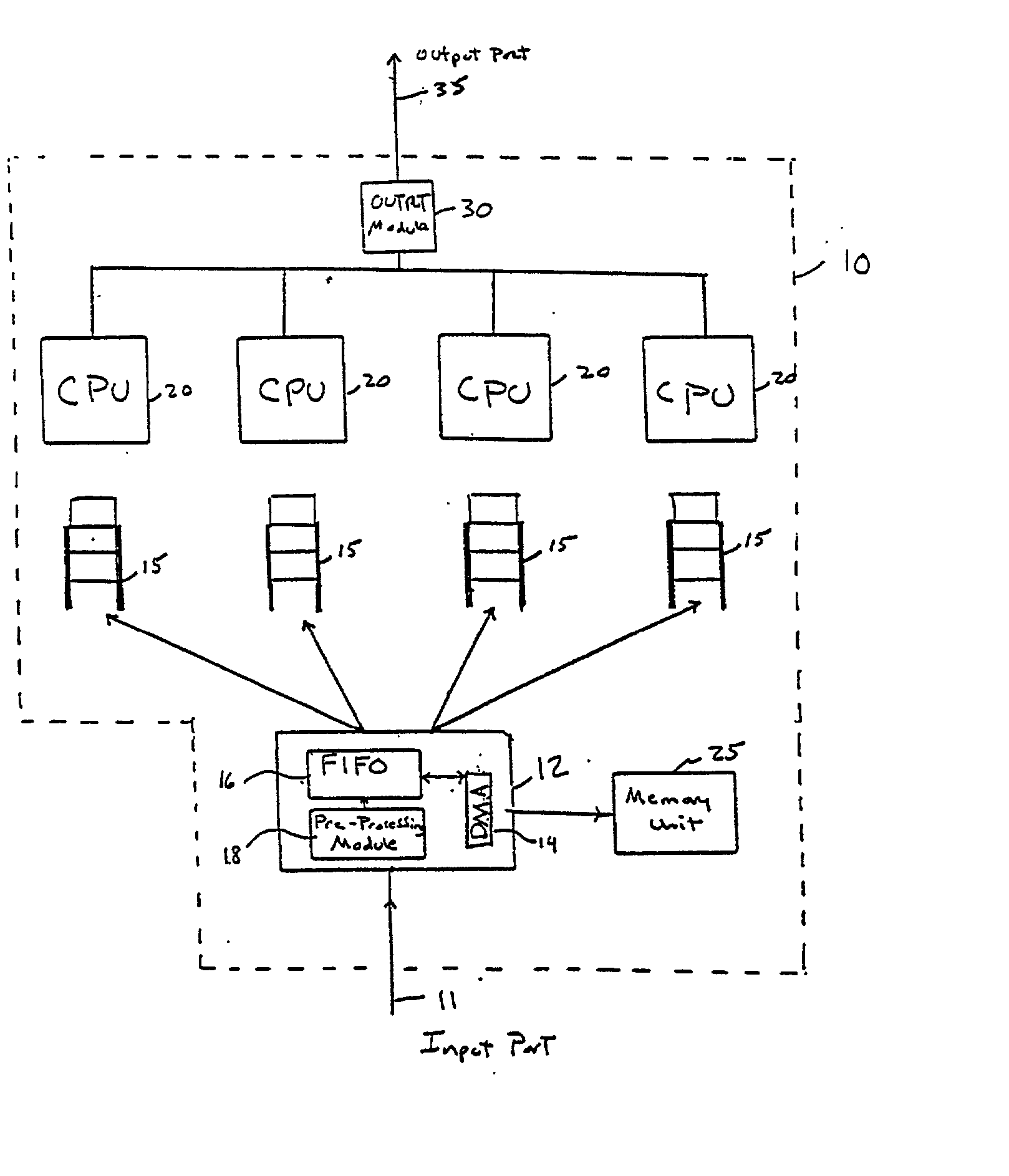

A network handler uses a DMA device to assign packets to network processors in accordance with a mapping function which classifies packets based on its content, e.g., bits in one or more header fields. Preferably, the mapping function is implemented as a hash function, which uses a predetermined number of bits from packet as inputs. The result of this function specifies the processor to which the packet is assigned. To make implementation manageable in a high-traffic environment, each processor may be equipped with a queue, which holds pointer information. Such a pointer provides an indication of the area in memory where incoming packet resides. The network handler is particularly useful in a Fibre Channel environment, where the hash function may be implemented to assign all packets from the same sequence to the same processor, thereby resulting in improved processing efficiency.

Owner:IBM CORP

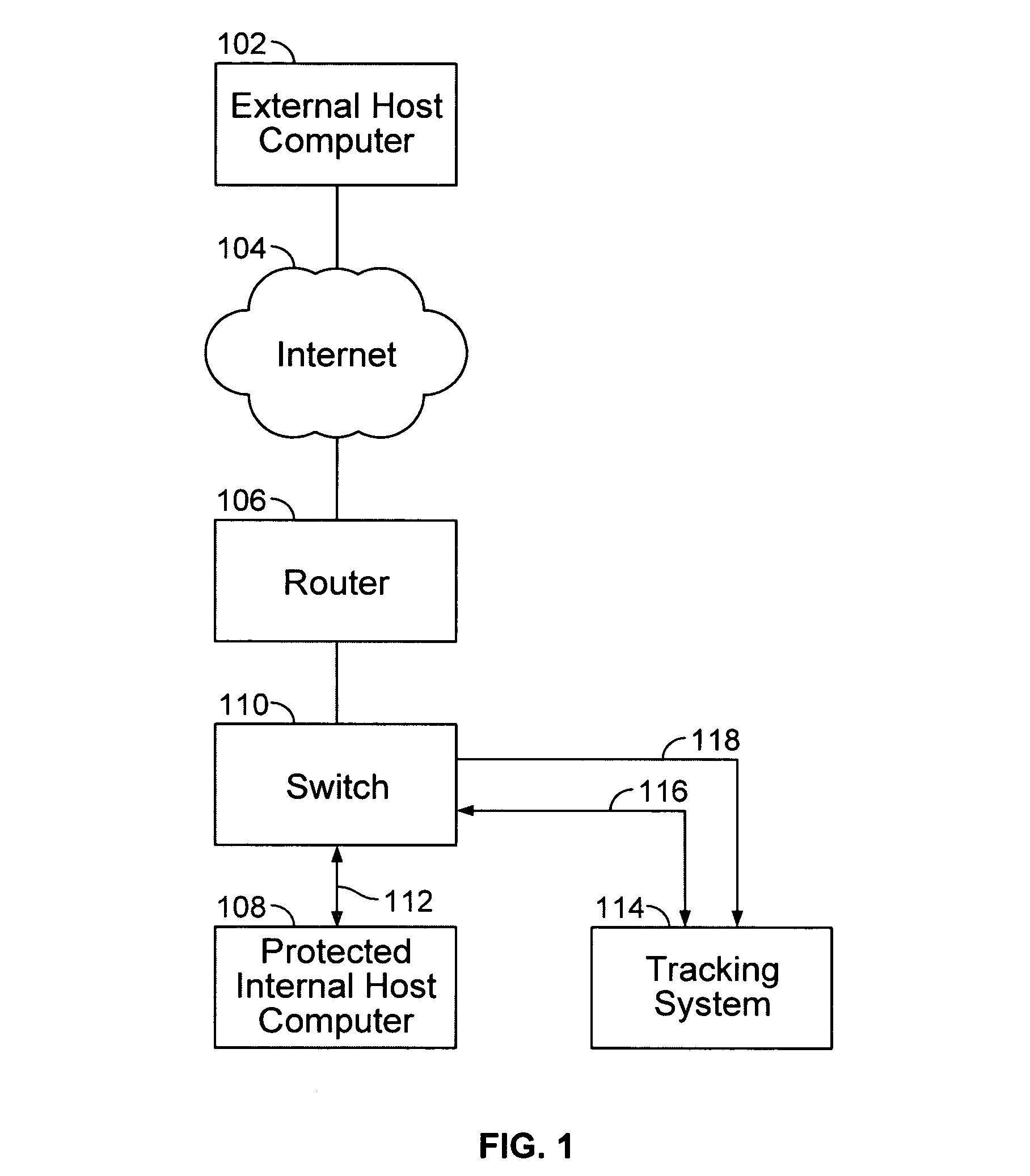

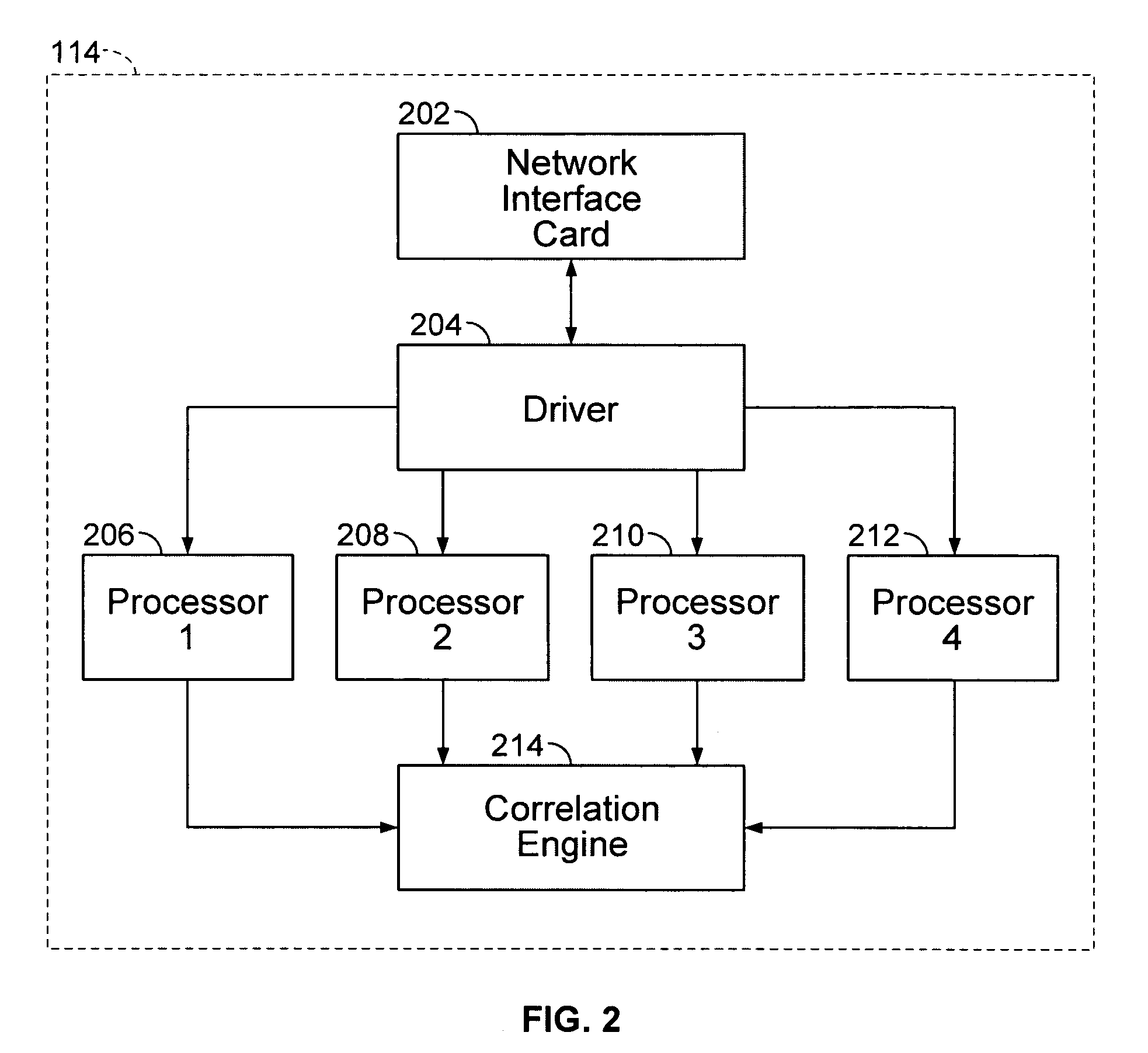

Routing network packets for multi-processor network flow analysis

InactiveUS7529242B1Memory loss protectionError detection/correctionTraffic capacityNetwork connection

A system and method are disclosed for routing data packets for network flow analysis by a multi-processor system. A data packet comprising data sufficient to identify a network connection with which the data packet is associated is received. A hash value is calculated based on the data sufficient to identify the network connection with which the data packet is associated. The data packet is assigned, based on the hash value, to one of the plurality of processors for analysis.

Owner:CA TECH INC

Packet preprocessing interface for multiprocessor network handler

InactiveUS6904040B2Efficient networkingEfficient processingData switching by path configurationMultiple digital computer combinationsTraffic capacityHash function

A network handler uses a DMA device to assign packets to network processors in accordance with a mapping function which classifies packets based on its content, e.g., bits in one or more header fields. Preferably, the mapping function is implemented as a hash function, which uses a predetermined number of bits from packet as inputs. The result of this function specifies the processor to which the packet is assigned. To make implementation manageable in a high-traffic environment, each processor may be equipped with a queue, which holds pointer information. Such a pointer provides an indication of the area in memory where incoming packet resides. The network handler is particularly useful in a Fiber Channel environment, where the hash function may be implemented to assign all packets from the same sequence to the same processor, thereby resulting in improved processing efficiency.

Owner:IBM CORP

Virtual Supercomputer

ActiveUS20110004566A1Improve efficiencyFinanceResource allocationInformation processingOperational system

The virtual supercomputer is an apparatus, system and method for generating information processing solutions to complex and / or high-demand / high-performance computing problems, without the need for costly, dedicated hardware supercomputers, and in a manner far more efficient than simple grid or multiprocessor network approaches. The virtual supercomputer consists of a reconfigurable virtual hardware processor, an associated operating system, and a set of operations and procedures that allow the architecture of the system to be easily tailored and adapted to specific problems or classes of problems in a way that such tailored solutions will perform on a variety of hardware architectures, while retaining the benefits of a tailored solution that is designed to exploit the specific and often changing information processing features and demands of the problem at hand.

Owner:VERISCAPE

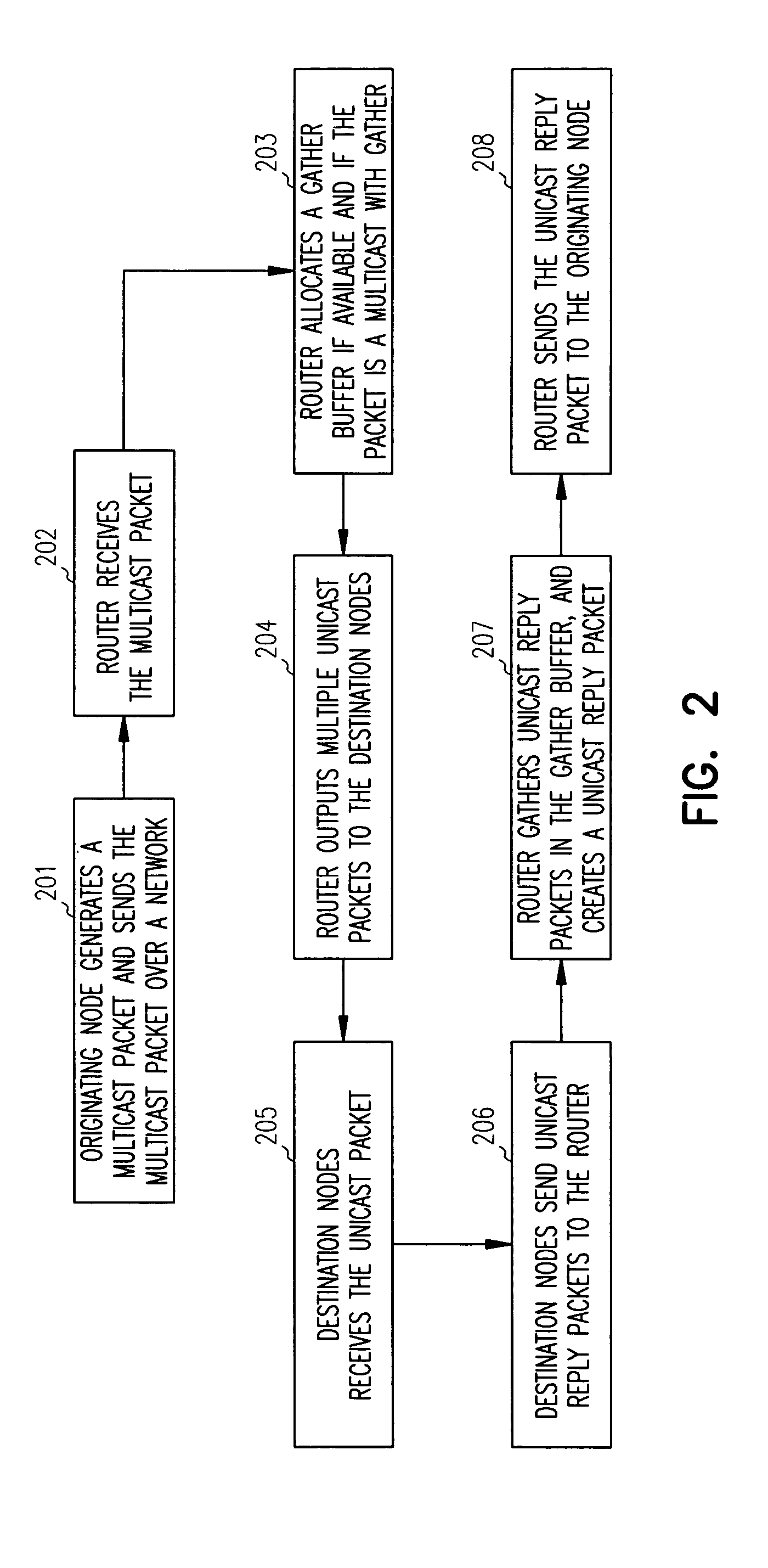

Multiprocessor network multicasting and gathering

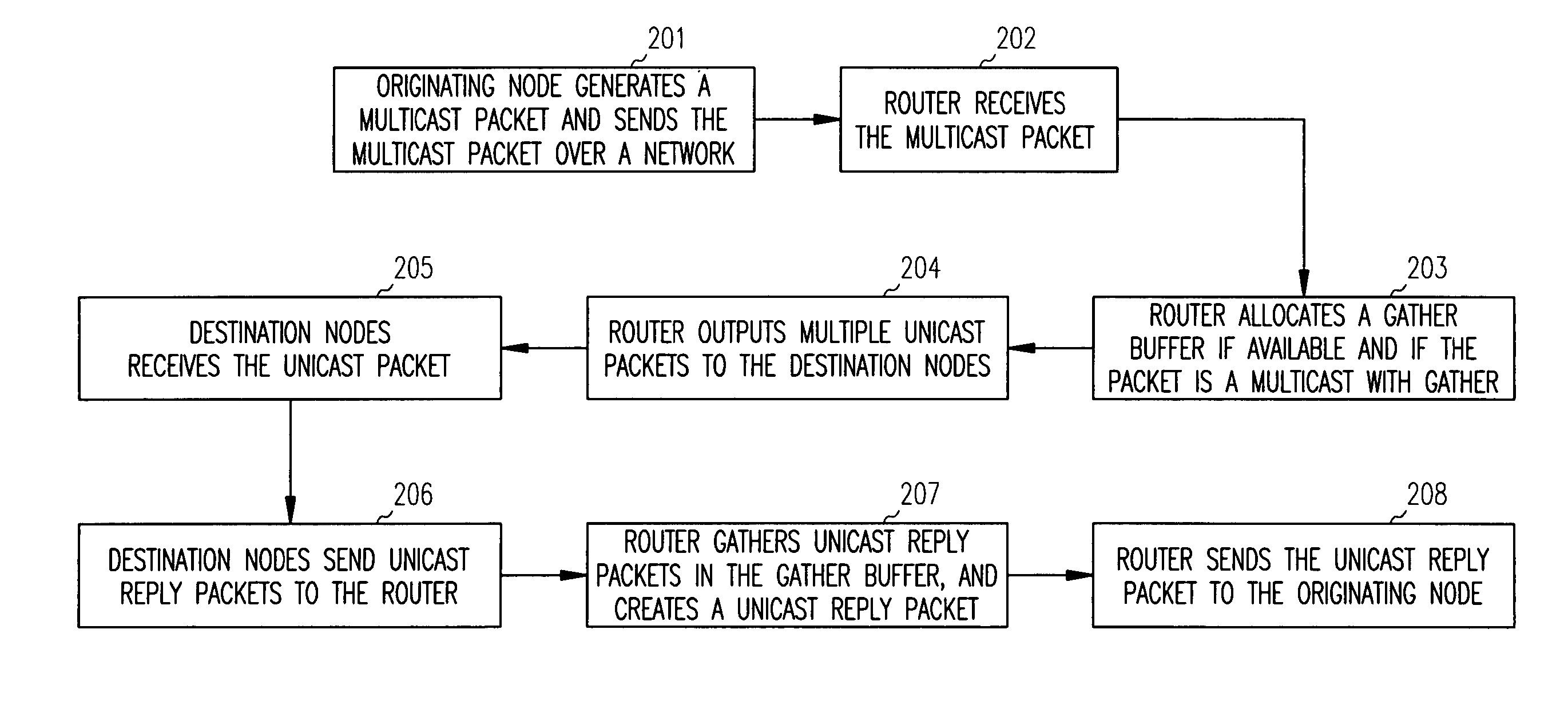

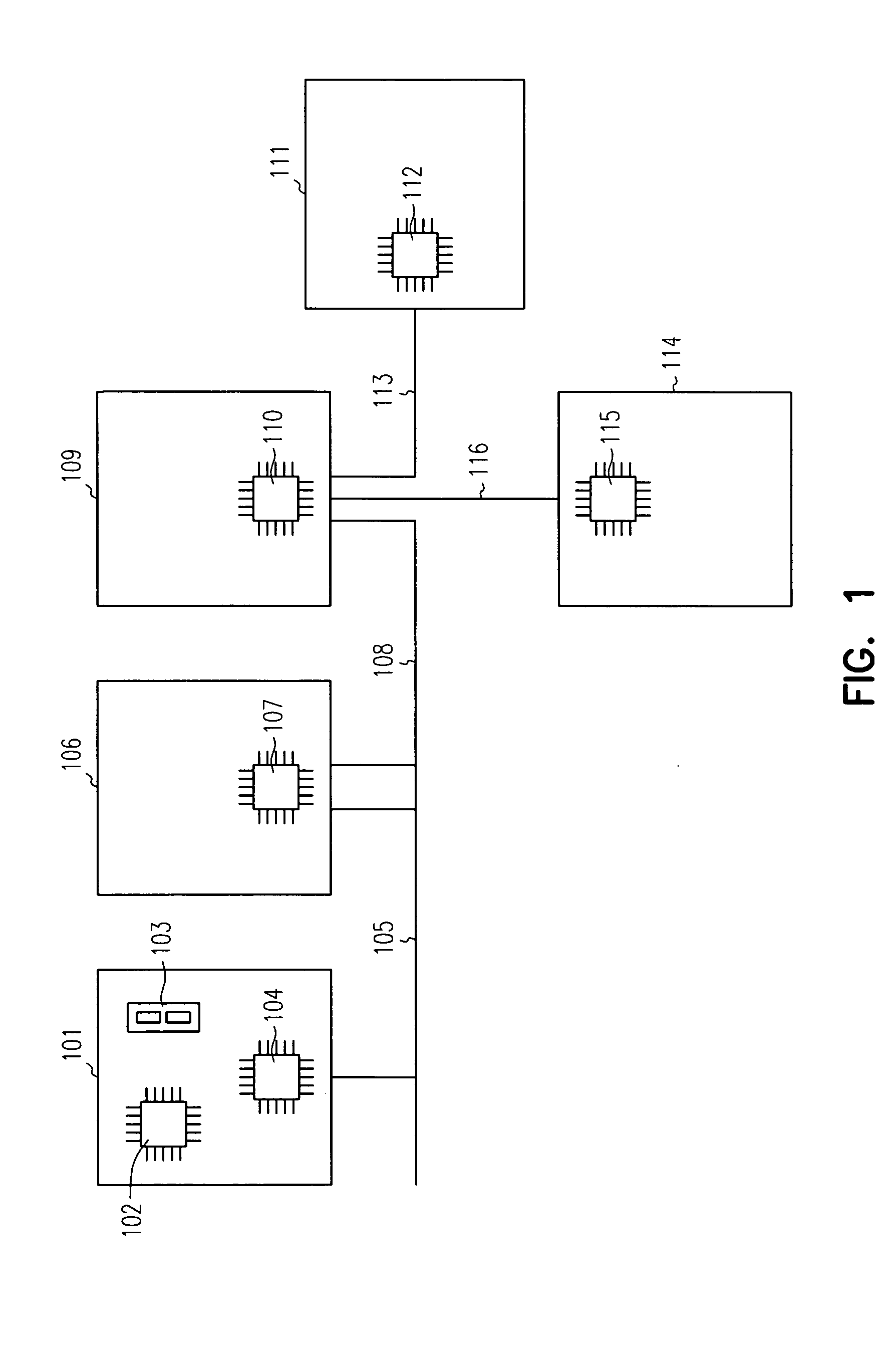

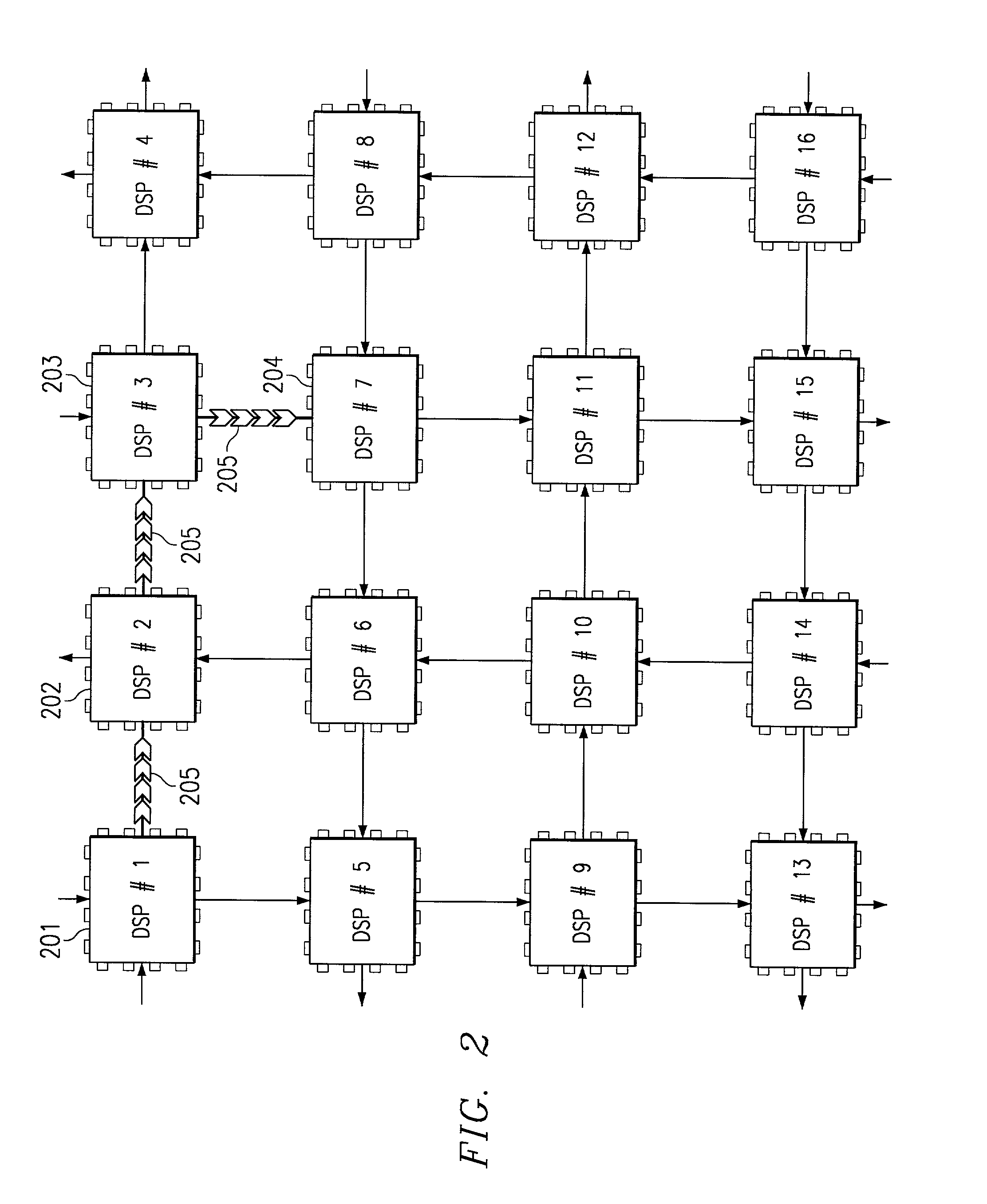

InactiveUS20050010687A1Special service provision for substationMultiple digital computer combinationsMulticast packetsMultiprocessor network

A parallel processor computer interconnect router comprises a multicasting module and a gathering module. The multicasting module is operable to receive a single incoming multicast packet comprising a destination identifier identifying a plurality of destination nodes, and to output multiple unicast packets, each of the multiple unicast packets comprising a destination header identifying a single destination node from among the plurality of destination nodes. The gathering module is operable to receive unicast reply packets from the plurality of destination nodes, and to output a combined multicast reply packet.

Owner:MORGAN STANLEY +1

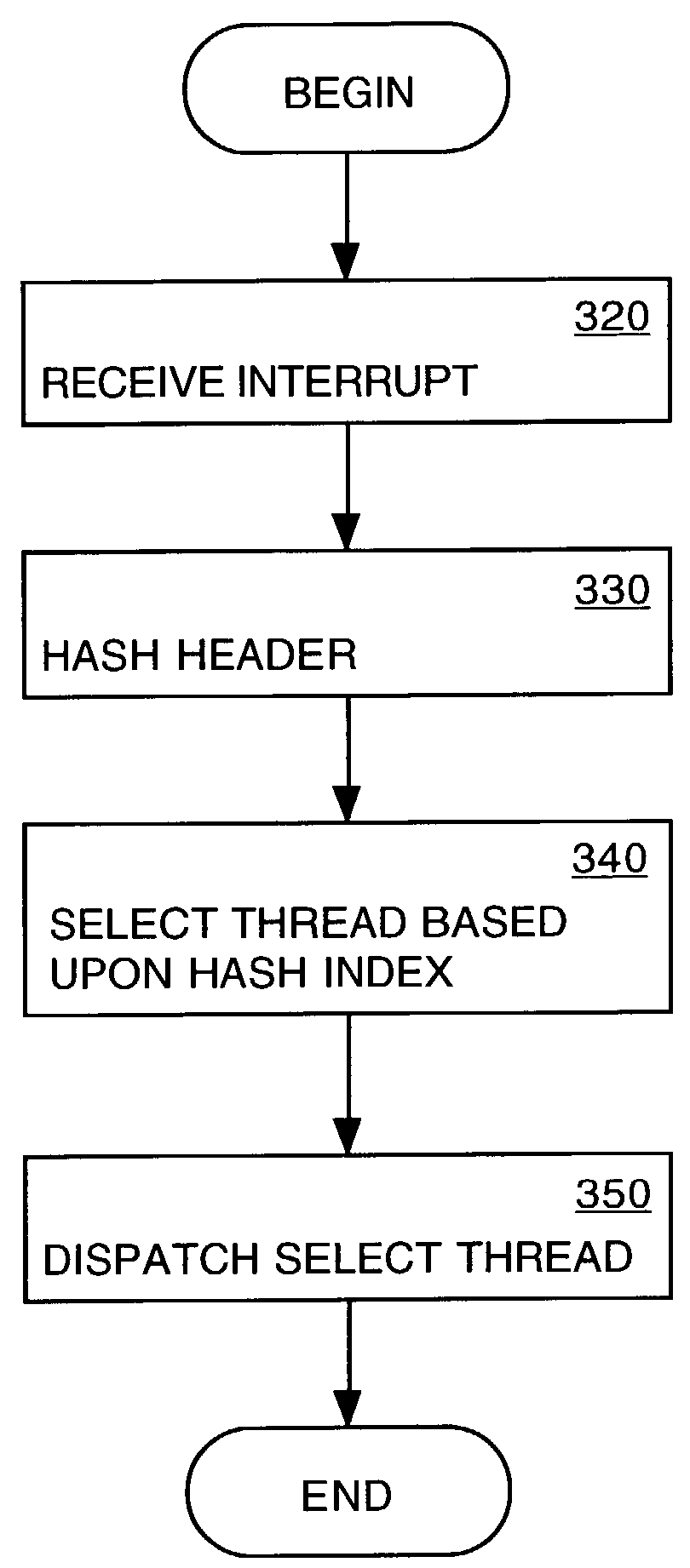

Dynamic allocation of a pool of threads

ActiveUS7257633B2Improve data localityEfficient comprehensive utilizationProgram initiation/switchingResource allocationMulti processorHash table

Embodiments of the present invention provide for execution of a protocol in a multi-processor network device. In one embodiment, a hash function is applied to one or more fields of the data packet header to determine a unique index. A hash table is then queried, whereby data indicating one or more threads corresponding to said unique index is extracted. An available thread of execution, which has previously handled packet in the same receive stream, may thus be selected from a pool of threads. The selected thread of execution is then dispatched to provide for receive processing of the present data packet.

Owner:ORACLE INT CORP

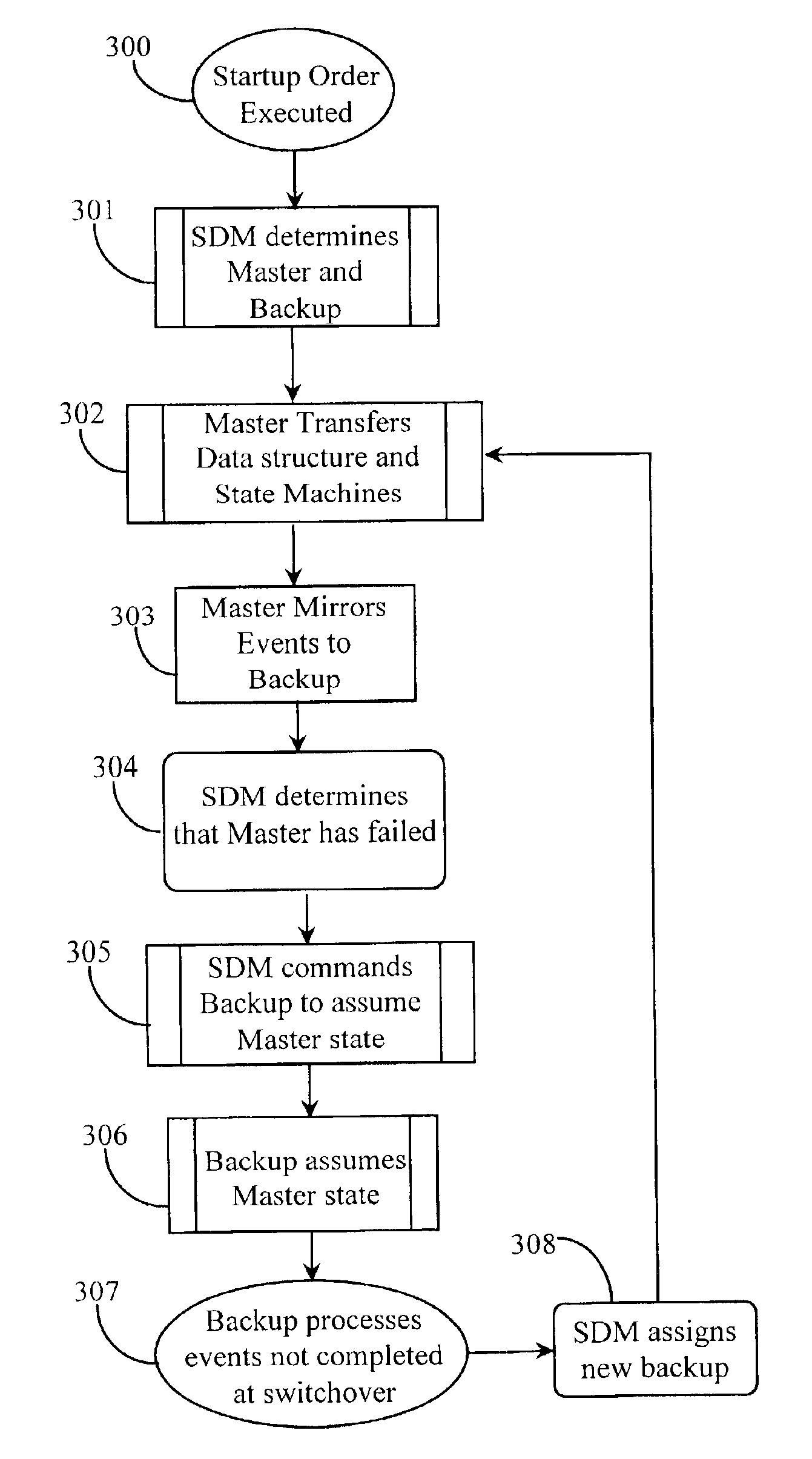

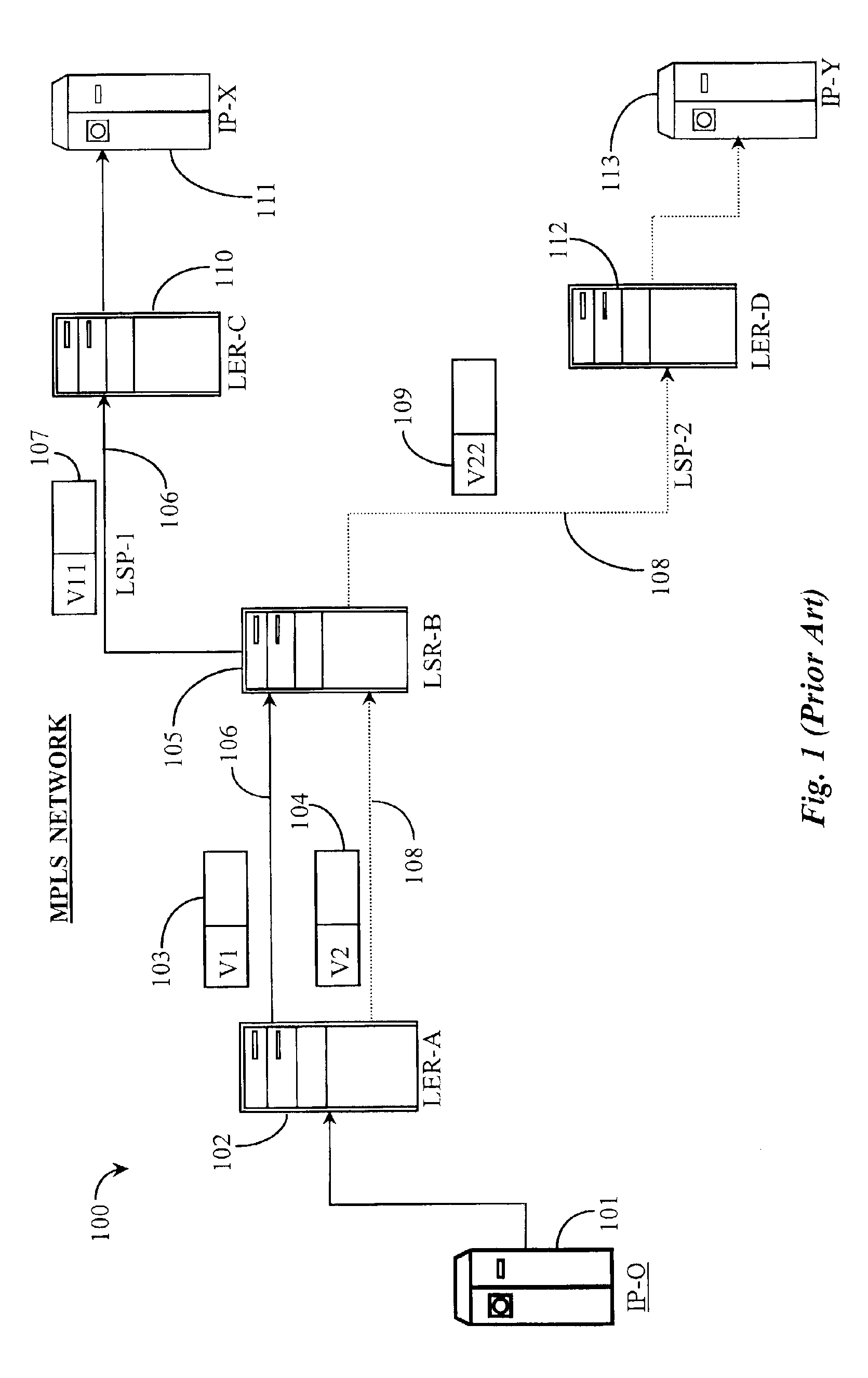

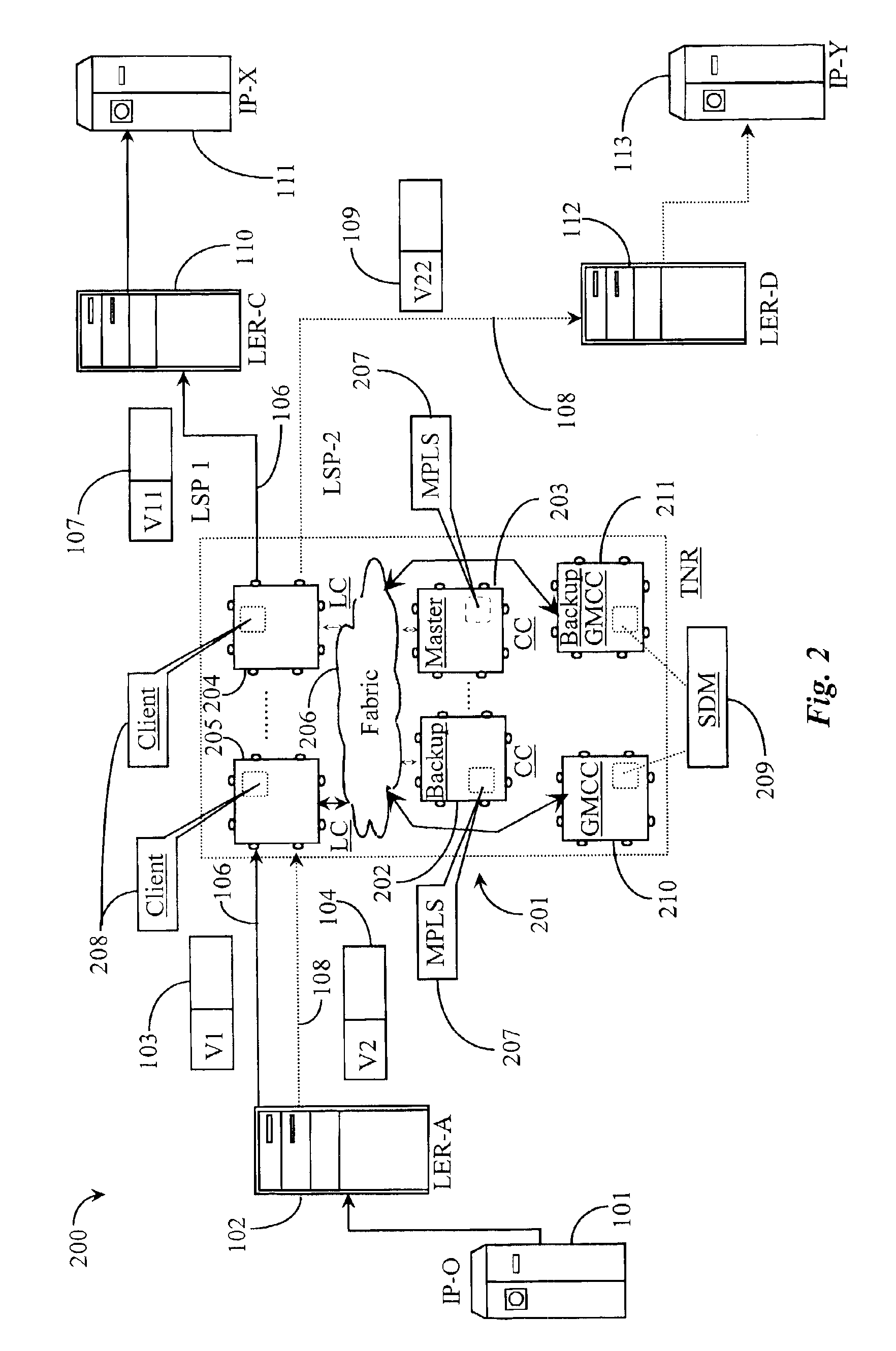

Fault-protection mechanism for protecting multi-protocol-label switching (MPLS) capability within a distributed processor router operating in an MPLS network

ActiveUS6915445B2Error detection/correctionNetworks interconnectionFault toleranceProtection mechanism

A method for providing fault-tolerance for Multi-Path Label Switching (MPLS) functionality in a multi-processor network routing node has the steps of (a) implementing an MPLS server application including state information, on a first and a second processor in the node; (b) designating the MPLS server on the first processor as a master server and the MPLS server on the second processor as a backup server, and providing MPLS functionality in the node with the master MPLS server; (c) directing all required MPLS events to both the master and the backup MPLS servers during operation; (d) monitoring operation of the master server; and (e) in the event of failure of the master server, designating the backup server as the master, allowing MPLS functions to continue on the routing node.

Owner:PLURIS

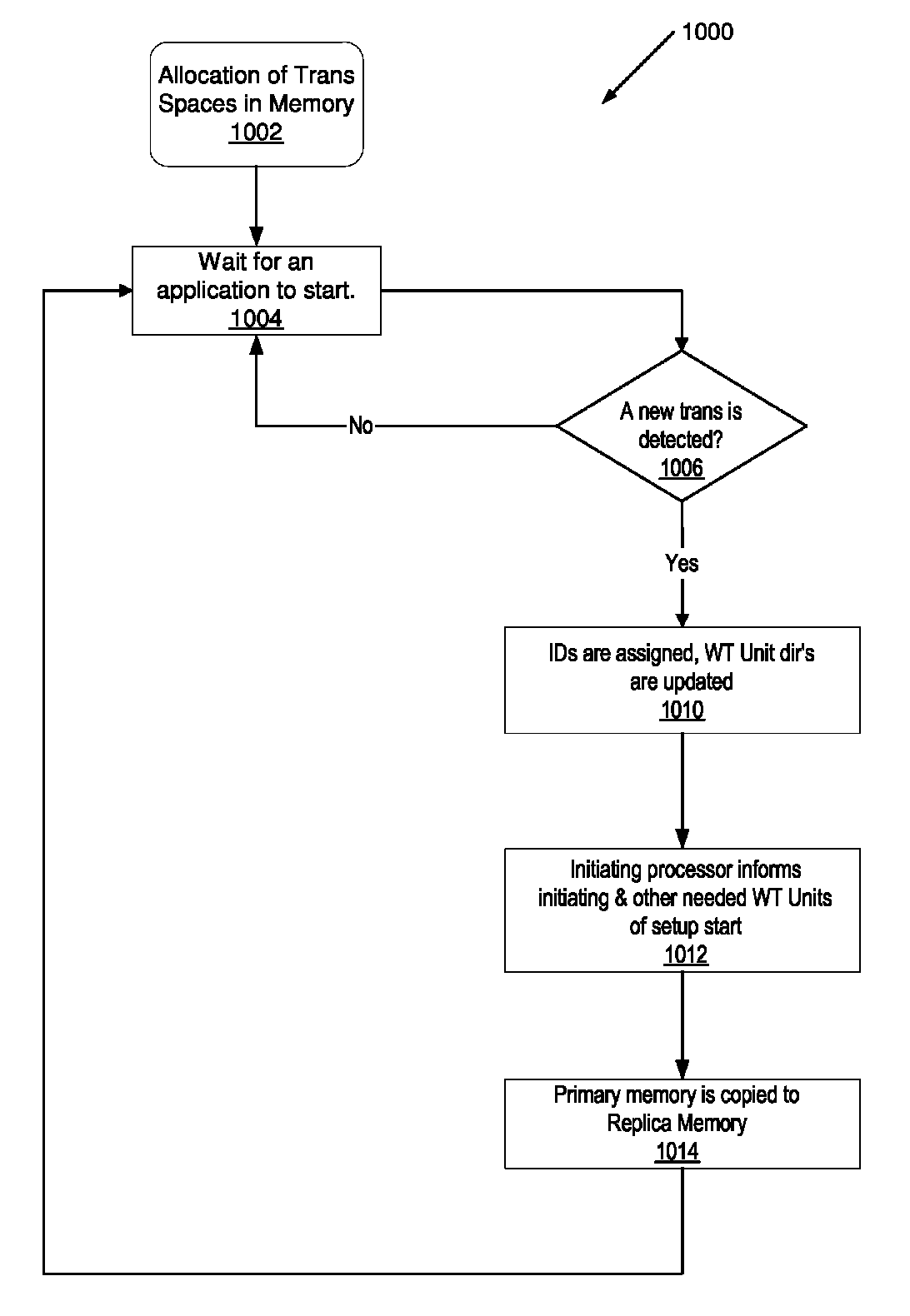

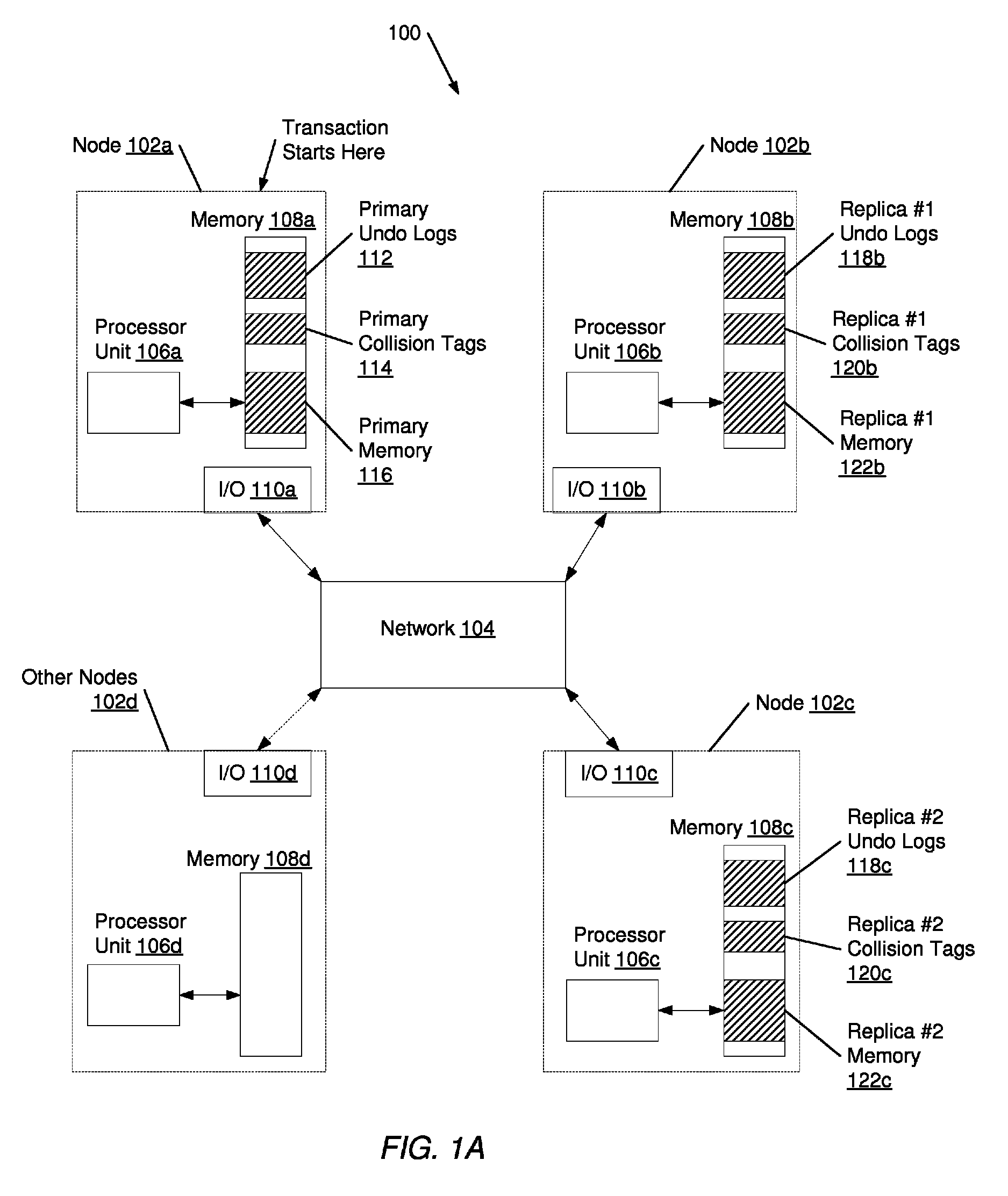

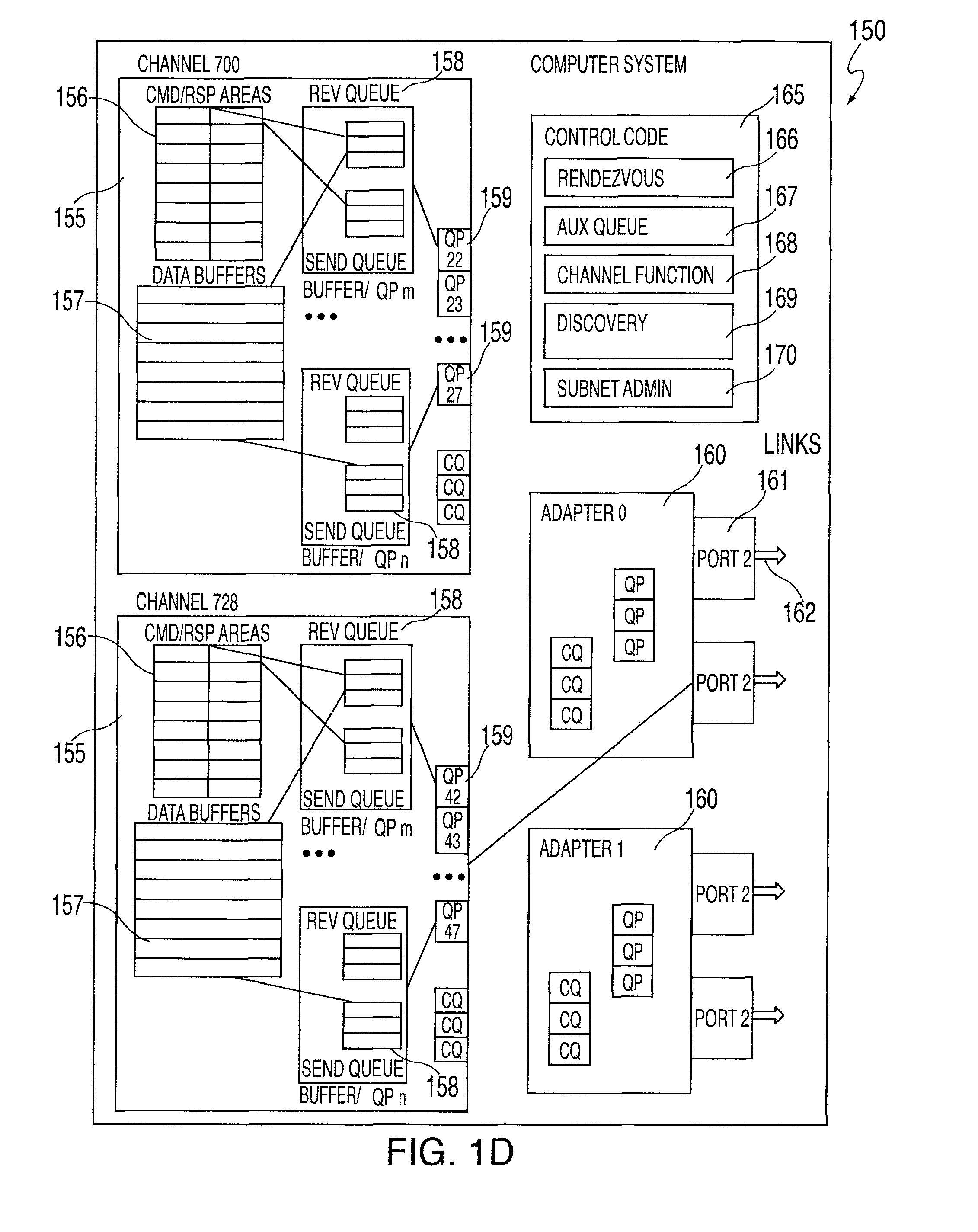

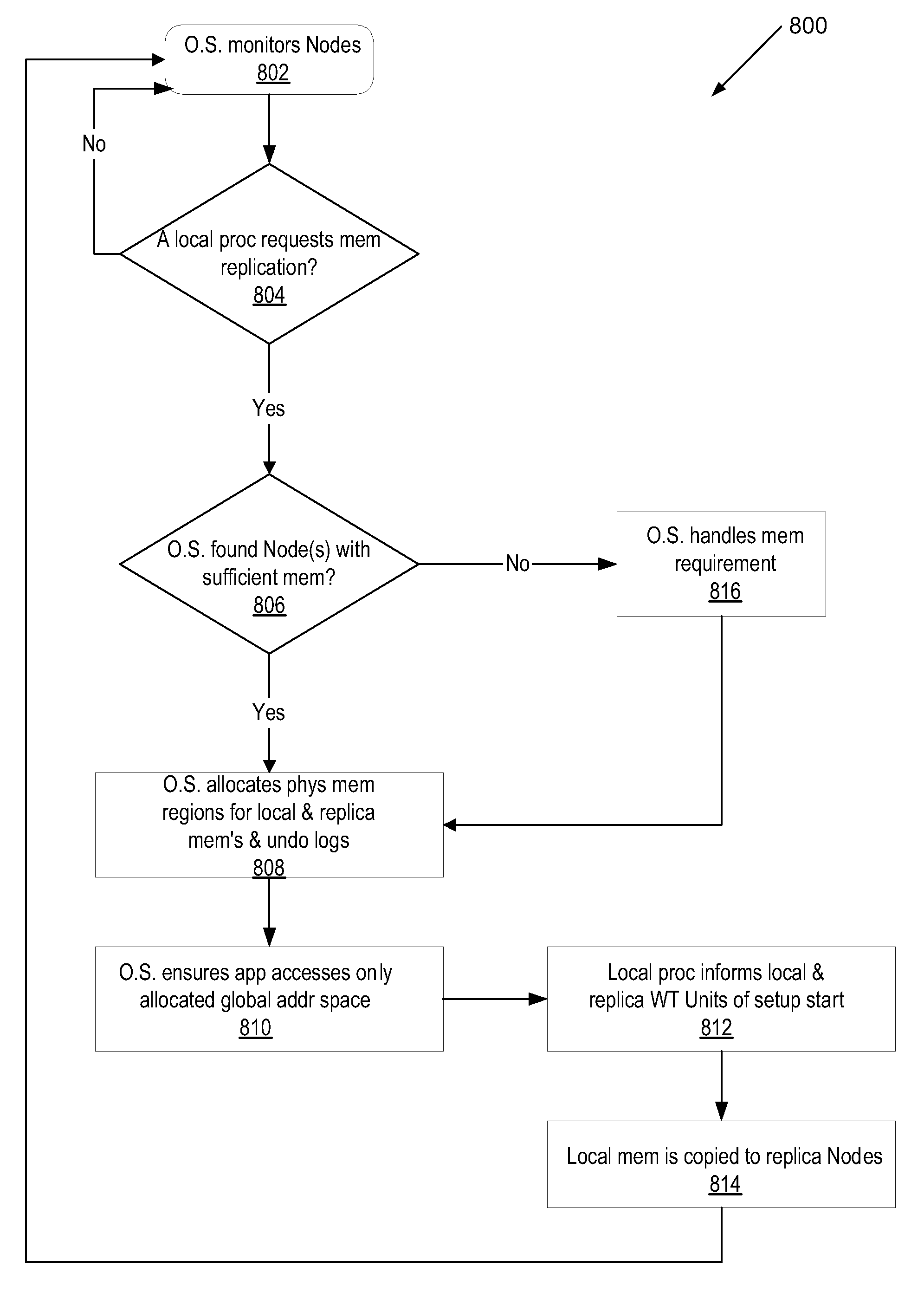

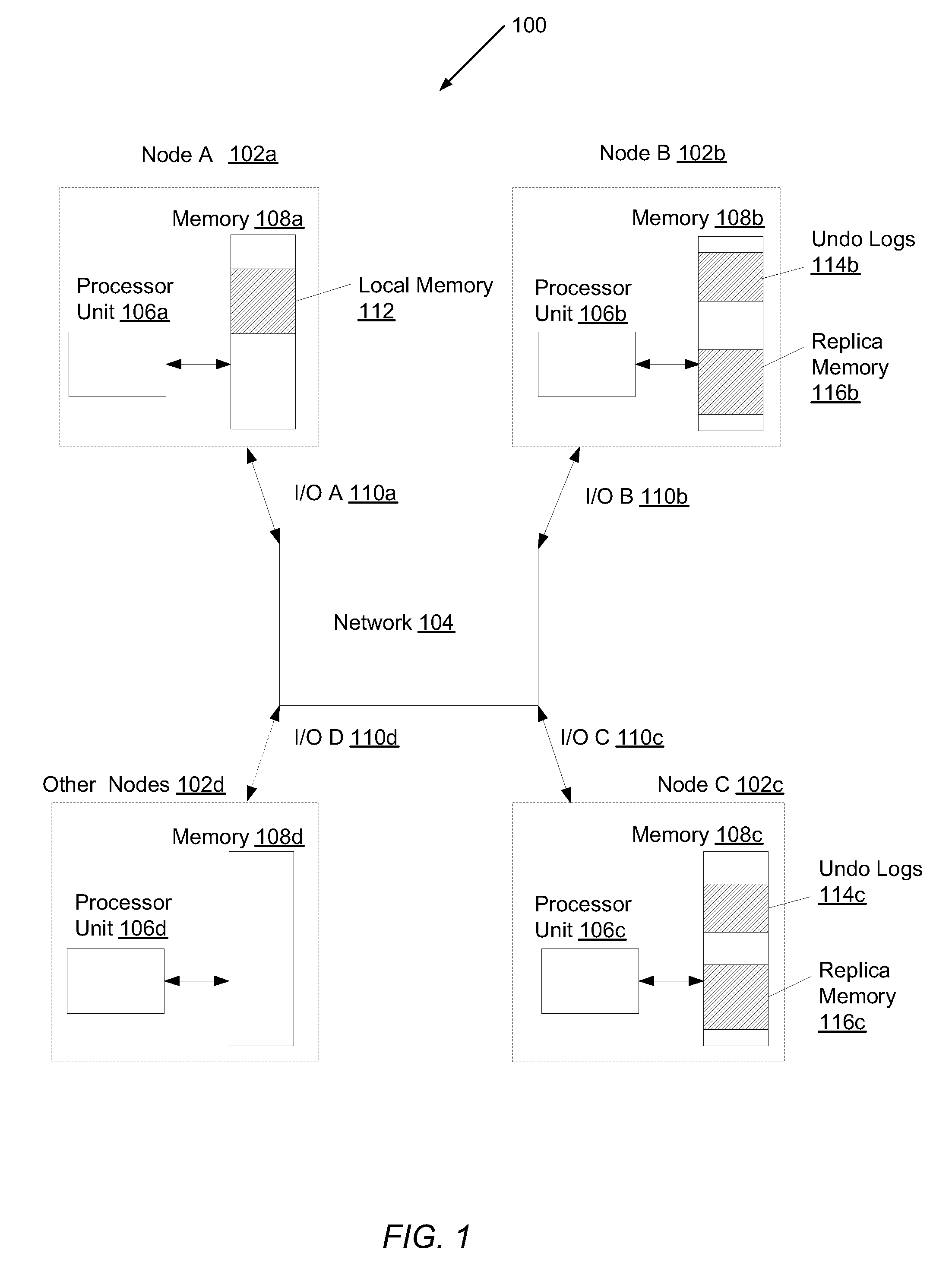

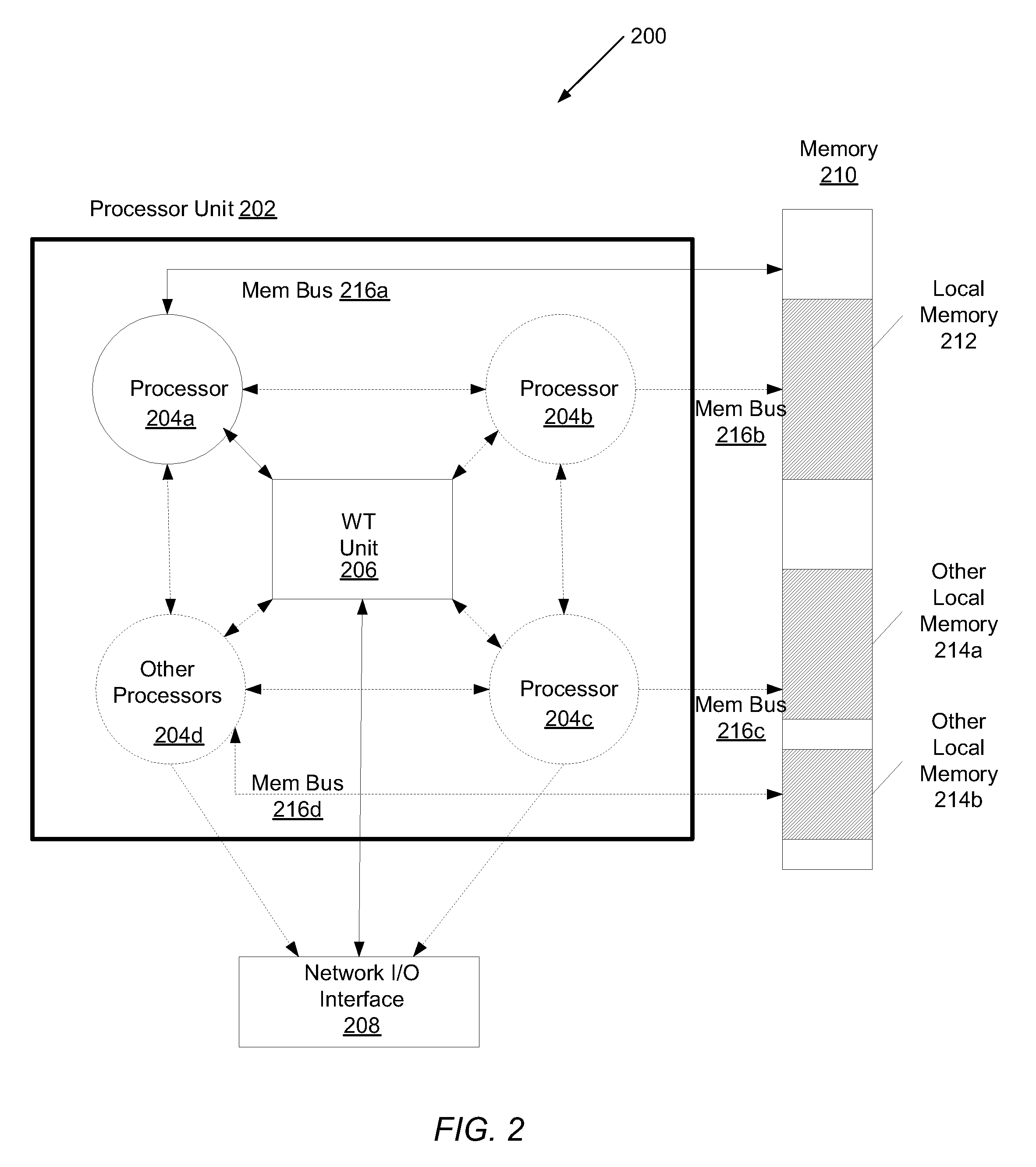

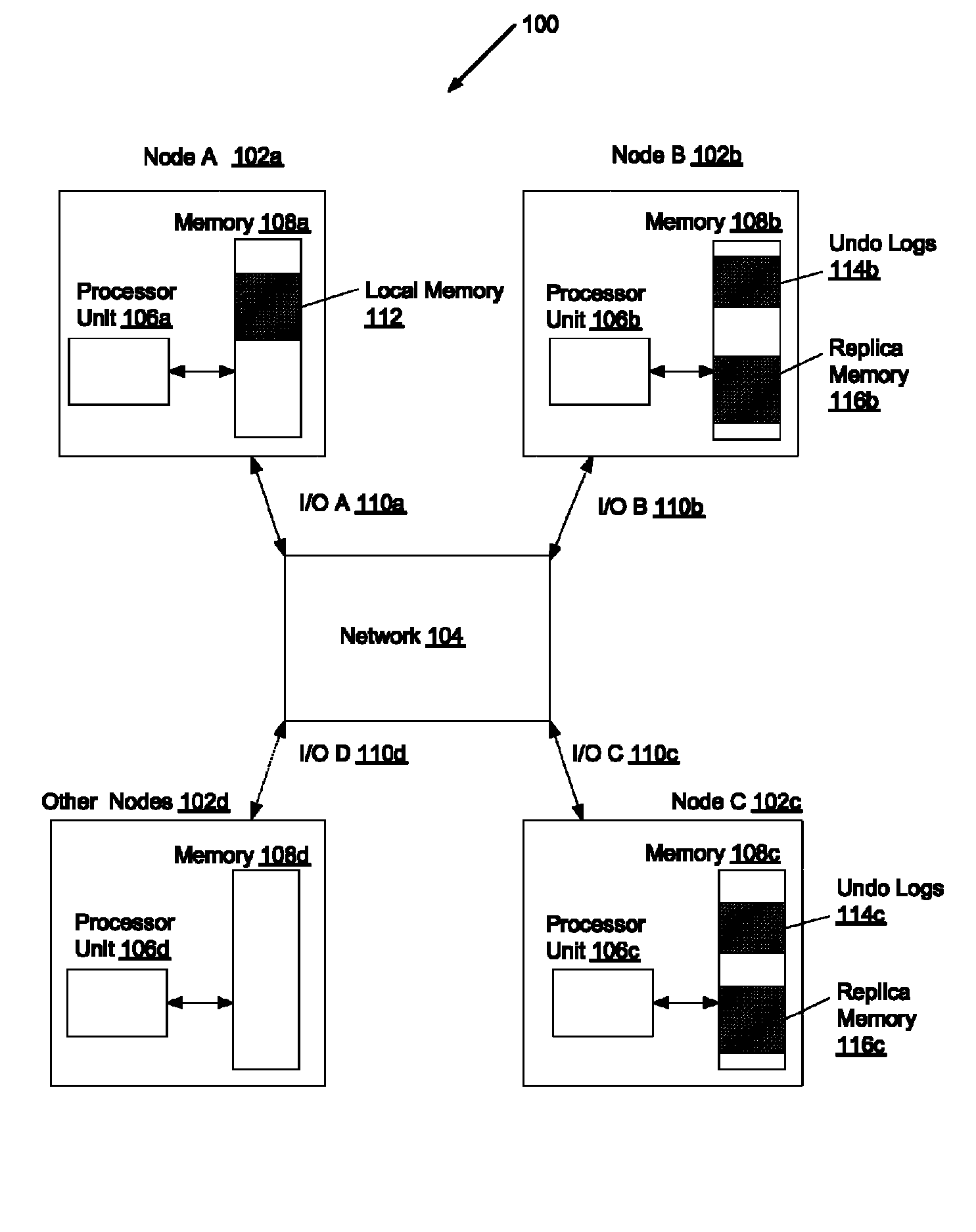

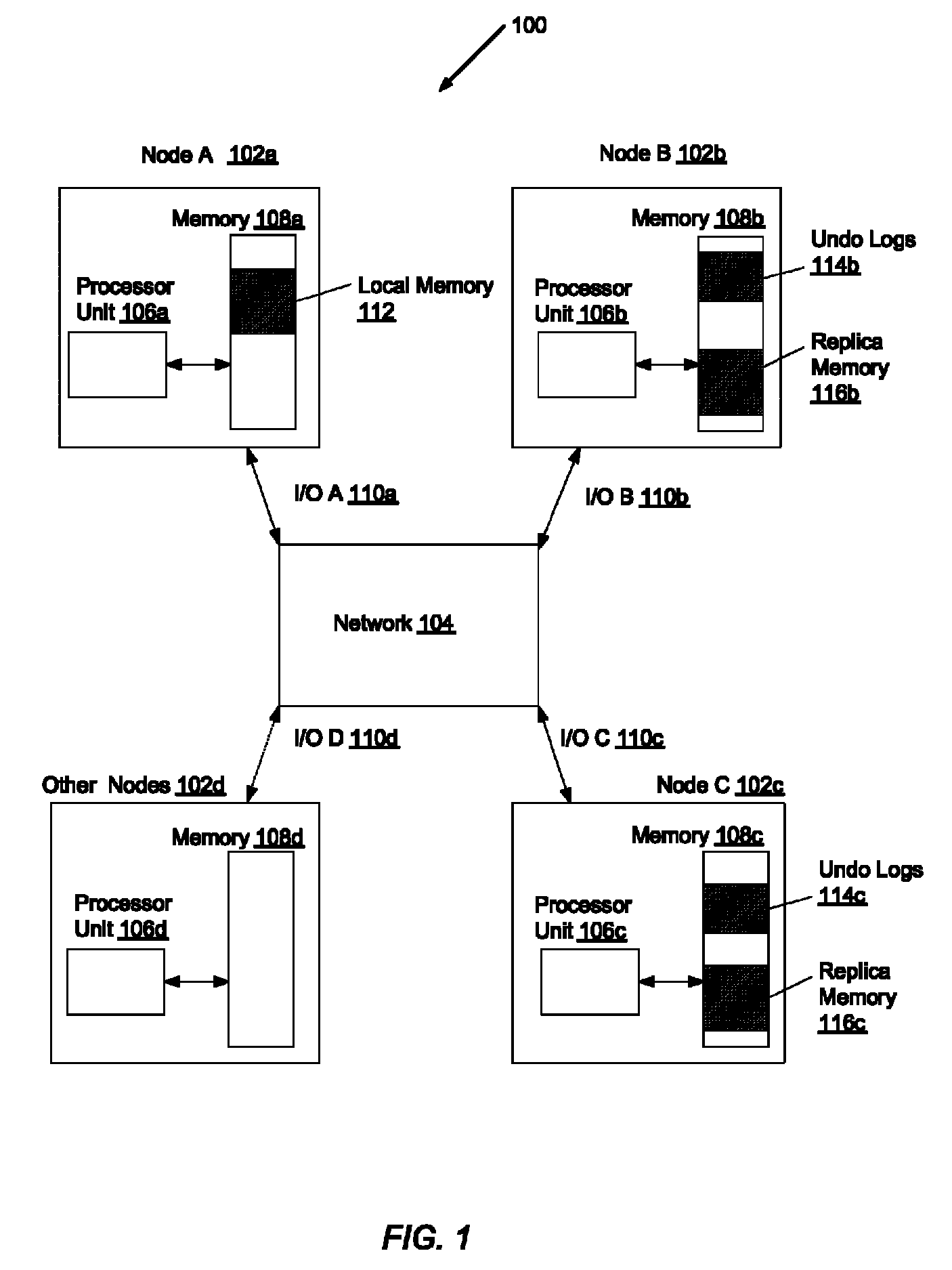

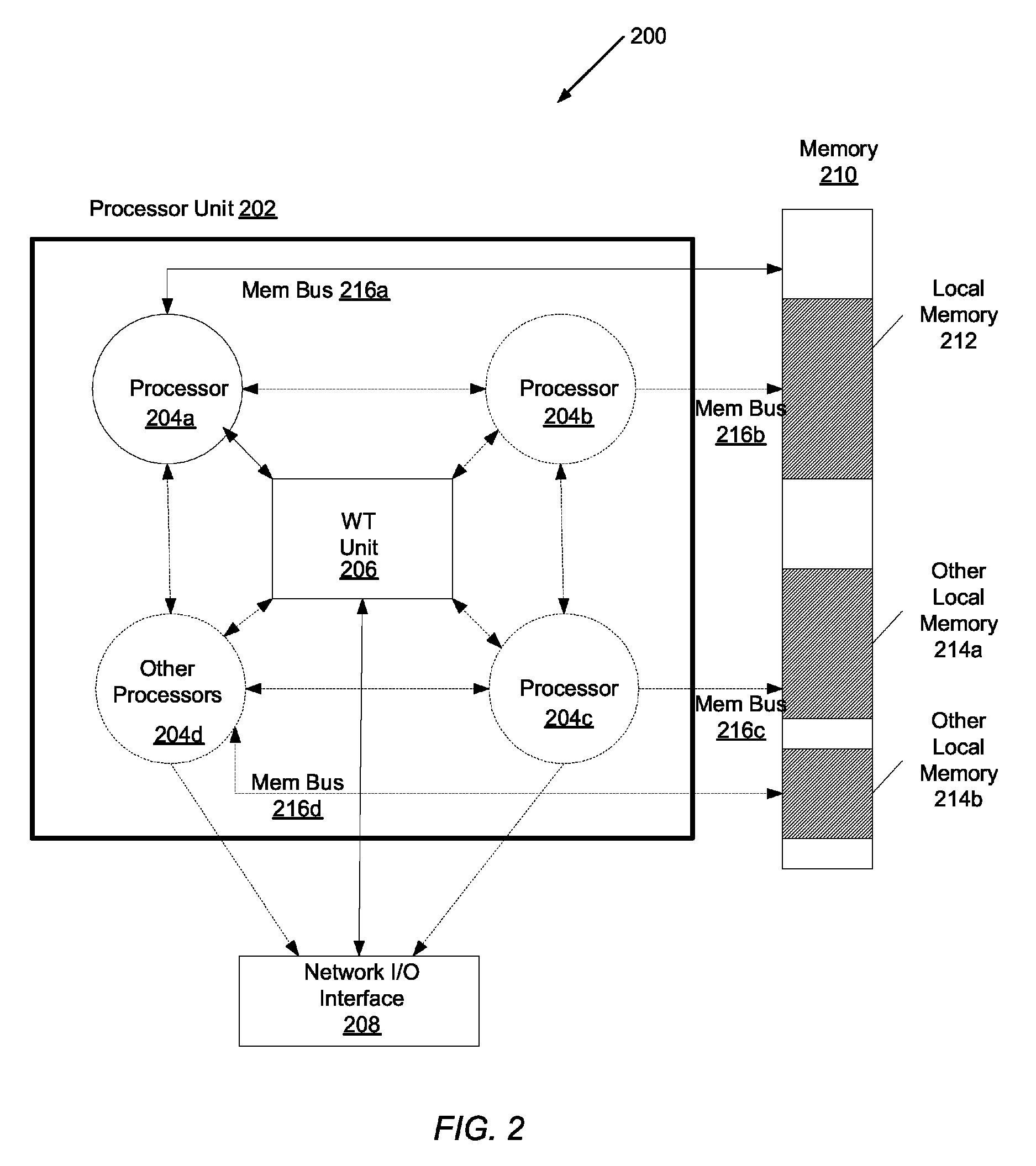

Efficient hardware scheme to support cross-cluster transactional memory

A method and system for increasing programmability and scalability of a multi-processor network. A system includes two or more nodes coupled via a network with each node comprising a processor unit and memory. The processor unit includes one or more processors and a wiretap unit. The wiretap unit is configured to monitor memory accesses of the processors. A transaction may execute a number of read and / or write operations to memory. The nodes are configured to replicate one or more portions of memory; detect data conflicts to memory; and restore memory to pre-transaction state if needed.

Owner:ORACLE INT CORP

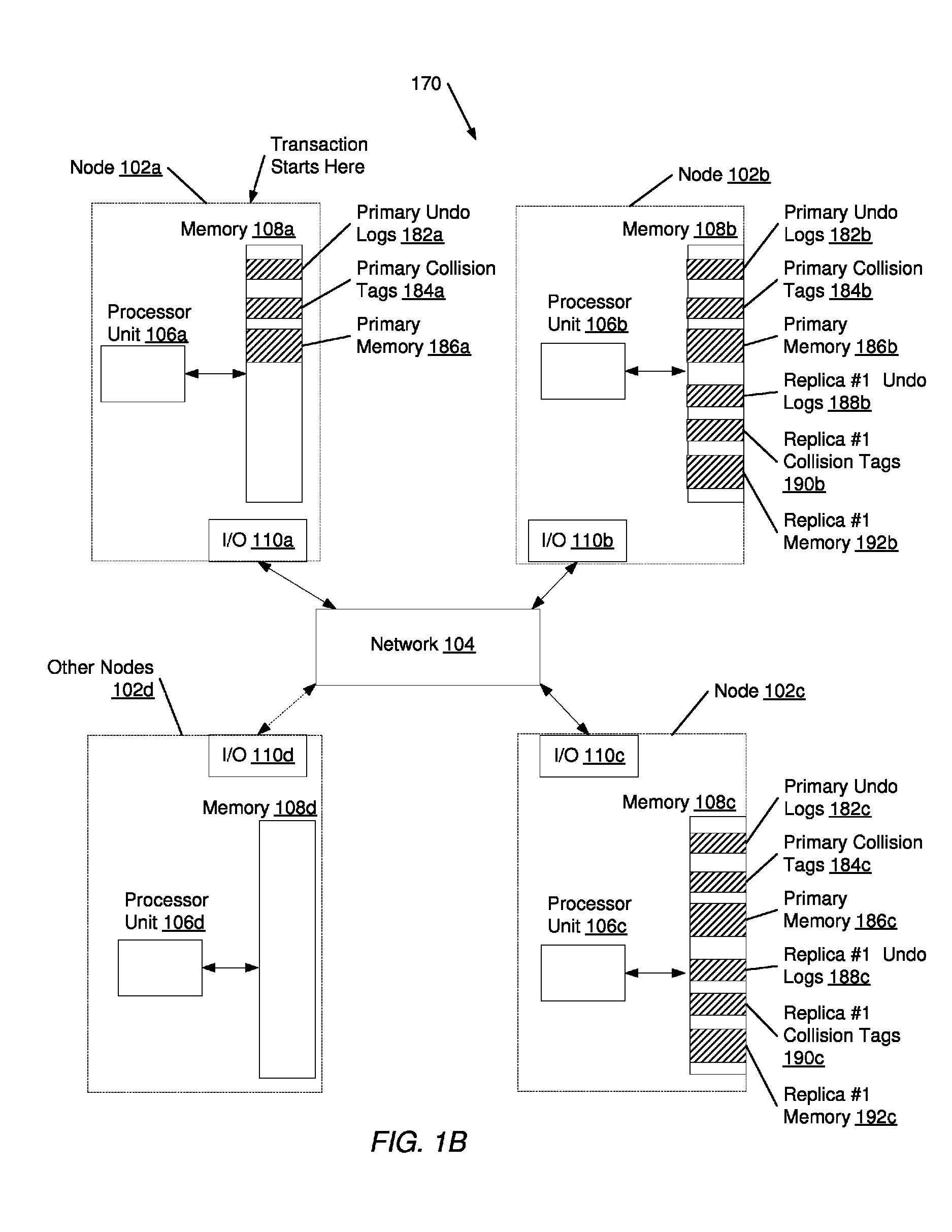

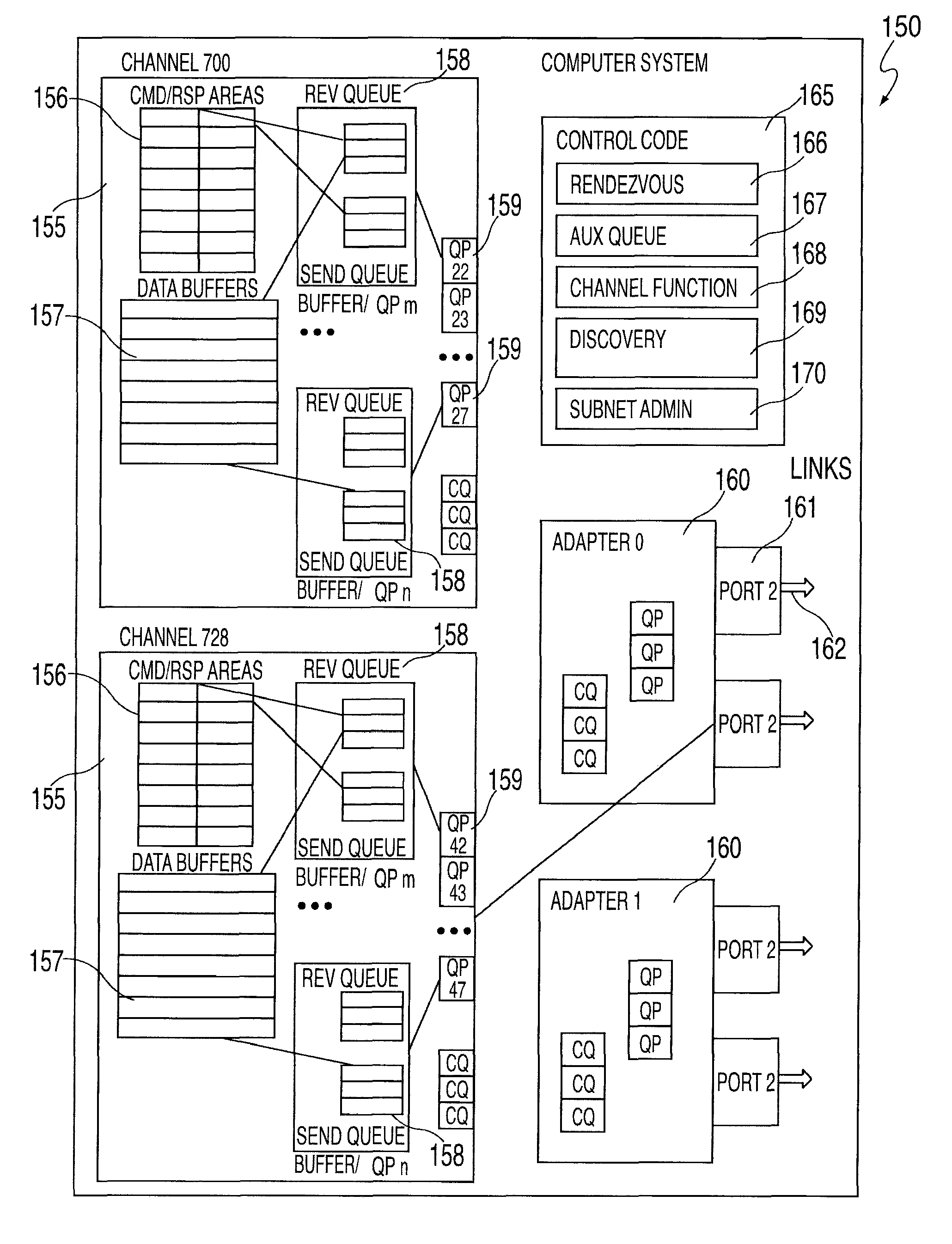

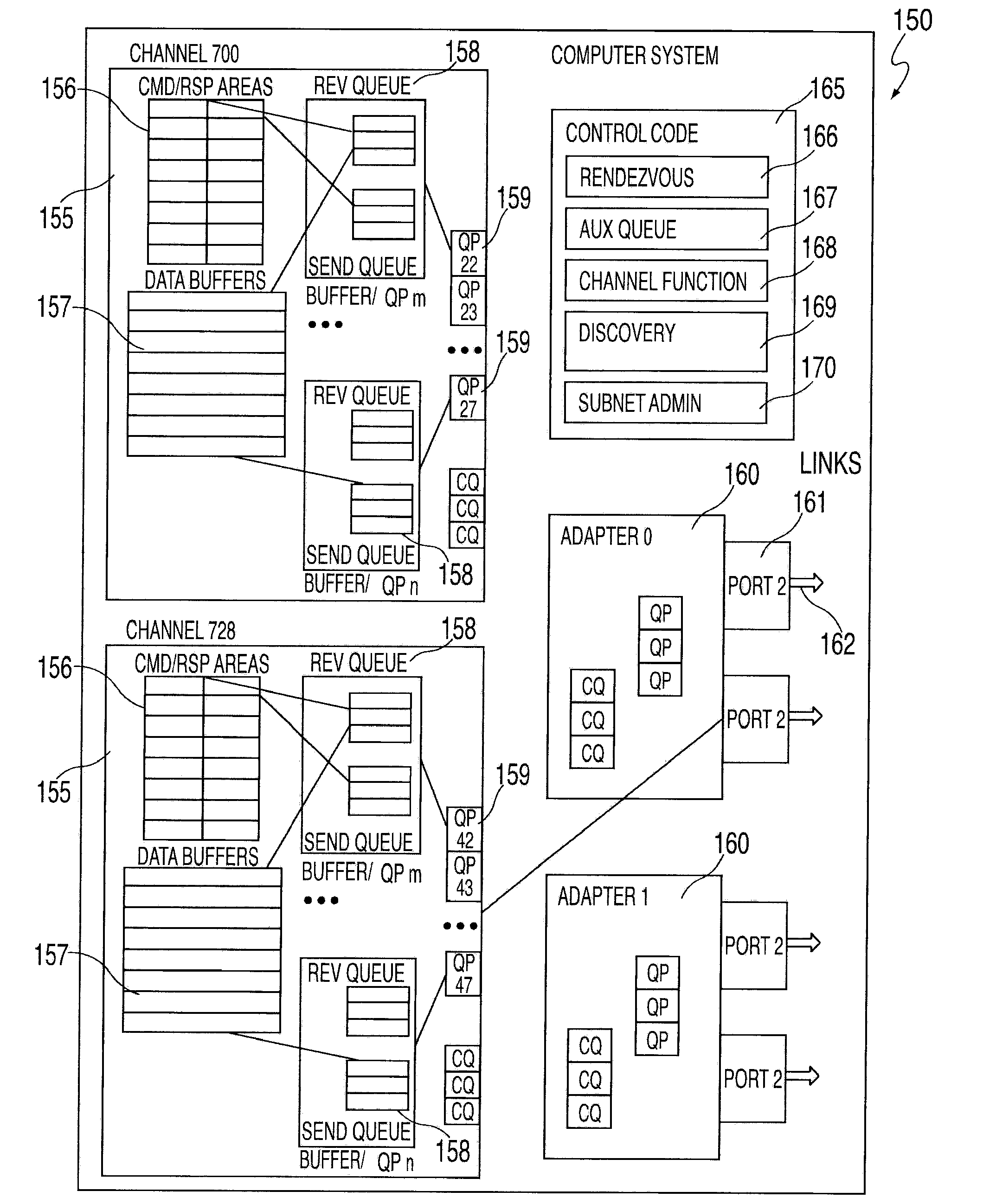

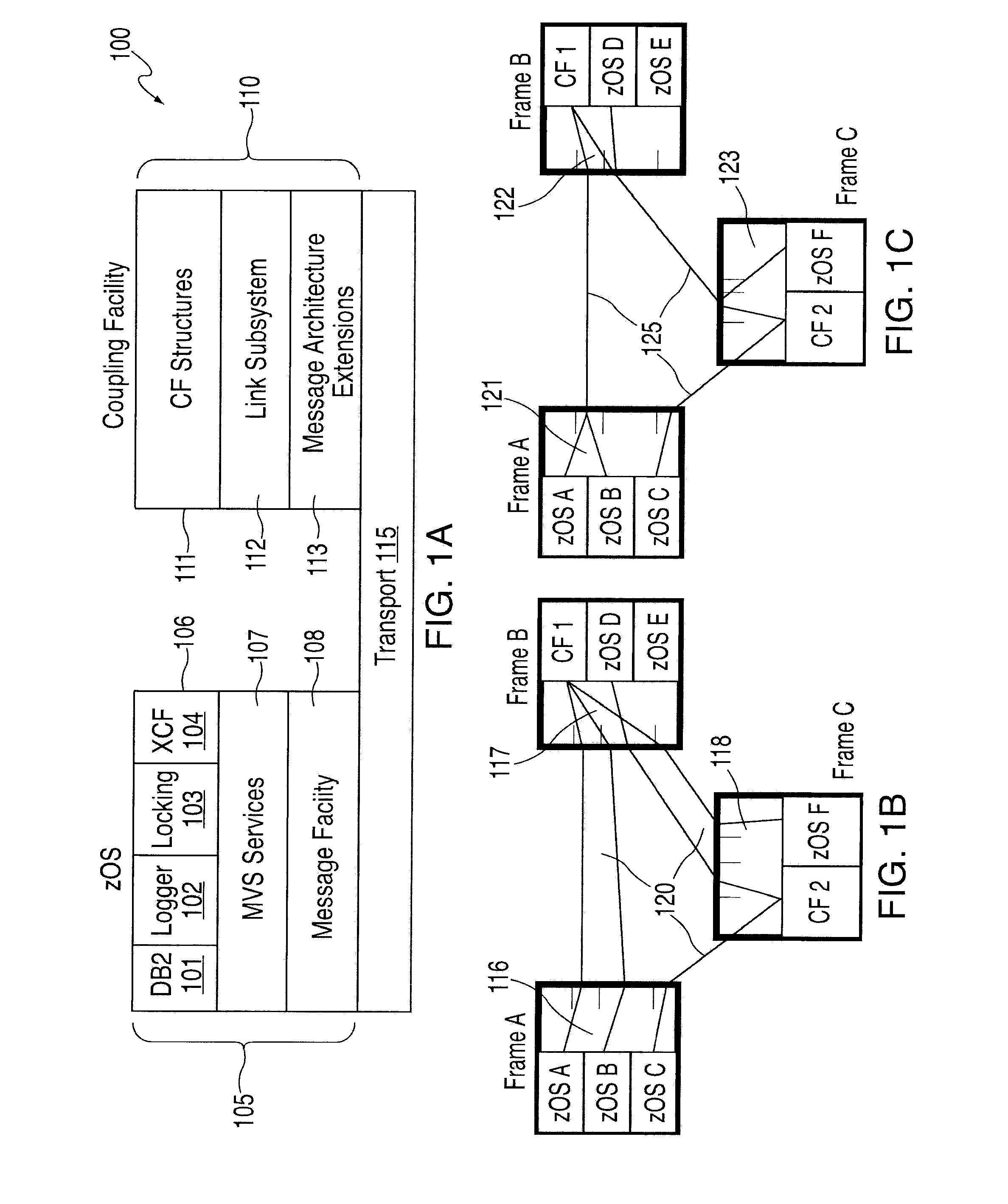

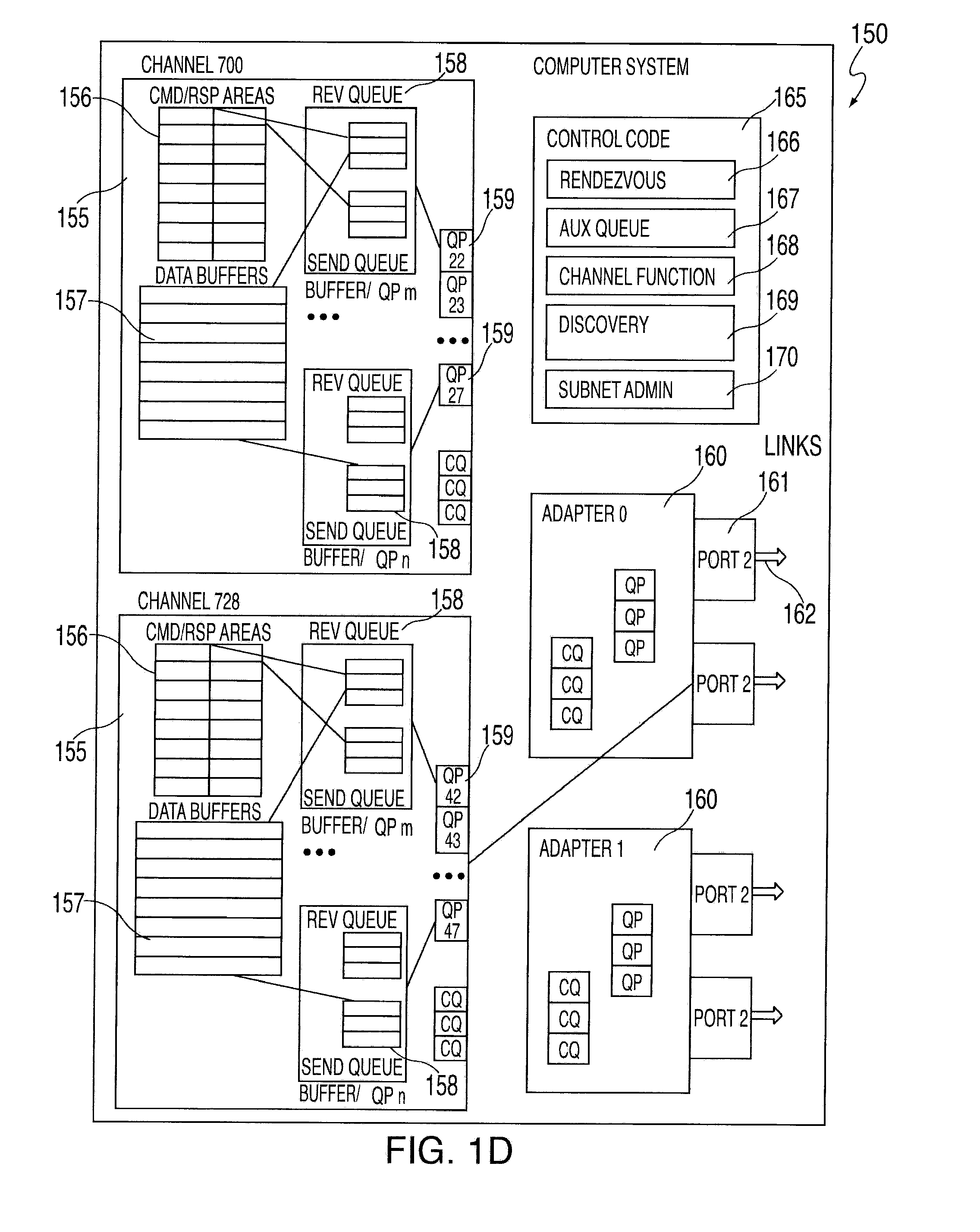

Discovery of a virtual topology in a multi-tasking multi-processor environment

InactiveUS7962564B2Error preventionFrequency-division multiplex detailsComputer networkMulti processor

A computer program product, apparatus and method for identifying processors in a multi-tasking multiprocessor network, the computer program product including a tangible storage medium readable by a processing circuit and storing instructions for execution by the processing circuit for performing a method including storing a service record for a port to which an LID has been assigned, retrieving service records for nodes to which channel paths may connect, retrieving path records that provide address destinations for the nodes identified in the service records, initiating channel initialization for the channel paths defined for the port and removing the service record for the port.

Owner:IBM CORP

Maintaining memory checkpoints across a cluster of computing nodes

A method and system for increasing reliability and availability of a multi-processor network. A system includes a network with at least two nodes, with each node comprising a multi-processor unit (mpu) and memory. The mpu includes one or more processors and a wiretap unit. The wiretap unit and the memory included in the node are coupled to the processors in the node. The wiretap unit is configured to monitor memory accesses of the processors and convey data indicative of such accesses to a second node. The second node maintains a replica of memory in the first node, and is configured to undo modifications to the memory if needed. In the event of a hardware or software fault, the nodes are configured to restart the application on another node.

Owner:ORACLE INT CORP

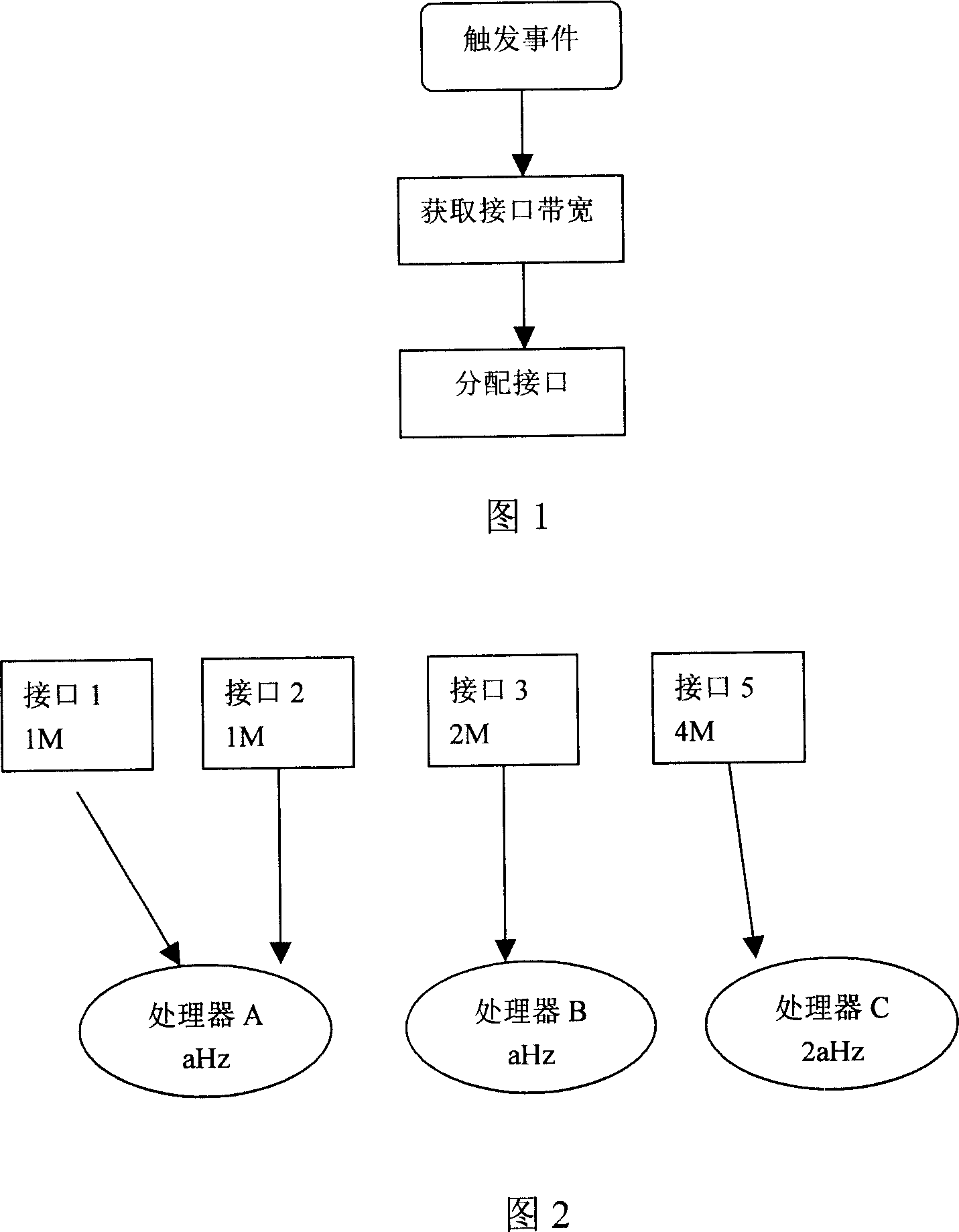

Multi-processor load distribution-regulation method

ActiveCN1979423AAvoid busynessAvoid mutual exclusionMultiprogramming arrangementsMultiple digital computer combinationsTraffic capacityMulti processor

The invention is a multiprocessor load allocation regulating method, relating to the data communication field, especially relating to a technique for regulating load allocation of each processor in multiprocessor network equipment. And it comprises the steps of: a. CPU obtains bandwidth condition of system interface socket; b. according to processing ability of each processor, CPU allocates interface to each processor in proportion. And it makes the data flow processed by each processor in operation basically equivalent, relatively uniformly and appropriately allocating processor resources and avoiding load allocation ununiformity in a multiprocessor system.

Owner:MAIPU COMM TECH CO LTD

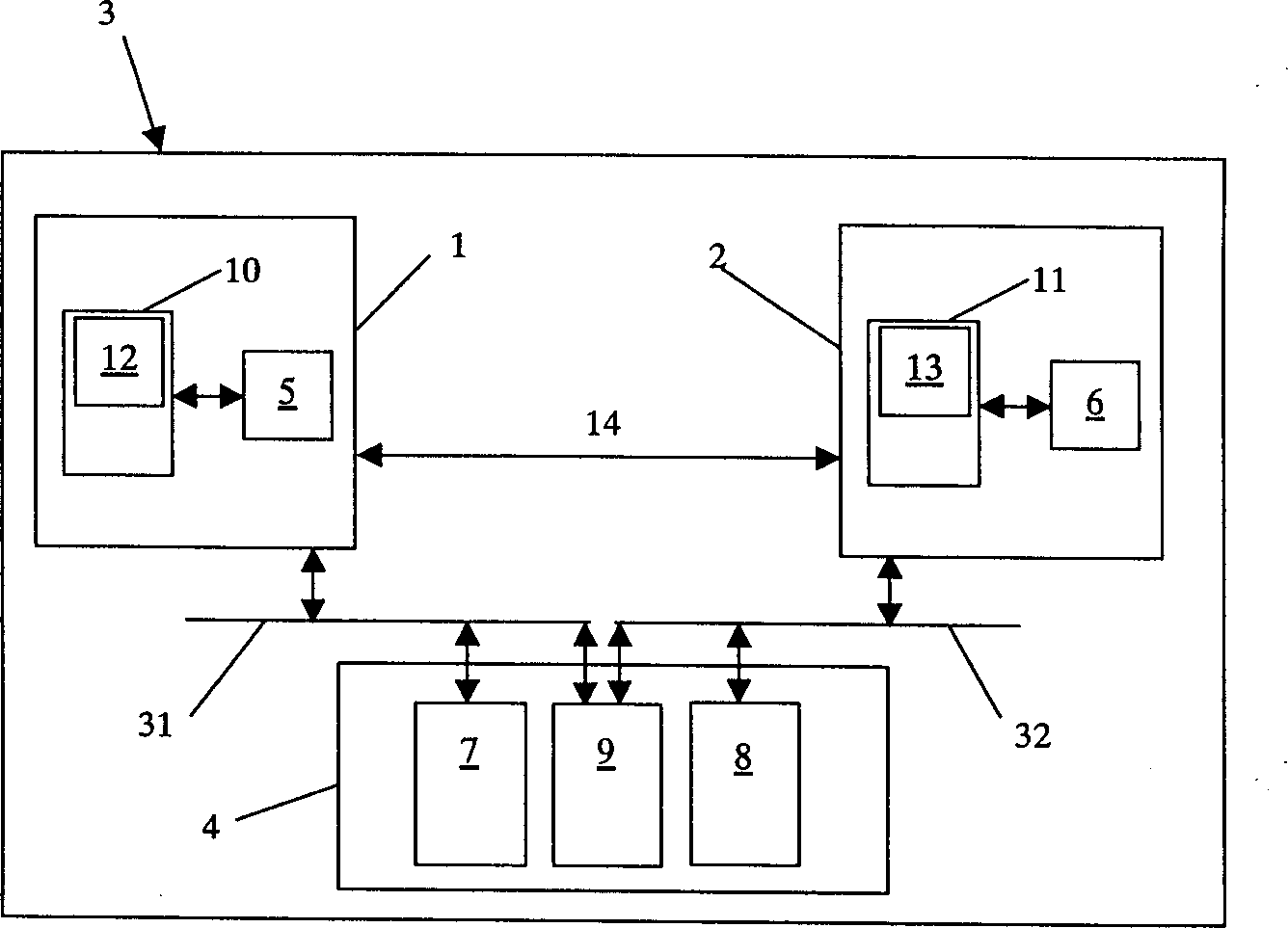

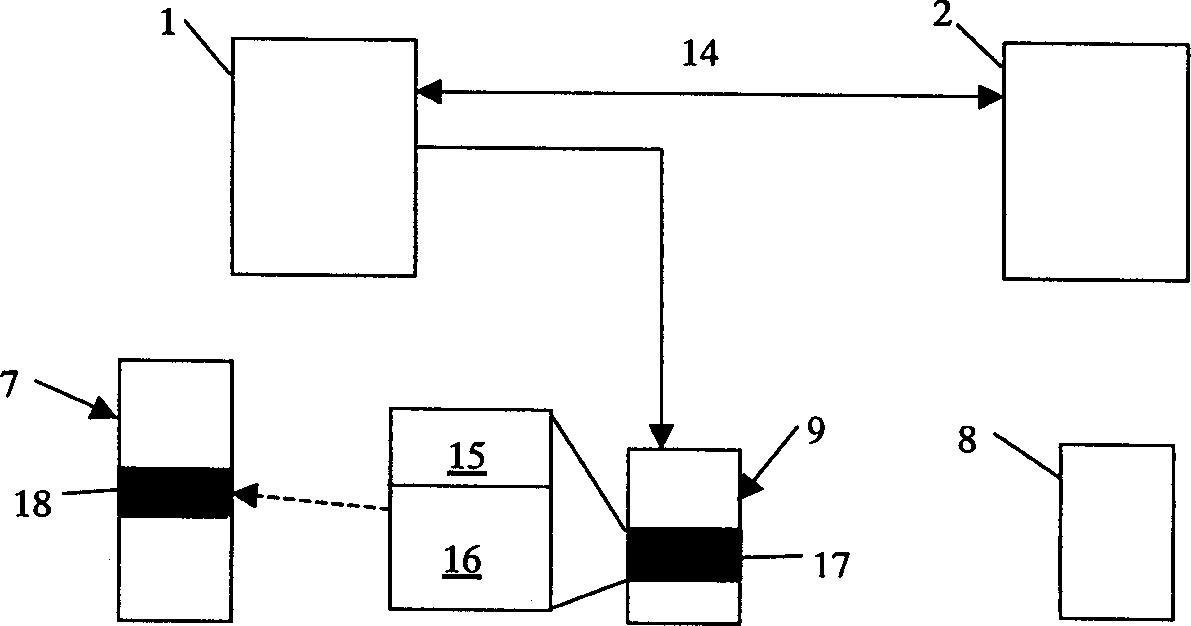

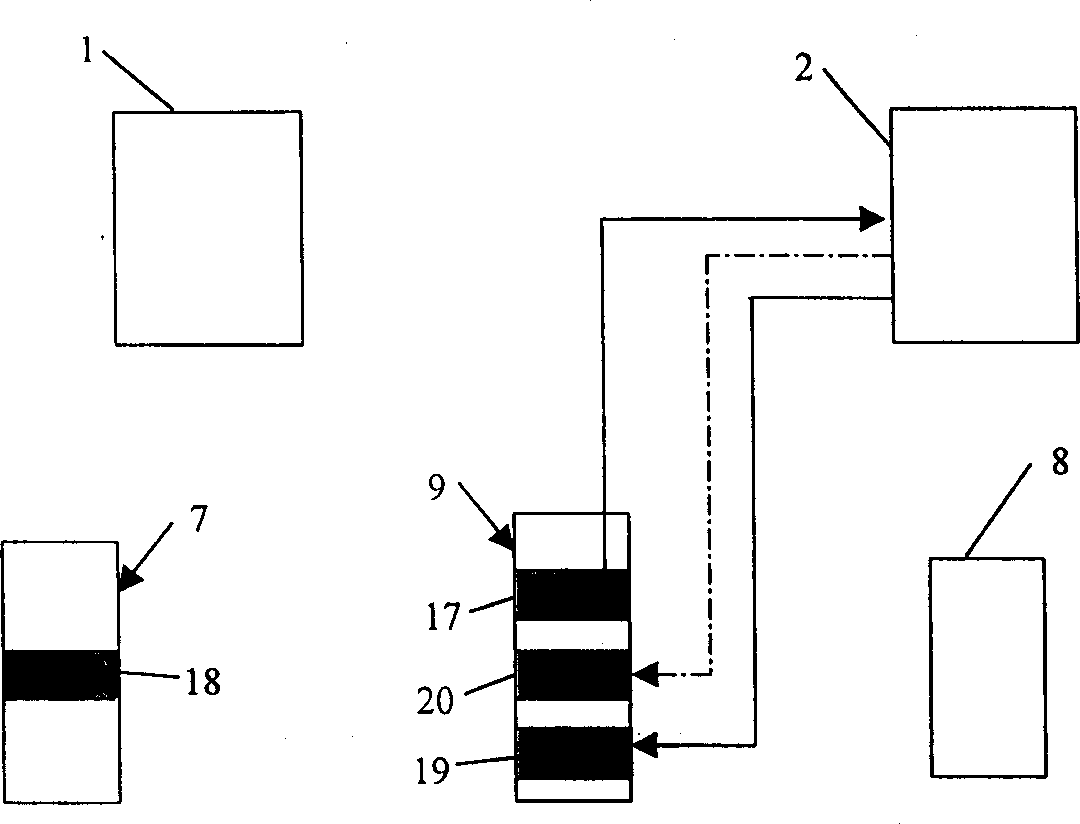

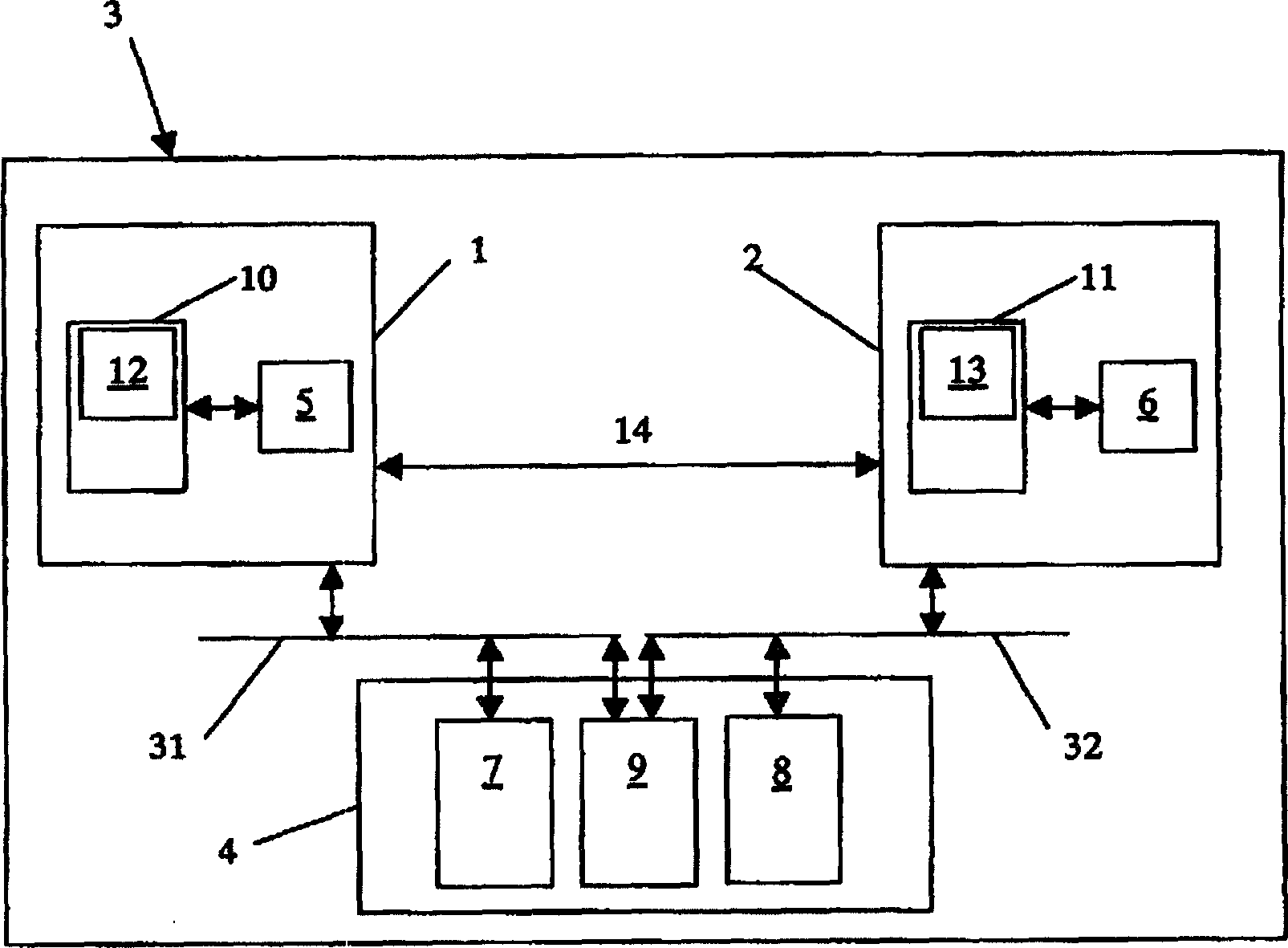

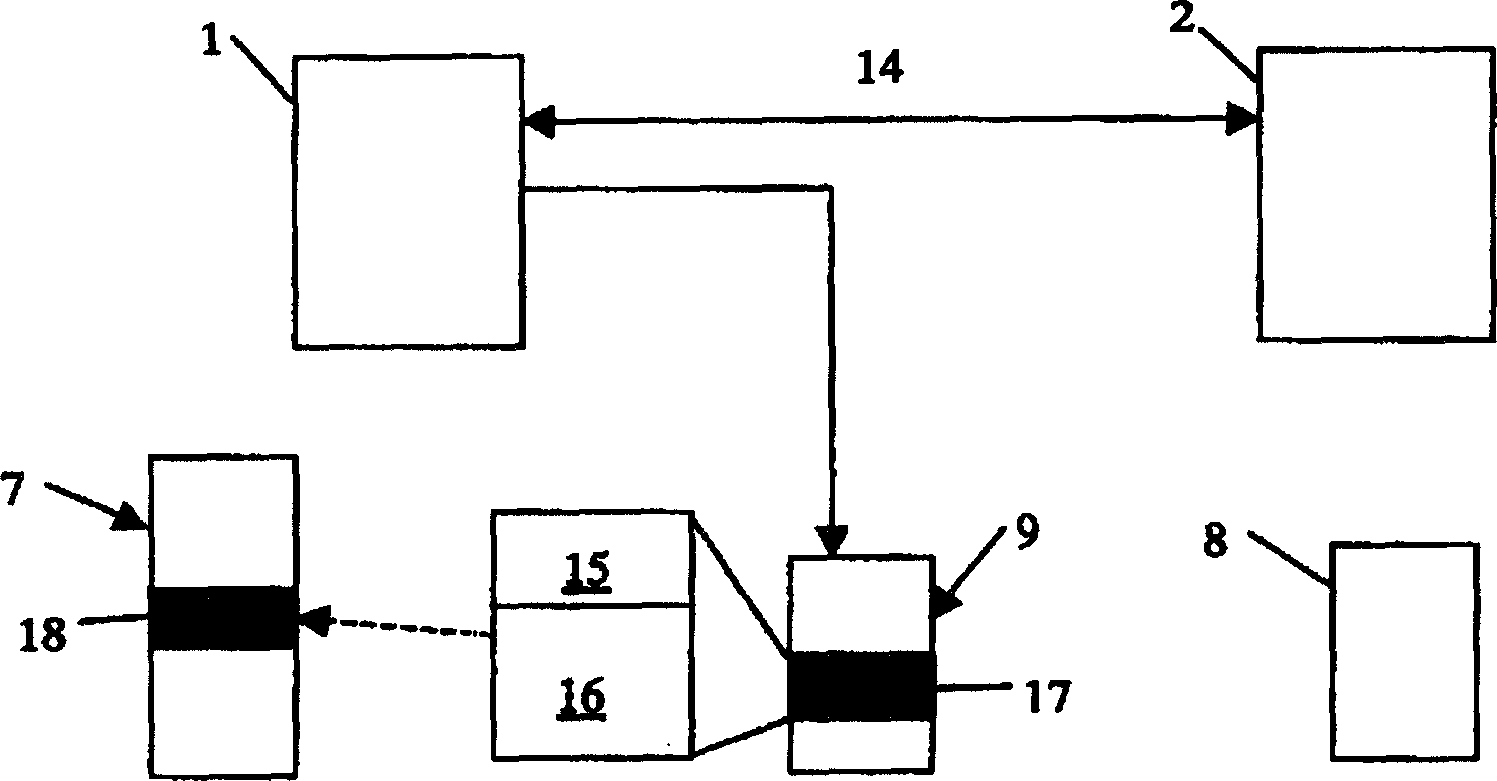

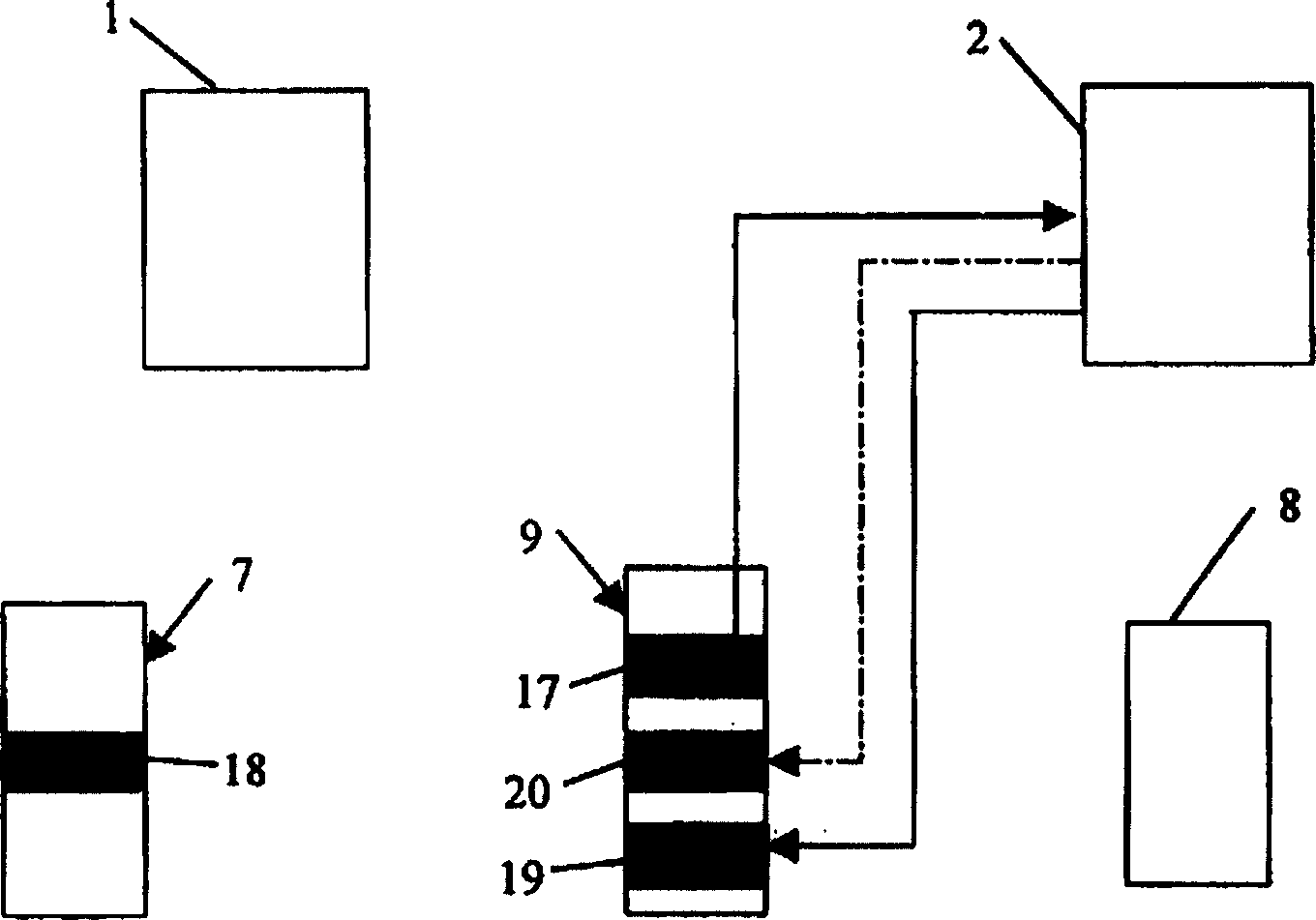

Data internal storage managing system and method, and related multiprocessor network

InactiveCN1347034AMemory adressing/allocation/relocationDigital computer detailsParallel computingMultiprocessor network

The present invention relates to a system and a method of memory management of data consistency relating to a main memory (4) accessible by at least two processors (1,2), as well as an associated multiprocessor network. The management system comprises an assembly for management of shared access of the processors to a common area (9) of the main memory, referred to as the exchanges area, at least one copy module (12,13) intended for performing a data copy between at least one first processor comprising at least one cache memory and the exchanges area and at least one transfer module (12,13) intended for performing a transfer of data between the exchanges area and at least one second processor. Triggering means controlled by the second processors trigger the copy modules and transfer modules when the first processors submit requests involving transfers of data between the first and second processors.

Owner:THOMSON LICENSING SA

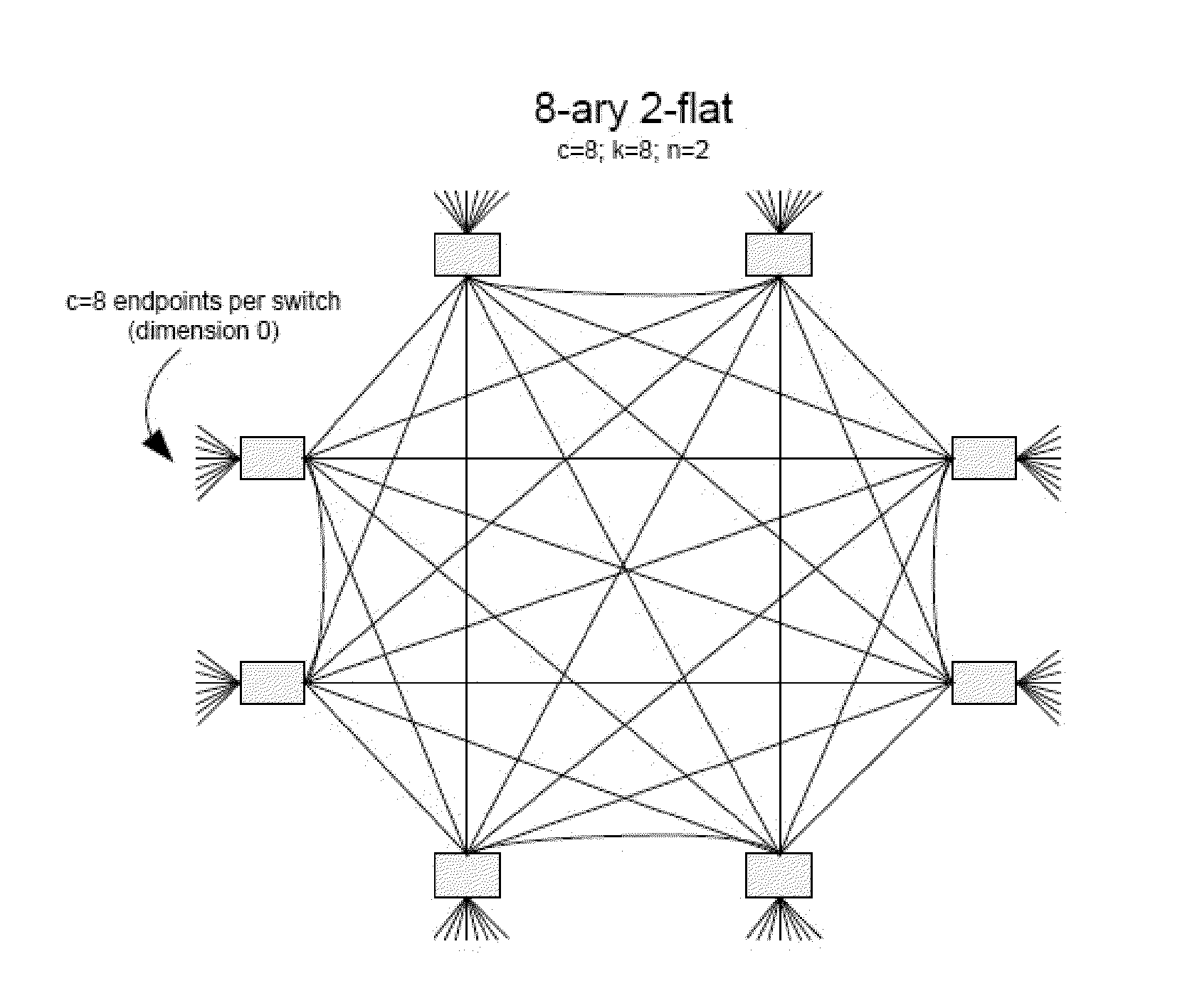

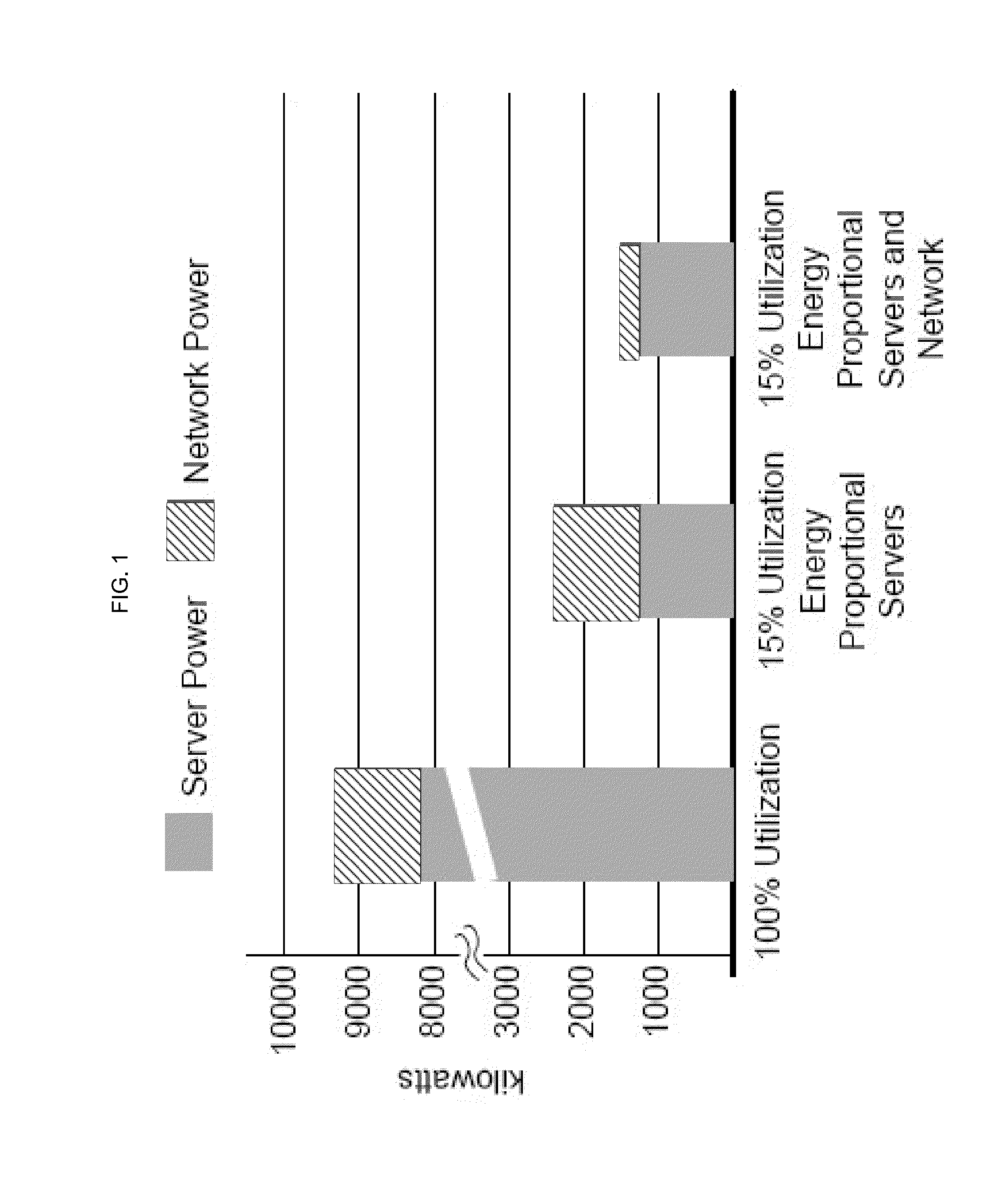

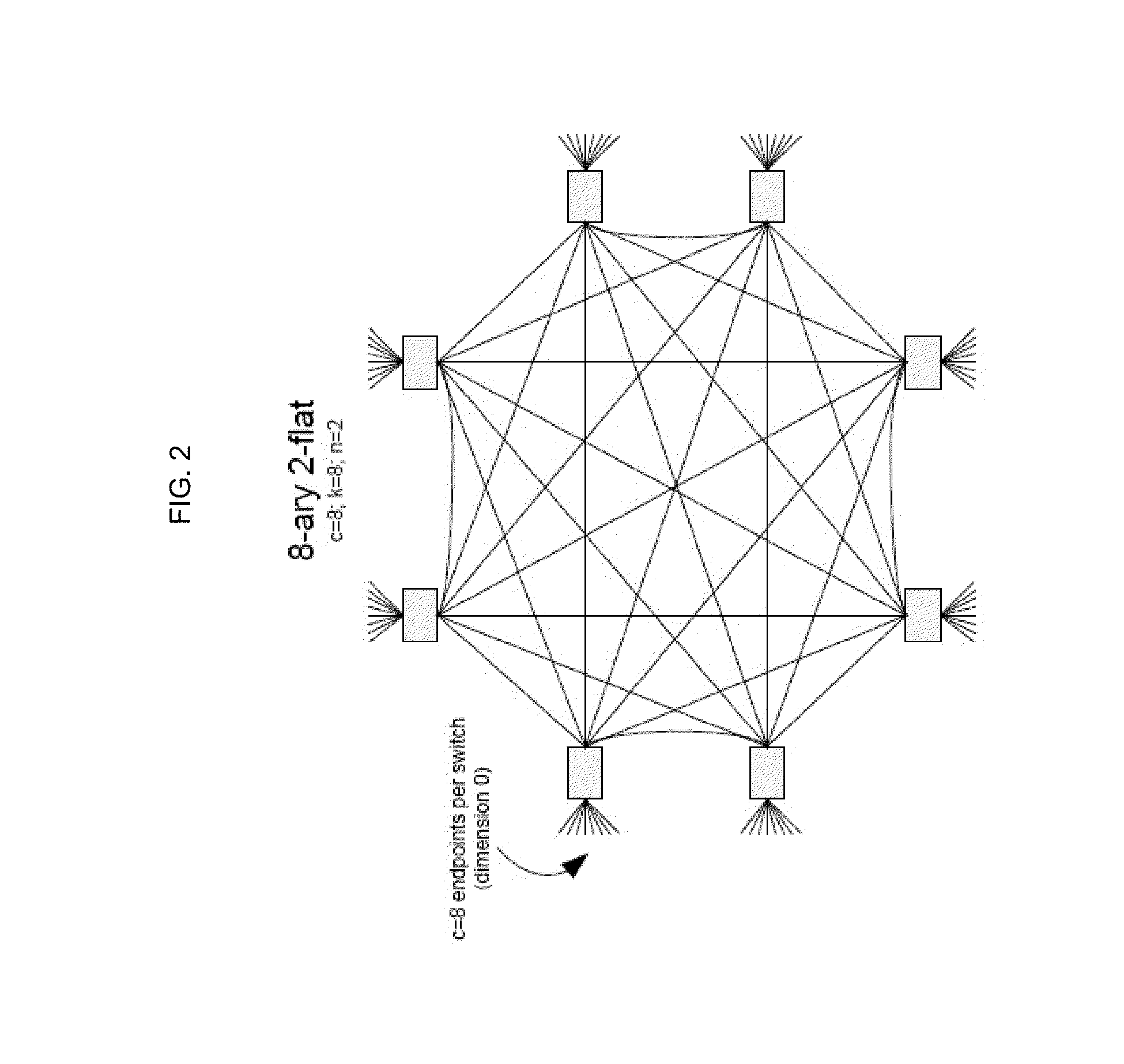

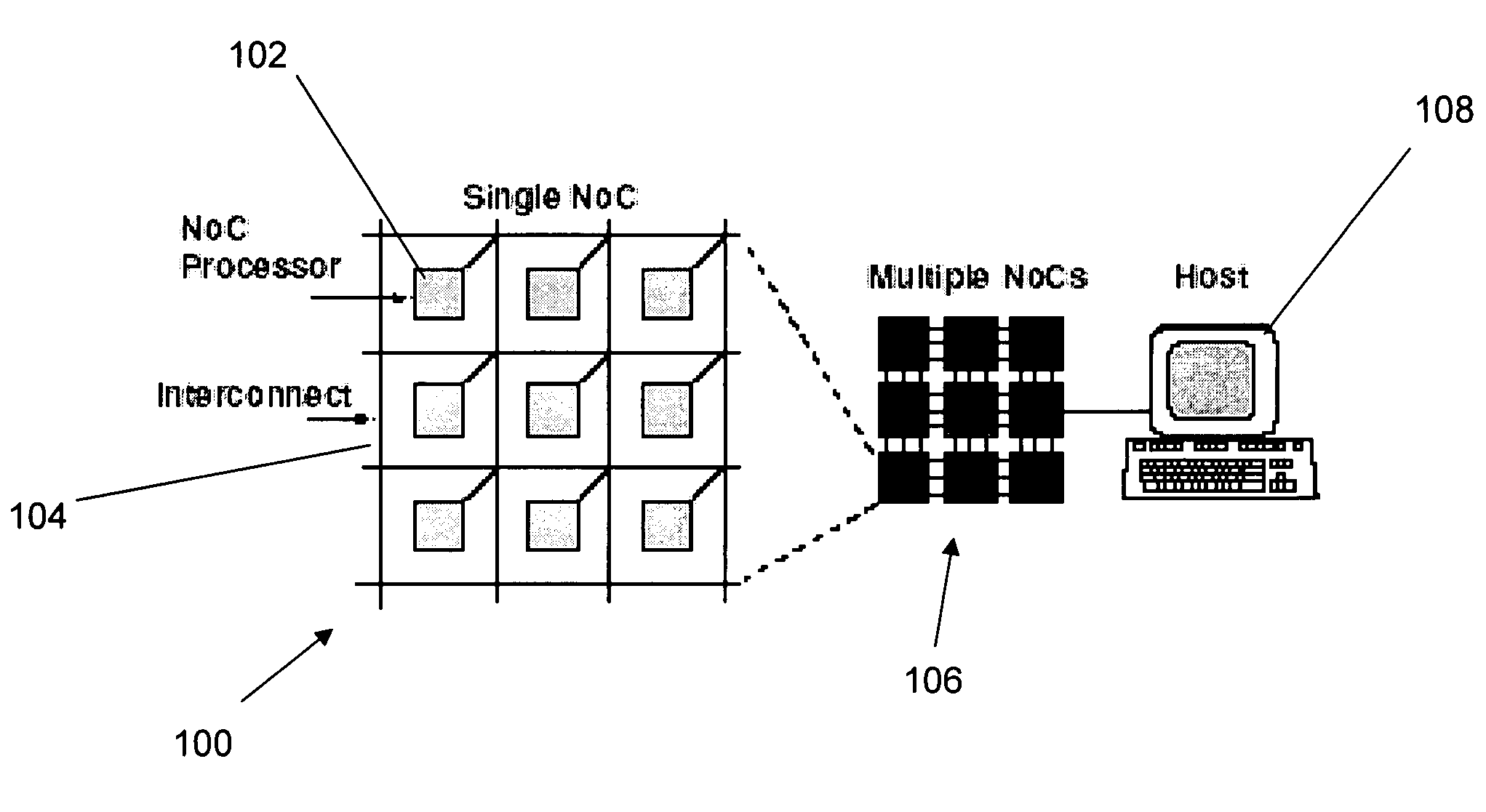

Systems and methods for energy proportional multiprocessor networks

ActiveUS8601297B1Reduce power consumptionEnergy efficient ICTVolume/mass flow measurementTraffic capacityTraffic intensity

Energy proportional solutions are provided for computer networks such as datacenters. Congestion sensing heuristics are used to adaptively route traffic across links. Traffic intensity is sensed and links are dynamically activated as they are needed. As the offered load is decreased, the lower channel utilization is sensed and the link speed is reduced to save power. Flattened butterfly topologies can be used in a further power saving approach. Switch mechanisms are exploit the topology's capabilities by reconfiguring link speeds on-the-fly to match bandwidth and power with the traffic demand. For instance, the system may estimate the future bandwidth needs of each link and reconfigure its data rate to meet those requirements while consuming less power. In one configuration, a mechanism is provided where the switch tracks the utilization of each of its links over an epoch, and then makes an adjustment at the end of the epoch.

Owner:GOOGLE LLC

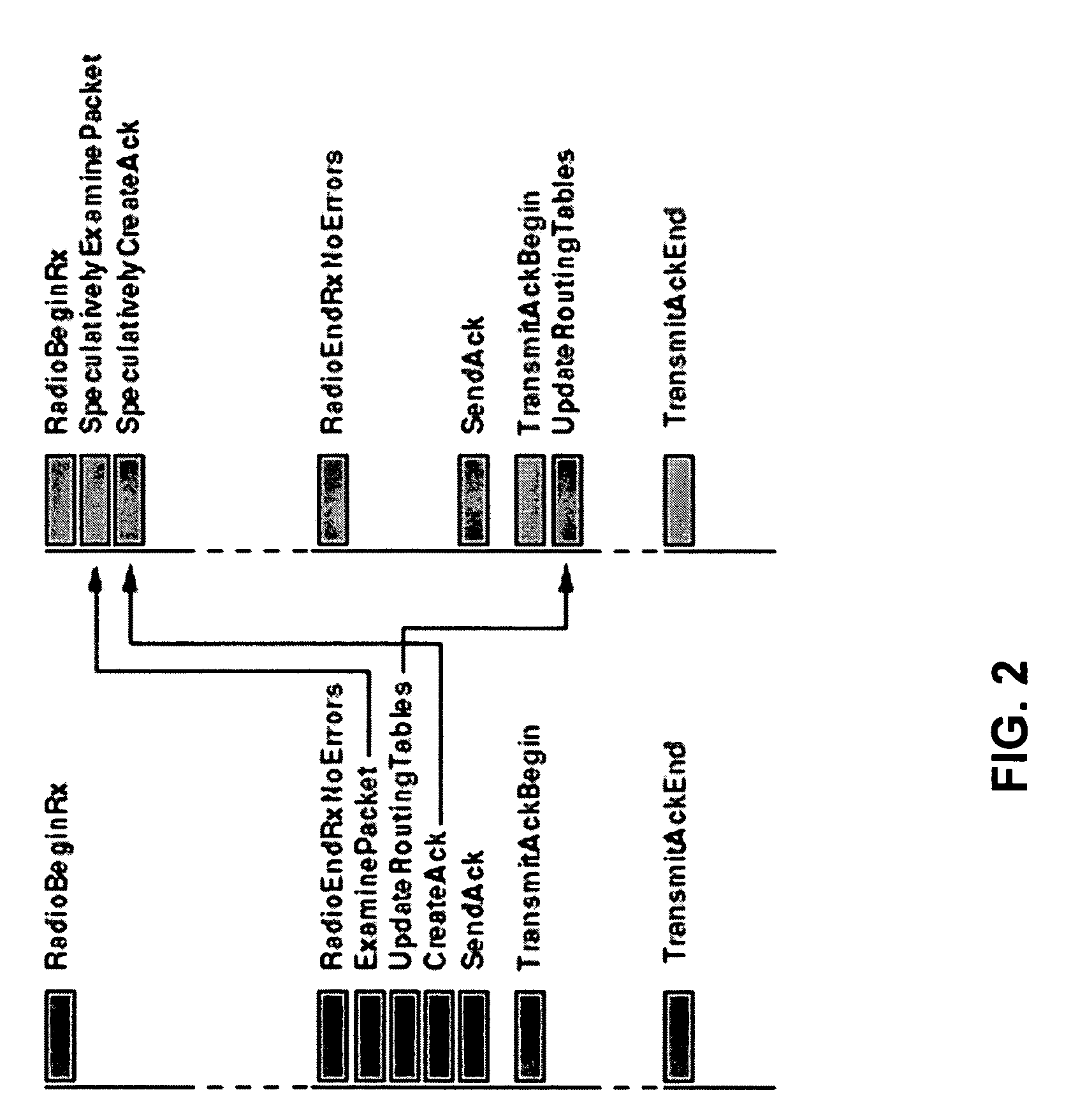

Event-synchronization protocol for parallel simulation of large-scale wireless networks

ActiveUS20090187395A1Easy to scaleAnalogue computers for electric apparatusRadio transmissionEvent synchronizationTimestamp

An event synchronization protocol called time-based synchronization (TBS) is employed to control operation of a network simulation. In TBS, processors in the simulated network execute events based on comparisons between timestamps for each event and a value generated by a time tracking device in the processor. In this manner, event execution is not dependent on other processes in the network and the simulation can actually be carried out at speeds faster than real time. A multiprocessor network is specially designed to execute TBS-based simulations.

Owner:CORNELL RES FOUNDATION INC

Event-synchronization protocol for parallel simulation of large-scale wireless networks

ActiveUS7564809B1Easy to scaleAnalogue computers for electric apparatusRadio transmissionTimestampEvent synchronization

An event synchronization protocol called time-based synchronization (TBS) is employed to control operation of a network simulation. In TBS, processors in the simulated network execute events based on comparisons between timestamps for each event and a value generated by a time tracking device in the processor. In this manner, event execution is not dependent on other processes in the network and the simulation can actually be carried out at speeds faster than real time. A multiprocessor network is specially designed to execute TBS-based simulations.

Owner:CORNELL RES FOUNDATION INC

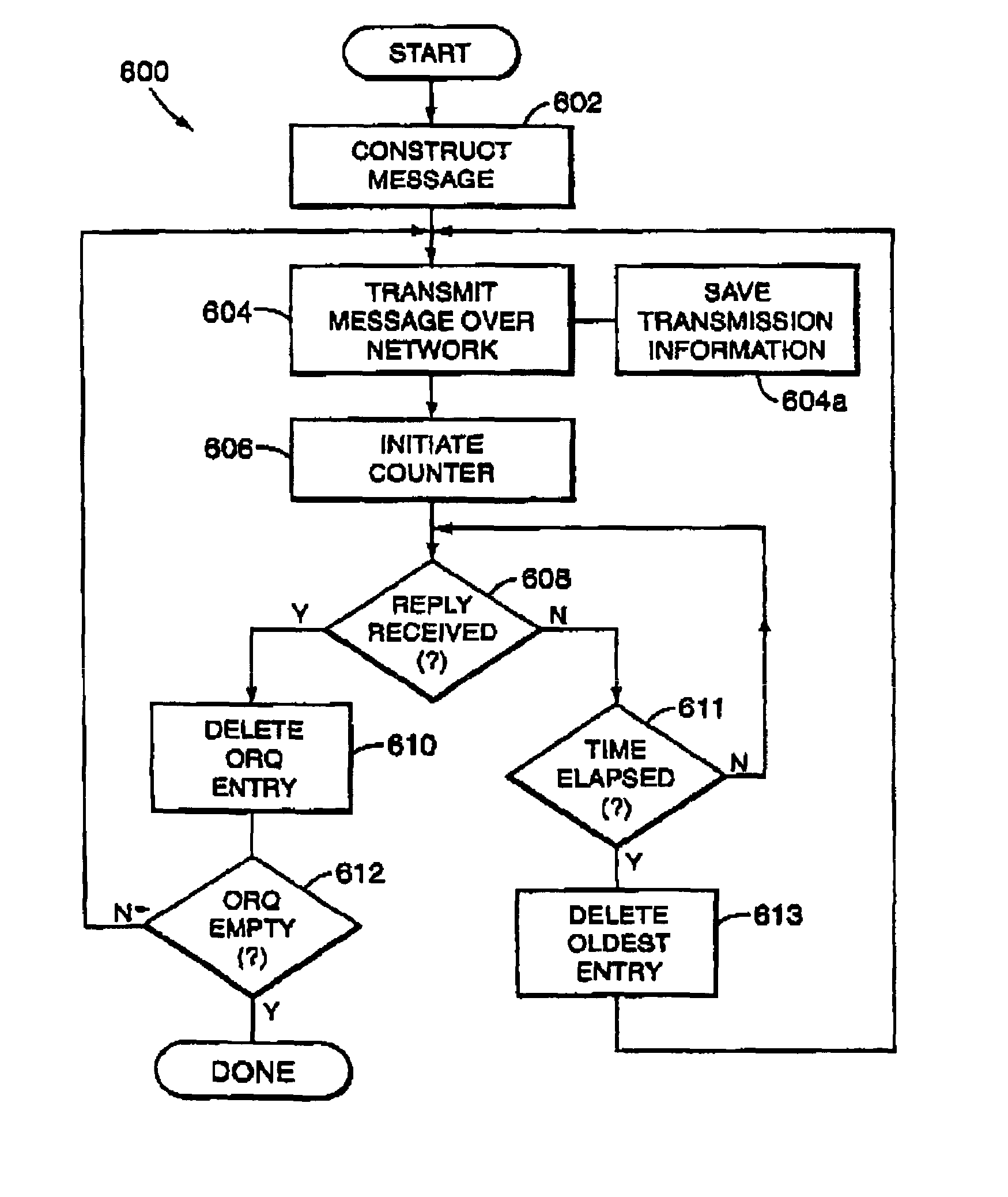

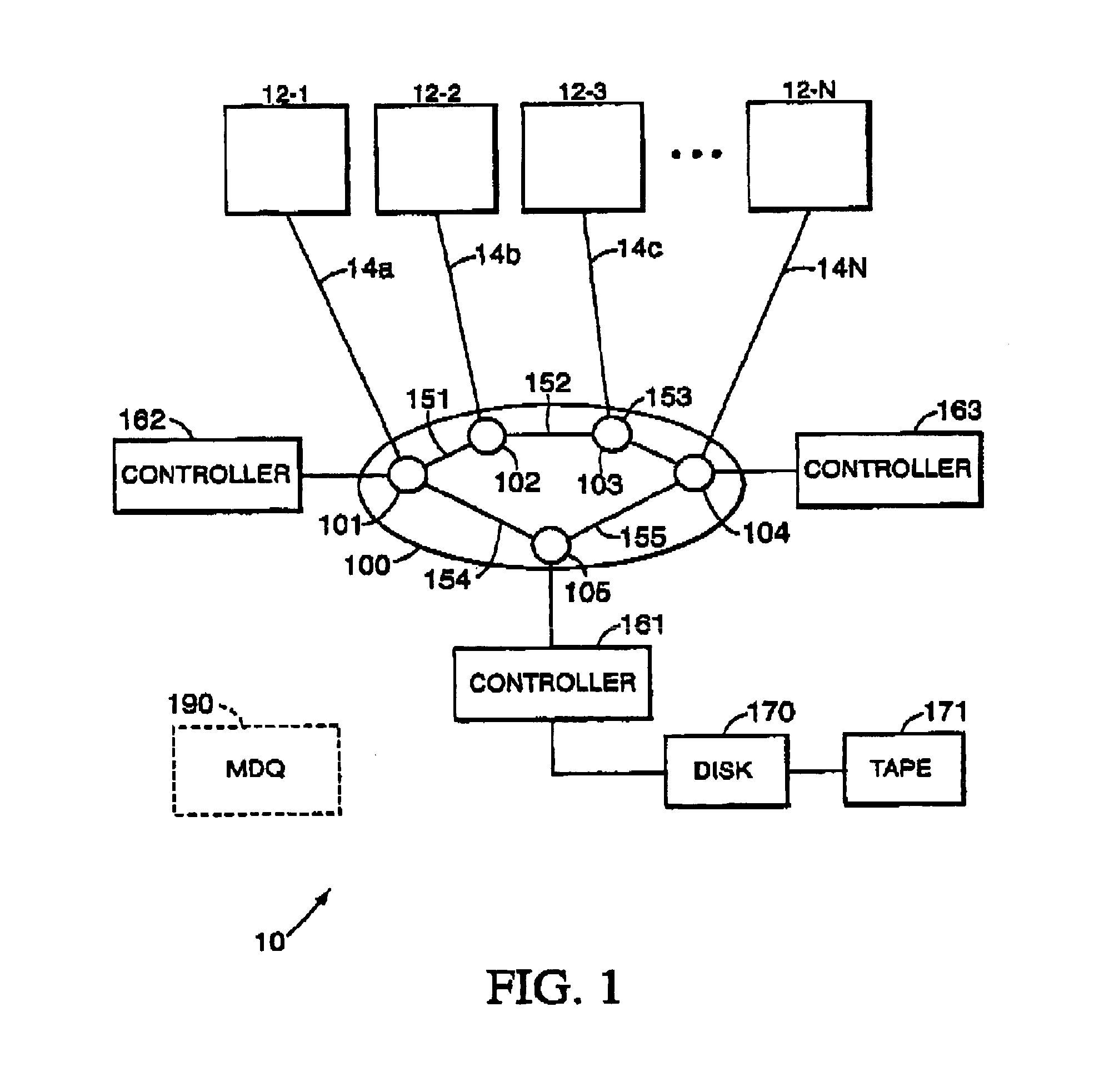

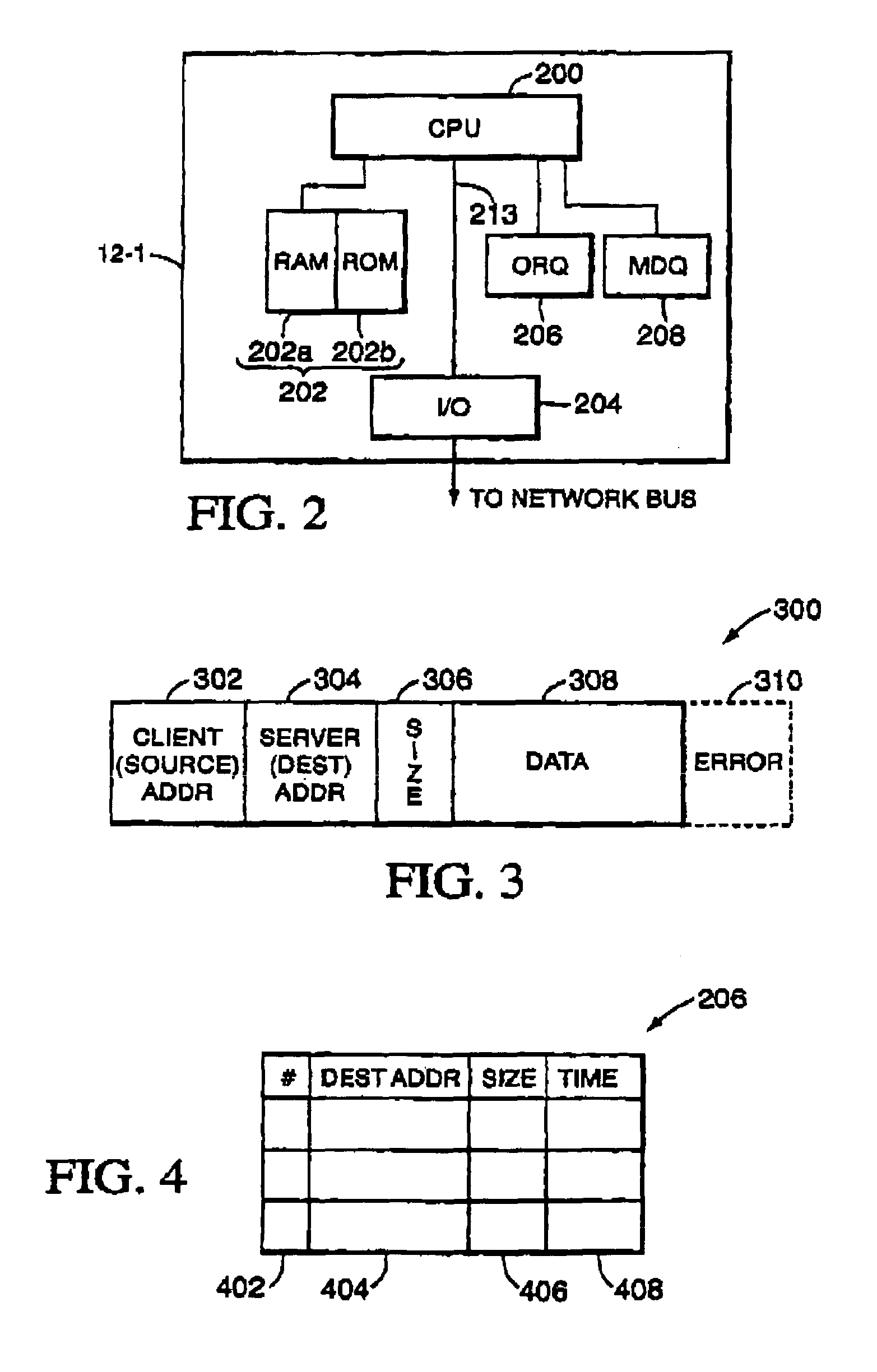

System and method for controlling network traffic flow in a multi-processor network

ActiveUS7388834B2Maximizing network efficiencyAbility to provideError preventionTransmission systemsTransmission protocolPush and pull

A system and method for controlling network traffic flow in a multi-processor network is disclosed. The method employs a two-part algorithm to determine when it is appropriate for a client node to transmit data over a network to one or more server nodes. The first part of the algorithm calls for the client node to transmit data over the network after receiving an acknowledgement from one or more of the server nodes to which data transfer is outstanding. The second part of the algorithm provides for the client node transmitting data over the network after a predetermined time interval has elapsed since a data transmission. The time interval is based, in part, on the length of outstanding data packets and a statistical analysis of the number of nodes transmitting or receiving data packets. The transmission of data over the network is accomplished by a hybrid scheme, comprising a combination of PUSH and PULL transmission protocols.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

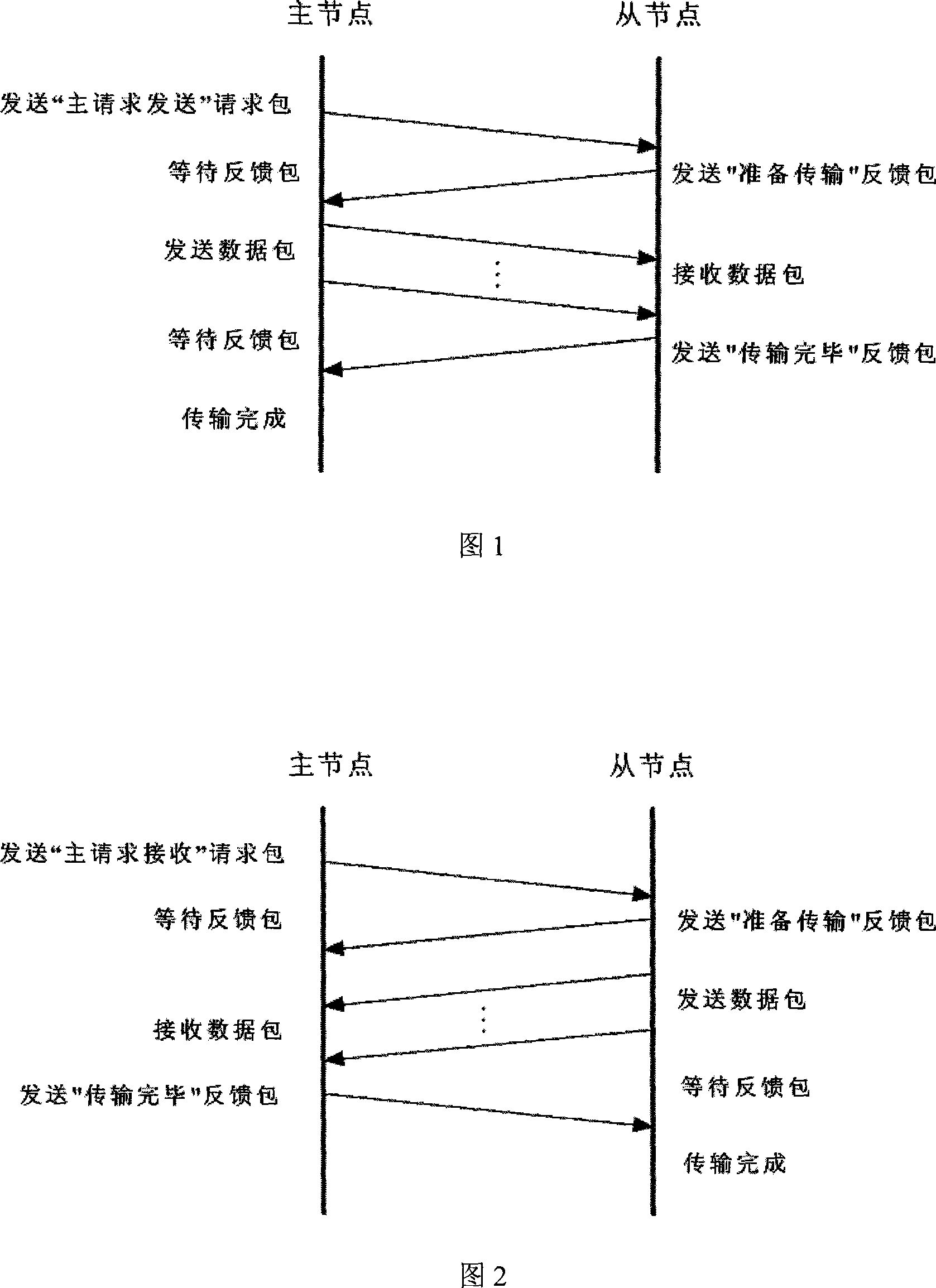

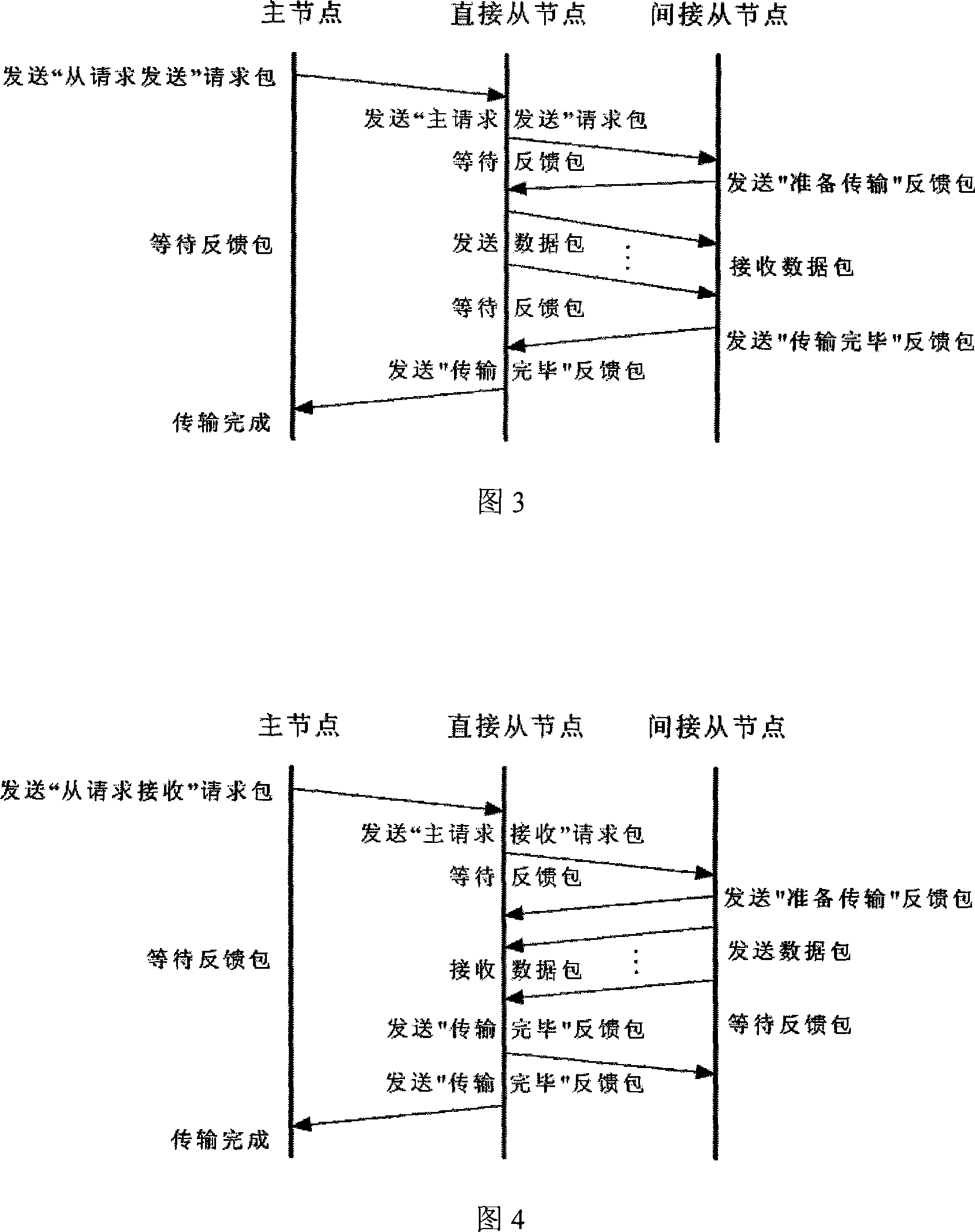

Transport protocols suitable for multiprocessor network on chip

InactiveCN101227486AError prevention/detection by using return channelTransmission protocolMulti processor

The invention discloses a transmission protocol which is suitable to the multi-processor on-chip network, and is suitable to the data transmission among on-chip network nodes, which comprises the four transmission processes, the first is that sending out the main request, the second is that receiving the main request, the third is that sending out the sub request, and the fourth is that receiving the sub request. The transmission protocol of the invention which is suitable to the multiprocessor on-chip network is mainly used on the data transmission among the multiprocessor on-chip network nodes.

Owner:ZHEJIANG UNIV

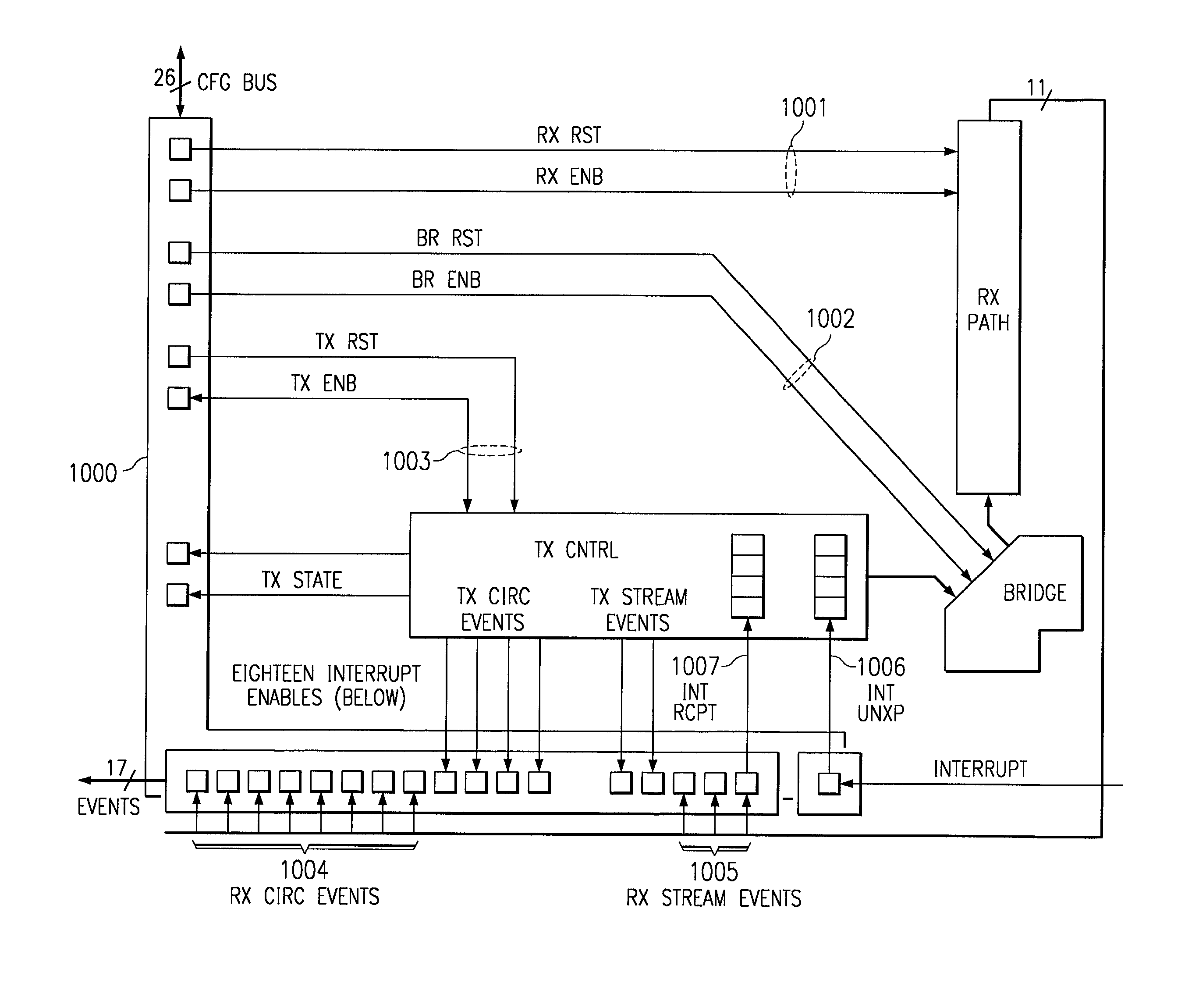

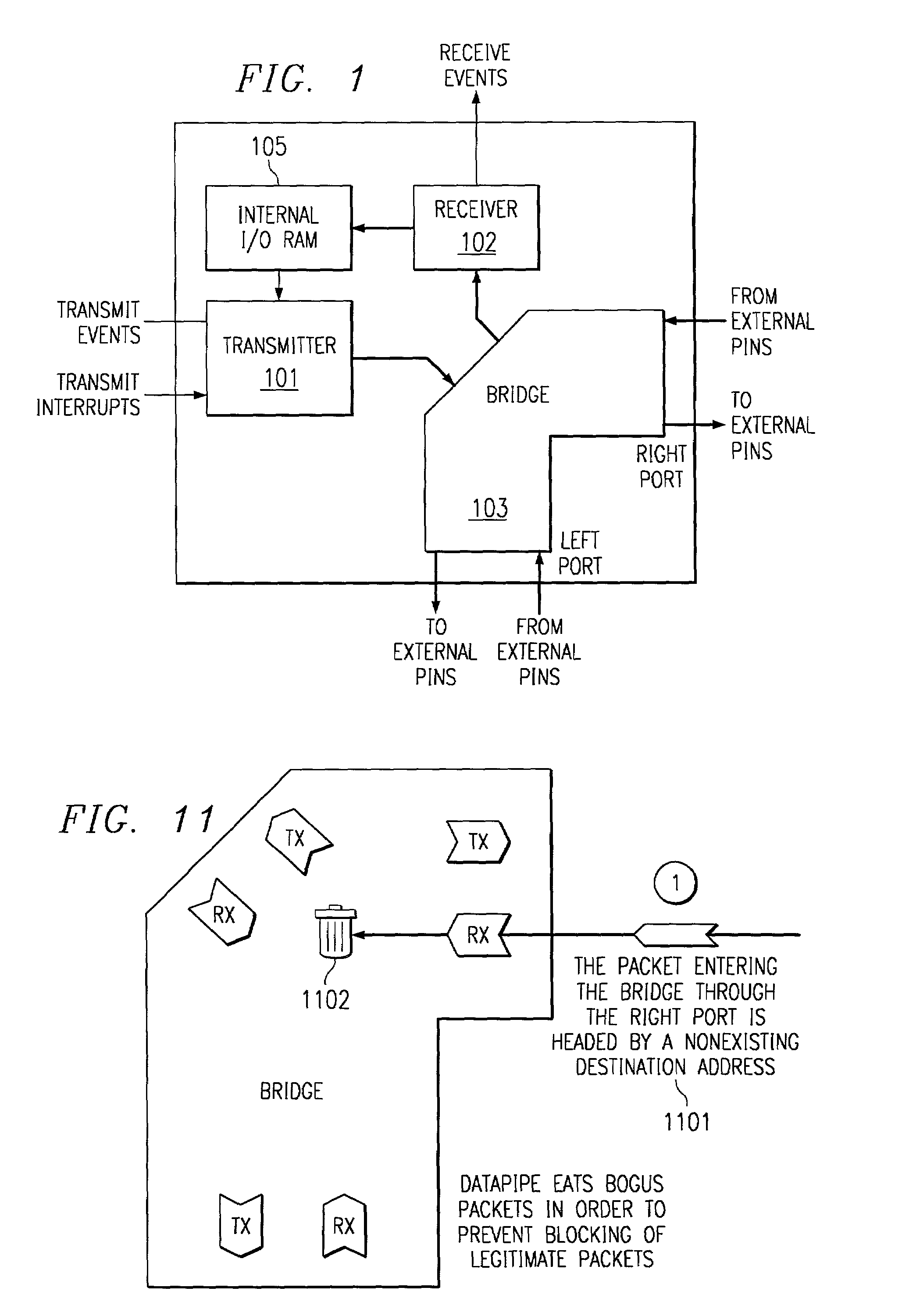

Multiprocessor network node failure detection and recovery

ActiveUS7002975B2Improve horizontal connectivityError preventionFrequency-division multiplex detailsNetwork packetMultiprocessor network

In a node failure detection technique at least one supervisory data processing node periodically transmits a receipt acknowledge data packet to each other data processing node. The supervisory data processing node determines a data processing node has failed upon failure to receive a return acknowledge data packet. This acknowledge data packet preferably includes health data concerning its current health operating status. The supervisory data processing node sends a reset data packet to any failed data processing node determined. If the reset does not return the data processing node to normal operation, then routing data at neighboring data processing nodes is altered to route data packets around the failed node.

Owner:TEXAS INSTR INC

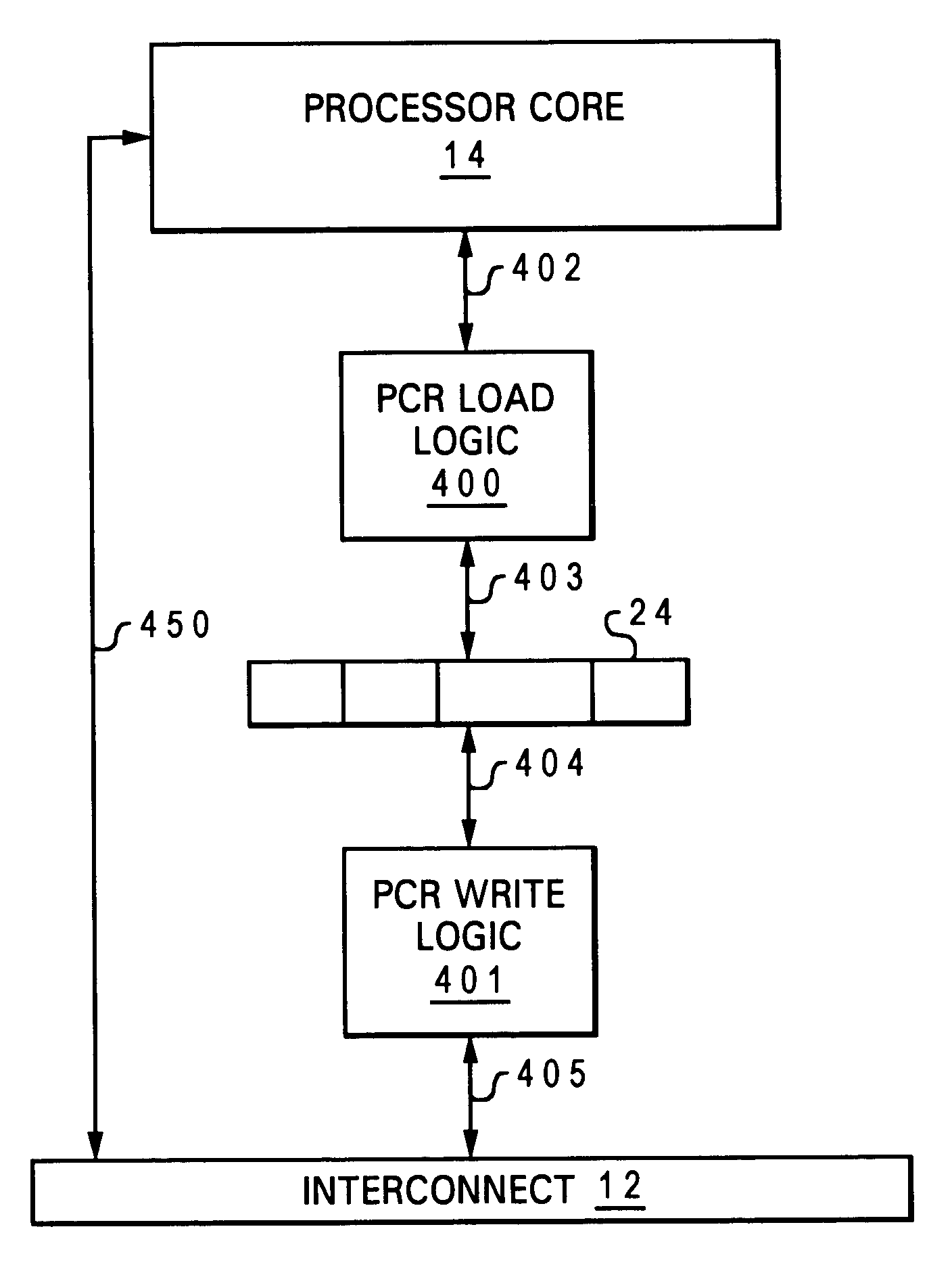

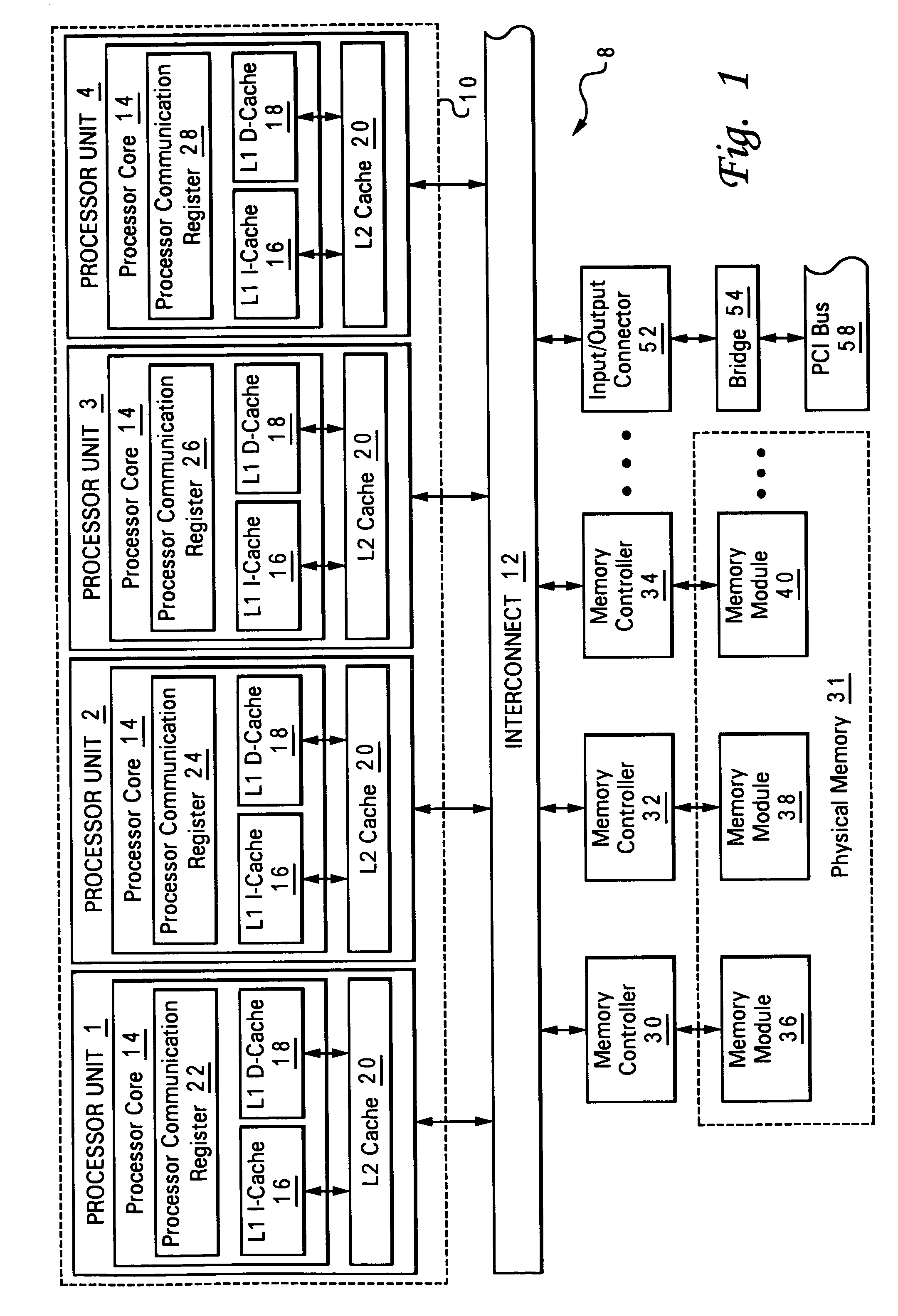

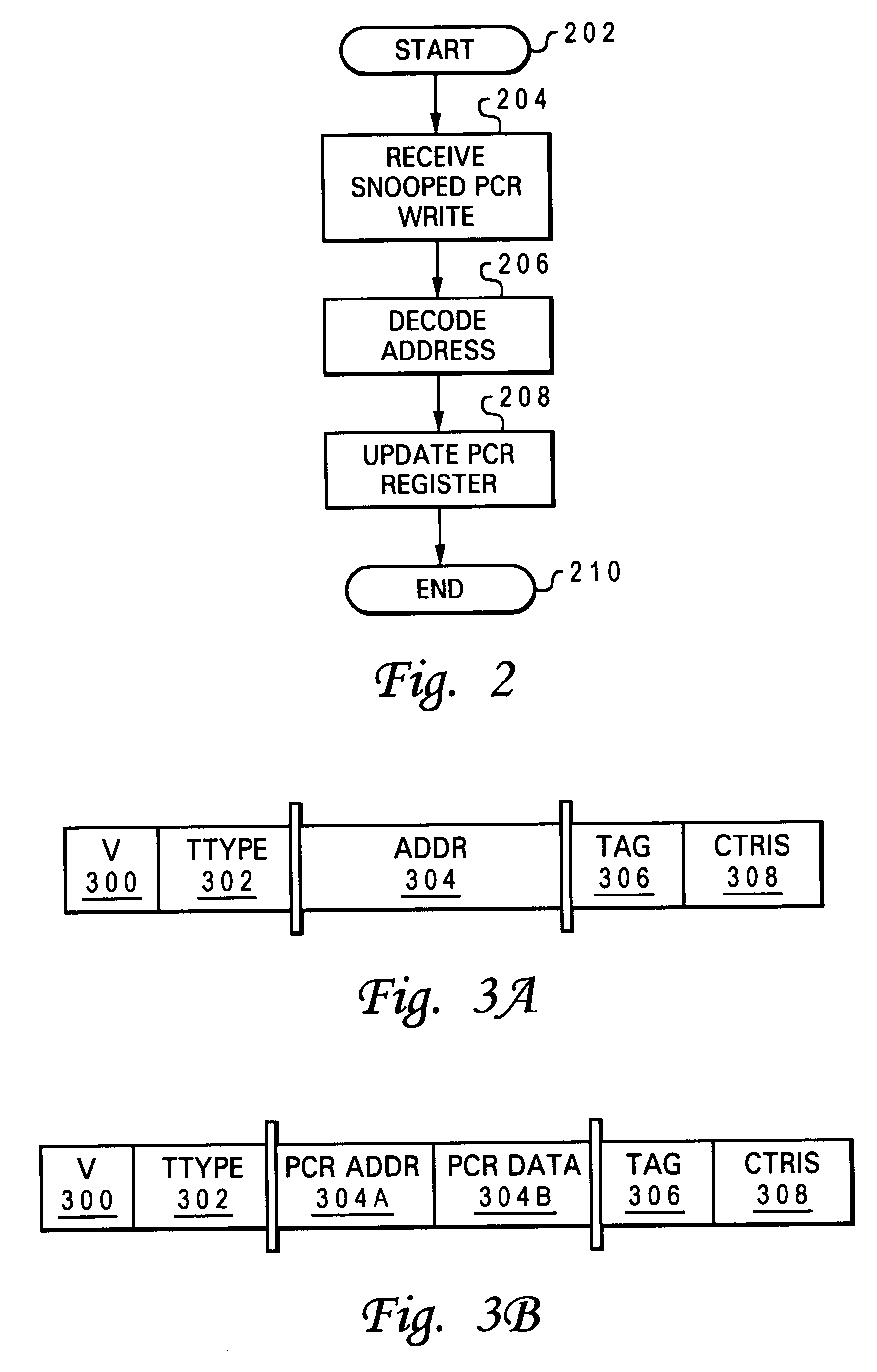

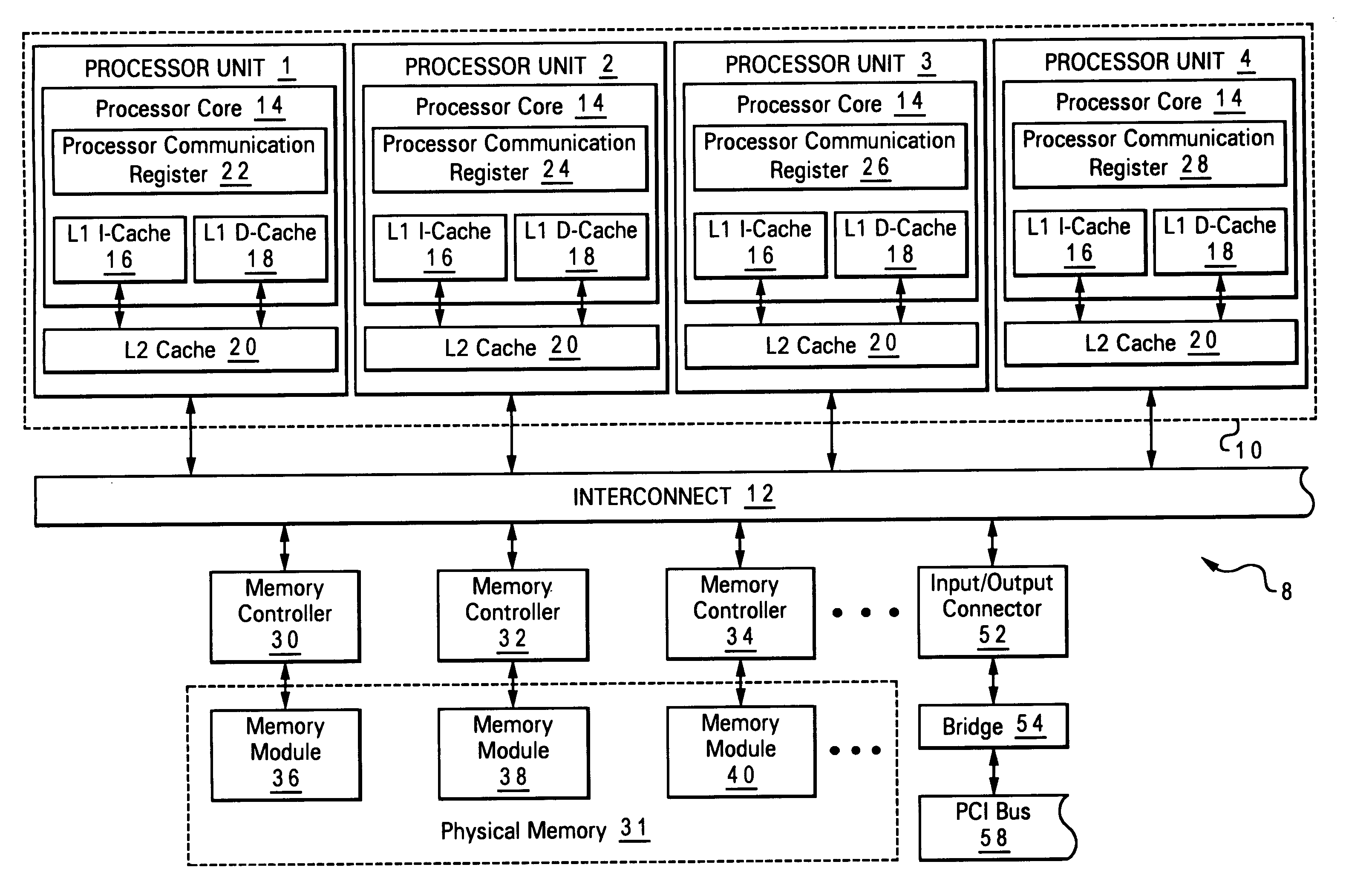

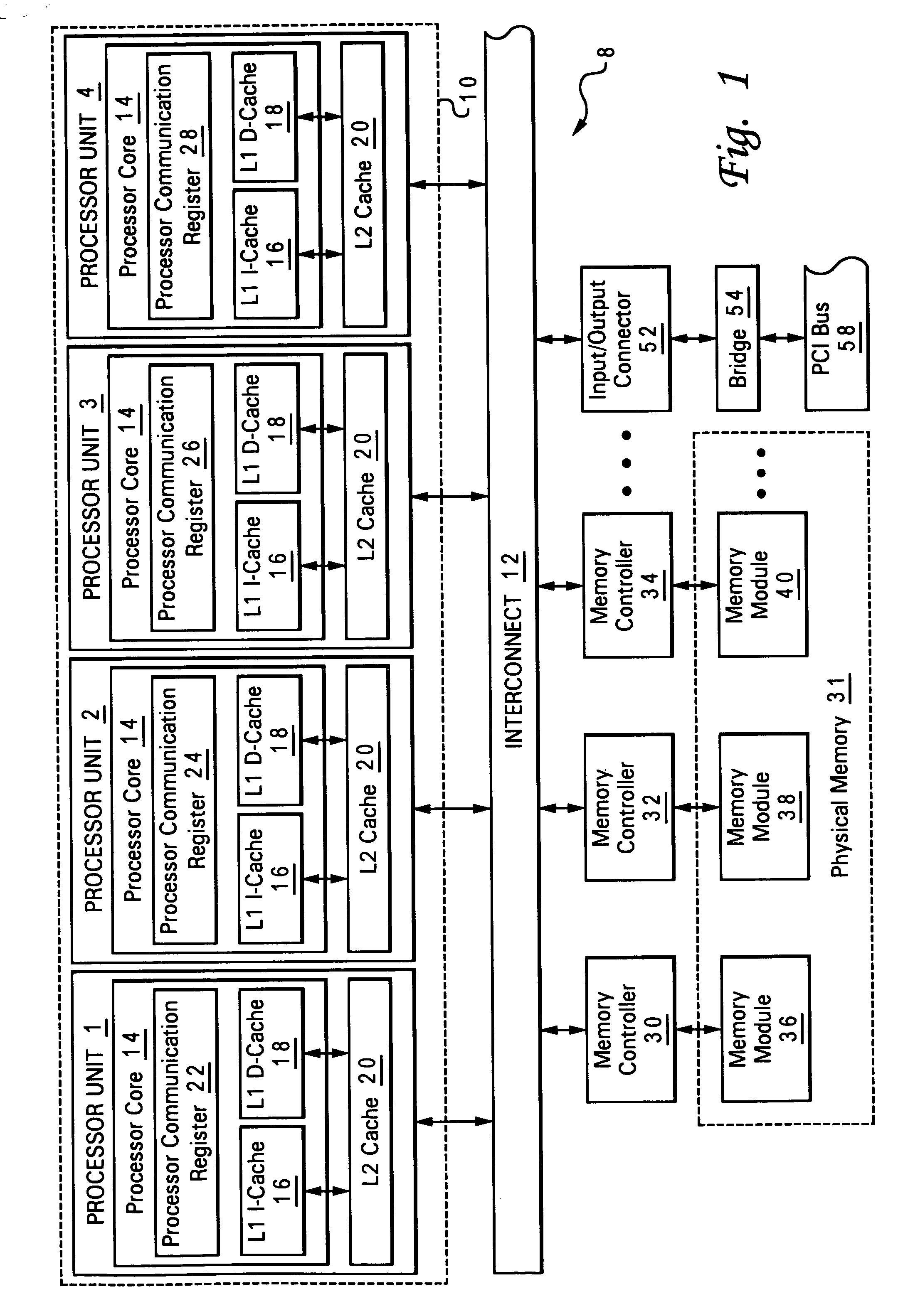

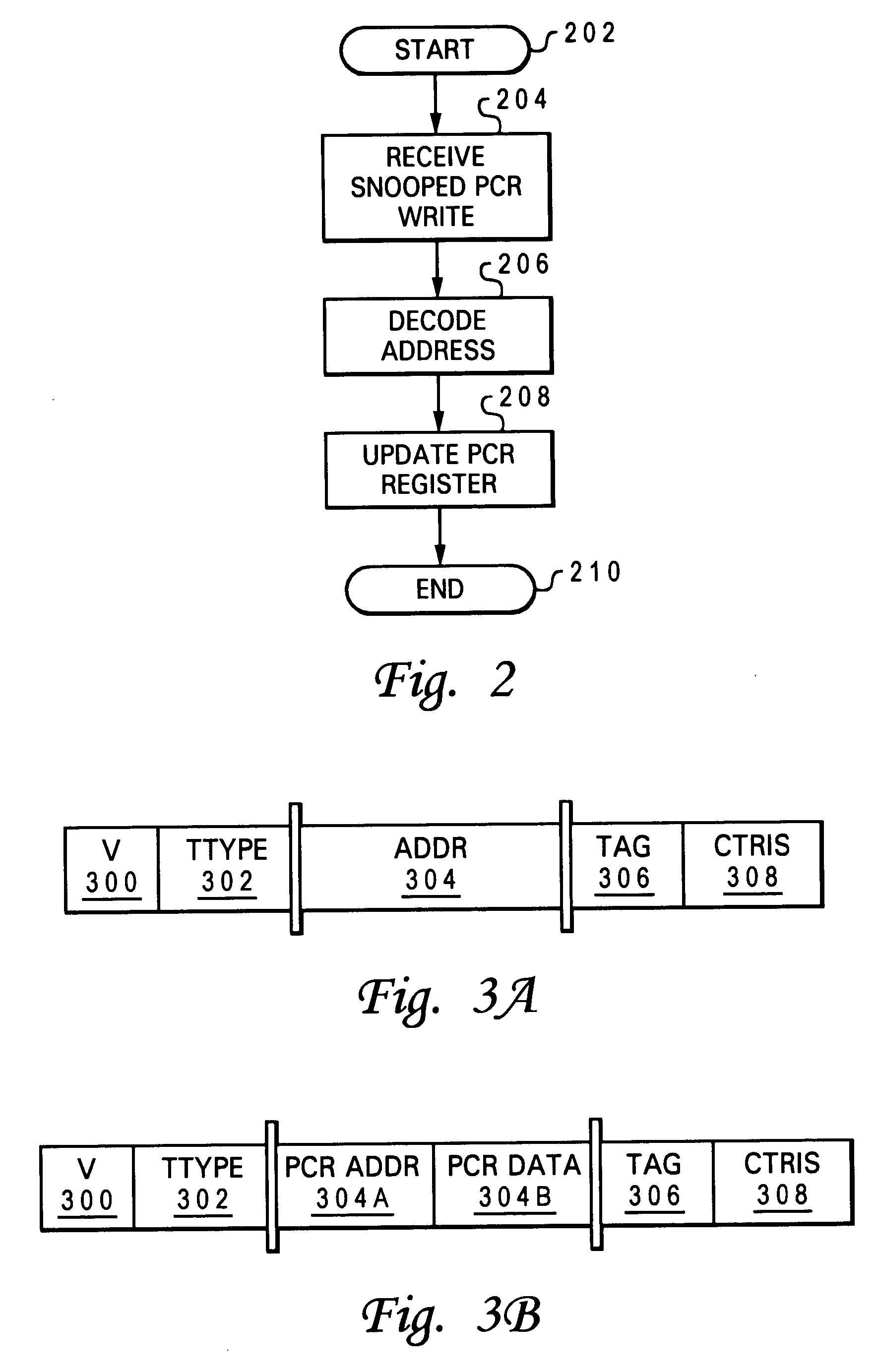

Method and data processing system for microprocessor communication in a cluster-based multi-processor network

InactiveUS7073004B2Fast and efficient update of synchronizationProgram synchronisationMemory adressing/allocation/relocationData processing systemMulti processor

The address tenure for PCR synchronization operations is redefined to support inclusion of the synchronization data within the address tenure. The bits of a particular field within the address tenure (e.g., the address field) are re-allocated to synchronization data, which is known to be small enough to fit within the unused bits. The address tenure is then broadcasted as a normal address operation and is snooped by all of the processors. The snooping logic is designed to recognize regular / normal address tenures and these modified address tenures and respond to a receipt of a modified address tenure by removing the synchronization data stored therein and updating the corresponding register location of the PCR.

Owner:INT BUSINESS MASCH CORP

Method and data processing system for microprocessor communication in a cluster-based multi-processor network

InactiveUS20040215899A1Fast and efficient update of synchronizationProgram synchronisationMemory adressing/allocation/relocationData processing systemProcessor register

The address tenure for PCR synchronization operations is redefined to support inclusion of the synchronization data within the address tenure. The bits of a particular field within the address tenure (e.g., the address field) are re-allocated to synchronization data, which is known to be small enough to fit within the unused bits. The address tenure is then broadcasted as a normal address operation and is snooped by all of the processors. The snooping logic is designed to recognize regular / normal address tenures and these modified address tenures and respond to a receipt of a modified address tenure by removing the synchronization data stored therein and updating the corresponding register location of the PCR.

Owner:IBM CORP

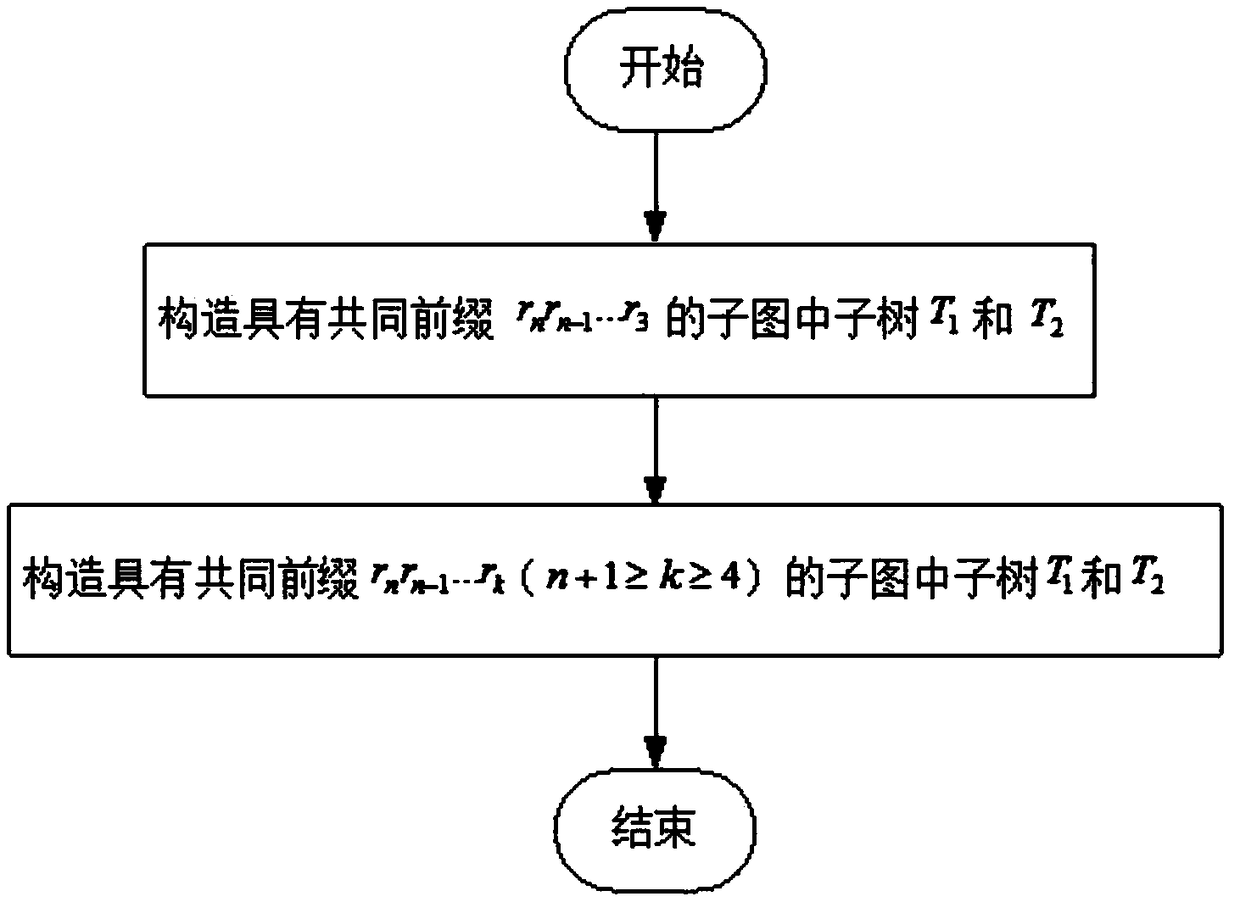

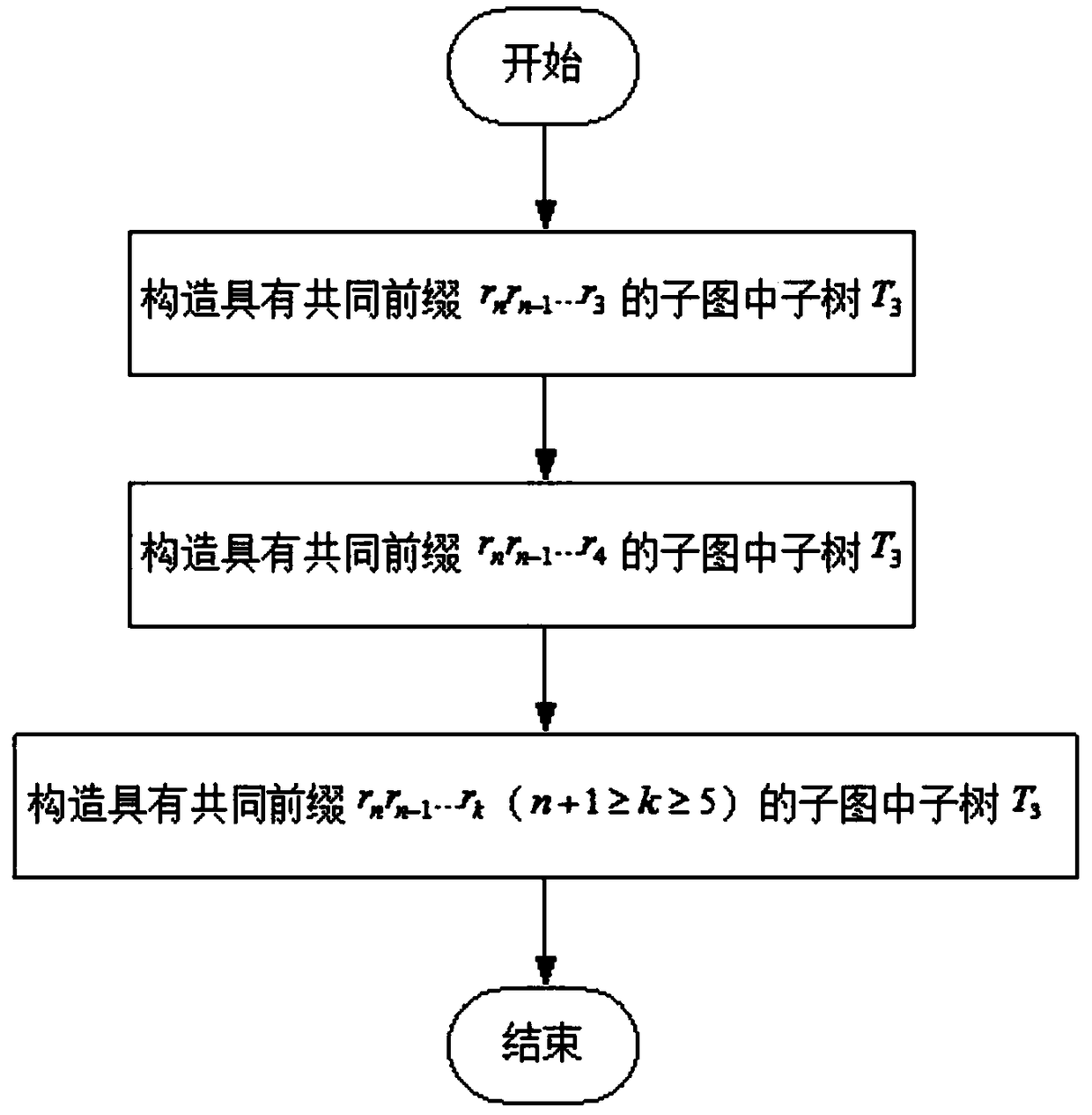

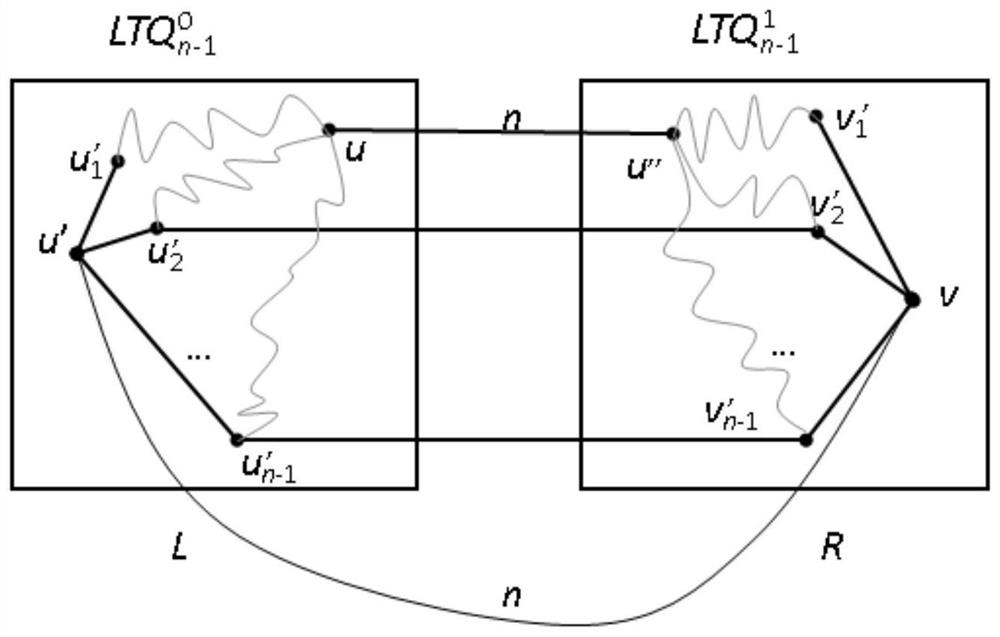

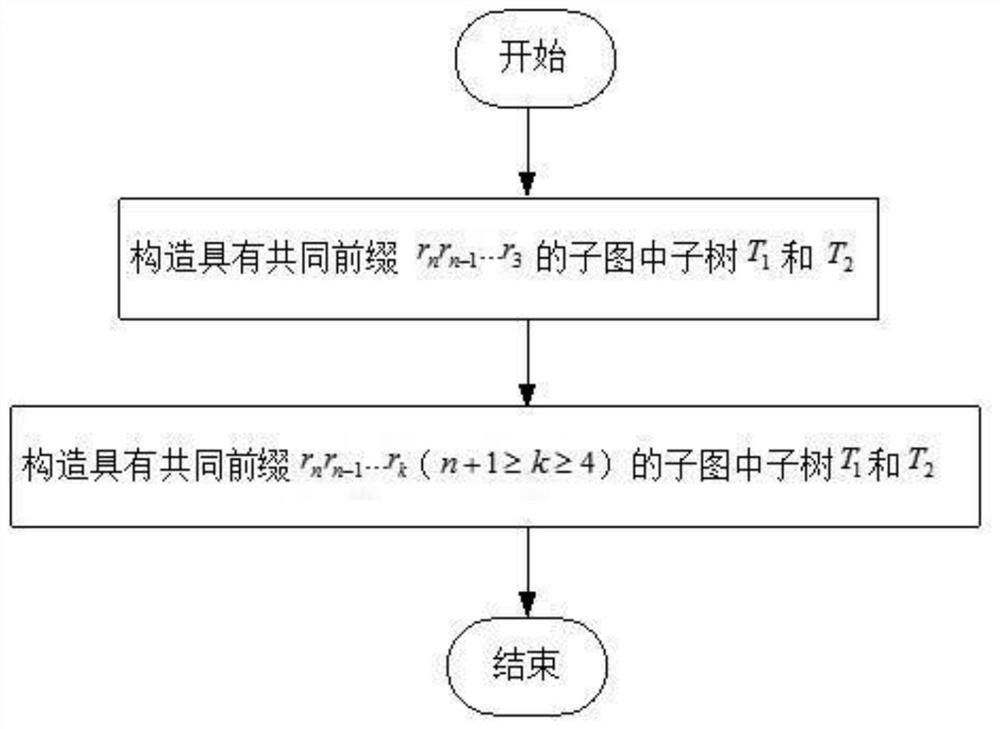

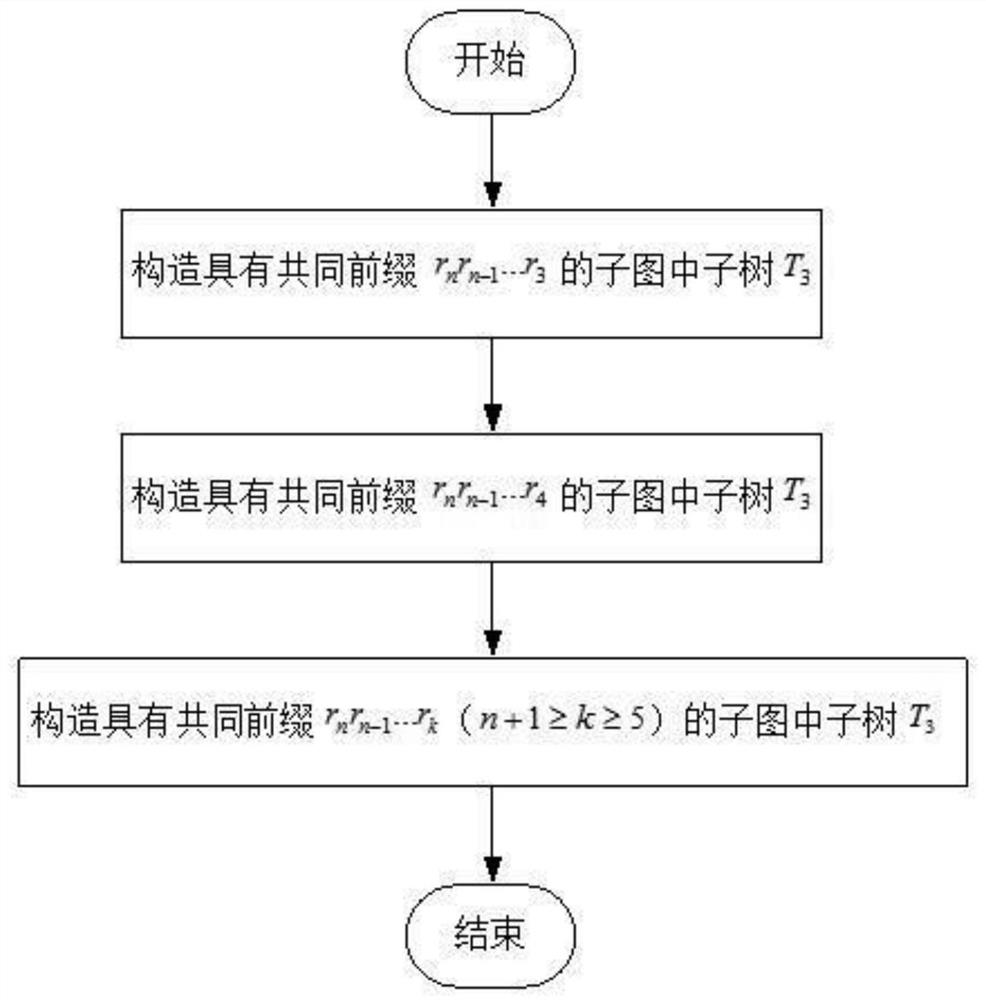

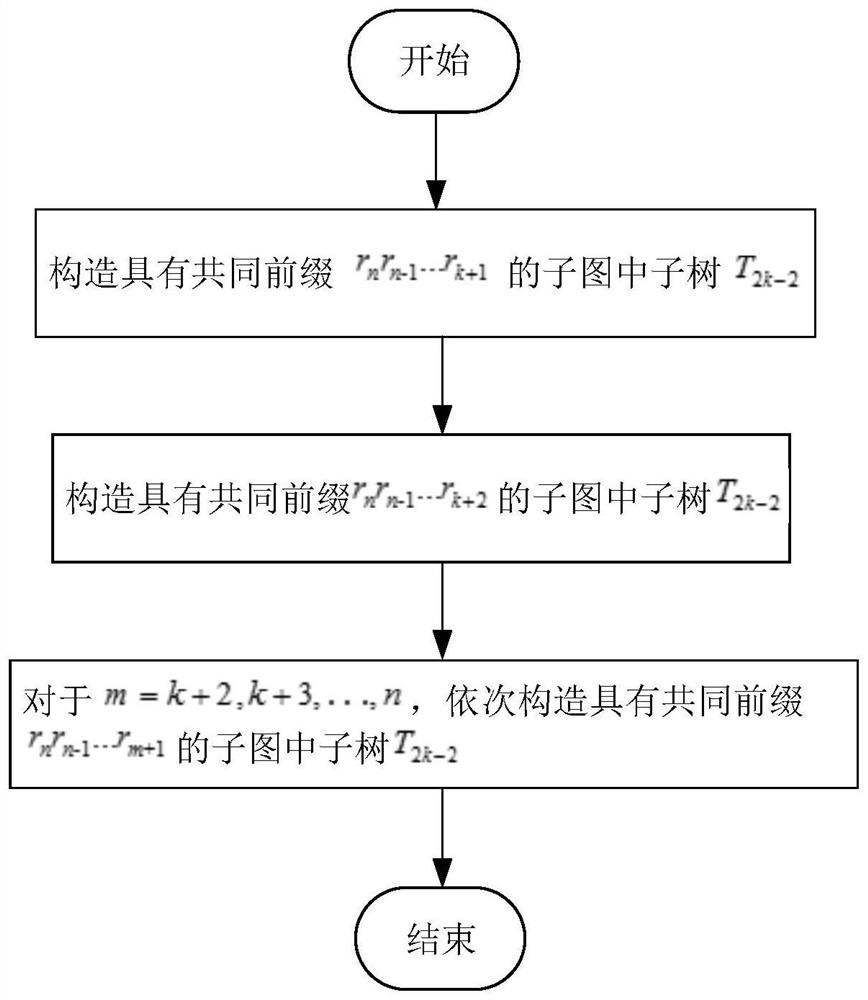

A parallel transmission method of data on a multiprocessor network with an extended cube structure

ActiveCN109165188ALow costReduce overheadDigital computer detailsElectric digital data processingNetwork structureParallel computing

The invention discloses a parallel transmission method of data on a multiprocessor network with an extended cube structure. When a processor is designated as a source processor, the invention can construct a group of edge independent spanning trees with the processor as a center in parallel, so that 2n-1 paths where the edges do not intersect exist between the processors and any other processors.Data can be decomposed to the 2n-1 paths without interfering with each other. According to any given vertex, the method can construct 2n-1 edge-independent spanning trees in parallel. There are 2n-1 paths whose sides do not intersect between the root vertex and any other vertex. Each tree can be constructed independently. The method has better topology property, can greatly reduce hardware cost and communication cost, improve the balance of communication cost, and has a wide market prospect in popularization of an interconnection network structure.

Owner:ZHANGJIAGANG INST OF IND TECH SOOCHOW UNIV +1

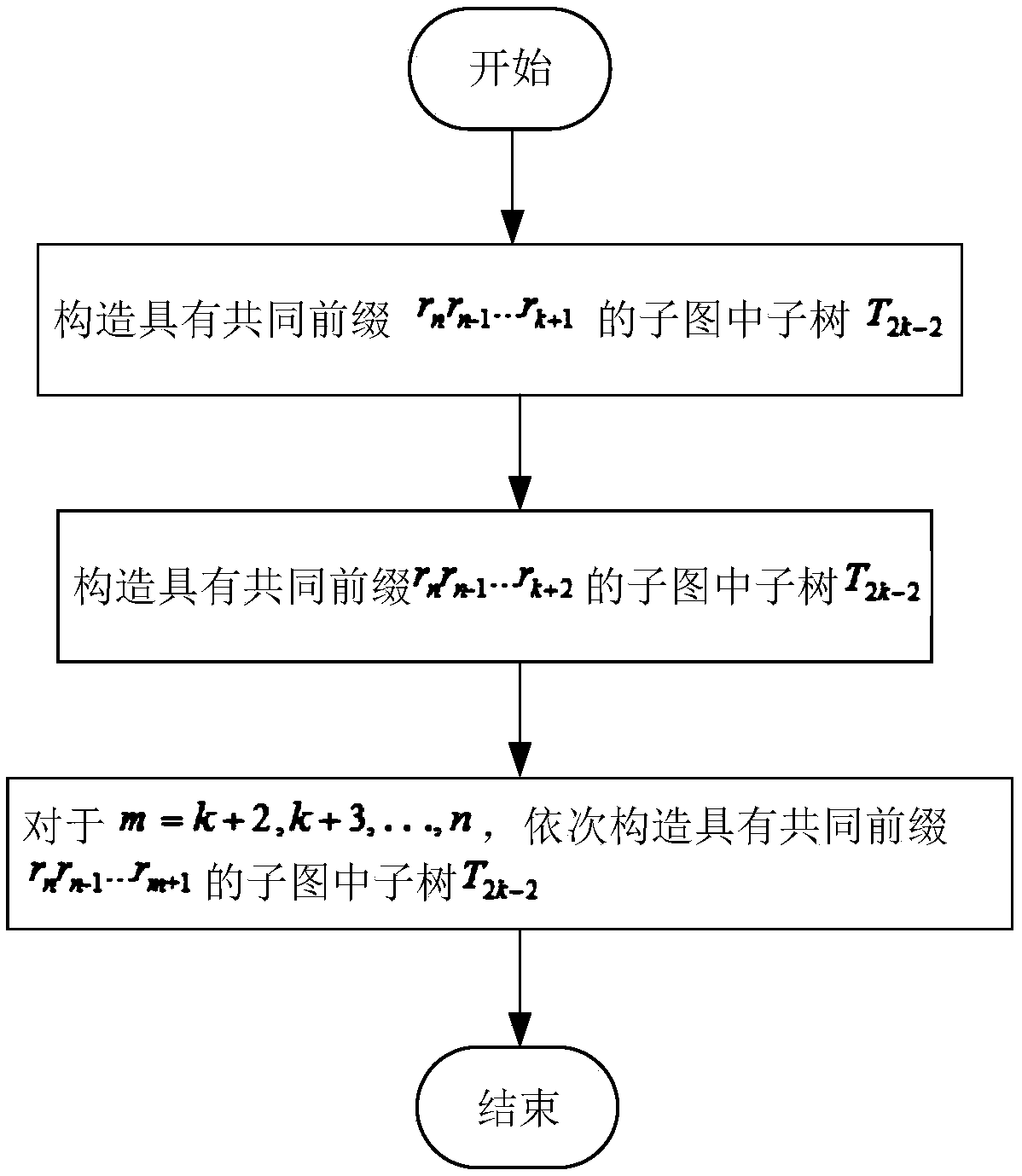

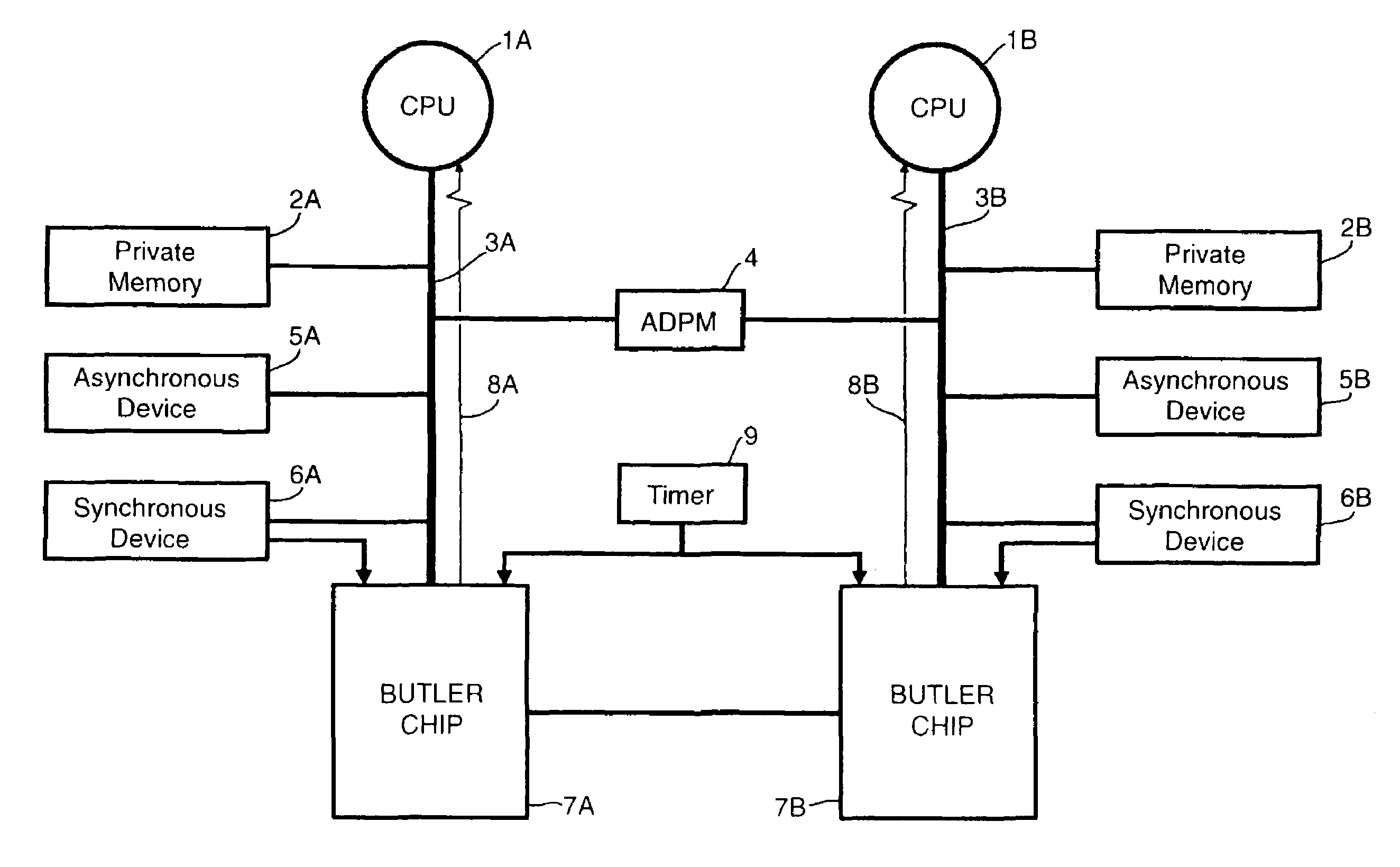

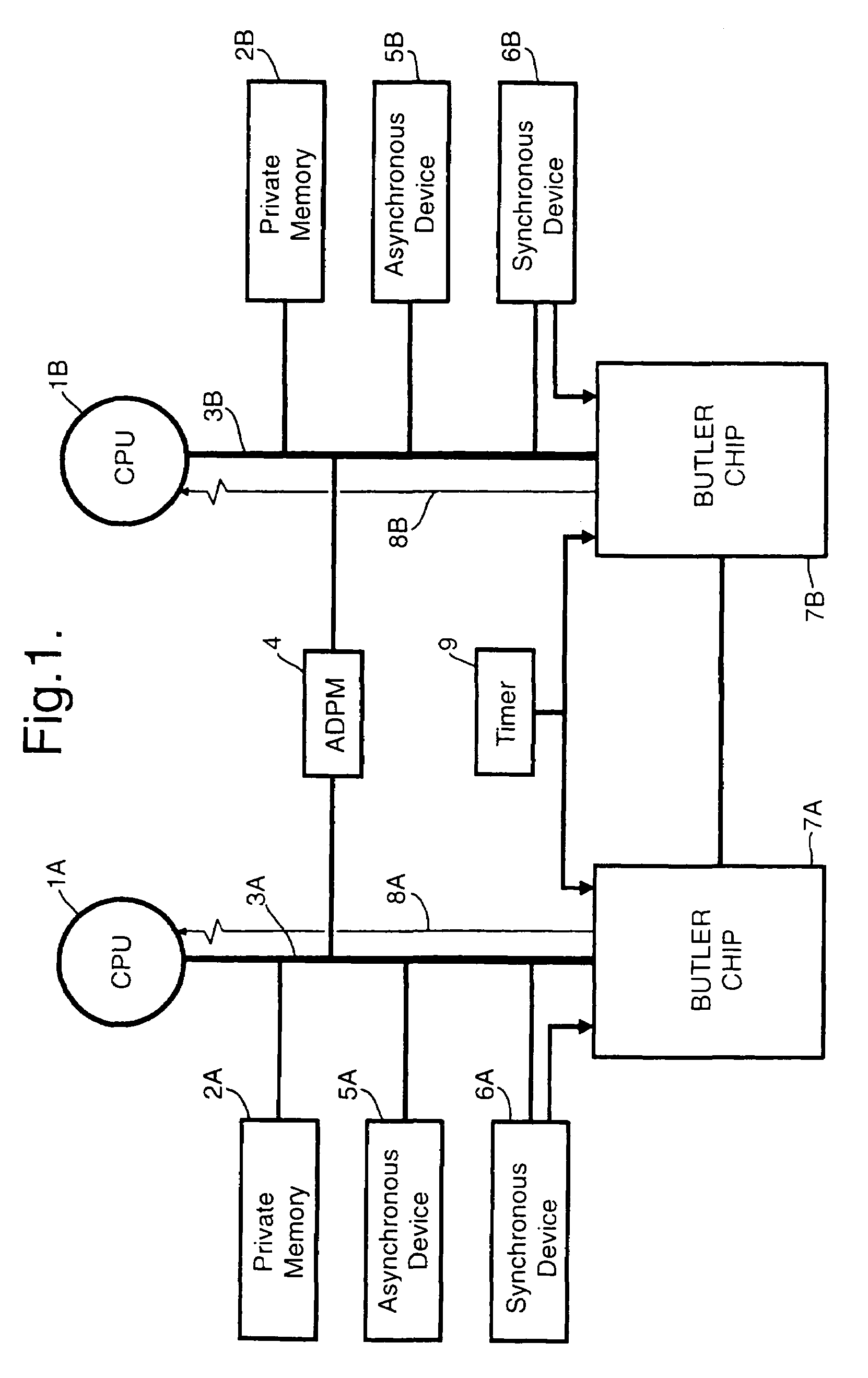

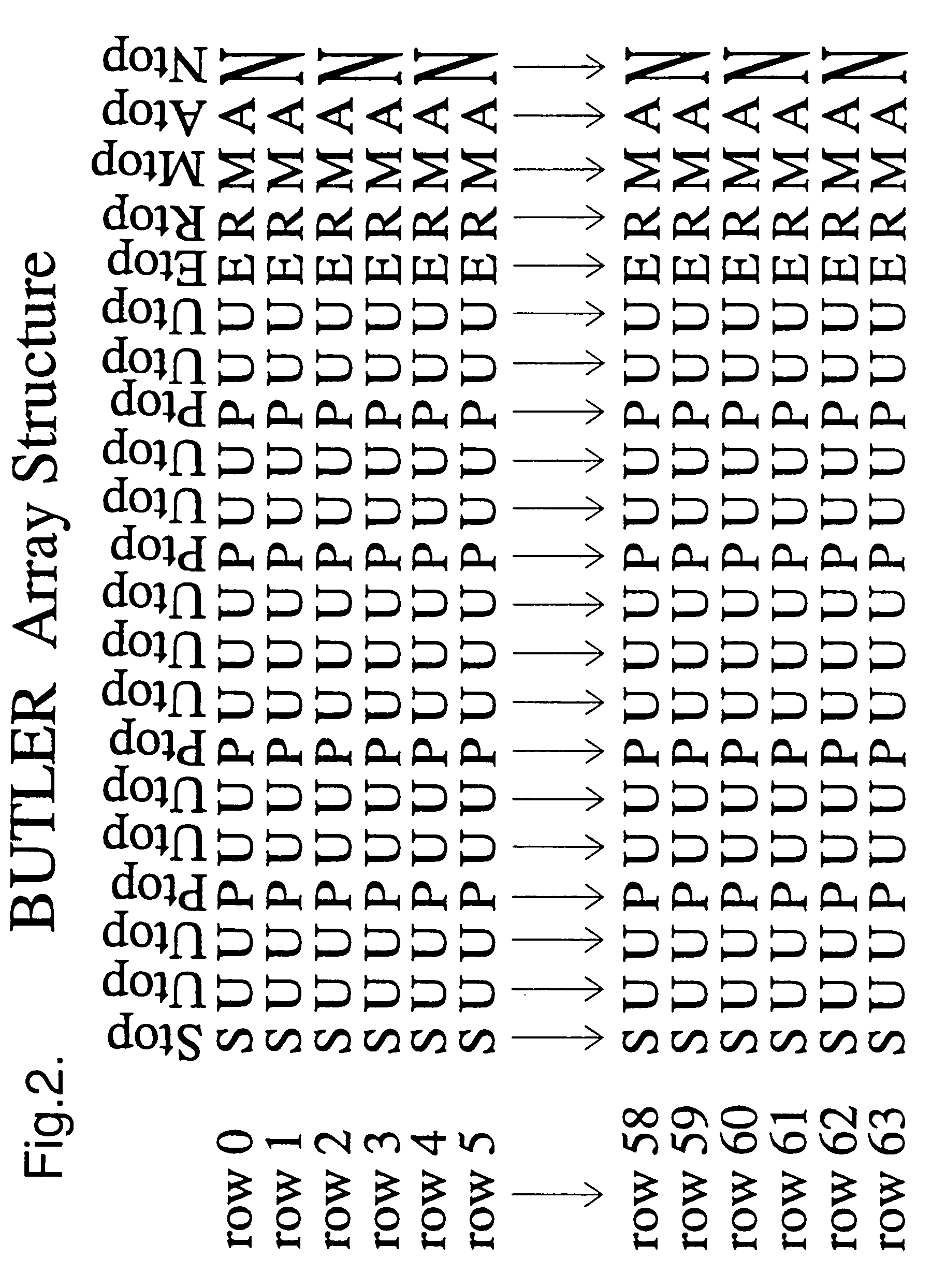

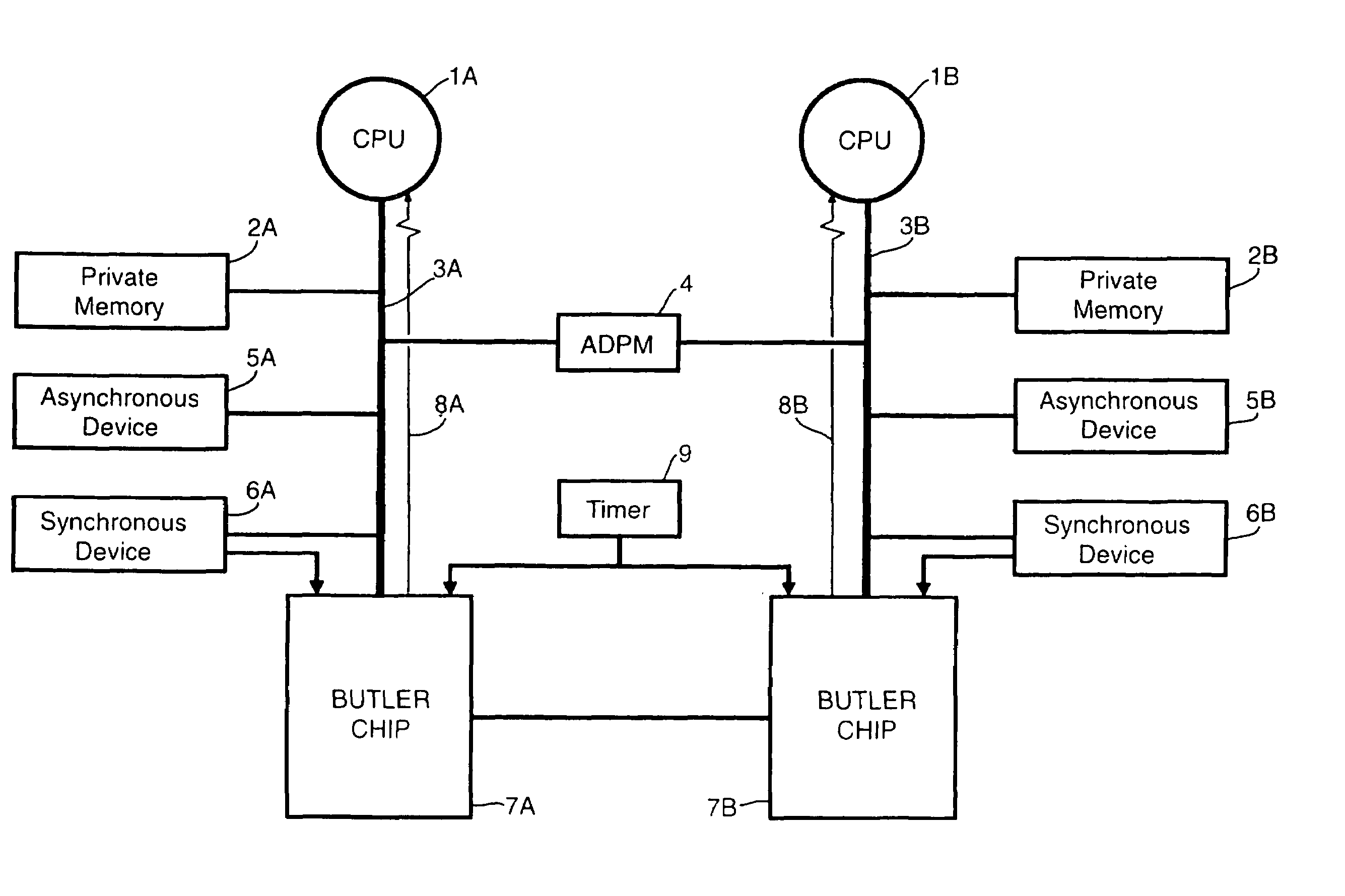

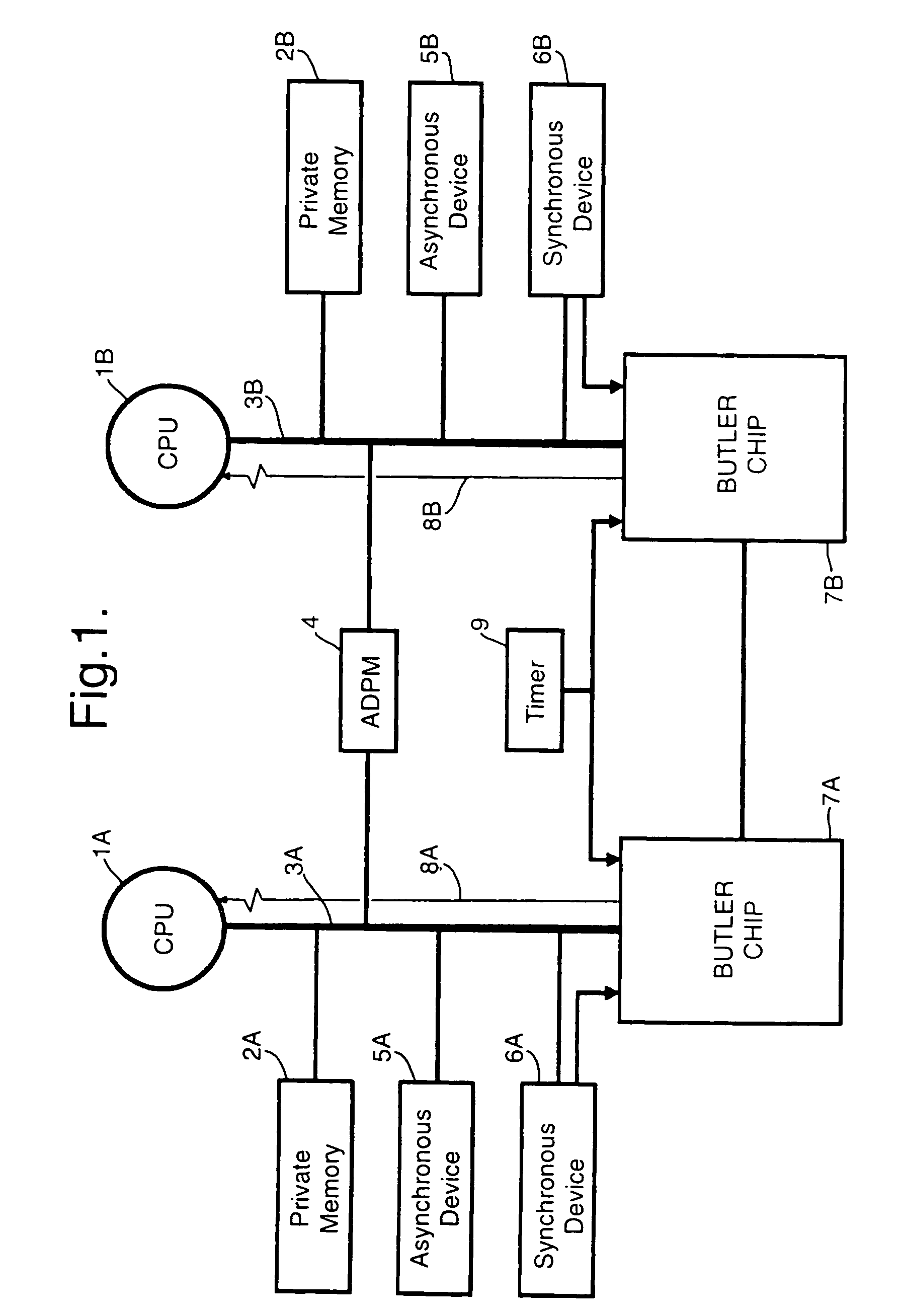

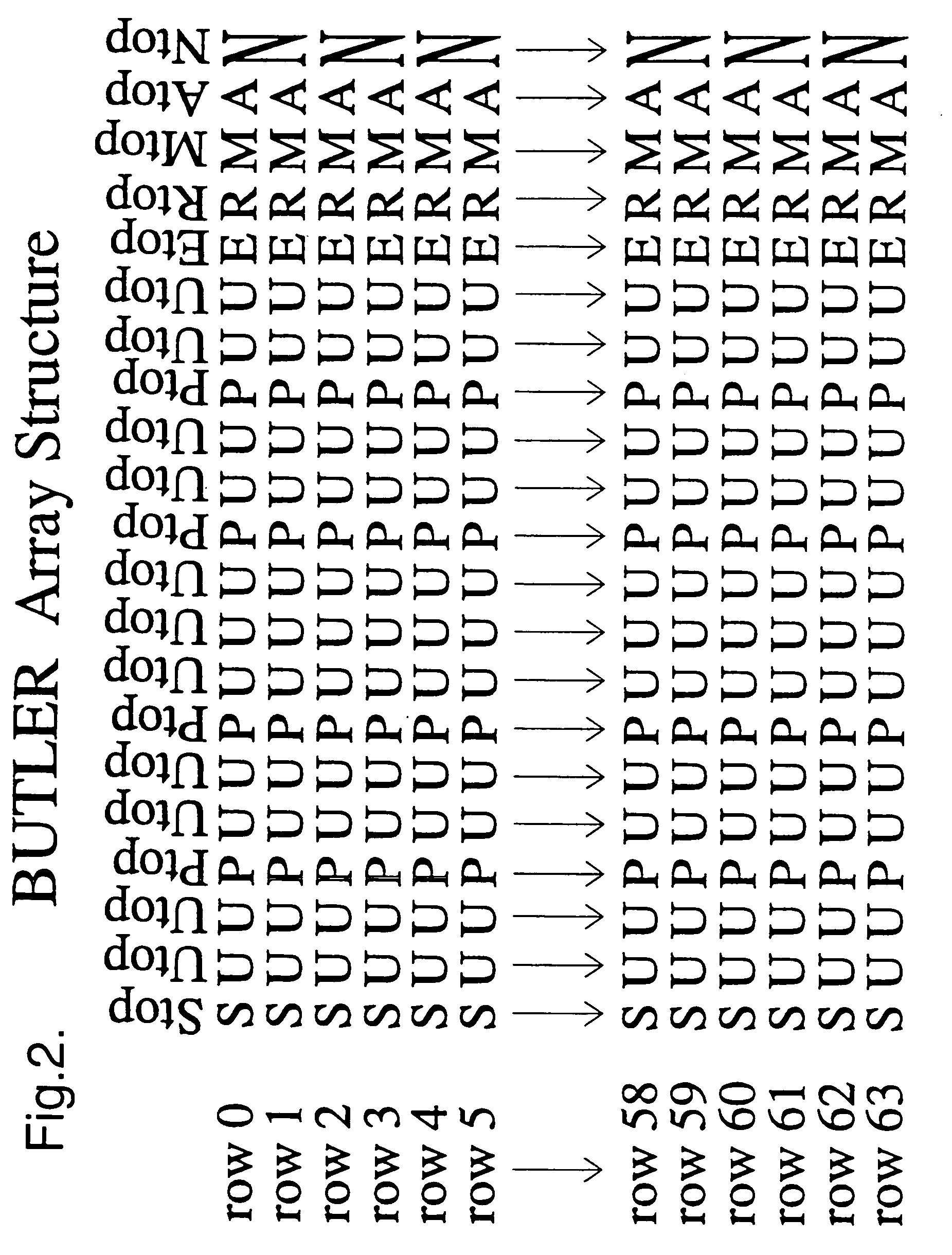

Integrated circuits for multi-tasking support in single or multiple processor networks

InactiveUS6971099B1Eliminate needEasy to implementSingle instruction multiple data multiprocessorsProgram initiation/switchingComputer architectureIntegrated circuit layout

An integrated circuit (7A) for multitasking support for processing unit (1A) holds control variables for each task (or activity) to run on its associated processor (1A) and identifies the next task that should run. The circuit (7A) employs level-driven, clock free ripple logic and is configured as a two dimensional array of “tiles”, each tile being composed of simple logic gates and performing a dedicated function. The circuit has particular application to asynchronous multiple processor networks.

Owner:MBDA UK

Data internal storage managing system and method, and related multiprocessor network

InactiveCN1193296CMemory adressing/allocation/relocationDigital computer detailsParallel computingMultiprocessor network

The present invention relates to a system and a method of memory management of data consistency relating to a main memory (4) accessible by at least two processors (1,2), as well as an associated multiprocessor network. The management system comprises an assembly for management of shared access of the processors to a common area (9) of the main memory, referred to as the exchanges area, at least one copy module (12,13) intended for performing a data copy between at least one first processor comprising at least one cache memory and the exchanges area and at least one transfer module (12,13) intended for performing a transfer of data between the exchanges area and at least one second processor. Triggering means controlled by the second processors trigger the copy modules and transfer modules when the first processors submit requests involving transfers of data between the first and second processors.

Owner:THOMSON LICENSING SA

Integrated circuits for multi-tasking support in single or multiple processor networks

InactiveUS6993766B2Eliminate needEasy to implementSingle instruction multiple data multiprocessorsProgram initiation/switchingComputer architectureIntegrated circuit layout

An integrated circuit (7A) for multitasking support for processing unit (1A) holds control variables for each task (or activity) to run on its associated processor (1A) and identifies the next task that should run. The circuit (7A) employs level-driven, clock free ripple logic and is configured as a two dimensional array of “tiles”, each tile being composed of simple logic gates and performing a dedicated function. The circuit has particular application to asynchronous multiple processor networks.

Owner:MBDA UK

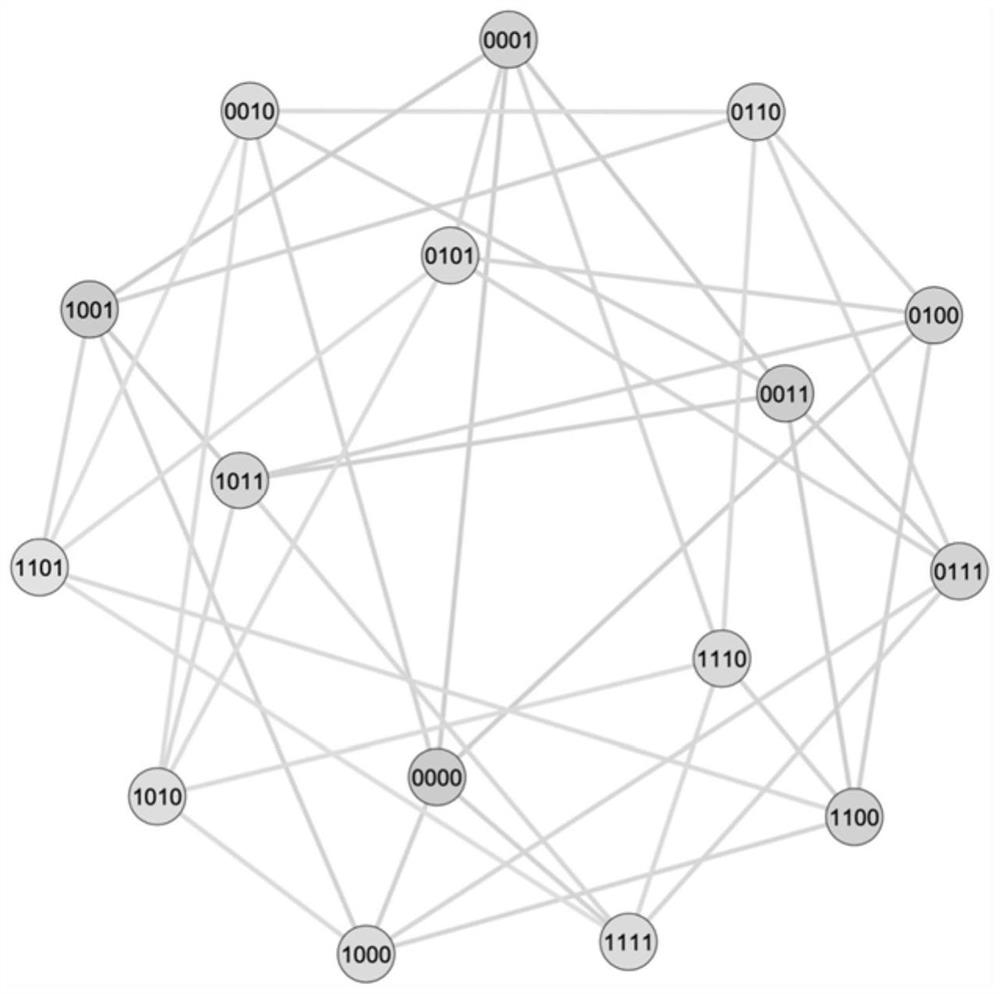

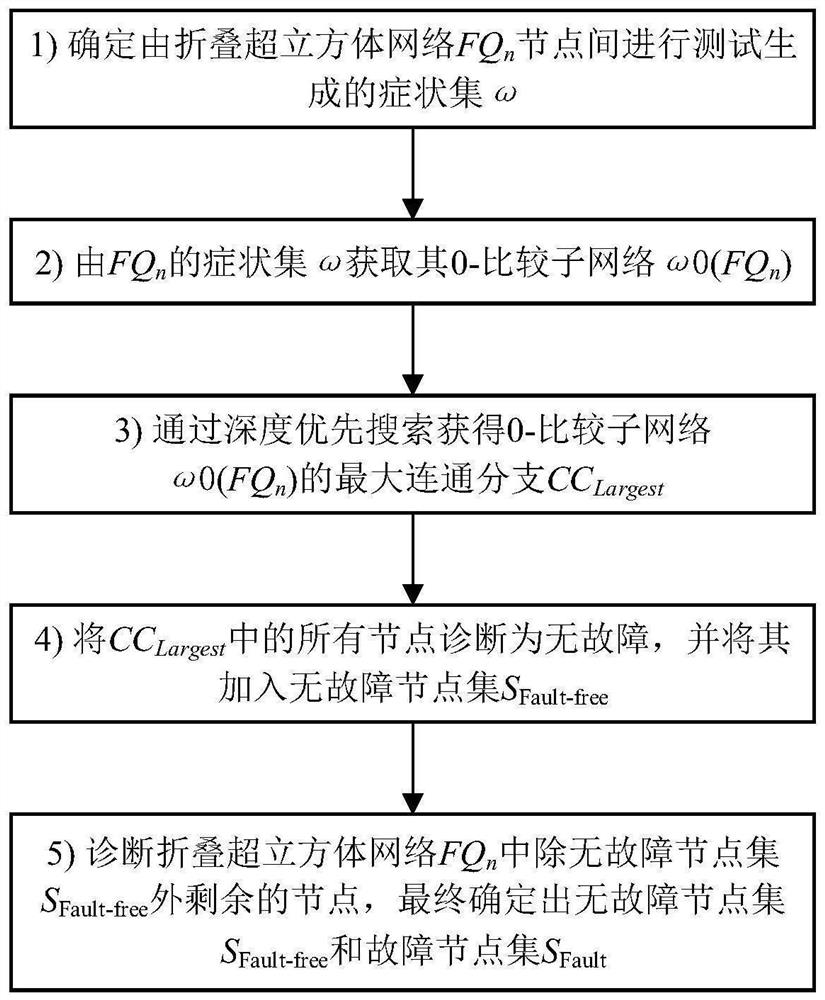

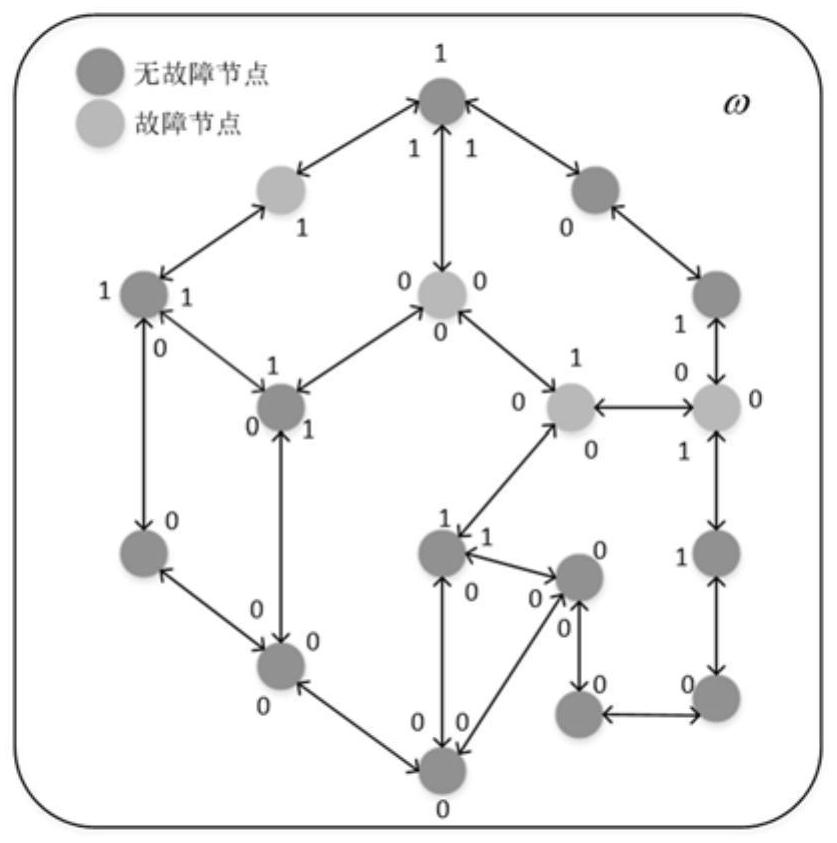

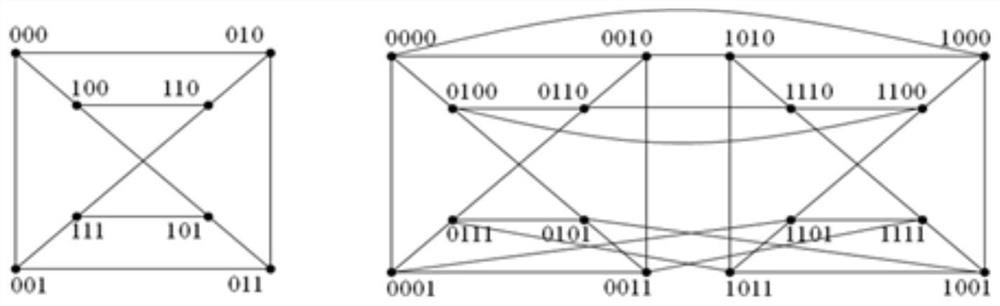

Multiprocessor network fault node diagnosis method based on folding hypercube

ActiveCN114448834AImprove fault diagnosis abilityTransmissionInformation technology support systemDepth-first searchMultiprocessor network

The invention discloses a multiprocessor network fault node diagnosis method based on a folding hypercube. The multiprocessor network fault node diagnosis method comprises the following steps: S1, determining a symptom set omega generated by testing between folding hypercube network FQn nodes; s2, generating a 0-comparison sub-network omega0 (FQn) according to the symptom set omega of the FQn; s3, the maximum connected branch CCLarge of the 0-comparison sub-network omega0 (FQn) is obtained through depth-first search; s4, diagnosing all the nodes in the CCLarge as no fault, and adding the nodes in the CCLarge into a fault-free node set SFault-free; and S5, diagnosing the remaining nodes in the folded hypercube network FQn except the fault-free node set SFault-free, and obtaining the final fault-free node set SFault-free and the fault node set SFault. According to the method, the network topology structure property of the folding hypercube network FQn is utilized, and the fault diagnosis capability of the FQn is greatly enhanced under the condition that a small number of nodes are misdiagnosed.

Owner:FUJIAN NORMAL UNIV

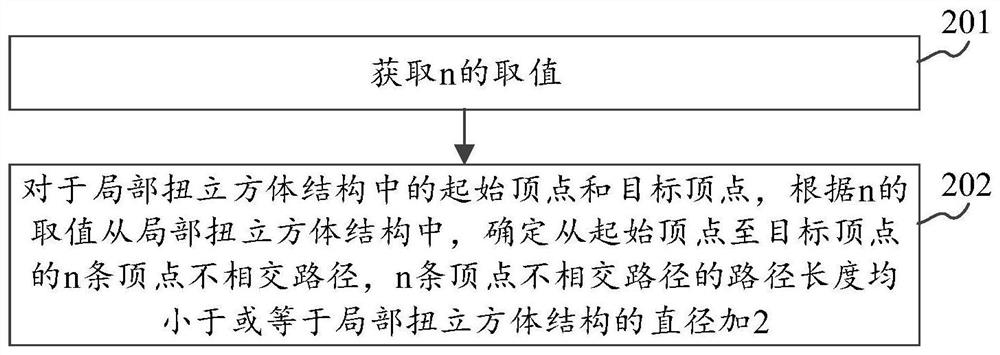

Method and device for determining processing path of multiprocessor network and storage medium

ActiveCN113079094AFast transmissionResolution delay is largeData switching networksComputational sciencePathPing

The invention relates to a method and device for determining a processing path of a multiprocessor network and a storage medium, and belongs to the technical field of computers. The method comprises the steps: for a starting vertex and a target vertex in an n-dimensional local twisted cube structure, determining, from the local twisted cube structure according to the value of n, n vertex disjoint paths from the starting vertex to the target vertex, wherein the path lengths of the n vertex disjoint paths are lower than or equal to the sum of the diameter of the local twisted cube structure and 2. The problem that data delay is large due to the fact that the longest path in n vertex disjoint path groups obtained through an existing vertex disjoint path construction algorithm is n + 1 can be solved. As the longest path in the n vertex disjoint path groups can be shortened to the diameter of the local twisted cube structure plus 2, the path length can be shortened, and the data transmission speed can be improved.

Owner:SUZHOU KEDA TECH +1

Discovery of a virtual topology in a multi-tasking multi-processor environment

InactiveUS20090217007A1Interprogram communicationDigital computer detailsComputer networkMulti processor

A computer program product, apparatus and method for identifying processors in a multi-tasking multiprocessor network, the computer program product including a tangible storage medium readable by a processing circuit and storing instructions for execution by the processing circuit for performing a method including storing a service record for a port to which an LID has been assigned, retrieving service records for nodes to which channel paths may connect, retrieving path records that provide address destinations for the nodes identified in the service records, initiating channel initialization for the channel paths defined for the port and removing the service record for the port.

Owner:IBM CORP

Parallel Data Transmission Method on Extended Cube Structure Multiprocessor Network

ActiveCN109165188BLow costReduce overheadDigital computer detailsElectric digital data processingComputational scienceTree root

Owner:ZHANGJIAGANG INST OF IND TECH SOOCHOW UNIV +1

Maintaining memory checkpoints across a cluster of computing nodes

ActiveUS7856421B2Digital data processing detailsError detection/correctionMulti processorSoftware fault

A method and system for increasing reliability and availability of a multi-processor network. A system includes a network with at least two nodes, with each node comprising a multi-processor unit (mpu) and memory. The mpu includes one or more processors and a wiretap unit. The wiretap unit and the memory included in the node are coupled to the processors in the node. The wiretap unit is configured to monitor memory accesses of the processors and convey data indicative of such accesses to a second node. The second node maintains a replica of memory in the first node, and is configured to undo modifications to the memory if needed. In the event of a hardware or software fault, the nodes are configured to restart the application on another node.

Owner:ORACLE INT CORP