Method of preparing an integrated circuit die for imaging

A technology of integrated circuits and bare chips, which is applied in the field of inspection and analysis of integrated circuits, and can solve the problems of difficult extraction of circuit layout information and easy errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

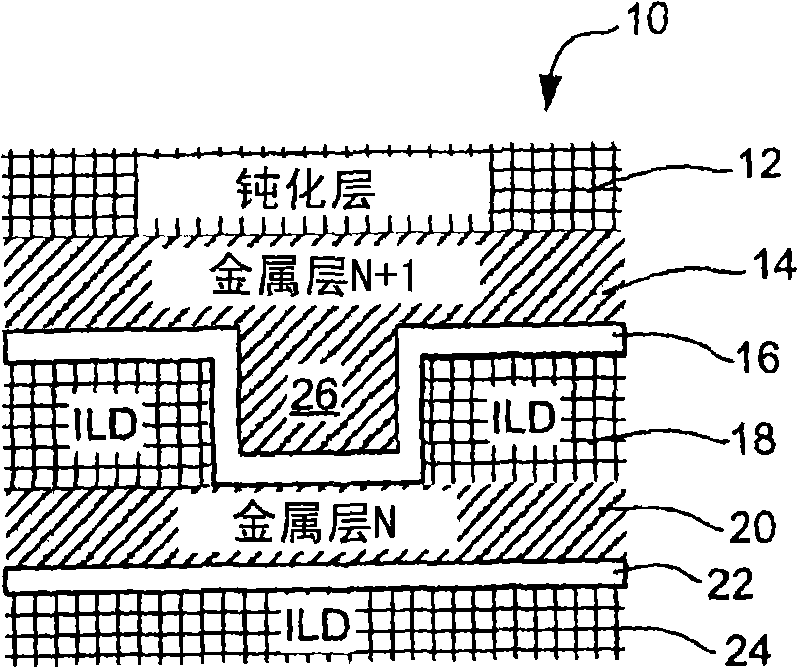

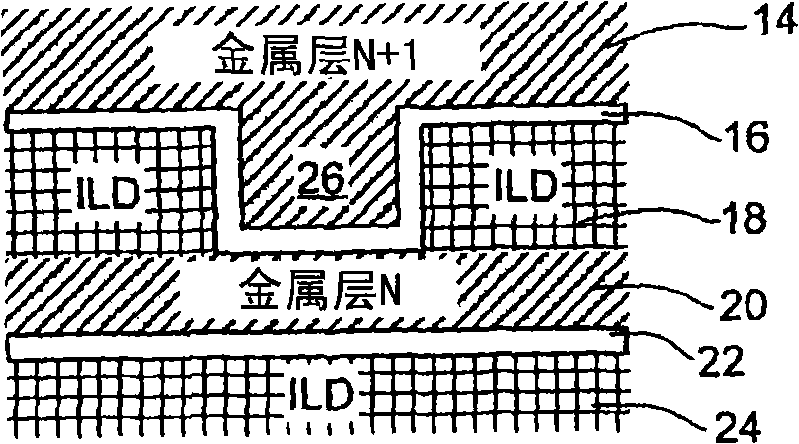

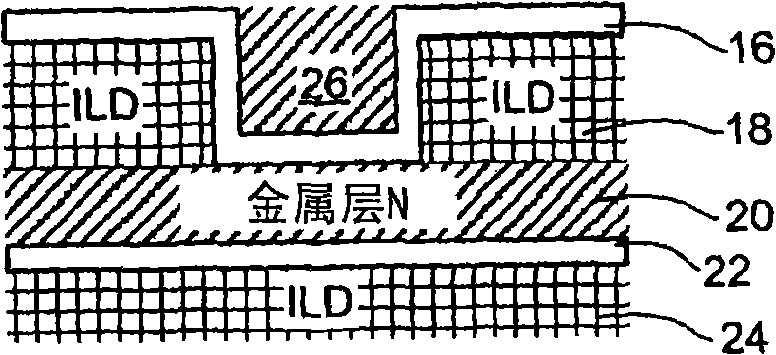

[0020] The present invention provides methods of preparing integrated circuit dies for imaging which are useful for preparing integrated circuit dies made by any process in which the metal lines and vias of the integrated circuit are formed with Made of the same metal. The method described above is very useful for integrated circuits made in an all-copper or all-aluminum process. However, the process is equally useful for making aluminum / tungsten integrated circuits traditionally used for imaging. According to the method described above, after exposing the metal layer of the integrated circuit, all the metal lines of the metal layer are etched away leaving the barrier layer material. When an image is taken with a scanning electron microscope, the barrier material appears in a first color, typically a light gray. If the chip is a copper / copper or aluminum / aluminum structure, the metal lines are etched away and the vias are also etched away, leaving a barrier layer surrounding...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap