Reed-Solomon decoder with low hardware spending

A hardware overhead and decoder technology, applied in the field of Reed-Solomon decoders, can solve complex problems, achieve the effects of reducing chip area and power consumption, optimizing hardware implementation complexity, and reducing hardware complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

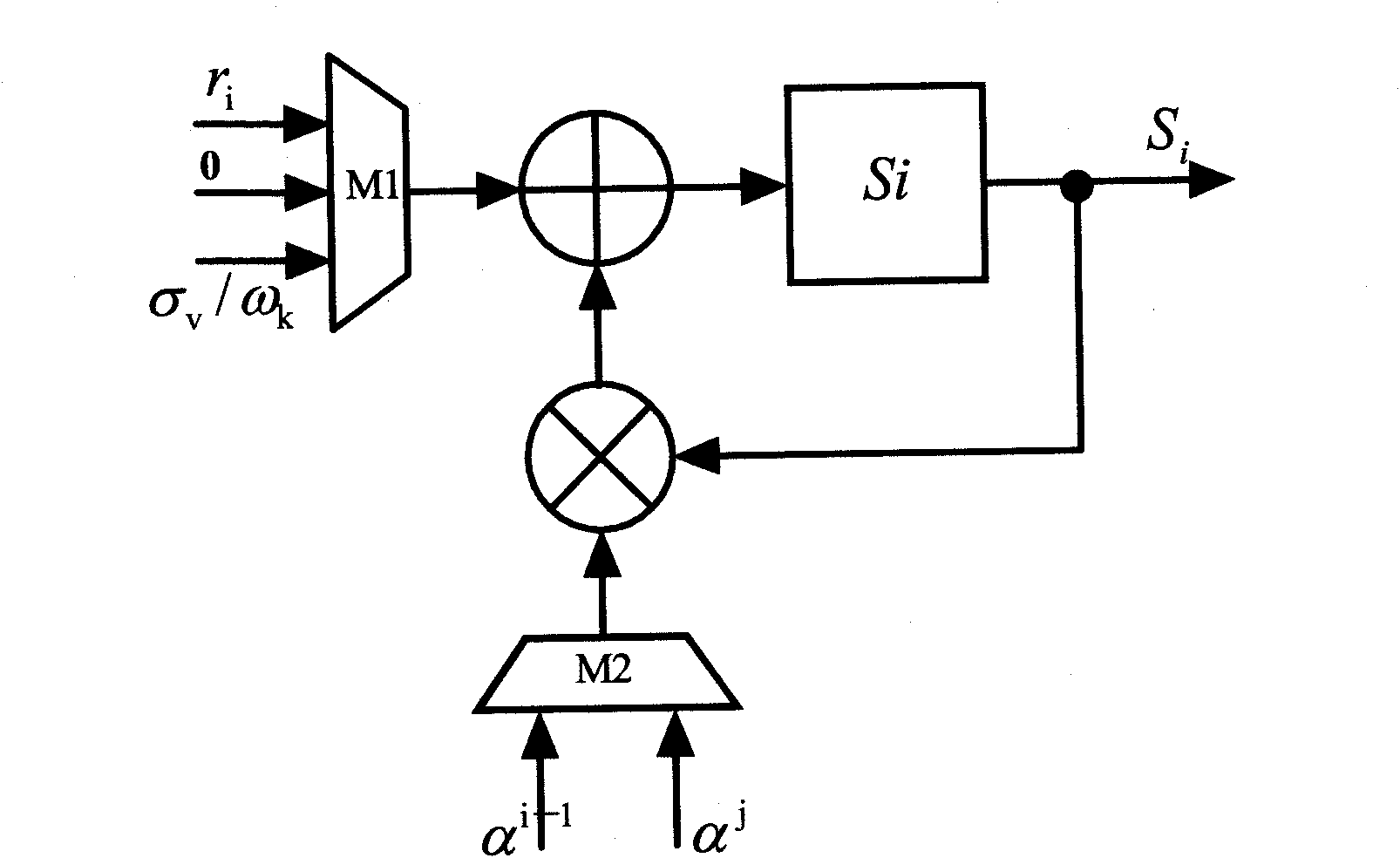

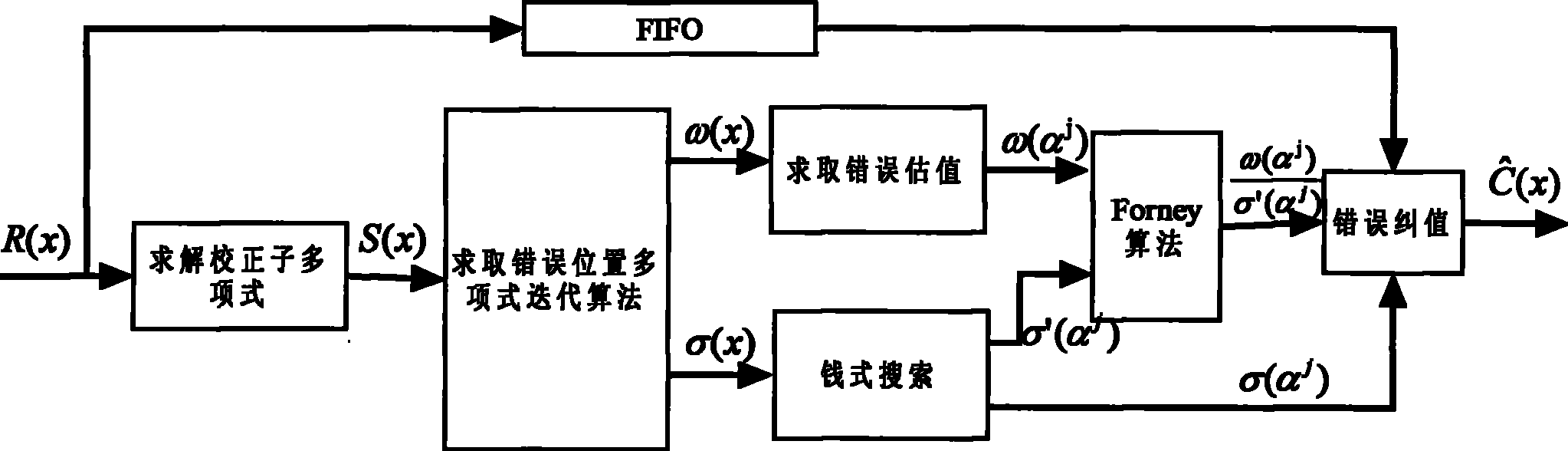

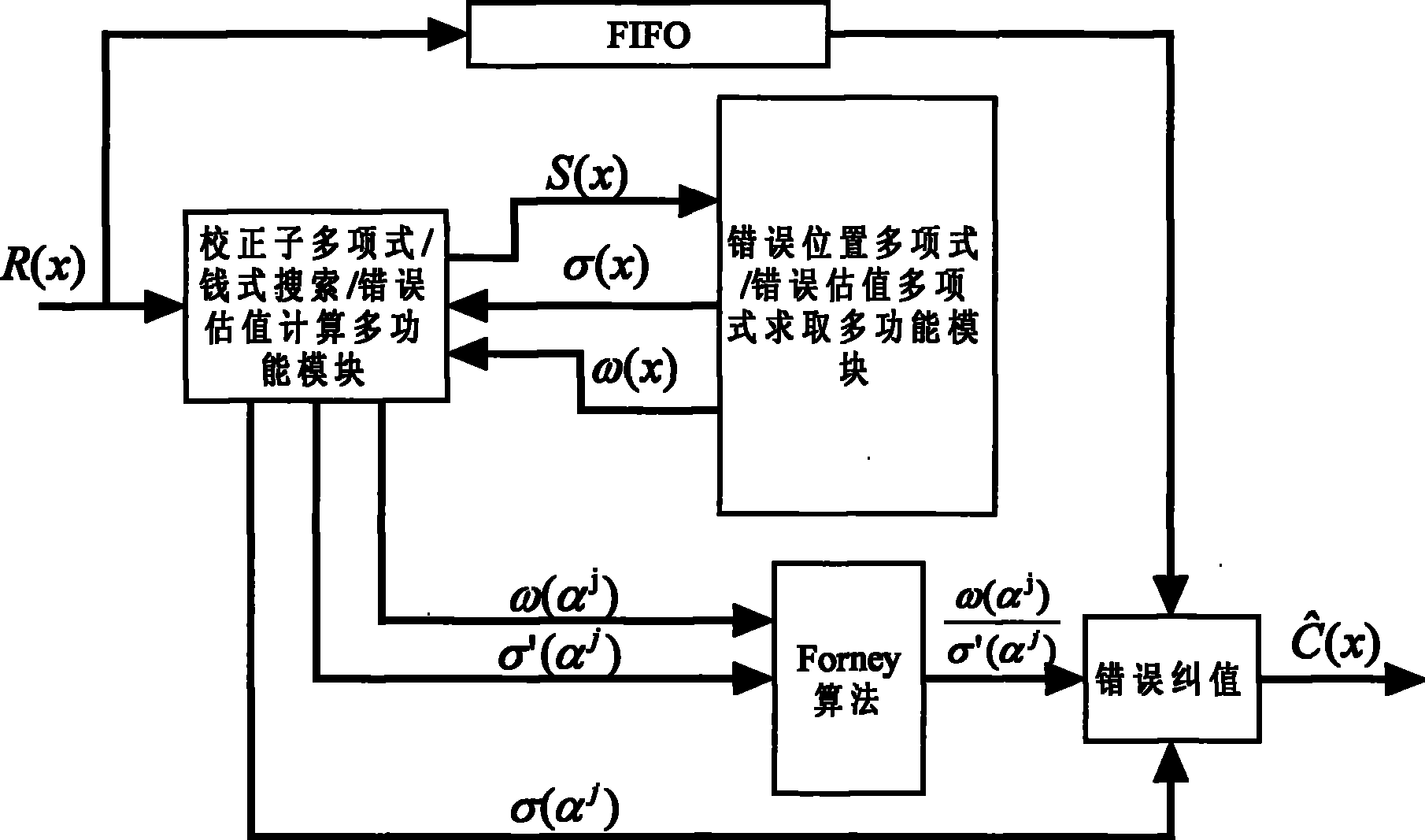

[0041] Such as figure 2 As shown, it is a structural block diagram of the Reed-Solomon decoder in the T-DMB receiving system of the present invention, including syndrome polynomial / money search / error estimation value calculation multifunctional module, error position polynomial / error estimation value polynomial calculation Multifunctional module, Forney algorithm module and error correction module. Wherein, the syndrome polynomial / chian search / error estimate calculation multifunctional module can realize syndrome calculation, chi search and error estimate calculation in time division under the control of the timing control module in the T-DMB receiving system. And described error position polynomial / erroneous estimated value polynomial seeks multi-function module, can realize adopting improved non-inverse Berlekamp-Massey algorithm to solve iterative algorithm for error position polynomial, this modified algorithm does not need to call inversion operation every iteration, Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More