Bus arbitration unit for guaranteeing access sequence and its implementing method

A technology of bus arbitration and sequencing, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of processor 2 reading wrong data, etc., and achieve the effect of satisfying the correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

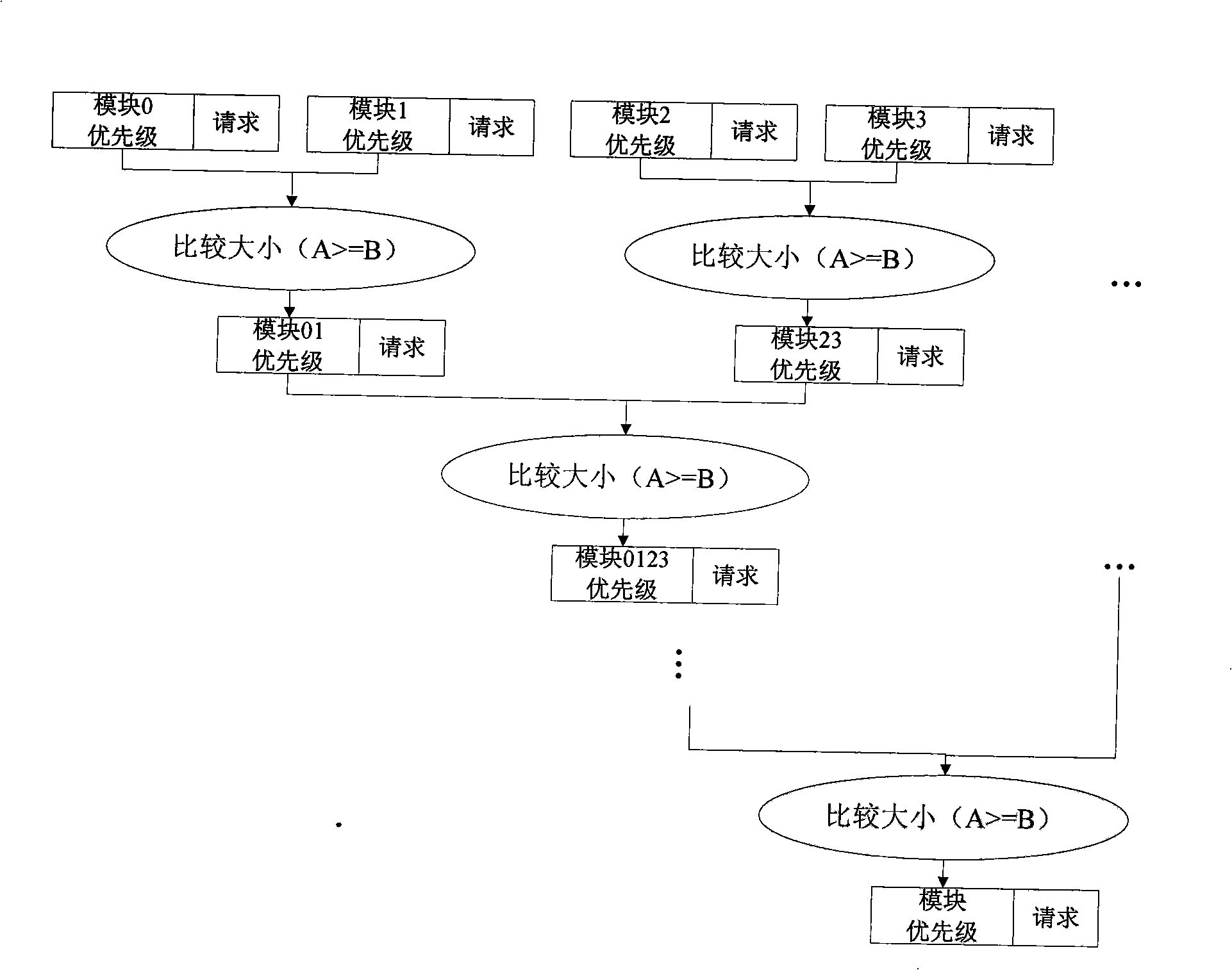

[0027] The present invention designs such a bus arbitration unit: when the bus arbitration unit is idle, if there are multiple requests at the same time, the application result is generated according to a certain priority arbitration strategy, and other unresponsive requests are suspended and saved down. When the bus arbitration unit is busy, subsequent requests will be suspended directly, and all requests coming in this cycle can only be processed after all requests before this time are processed. In short, this bus arbitration unit can ensure the first-come-first-response requests of multiple modules, and then consider the priority of each module itself, ensuring that the sequence of accessing memory by multiple modules is not disrupted, satisfying multiple Correctness of modules working together.

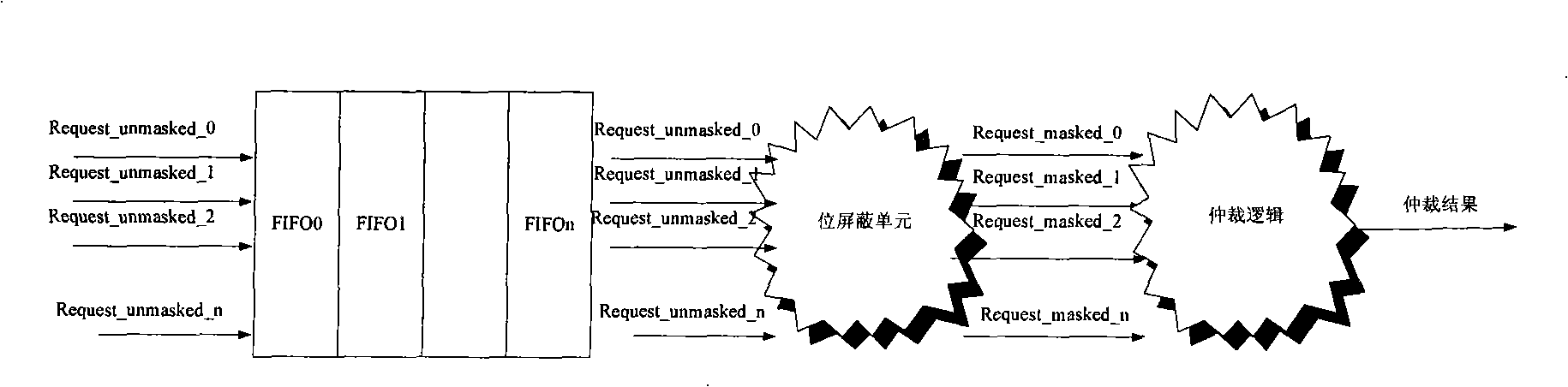

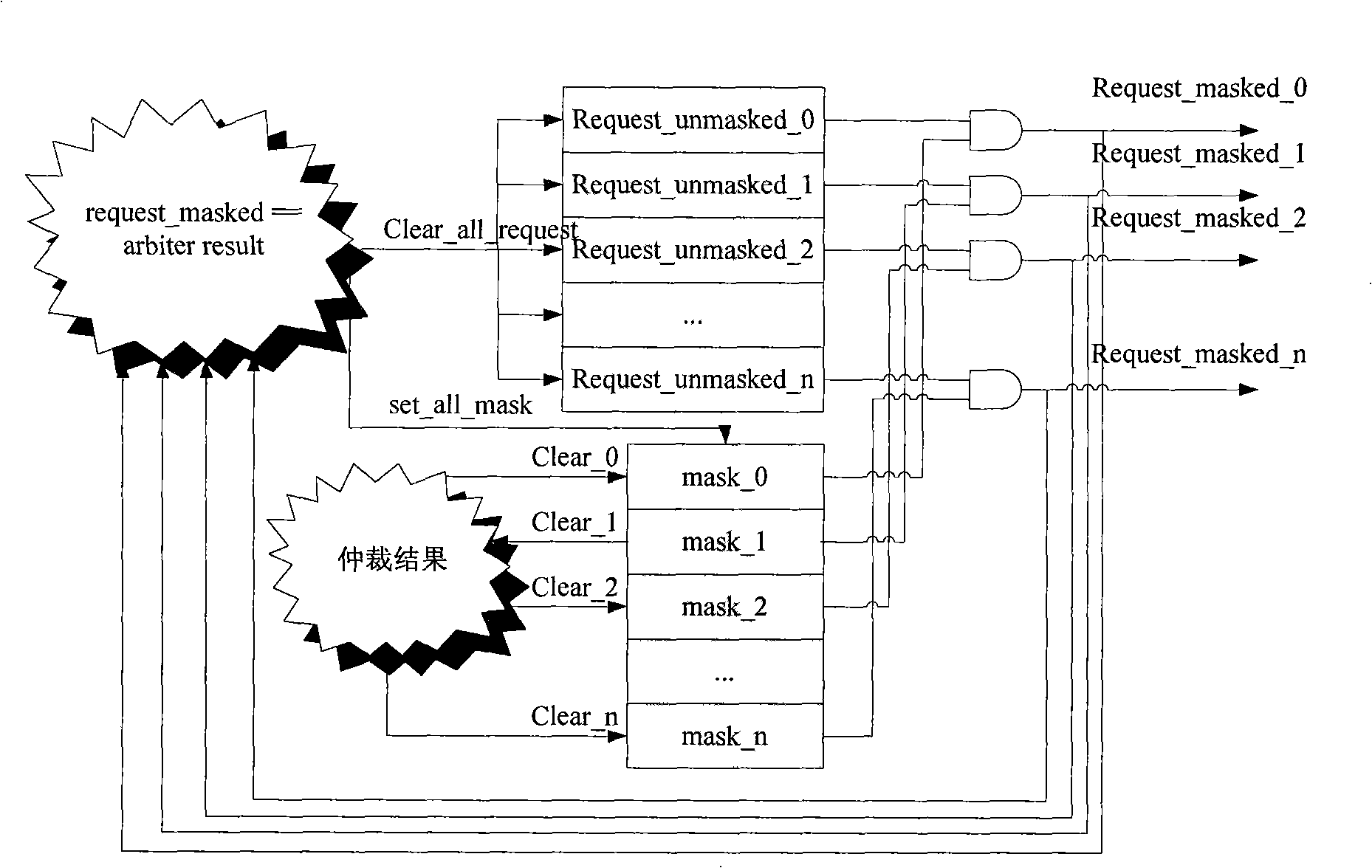

[0028] figure 1 is a block diagram of the bus president unit according to the present invention.

[0029] Such as figure 1 As shown, the bus president unit according to the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More