Improved permutable address processor and method

A technology for replacing addresses and processors, which is used in electrical digital data processing, digital data processing components, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In addition to the preferred embodiment or embodiments disclosed below, the invention is capable of other embodiments and of being practiced or carried out in various ways. Therefore, it should be understood that the invention is not limited to the details of construction and the arrangement of parts shown in the following description or drawings. If only one embodiment is described herein, the claims are not limited to that embodiment. Furthermore, the claims should not be read restrictively unless there is clear and convincing evidence of some exclusion, limitation or disclaimer.

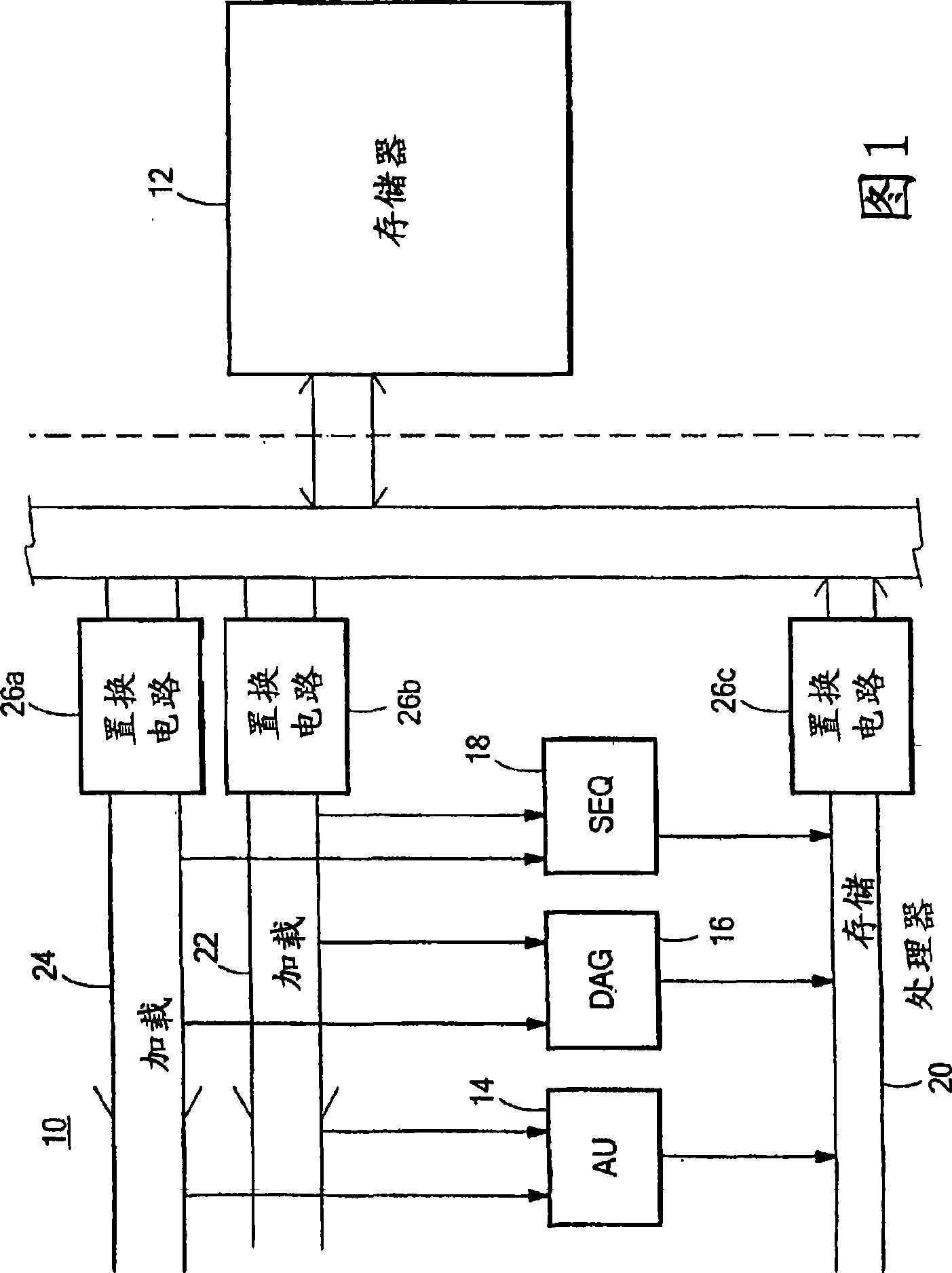

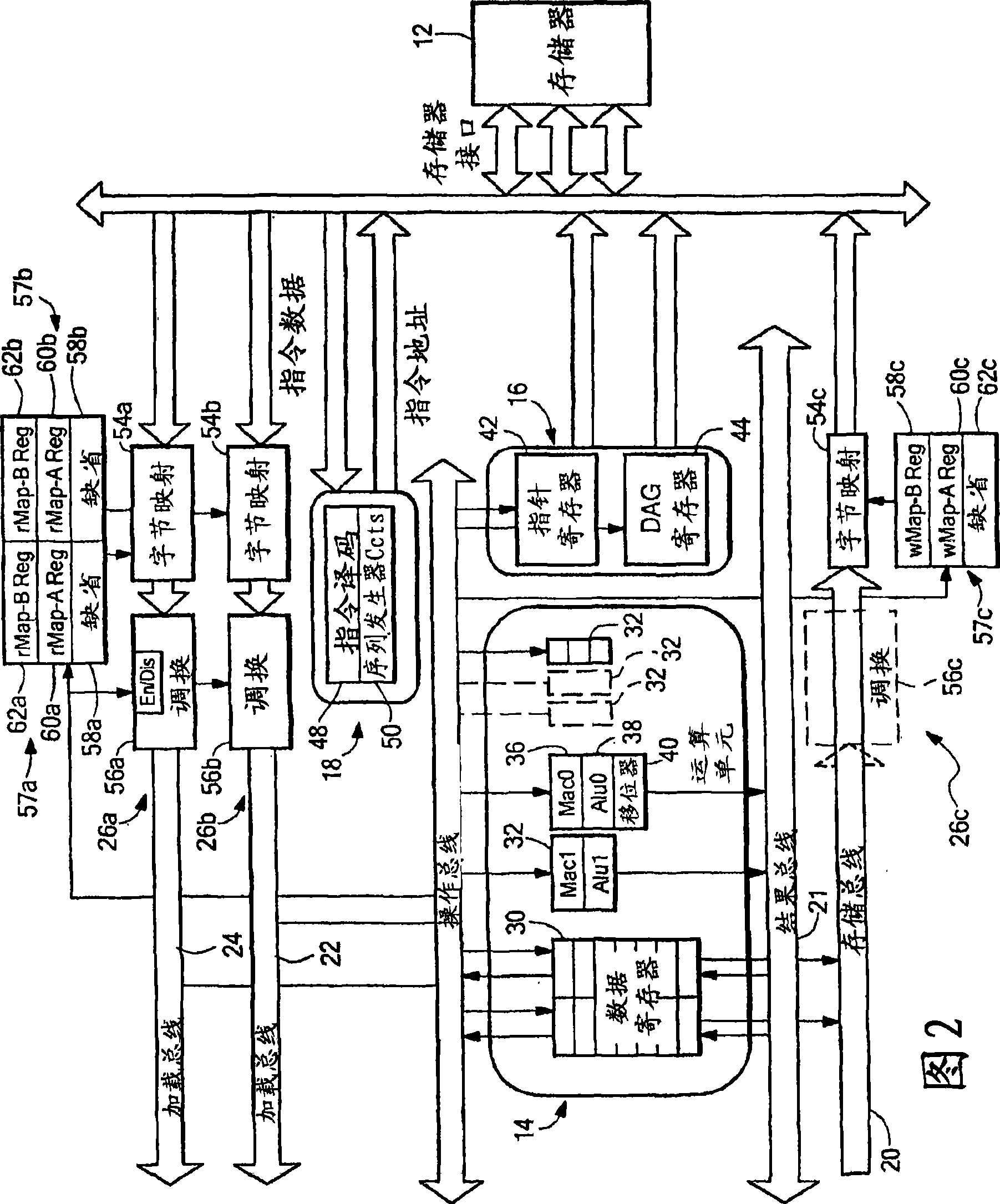

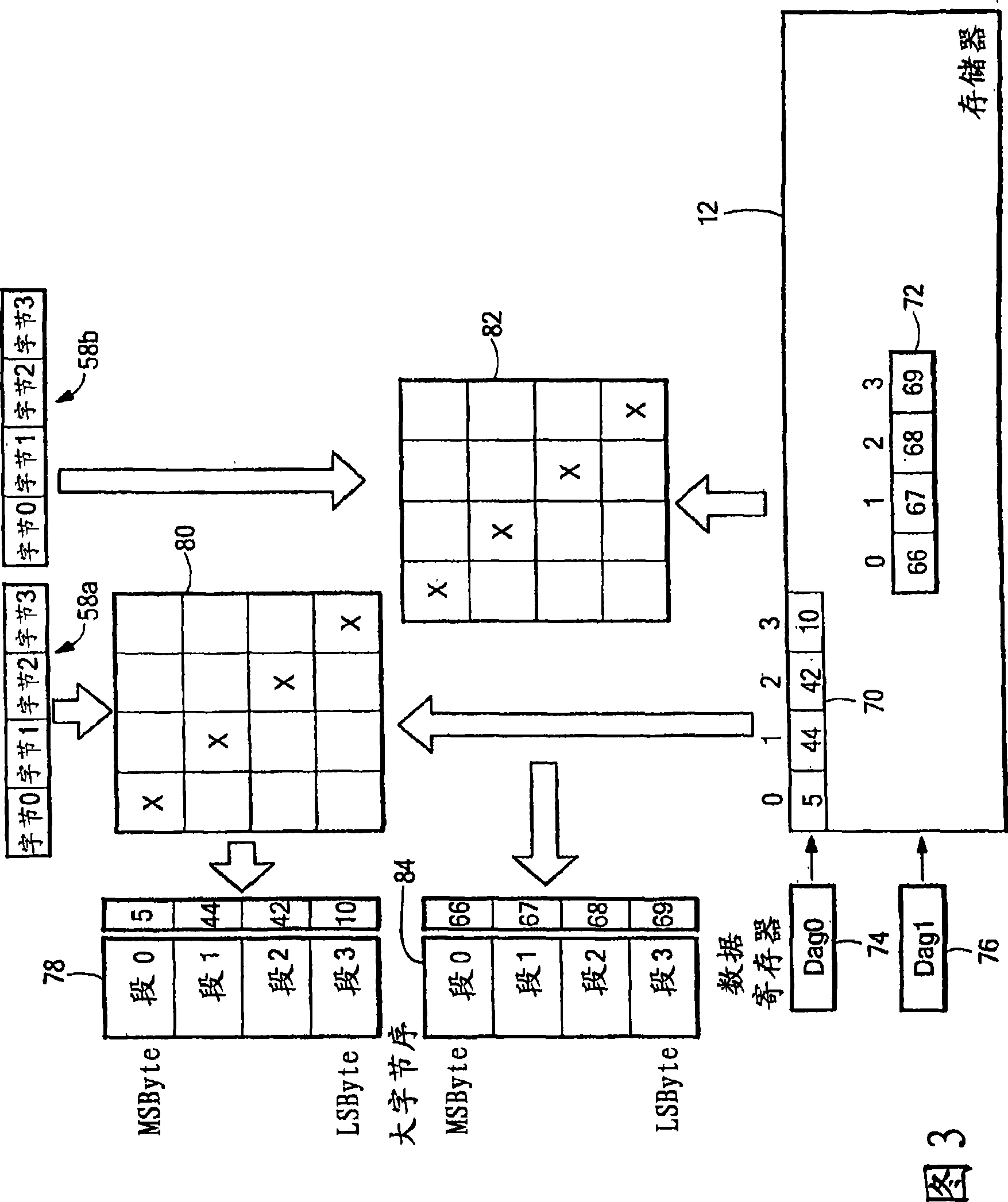

[0033] FIG. 1 shows a processor 10 according to the invention, with external storage means, a memory 12 . Processor 10 typically includes an arithmetic unit 14, a digital data address generator 16 and a sequencer 18 operating in a conventional manner. Data address generator 16 is the controller of all loads and stores with respect to memory 12, and sequencer 18 controls the sequence of in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More