Chip packaging structure

A chip packaging structure and chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problem of inability to increase the number of conductive balls to increase the number of pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

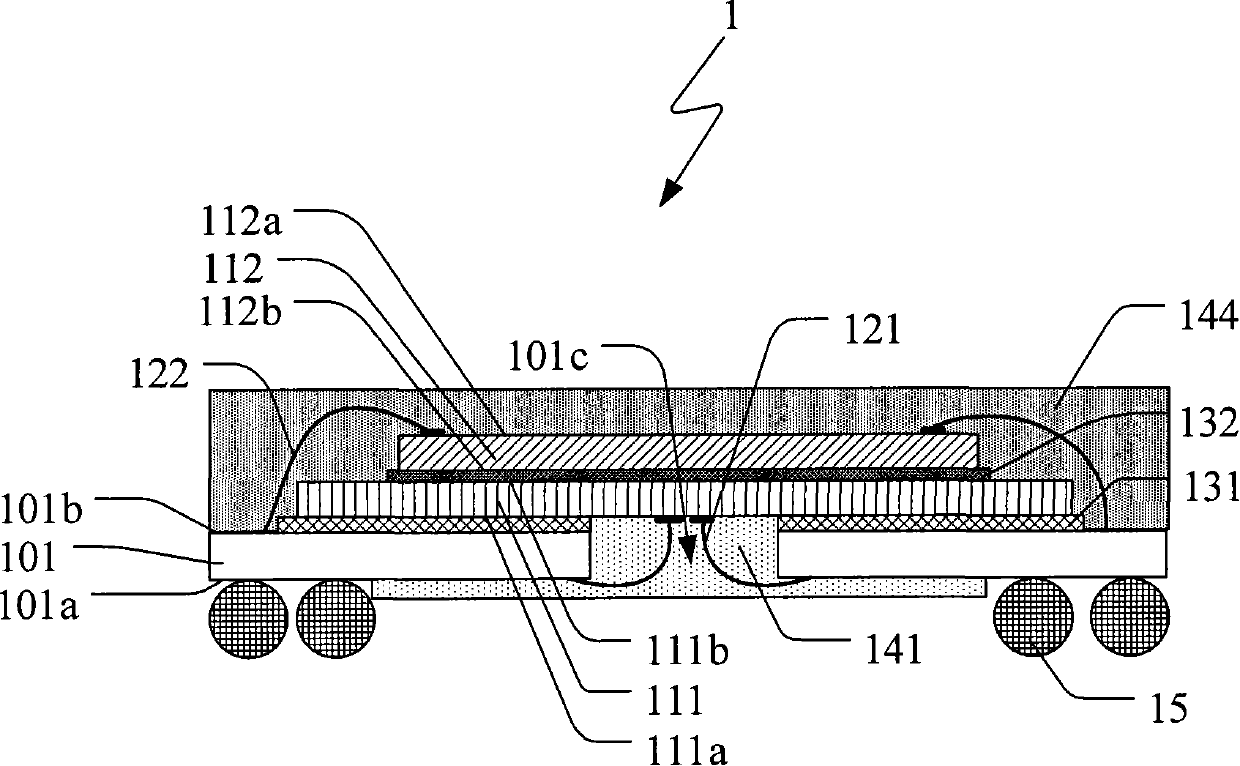

[0016] The basic concept of the chip packaging structure of the present invention is to use two substrates to perform multi-chip stack packaging (Package on Package, PoP), so that at least one of the two substrates does not need to open through holes for electrically connecting chips , and the suit can maintain a complete surface. Therefore, the conductive balls can be covered on the above-mentioned complete surface without avoiding the above-mentioned through holes, and the ball grid array (BGA) package can be carried out, and the number of ball grids can be greatly increased to cope with the increase in a certain area. Trends in chip package structure pin counts.

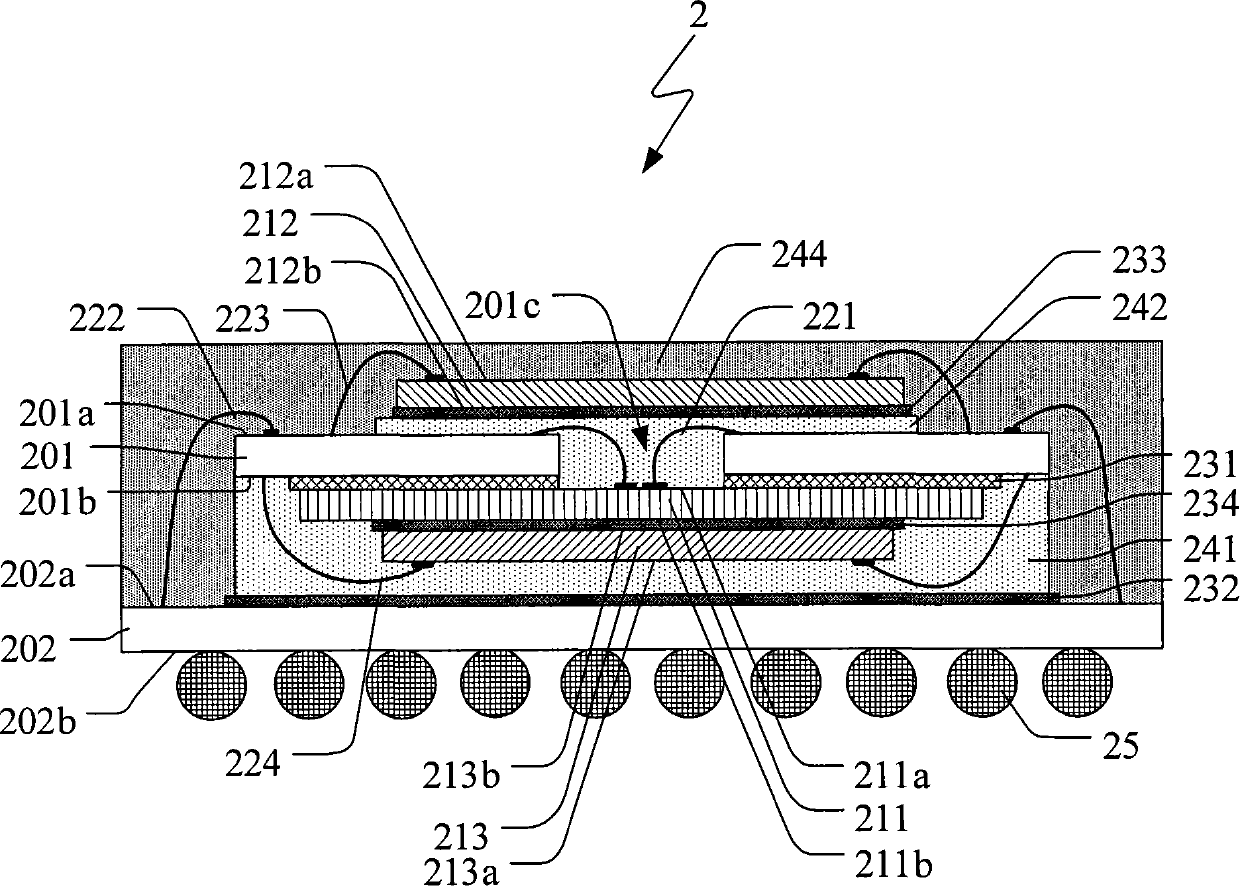

[0017] Such as figure 2 As shown in the part, the chip packaging structure 2 of the present invention as a whole includes at least a first substrate 201, a second substrate 202, a plurality of chips, a first wire part 221, a second wire part 222, a third wire part 223, a first wire part 223, a The four wire par...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More