Method for optimizing area of mixed signal chip

A chip area, mixed signal technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of large IP area, large chip area, large device area, etc., to optimize performance and reduce chip area , the effect of reducing the use of capacitors or resistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

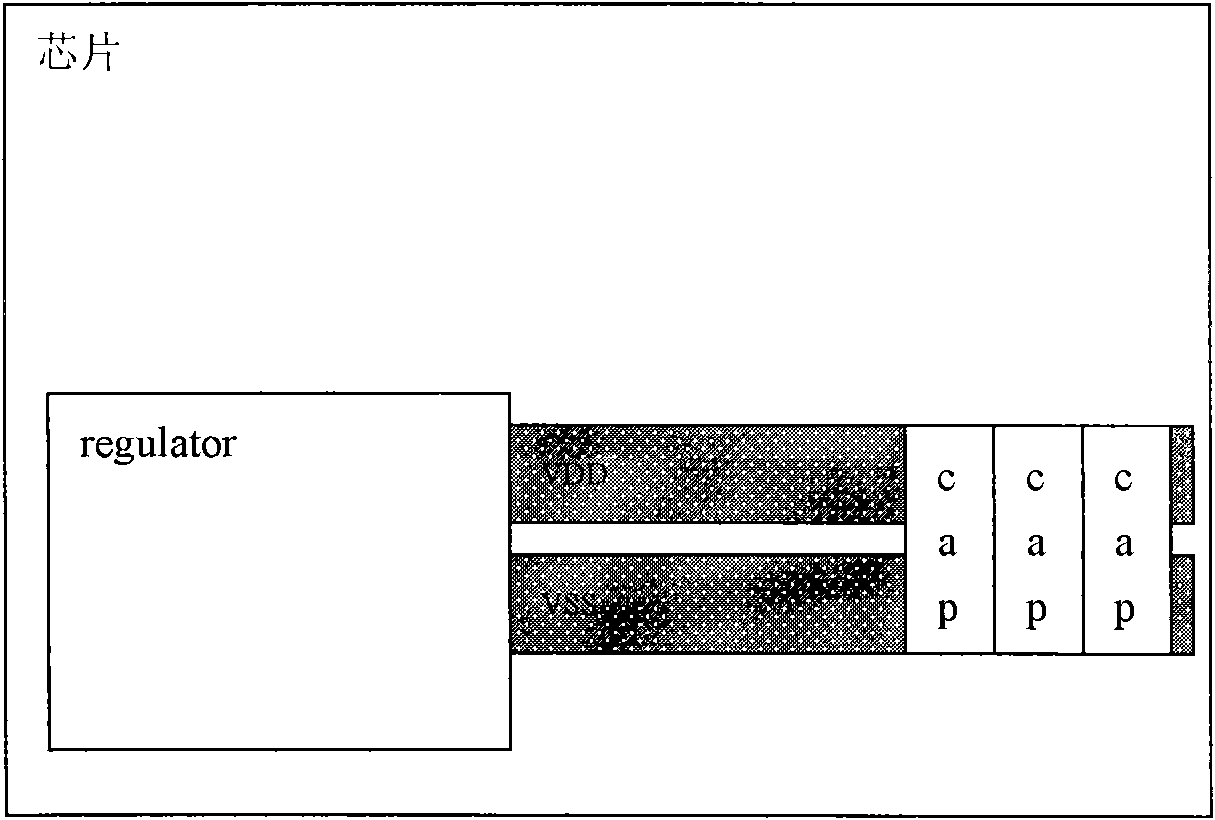

[0023] see Figure 1 to Figure 3 , the steps of the method for optimizing the area of the mixed-signal chip in the present invention are:

[0024] ① When designing the regulator layout, separate the capacitors in the regulator to greatly reduce the area of the regulator;

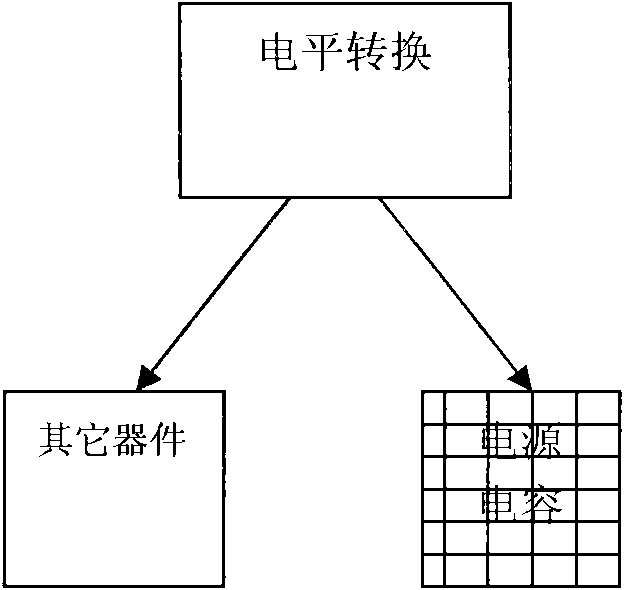

[0025] ② Arrange the completed regulator and other logic units to obtain the area of the entire chip;

[0026] ③ Place the separated capacitor on the power ring on the chip or under the pad that uses a different metal layer from the capacitor.

Embodiment 2

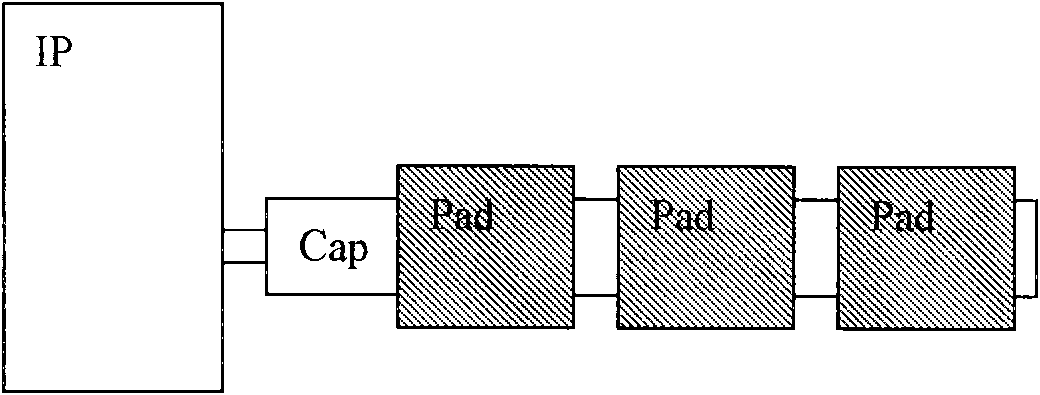

[0028] A method for optimizing the area of a mixed-signal chip is as follows:

[0029] ① When designing the IP layout, do not place resistors or capacitors in the IP, so that the IP area is greatly reduced;

[0030] ② Arrange the completed IP and other logic units to obtain the area of the entire chip;

[0031] ③ According to the simulation of the whole chip, the number of resistors or capacitors to be added is obtained, and the resistors or capacitors are placed on the chip power ring, under the pad pad, or in a wiring area that is different from the metal layer used by the resistors or capacitors .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More