Decoding method of power supply line of memory array

A memory and memory cell technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of high power, consumption, and difficulty in reducing device power consumption, and achieve the goal of reducing standby current, simple design, and low-cost implementation. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

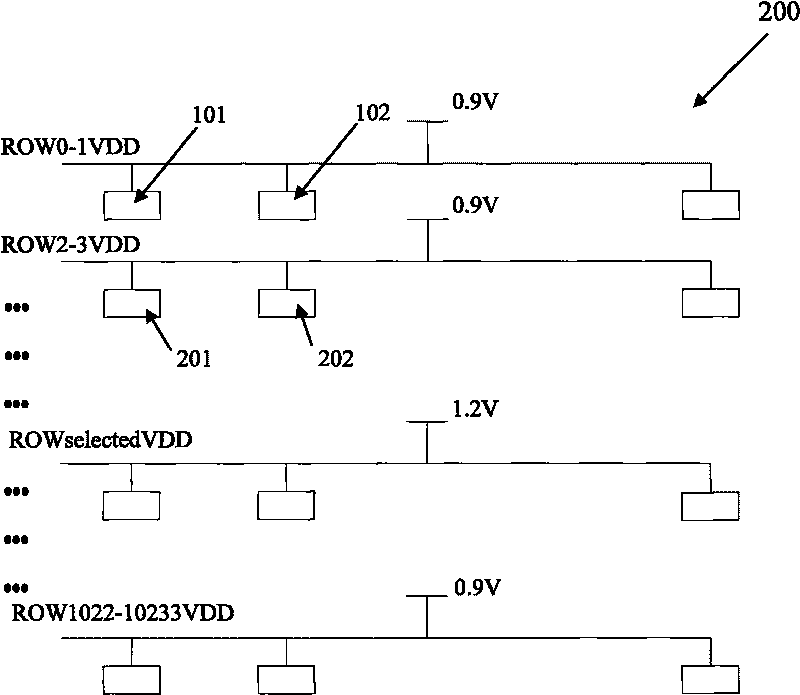

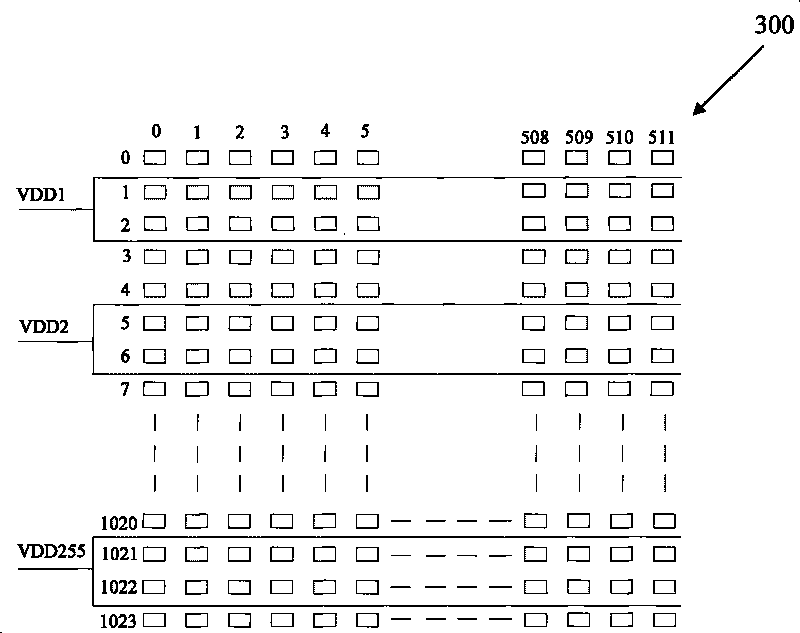

[0025] According to the present invention, an integrated circuit and a process thereof for semiconductor device manufacture are provided. More specifically, the present invention provides a method and apparatus for selectively reducing the supply voltage of an SRAM memory array. By way of example only, the invention has been applied to SRAM devices to provide low power consumption while maintaining high storage speeds. It should be realized, however, that the invention has a much wider range of applicability. For example, the invention is applicable to other embedded or stand-alone integrated circuit memories, such as DRAM and non-volatile memories.

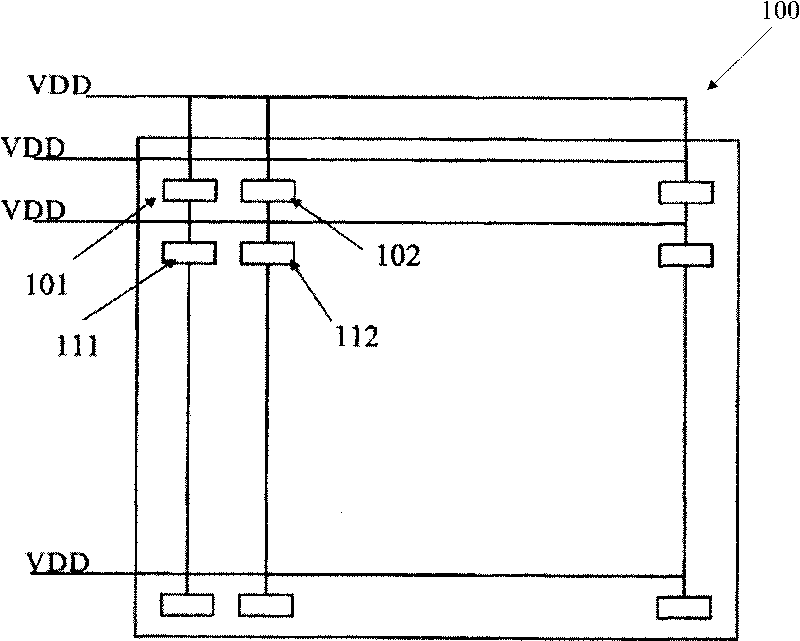

[0026] figure 1 is a schematic diagram of an existing SRAM array 100 . As shown, the SRAM memory array 100 includes memory cells, such as 101 , 102 , . . . , 111 , 112 . . . . In a typical existing SRAM array, such as the SRAM array 100, all memory cells are supplied with the same power supply voltage VDD. The power grid in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More