Method for dynamically and fairly partitioning shared cache based on chip multiprocessor

A multi-core processor, dynamic technology, applied in the direction of resource allocation, multi-programming devices, etc., can solve the problem of lack of fairness in the system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

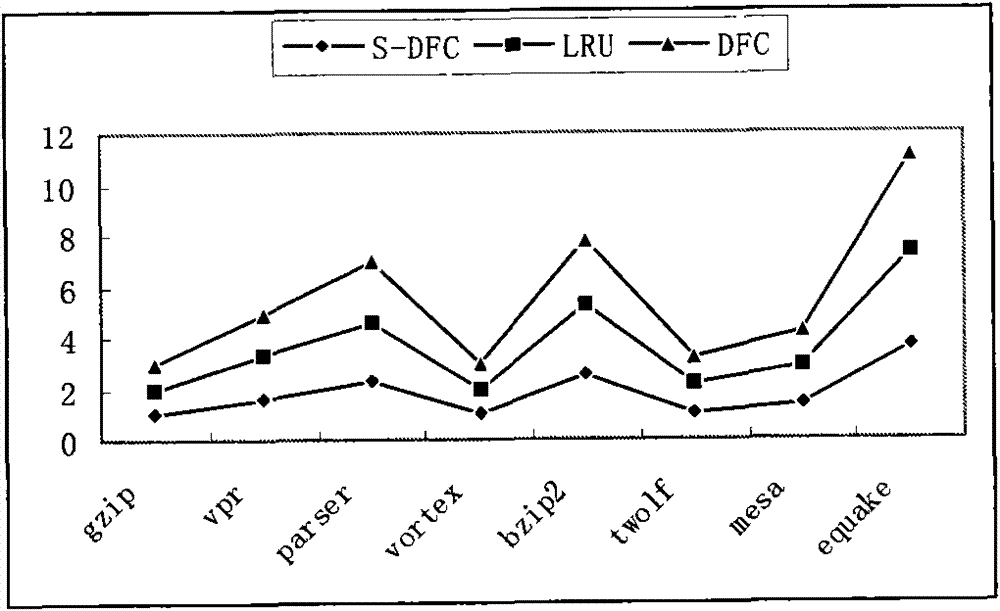

[0065] Taking an on-chip multi-core processor as an example, the method of the present invention will be described in detail below. The processor configuration is shown in Table 1:

[0066] Table 1 CMP configuration

[0067]

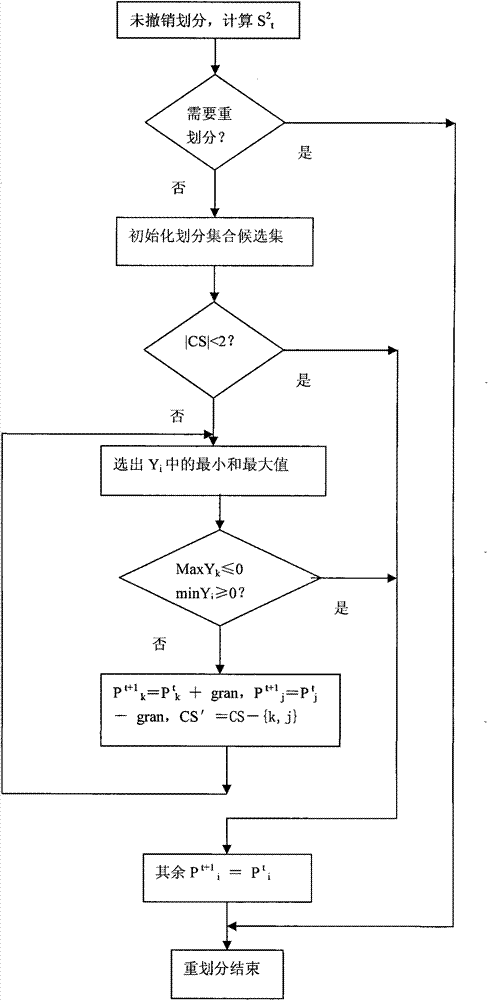

[0068] On this processor, the four parameters take the value S respectively rollback =10%, S repartition =1%, gran=64B and t=1000000, the specific division steps are as follows:

[0069] (1) Initialization:

[0070] 1.1) All threads equally divide Cache, Pi=512KB / 4=128KB;

[0071] 1.2) According to the current computer architecture, then M 1 =0.1,E 1 =3,E 2 =6,E 3 = 158 and CPI base =0.5

[0072] 1.3) Calculated = CPI base +E 1 +M 1 ×E 2 = 4.1 and β = E 3 =158;

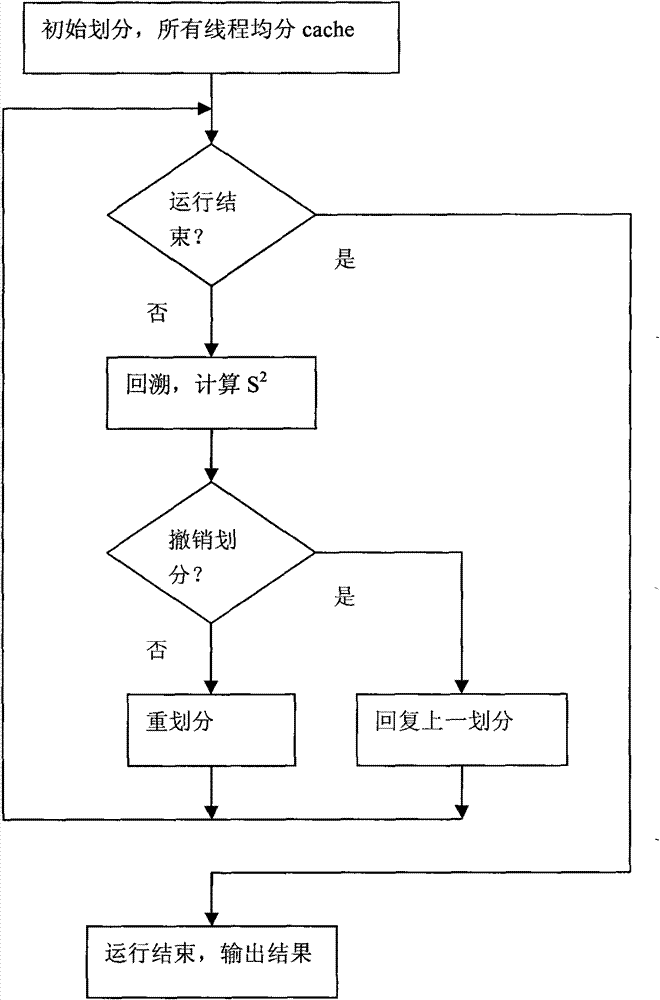

[0073] (2) Backtracking stage:

[0074] 2.1) Calculate the fairness index S of the current division scheme 2 , currently the first time slice, S 2 1 = 1.38;

[0075] 2.2) If the current time is the end of the first time slice, then let S 2 0 =1000000;S 2 1 2 0 , go t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More