Memory control method and memory control device

A control method and control device technology, applied in the direction of instruments, data conversion, electrical digital data processing, etc., can solve problems such as unavailable triggers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Hereinafter, embodiments of the present invention will be described with reference to the accompanying drawings.

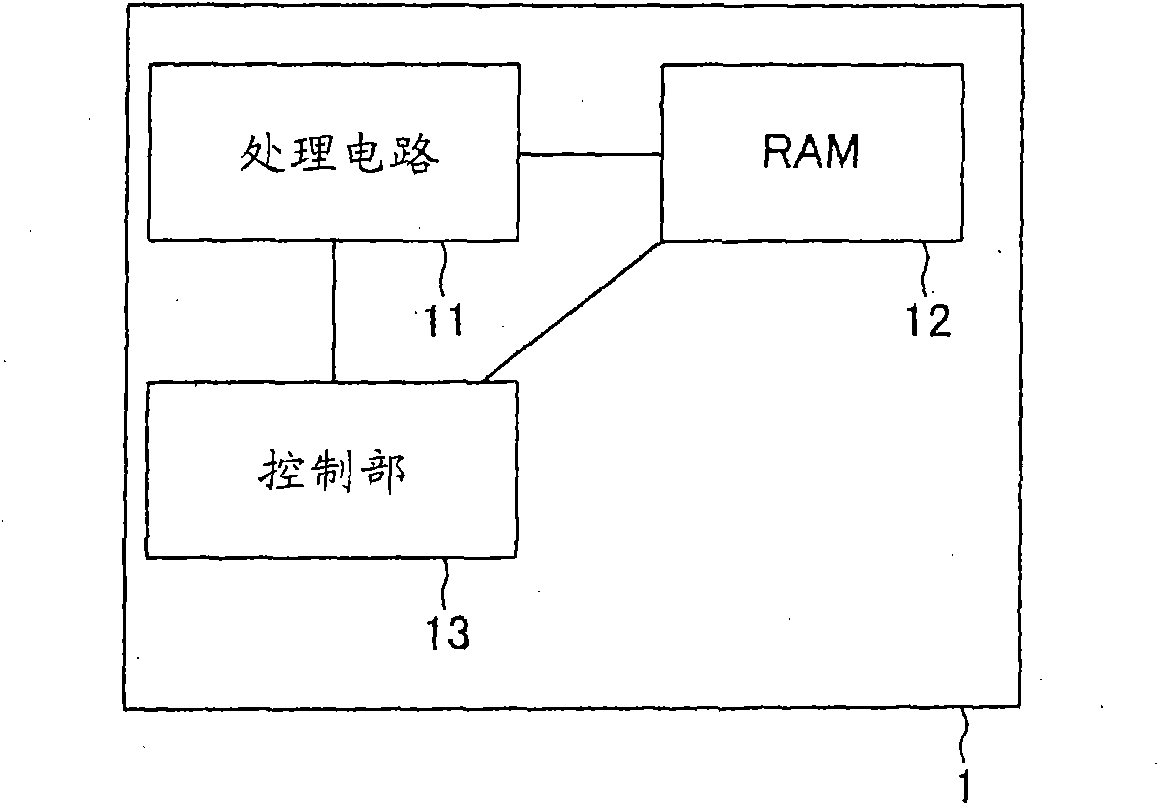

[0040] The structure of the integrated circuit of this embodiment mode will be described below. figure 1 The structure of the integrated circuit according to this embodiment is shown.

[0041] Such as figure 1 As shown, the integrated circuit 1 of this embodiment includes a processing circuit 11, a RAM 12 (memory), and a control unit 13 (memory control device). The processing circuit 11 executes predetermined processing using the RAM 12 . The RAM 12 temporarily stores data scheduled to be processed by the processing circuit 11 . The control section 13 performs first-in-first-out access control to the RAM 12 .

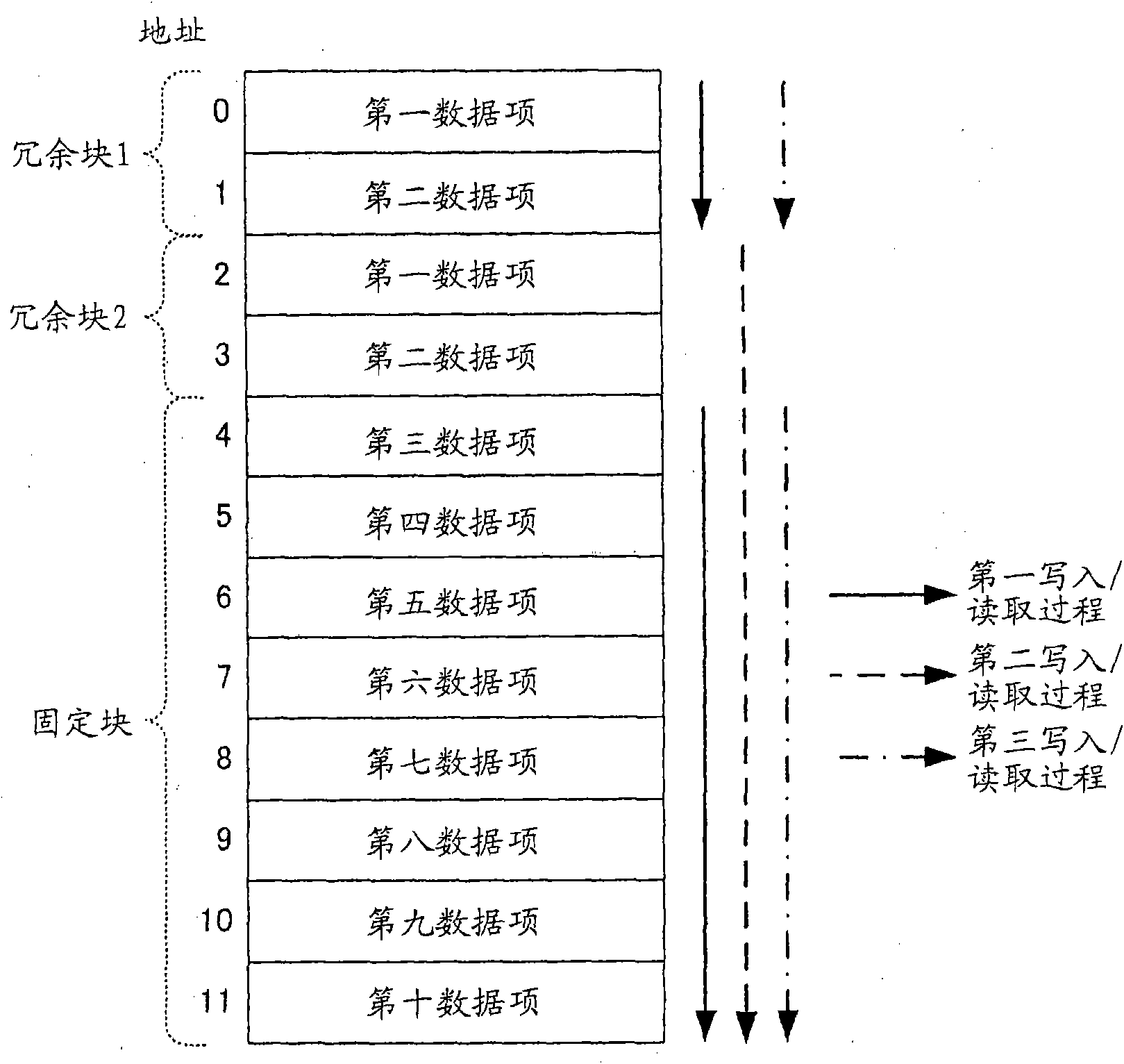

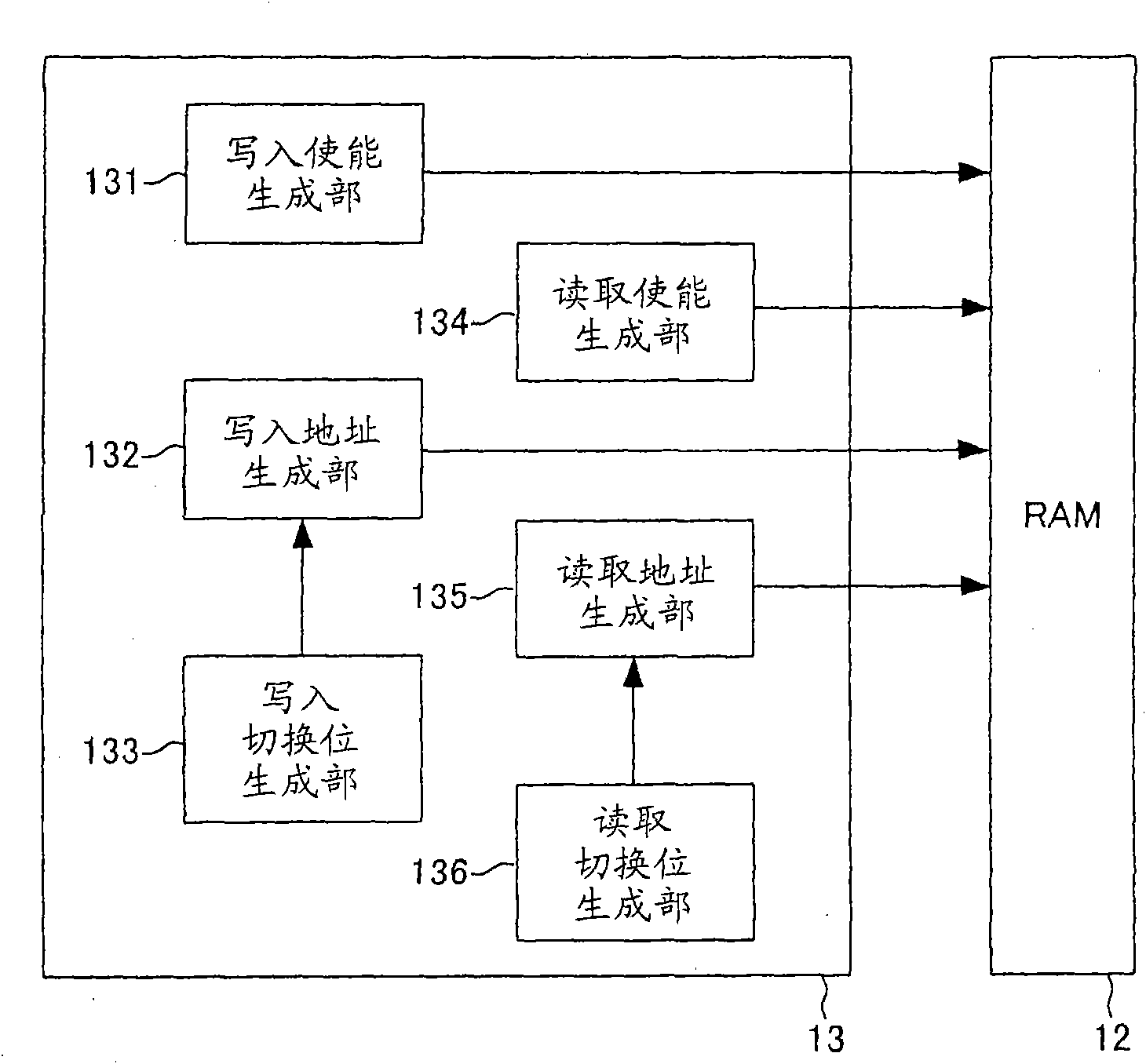

[0042] Next, the schematic structure and access control of the RAM will be described. figure 2 Show the schematic structure and access control of RAM.

[0043] Such as figure 2As shown, the RAM 12 includes memory areas represented by addre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More