Out-of-order execution micro-processor and method of executing the related command

A technology for microprocessors and executing instructions, applied in the direction of machine execution devices, etc., can solve problems such as system performance damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

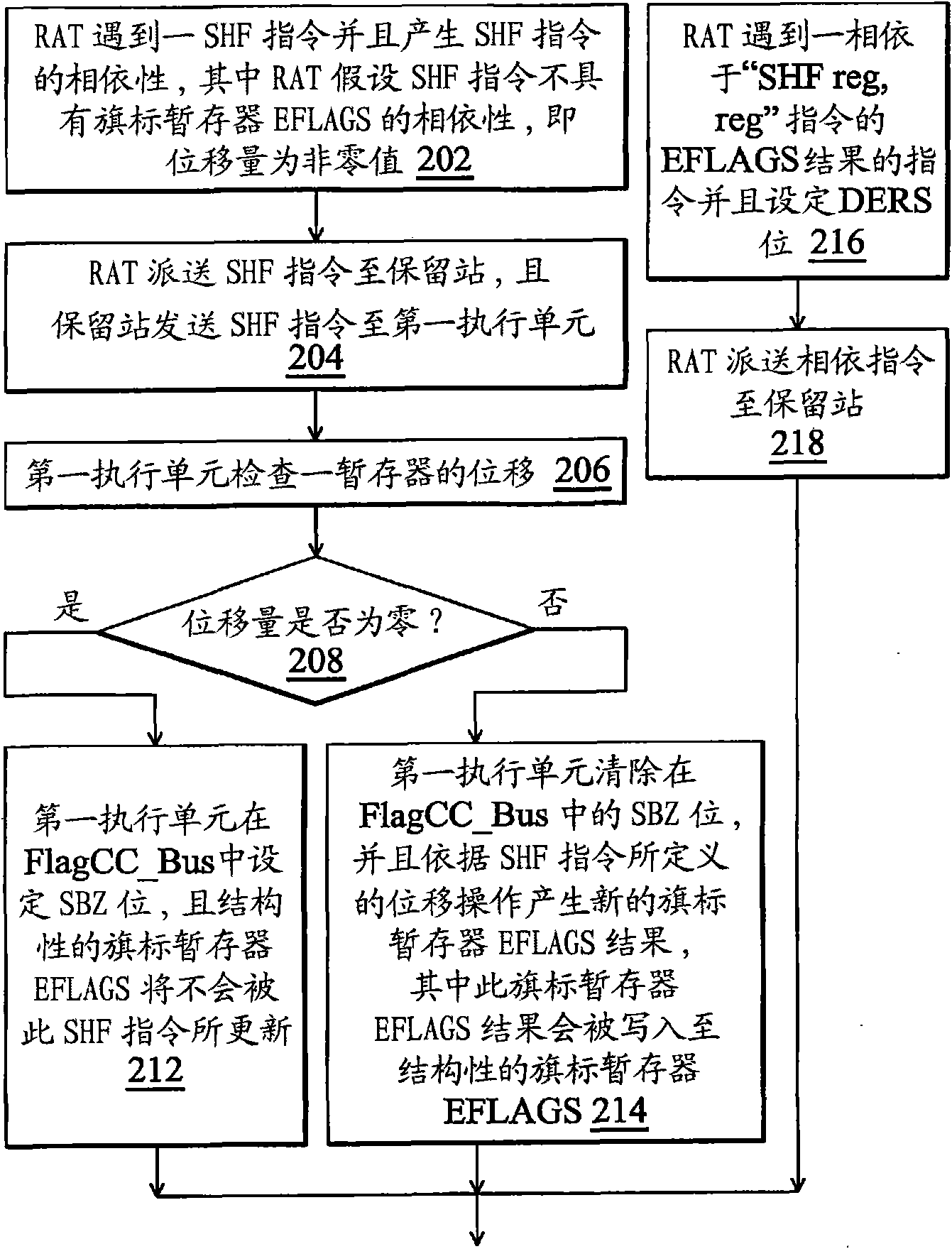

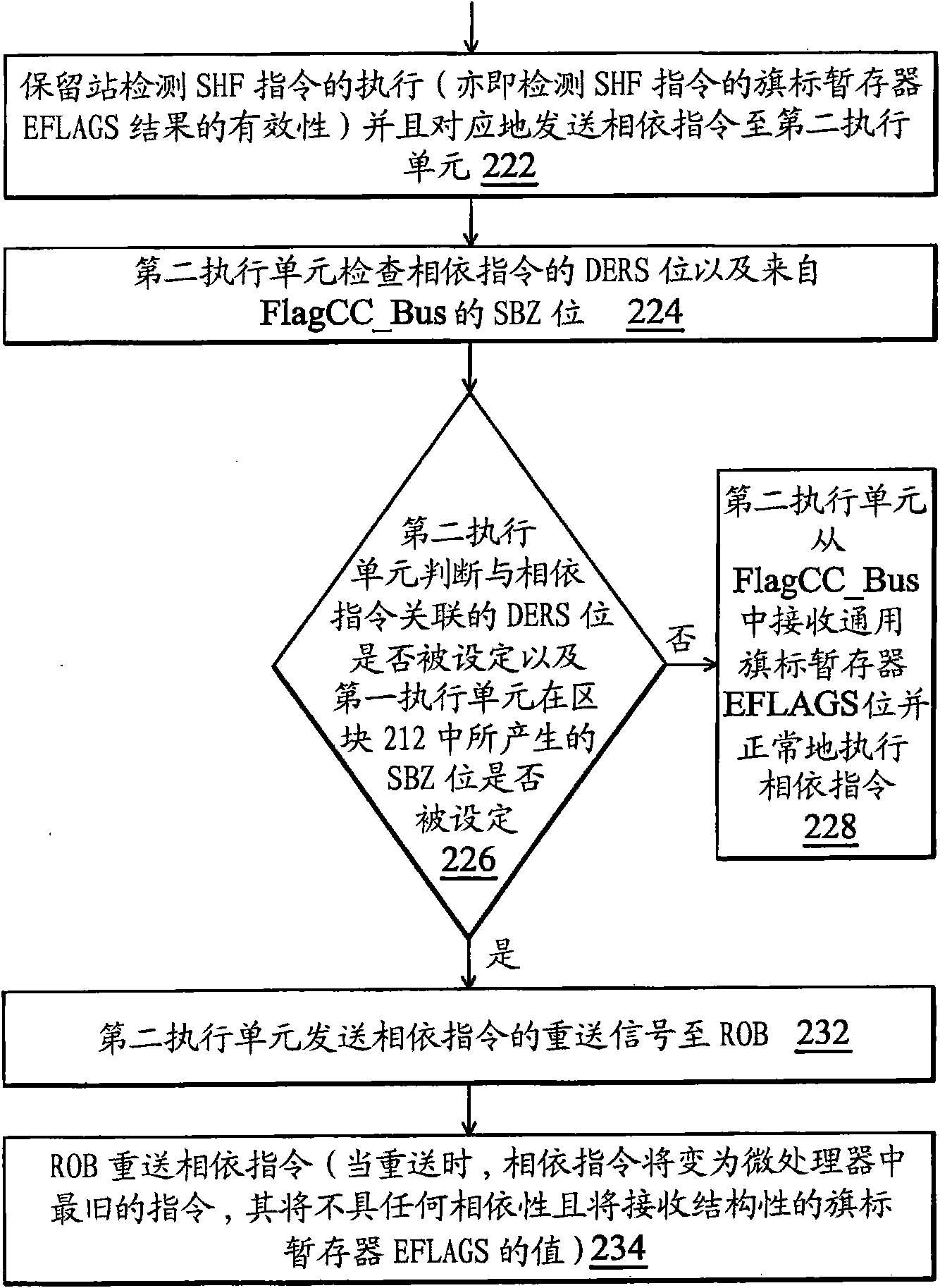

[0028] In order to solve the aforementioned performance problems, the register alias table (RAT) always assumes that the displacement is non-zero. In this way, an SHF instruction does not need to depend on a flag register EFLAGS (that is, There is no need to depend on the nearest flag register EFLAGS-modify command older than the SHF command). If the execution unit later determines that the displacement of the SHF instruction is zero, and encounters an instruction that specifies a condition code result as a source operand, the above instruction depends on the flag of an older SHF instruction When the EFLAGS result is stored in the register, the reorder buffer (ROB) will replay the instructions dependent on the SHF instruction. In one embodiment, the result of the above condition code is, for example, the result of a flag register EFLAGS of the x86 architecture, which may be a value in the flag register EFLAGS.

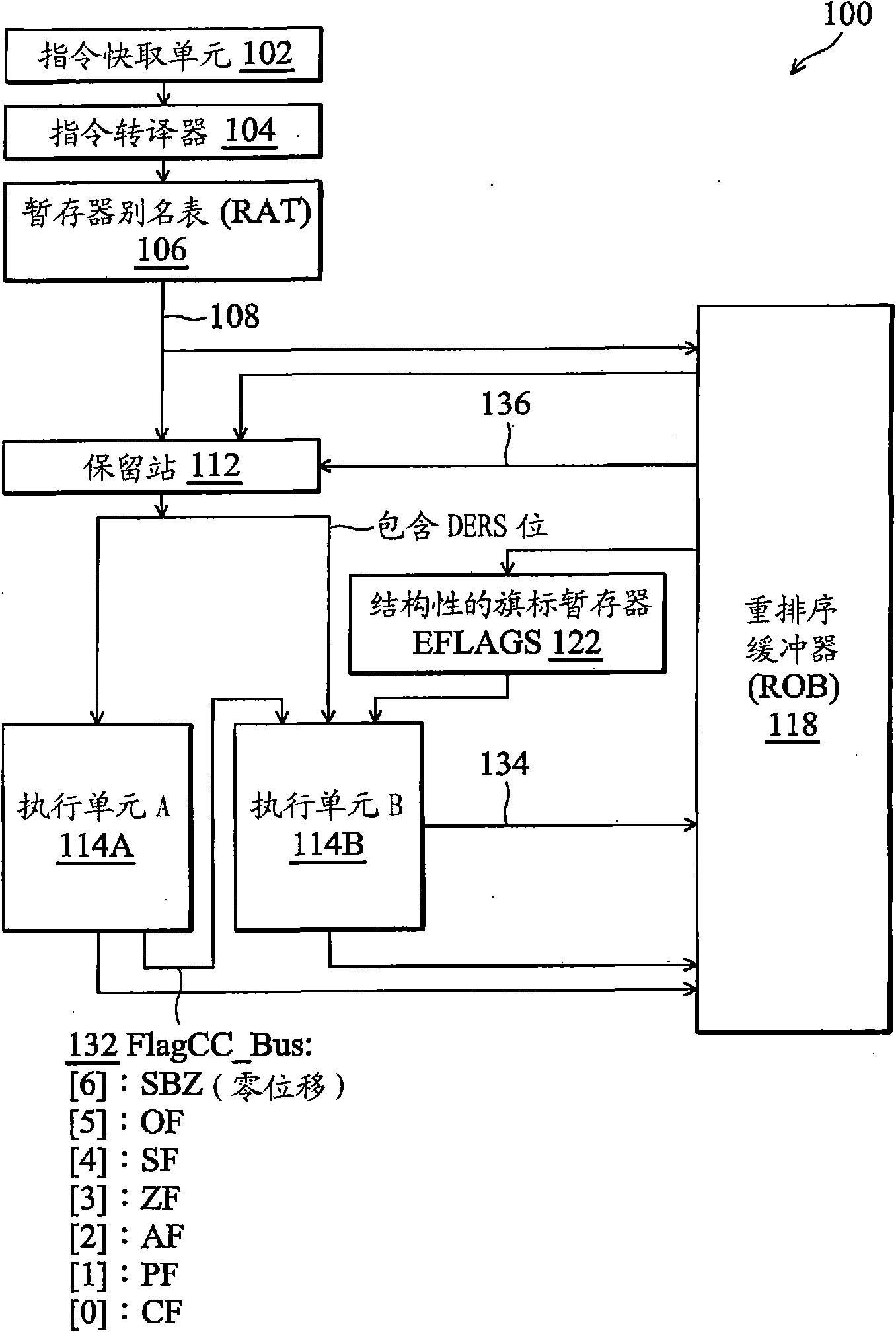

[0029] See figure 1 , Is a block diagram showing a microprocessor 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More