JTAG (Joint Test Action Group) based synchronous debugging method of multi-chip microprocessor

A debugging method, microprocessor technology, applied in the direction of electrical digital data processing, instrumentation, calculation, etc., to achieve the effect of good reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

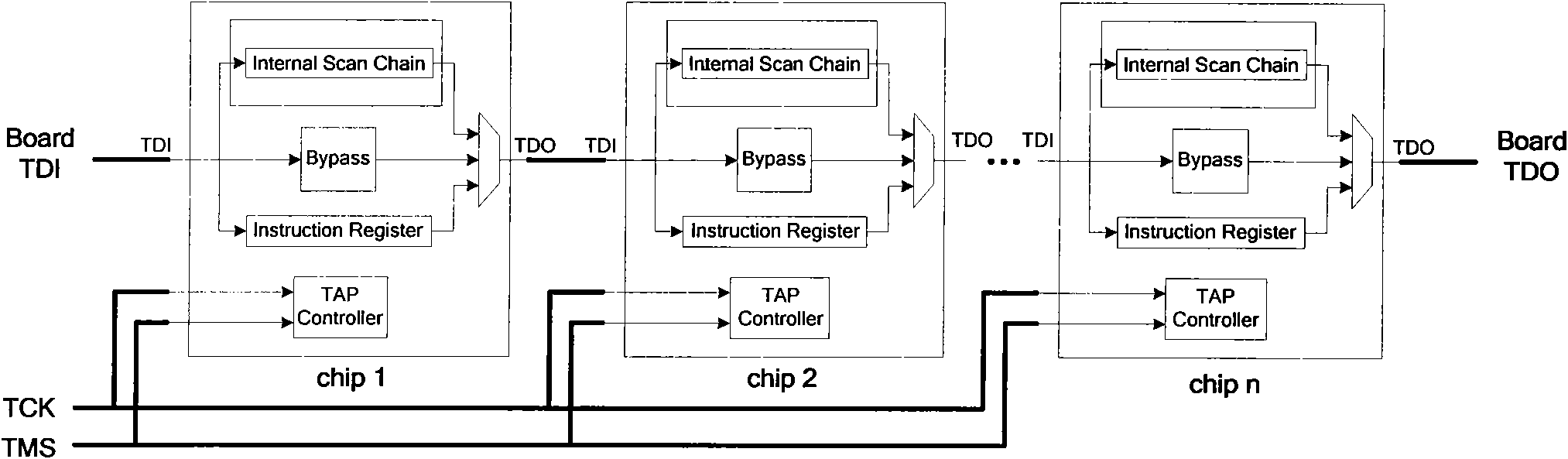

[0017] Such as figure 1 As shown, in an interconnected system with multiple processors, the JTAG links of multiple processor chips are serially connected to one JTAG link in a daisy chain mode, that is, the TDI of the first processor chip chip 1 (test Data input) is connected to the TDI of the off-chip JTAG emulator interface, the TDI of the second chip 2 to the last processor chip chip n is connected to the TDO (Test Data Output, test data output) of the previous processor chip in turn, and finally A TDO of the processor chip is connected to a TDO of the off-chip JTAG emulator interface. The TDI signal and TDO signal of each chip are connected into a serial link. TCK and TMS of the off-chip JTAG emulator interface are connected in parallel with TMS (test clock input) and TCK (test mode selection) of all chips.

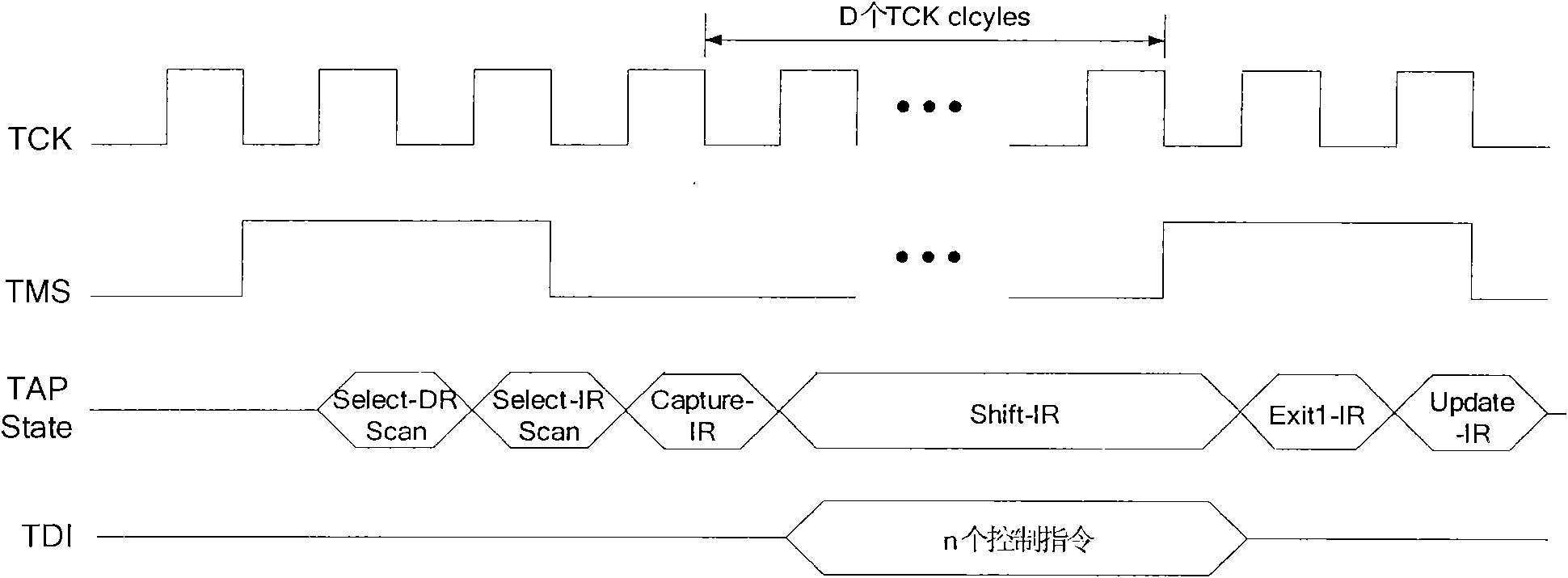

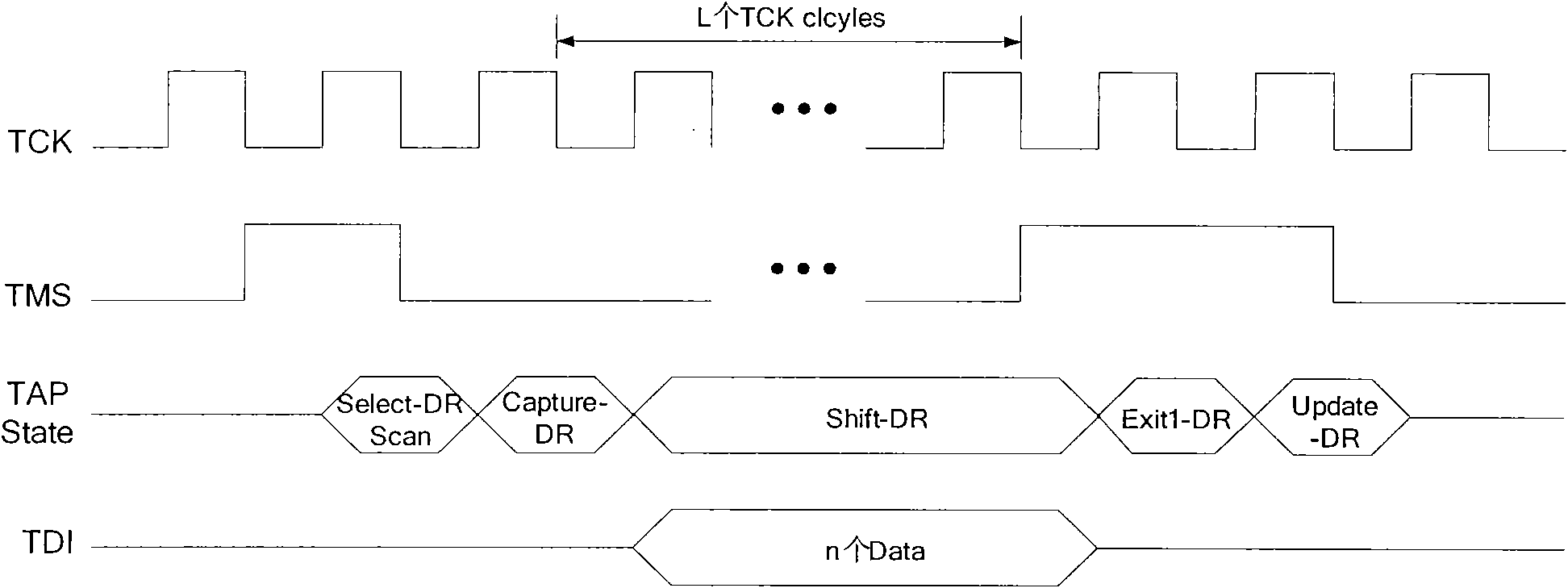

[0018] Such as figure 2 As shown, after the JTAG emulator receives the control command, it generates and sends a TMS signal according to the length parameter of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More